112

И;5обре.тение относится к автоматике и вычислительной технике и может найти применение, в частности, в моделирующих гибридных вычислительных системах,.

Цель изобретения - повышение динамической точности воспроизведения функций переменного запаздывания.

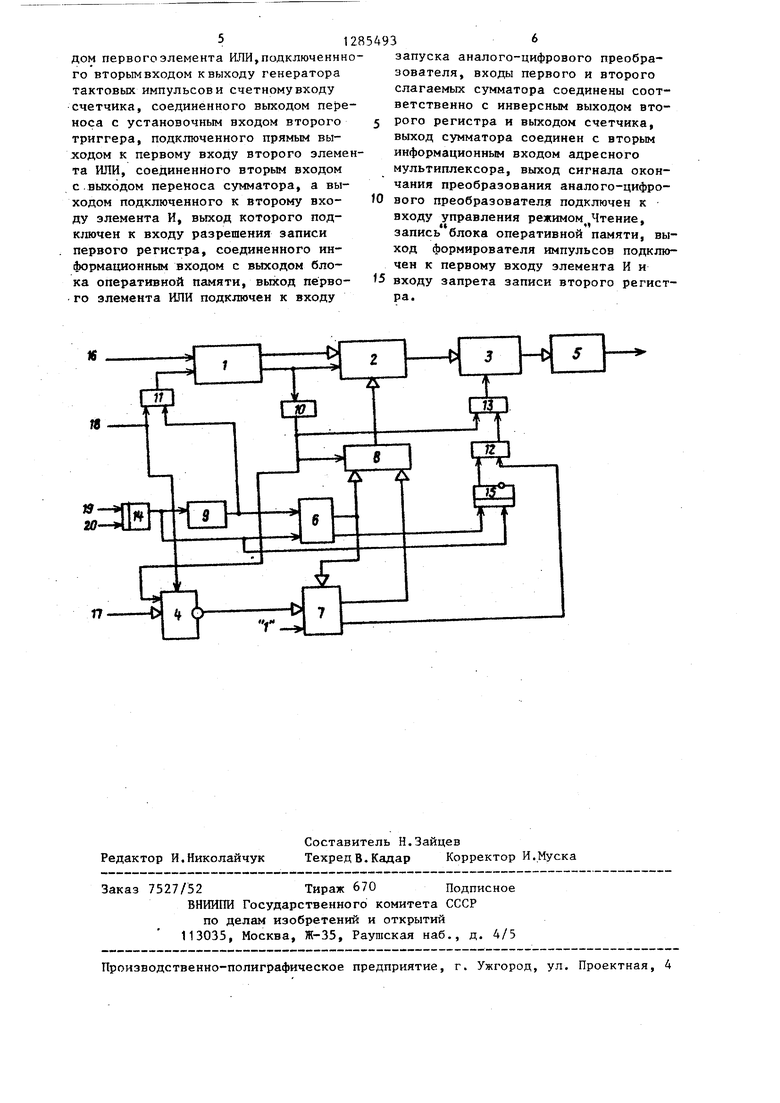

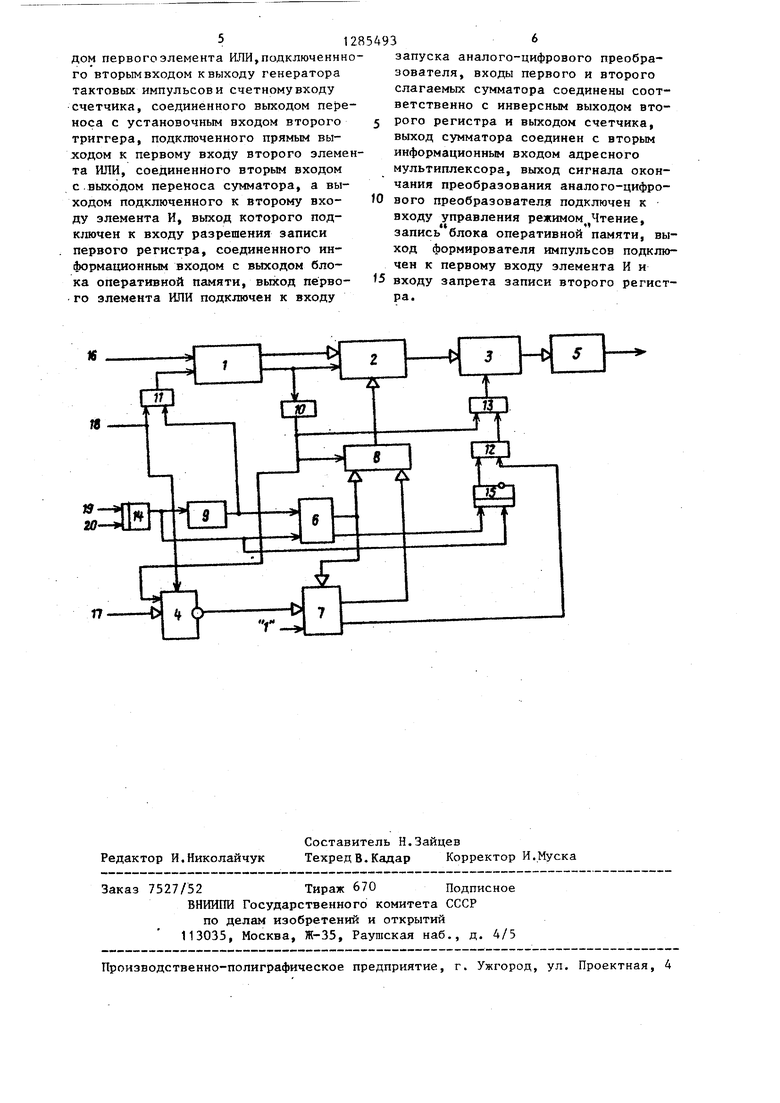

На чертеже приведена функциональная схема устройства для воспроизве- дения запаздывающих функций.

Устройство содержит аналого-цифровой преобразователь 1, блок 2 оперативной памяти, первый 3 и второй 4 регистры, цифроаналоговый преоб- разователь 5, счетчик 6, сумматор 7, адресньй мультиплексор 8, генератор

9тактовых импульсов, формирователь

10импульсов, первый 11 и второй 12 элементы ИЛИ, элемент И 13, первый 14 и второй 15 триггеры, вход 16 задания начальных условий устройства, вход 17 задания кода з адвржки функции устройства, вход 18 управления установкой нача.льньгх условий устройства, вход 19 запуска устройства и вход 20 останова устройства.

Устройство работает следующим

образом.

I

В 1гачальном состоянии триггер 14 сигналом с входа 20 останова сброшен в нулевое состояние. Выходной сигнал триггера 14 при этом запрещает работу генератора 9 и удерживает в нуле- вом состоянии счетчик 6 и триггер 15

Перед запуском устройства на вход 18 подается импульс установки начальных условий. Этот импульс обнуляет регистр 4, предназначенньй для хра- нения текущего значения кода времени запаздывания, и поступает через элемент ИЛИ 11 на вход запуска аналого- цифрового преобразователя 1,

Преобразователь 1 формирует кодо- вьй эквивалент начального условия, поступающего на аналоговый вход 16 устройства, и передает его на инфор- мационньй вход блока 2 оперативной памяти. По переднему фронту импульса окончания преобразования выполняется запись кода начального условия в блок 2 по нулевому адресу, поступающему на адресный вход блока 2 с выхода счетчика 6 через адресный мульти- плексор 8.

Задний фронт импульса окончания преобразования переводит блок 2 оперативной памяти в режим чтения дан5

4

0

5

0

0

0

5 50 55

932

ных. в моме.чт времени на выходе формирователя 10 появляется импульс, которьй блокирует изменение содержимого регистра 4 по входу запрета записи (подает запирающий сигнал на вход разрешения записи регистра 4, например, с помощью элемента НЕ, подключенного к этому входу), переводит мультиплексор 8 в режим передачи на адресный вход блока 2 выходного кода сумматора 7 и поступает на первый вход элемента И 13,

При этом выходной код сумматора равен нулю и на его выходе переноса присутствует единичный сигнал, поступающий через элемент ИЛИ 12 на второй вход элемента И 13, В результате в регистр 3 записан код из нулевой ячейки блока 2 оперативной памяти, т,е, код начального условия.

Перевод устройства в рабочий режим осуществляется подачей управляющего сигнала с входа 19 на установочный вход триггера 14, переводя его в единичное состояние. Выходной сигнал триггера 14 разрешает работу генератора 9 и прекращает блокировать работу счетчика 6 и триггера 15,

На выходе генератора 9 начинают формироваться импульсы, поступакяцие на счетный вход счетчика 6 и через элемент ИЛИ 11 на вход запуска преобразователя 1 ,

В счетчике 6 формируется линейно изменяющийся код развертки, поступающий на первьй информационный вход мультиплексора 8 и вход второго слагаемого сумматора 7,

Преобразователь 1 преобразует входной аналоговый сигнал в цифровой код, поступающий на информационньш вход блока 2 оперативной памяти.

По переднему фронту импульса окончания преобразования выполняется запись полученного цифрового кода в блок 2 оперативной памяти по адресу, соответствующему текущему коду счетчика 6, поступающему на адресный

вход блока 2 через мультиплексор 8.

)

По заднему фронту импульса окончания преобразования блок 2 переходит в режим чтения данных из ячейки, адрес которой определяется текущим состоянием кода сумматора 7,

При этом импульсом с выхода формирователя 10 осуществляется блокировка изменения кода задержки N zr , поступающего с входа 17 на информа.

ционным вход 4 на время чтения данных и- бпокл оперативной памяти.

Импульс с выхода формирователя 10 подключает к адресному входу блока 2 через мультиплексор 8 кодовый выход сумматора 7 и, кроме этого, поступает на первьй вход элемента И 13.

В том случае, когда блок 2 оперативной памяти заполнен не полностью, работа устройства зависит от знака разности кодов текущего состояния счетчика 6 и кода задержки регистра 4. Если эта разность положительна, т.е. выходной код сумматора 7 указывает адрес ячейки блока 2 в которую занесены данные о воспроизводимой функции, то на выходе переноса сумматора 7 формируется единичный сигнал. Этот сигнал через элемент ИЛИ 17. поступает на элемент И 13 и открывает его для прохождения импульса с выхода формирователя 10 на вход разрешения, записи данных в регистр 3. В последний заносится из блока 2 ко функции, сдвинутый по временной шкале относительно текущего момечта времени на величину Т (N + ) tn,

где tn - период следования импульсов на выходе генератора 9.

Если текущее значение кода задержки больше текущего значения кода счетчика 6, то на выходе переноса сумматора 7 формируется нулевой сигнал, запирающий элемент И 13. Считывание очередной ячейки блока 2 в регистр 3 не производится и на выходе устройства сохраняется предшествующее значение запаздывающей функции.

В момент времени, когда происходит полное заполнение блока 2 оперативной памяти последовательностью дискретных отсчетов входной аналоговой функции, на выходе переноса счетчика 6 появляется импульс, устанавливающий триггер 15 в единичное состояние. Выходной сигнал триггера 15 через элемент ИЛИ 12 начинает подавать на элемент И 13 постоянный сигнал, разрешающий прохождение выходных импульсов формирователя 10 на регистр 3. В результате в регистр 3 начинает заноситься информация о запа дывающих значениях функции в полном динамическом диапазоне изменения теS 4 9 4

кущего времени задержки, определяемого емкостью счетчика 6.

Дальнейшая работа устройства осуществляется аналогично описанному, однако новые дискретные отсчеты входной функции записываются в блок 2 по адресам, определяемым повторным формированием кода развертки на выходе счетчика 6.

m

Таким образом, устройство позволяет повысить динамическую точность формирования запаздывающих функций за счет обеспечения режима расшире- /5 ния динамического диапазона задержки по мере накопления данных в предыстории процесса (дискретных отсчетов входной функции )i3 блоке 2 оперативной памяти.

20

Формула изобретения

Устройство для воспроизведения запаздывающих функций, содержащее 25 первьш регистр, выход которого соединен с цифровым входом цифроанало- гого преобразователя, выход которого является выходом устройства, аналого- цифровой преобразов.атель, подключен- 30 ный аналоговым входом к входу зада-, ния начальных условий устройства, цифровым выходом к информационному входу блока оперативной памяти, а выходом сигнала окончания преобразо- г вания подключен к входу формирователя импульсов, адресный вход блока оперативной памяти соединен с выходом адресного мультиплексора, подключенного управляющим входом к пер- 0 вому входу элемента И, а первым ин- формационным входом - к выходу счетчика, вход обнуления которого соединен с первым выходом первого триггера, входом запуска генератора такто- S вых импульсов и входом сброса второго триггера, причем установки и сброса первого триггера подключены к входам запуска и останова устройства, отличающееся 0 тем, что, с целью повьшгения динамической точности воспроизведения функций переменного запаздывания, в него введены сумматор, два элемента ИЛИ и второй регистр, соединенный с информационным входом с входом задания кода задержки функции устройства, входом обнуления соединенный с входом управления установкой начальных условий устройства и первым вхо1/М

дом первого элемента ИЛИ,подключеннно- го вторым входом к выходу генератора тактовых импульсов и счетномувходу счетчика, соединенного выходом переноса с установочным входом второго триггера, подключенного прямым выходом к первому входу второго элемента ИЛИ, соединенного вторым входом с,выходом переноса сумматора, а выходом подключенного к второму входу элемента И, выход которого подключен к входу разрешения записи первого регистра, соединенного информационным входом с выходом блока оперативной памяти, выход первого элемента ИЛИ подключен к входу

128

Редактор И.Николайчук

Составитель Н.Зайцев

Техред В. Кадар Корректор И.Муска

пяш п;дп;;с;о;

ьниипи Государственного комитета СССР

по делам изобретений и открытий 3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятйёГгГужгородГулГпр ёктна ГА

1/М

о- н1285493

запуска аналого-цифрового преобразователя, входы первого и второго слагаемьк сумматора соединены соответственно с инверсньи выходом ВТОРОГО регистра и выходом счетчика выход сумматора соединен с вторьи информационным входом адресного мультиплексора, выход сигнала окончания преобразования аналого-цифрового преобразователя подключен к входу управления режимом Чтение запись блока оперативной памяти выход формирователя импульсов подклю- чен к первому входу элемента И и входу запрета записи второго регист- рэ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1249546A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Формирователь сложной функции | 1985 |

|

SU1287135A1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение, в частности, в моделирующих гибридных вычислительных системах. Цель изобретения - повышение динамической точности воспроизведения функций переменного запаздывания. Поставленная цель достигается за счет введения сумматора, двух элементов ИЛИ, второго регистра и соответствующих связей. Устройство позволяет повысить динамическую точность формирования запаздывающих функций за счет обеспечения режима расширения динамического диапазона задержки по мере накопления данных в предыстории процесса (дискретных отсчетов входной функции) в блоке оперативной памяти. 1 ил. (Л

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1157552A1 |

| Формирователь сложной функции | 1982 |

|

SU1107293A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-23—Публикация

1985-08-02—Подача