чика адреса памяти предыстории. Выход первого триггера подключен к входу запись-считывание блока памяти предыстории, а инверсный его выход - к входу запись-считывание блока основной памяти.

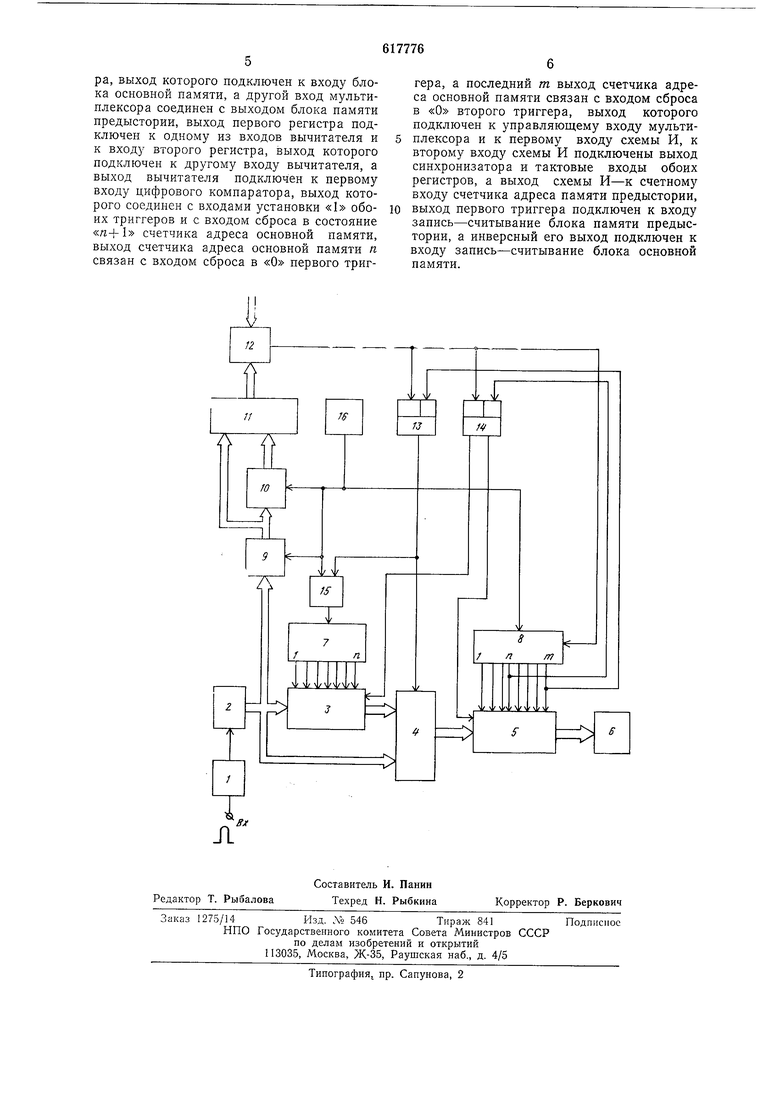

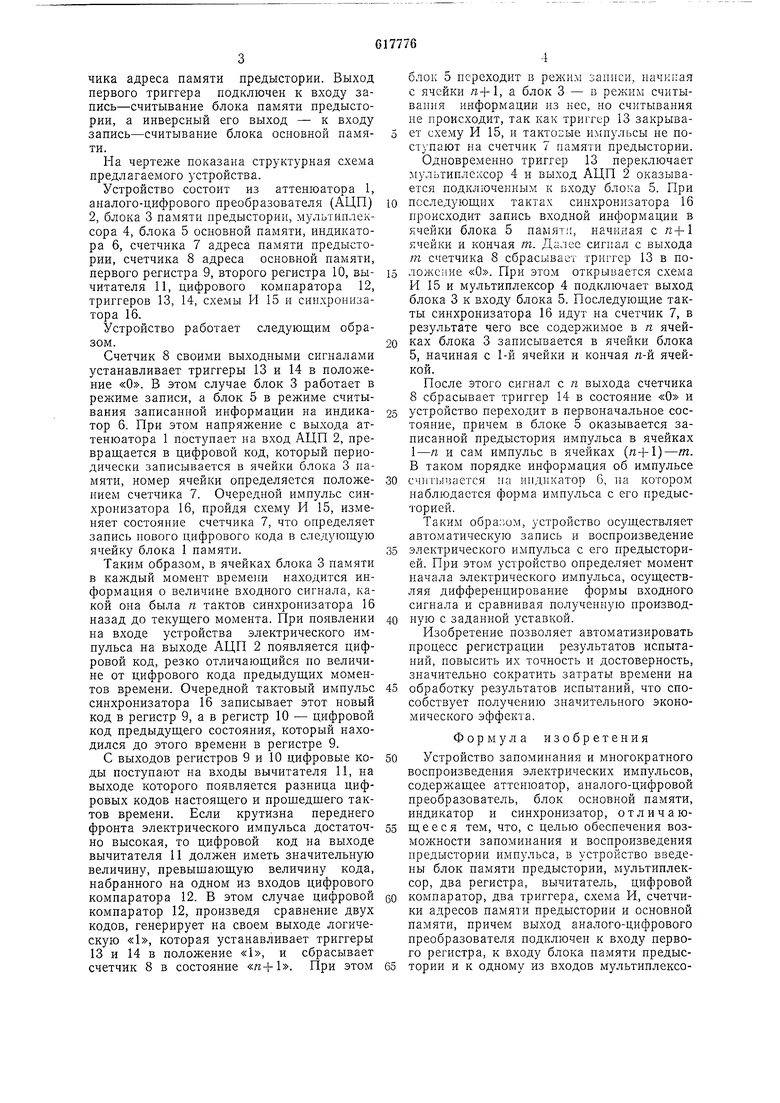

На чертеже показана структурная схема предлагаемого устройства.

Устройство состоит из аттенюатора 1, аналого-цифрового преобразователя (АЦП) 2, блока 3 памяти предыстории, мультиплексора 4, блока 5 основной памяти, индикатора 6, счетчика 7 адреса памяти предысторпи, счетчика 8 адреса основной памяти, первого регистра 9, второго регистра 10, вычитателя 11, цифрового компаратора 12, триггеров 13, 14, схемы PI 15 и синхронизатора 16.

Устройство работает следуюш,им образом.

Счетчик 8 своими выходными сигналами устанавливает триггеры 13 и 14 в положение «О. В этом случае блок 3 работает в режиме записи, а блок 5 в режиме считывания записанной информации на индикатор 6. При этом напряжение с выхода аттенюатора 1 поступает на вход АЦП 2, преврапдается в цифровой код, который периодически записывается в ячейки блока 3 памяти, номер ячейки определяется положением счетчика 7. Очередной импульс синхронизатора 16, пройдя схему И 15, изменяет состояние счетчика 7, что определяет запись нового цифрового кода в следующую ячейку блока 1 памяти.

Таким образом, в ячейках блока 3 памяти в каждый момент времени находится информация о величине входного сигнала, какой она была л тактов синхронизатора 16 назад до текущего момента. При появлении на входе устройства электрического импульса на выходе АЦП 2 появляется цифровой код, резко отличающийся по величине от цифрового кода предыдущих моментов времени. Очередной тактовый импульс синхронизатора 16 записывает этот новый код в регистр 9, а в регистр 10 - цифровой код предыдущего состояния, который находился до этого времени в регистре 9.

С выходов регистров 9 и 10 цифровые коды поступают на входы вычитателя И, на выходе которого появляется разница цифровых кодов настоящего и прощедщего тактов времени. Если крутизна переднего фронта электрического импульса достаточно высокая, то цифровой код на выходе вычитателя 11 должен иметь значительную величину, превыщающую величину кода, набранного на одном из входов цифрового компаратора 12. В этом случае цифровой компаратор 12, произведя сравнение двух кодов, генерирует на своем выходе логическую «1, которая устанавливает триггеры 13 и 14 в положение «I, и сбрасывает счетчик 8 в состояние «п+1. При этом

блок 5 переходит в режим записи, начиная с ячейки п+1, а блок 3 - в режим считывания информации нз нее, но считывания не происходит, так как триггер 13 закрывает схему И 15, и тактогые импульсы не поступают на счетчик 7 памяти предыстории. Одновременно триггер 13 переключает мультиплексор 4 и выход АЦП 2 оказывается подключенным к входу блока 5. Прп

последующих тактах синхронизатора 16 происходит запись входной информации в ячейки блока 5 памяти, начиная с ячейки и кончая т. Далее сигнал с выхода т счетчика 8 сбрасывает триггер 13 в положсиие «О. При этом открывается схема И 15 и мультиплексор 4 подключает выход блока 3 к входу блока 5. Последующие такты синхронизатора 16 идут на счетчик 7, в результате чего все содержимое в я ячейках блока 3 записывается в ячейки блока 5, начиная с 1-й ячейки и кончая л-й ячейкой.

После этого сигнал с л выхода счетчика 8 сбрасывает триггер 14 в состояние «О и

устройство переходит в первоначальное состояние, причем в блоке 5 оказывается записанной предыстория импульса в ячейках 1-л и сам импульс в ячейках (л-f-l)-т. В таком порядке информация об импульсе

считывается па ипдикатор 6, на котором наблюдается форма импульса с его предысторией.

Таким обра:юм, устройство осуществляет автоматическую запись и воспроизведение

электрического импульса с его предысторией. При этом устройство определяет момент начала электрического импульса, осуществляя дифференцирование формы входного сигнала и сравнивая полученную производпую с заданной уставкой.

Изобретение позволяет автоматизировать процесс регистрации результатов испытапий, повысить их точность и достоверность, значительно сократить затраты времени на

обработку результатов испытаний, что способствует получению значительного экономического эффекта.

Формула изобретения

Устройство запоминания и многократного воспроизведепия электрических импульсов, содержащее аттенюатор, аналого-цифровой преобразователь, блок основной памяти, индикатор и синхронизатор, отличающееся тем, что, с целью обеспечения возможности запоминания и воспроизведения предыстории импульса, в устройство введены блок памяти предыстории, мультиплексор, два регистра, вычитатель, цифровой

компаратор, два триггера, схема И, счетчики адресов памяти предыстории и основной памяти, причем выход аналого-цифрового преобразователя подключен к входу первого регистра, к входу блока памяти предыстории и к одному из входов мультиплексо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового измерения,запоминания и воспроизведения дискретных значений однократного сигнала | 1983 |

|

SU1117667A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1092567A1 |

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

| Устройство для цифрового измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса | 1980 |

|

SU868790A1 |

| Устройство для индикации однократных сигналов | 1984 |

|

SU1275519A1 |

| Устройство для испытания изделий на случайные широкополосные вибрации | 1985 |

|

SU1298571A2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| Матричный осциллограф | 1981 |

|

SU1018021A1 |

| Устройство для передачи телеметрической информации | 1984 |

|

SU1231529A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

Авторы

Даты

1978-07-30—Публикация

1976-10-12—Подача