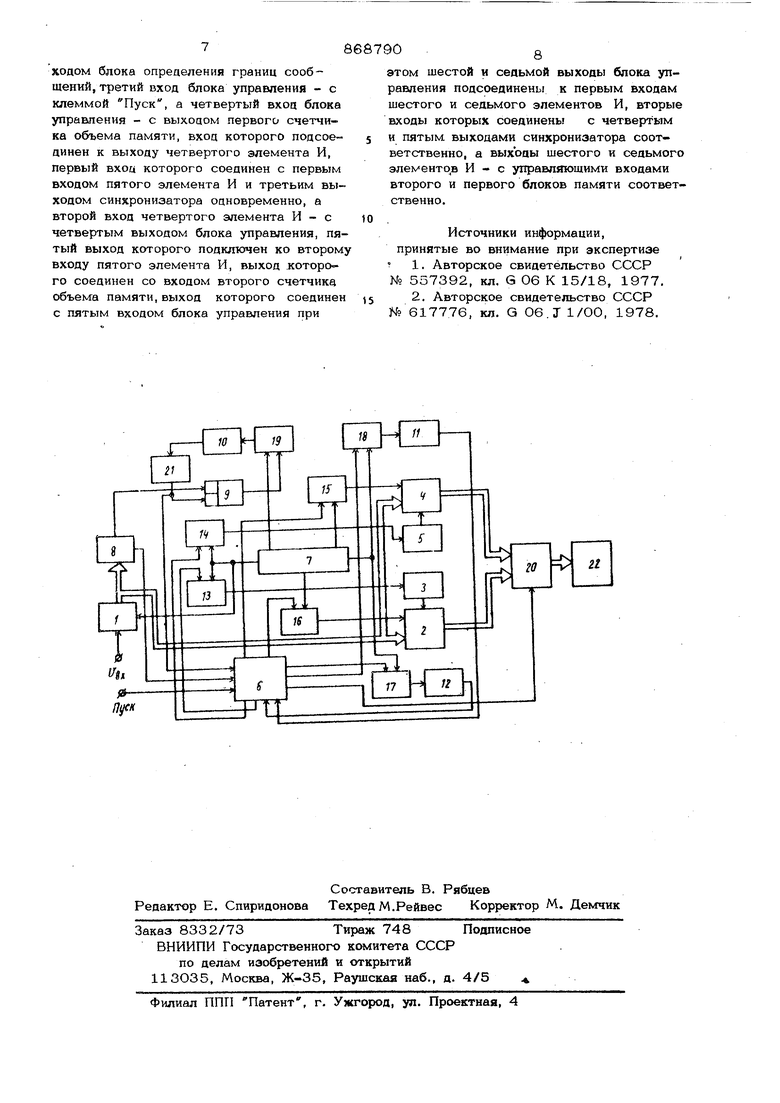

(54) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ИЗМЕРЕНИЯ, ЗЛПОМКИАЬ ИЯ И МНОГОКРАТНОГО ВОСПРОИЗВЕДЕНИЯ ДИСКРЕТНЫХ ЗНАЧЕНИЙ ОДНОКРАТНОГО ПРОЦЕССА . Изобретение относится к измерительной технике, а именно к устройствам записи и воспроизведения однократных процессов. Известно устройство для икфрового из мерения и регистрации дискр€ тных значений однократного процесса Однако оно не позволяет осушес-твить запись и воспроизведение предыстории однократного процесса. Наиболее близким к предлагаемому является устройство запоминания и многократного воспроизведения электрических импульсов, содержац;ее аттетоатор, анало го-цифровой преобразователь, блок основной памяти, индикатор, синхронизатор, блок памяти предыстории, мультиплексор, два регистра, вычитатель, цифровой компаратор, два триггера, схему И, счетчики адресов памяти предыстории и основной памяти 2 3i Это устройство позволяет осушествпят запись электрического импульса и его многократное воспроизвеление, а также обеспечивает запись и воспроизведение предыстории исследуемого импульса. Однако данное устройство обладает низкой разрешающей способностью. При записи и воспроизведении одного стенала с предысторией олительность цикла равна: (где ы - объем основной памяти; у, - объем памяти предыстории; -Ь - период следо ания тактовых иьшульсов. Цель изобретения - повышение разрешающей способности. Поставленная цель достигается тем, что в устройство для цифрового измерения, запоминания и многократного восщюиэведеа.ш дискретных значений однократного процесса, содержав .ее аналого-циф |Овой преобразователь, первый и второй блоки памяти, индикатор, синхронизатор, мультиплексор, блок определения границ сообщения, первый и второй счетчики адре сов, гфкчем выход аналого-цифрового прв38образователя подкггючеп ко входу блокаопределения границ сообщений и к первому входу первого блока памяти одновре менно, а выход последне1Ч) соединен с пер вым входом мультиплексора, выход которого подсоединен ко входу индикатора, npxi этом выход блока определения границ сообщений соединен с первым входом трш гера, а вторые входь; первого и второго блока памяти - с выходами первого и второго счетчиков адресов соответстьенно, в него введены семь элементов И, счетчик объема сигнала, первый и второй счетчики объема памяти, формирователь импульсов, и блок управления, причем выход аналого-цифрового преобразователя соединен с первым входом второго блока памяти, выход которого подсоединен ко второму вхопу мультиплексора, управляющий вход которого соединен с первым выходом блока управления, второй и третий выход которого подключены к первым входам первого и второго элементов И соответственно, вторые входы которых объединены между собой и соединены с первым выходом блока синхронизации И с управляющим входом аналого-цифрового преобразователя одновременно, а выходы первого и второго элементов И подключены ко входам первого и второг о счетчиков адреса соот ветственно, кроме того второй выход синхронизатора подсоединен к первому входу третьего элемента И, втсфой вход которого соединен с ф-выходом триггера, а выход - со входом счетчика объема сигнала, выход которого через формирователь подключен -ко второму входу триггера и первому входу блока упраш1ения одновременно, причем второй вход блока управления соединен с управляющим выходом блока определения границ сообщений, третий вход блока управления - с клеммой Пуск, а четвертый вход блока управления - с выходом первого счетчика объема памяти, вход которого подсоединен к выходу четвертого элемента И, первый вход которого соединен с первым входом пятого элемента И и третьим выходом синхронизатора одновременно, а второй вход четвертого элемента И - с четвертым выходом блока управления, пятый выход которого подключен ко втором входу пятого элемента И, выход которого соединен со входом второго счетчика объ ма , выход которого соединен с пя тым входом блока управления, при этом шестой и седьмой выходы блока управлен подсоединены к первым входам шестого и седьмого элементов И, вторые входы 0 которых соединены с четвертым и пятым выходами синхронизатора соответственно, а выходы шестого и седьмого элементов И с управл5пошими входами второго и первого блоков памяти соответственно. На чертеже показана блок-схема устройства для цифрового измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса. Устройство содержит аналого-цифровой г эеобразователь 1, первый блок 2 памяти объемом hi , первый счетчик 3 адресов, второй блок 4 памяти объемом Hi , второй счетчик 5 адресов, блок 6 управления, синхронизатор 7, блок 8 определения границ сообщений, триггер 9, счетчик 10 объема сигнала, первый и второй счетчики 11 и 12 объема памяти, семь элементов И 13-19, мультиплексор 20, формирователь 21, индикатор 22. При этом клемма Вход соединена с аналого-цифровым преобразователем 1. Устройство работает следующим образом. По сигналу Пуск устанавливается исходное положение, при котором первый блок 2 памяти находится в режиме записи, а второй блок 4 памяти в режиме считывания. Через первый и второй элементы И 13 и 14 импульсы синхронизатора 7 поступают на входы первого и второго счетчиков адресов 3 и 5. Через седьмой элемент И 16 импульсы записи поступают на первый блок 2 памяти. Напряжение, поступающее на вход аналогоци4 ового преобразователя 1 превращается, в цифровой код который записывается в ячейки первого блока 2 памяти, а номер ячейки определяется положением первого счетчика 3 адресов. Очередной импульс синхронизатора 7, пройдя первый элемент И 13, изменяет состояние первого счетчика 3 адресов, что определяет запись одного цифрового кода в следующую ячейку первого блока 2 памяти. При записи всех ы ячеек первого блока 2 памяти, запись очередного Hi+l значения цифрового кода осуществляется снова в первую ячейку первого блока 2 памяти,ии-2 значение цифрового кода записывается во вторую ячейку и т.д. При появлении на входе устройства электрического импульса на выходе аналого-ци4 ового преобразователя 1 появляется ци4чзовой код, резко итличаюшийся по величине от ци(} ового кода предыдущих моментов времени. Блок и1ределения границ сообщений 8 вырабатьшает импульс, который переводит трнг- rep 9 из нулевого состояния в единичное С этого момента времени счетчик 10 объема сигнала отсчитывает щ- и следую щих значений цифрового кода, которые также записываются в ячейки первого блока 2 памяти. При этом и - объем памяти, записанной предыстории. После того, как счетчик 10 объема сигнала насчитает VKI- У импульсов, он устанавливается в нулевое состояние и одновременно формиро ватель 21 вырабатывает импульс, который устанавливает триггер 9 в нулевое состояние. По этому же импульсу блок 6 управления запрещает прохождение импуль сов записи через седьмой элемент И 16 на первый блок 2 памяти и подключает индикатор 22 к выходу первого блока 2 памяти через мультиплексор 20. Первый блок 2 памяти переходит в режим считывания записанной информаш5и на индикатор 22. Пусть запись значений цифрового кода в лэрвый блок 2 памяти закончилась на V ячейке. Тогдч считывание информации начинается с k +1 ячейки, причем в ячейках clt+l по К+ И записана предыстория сигнала, а в ячейках с1(+И+1 по К записан сам импульс. В режиме считывания информации с первого блока 2 памяти, блок управления б разрешает прохождение импульсов синхронизатора 7 че рез пятый элемент И 17 на вход второго счетчика 12 объема памяти. Число состоя ний этого счетчика равно Vvi . Поэтому в режиме считывания О состояние этого счетчика будет соответствовать 1( ячейке первого блока 2 памяти. По окончанию действия электрического импульса на входе аналого-цифрового преобразователя 1, блок 8 определения границ сообщений вырабатывает импульс, поступающий на блок б управления. По этому импульсу блок 6 управления разрещает прохождение импульсов записи с синхронизатора 7 через шестой элемент И 15 на второй блок 4 памяти. Второй блок 4 памяти переходит в режим записи информации. Запись информации во второй блок 4 памяти происходит аналогично записи информации в первый блок 2 памяти Таким образом предлагаемое устройство позволяет записывать предысторию электрического импульса, а также импульс сразу после окончания предыдущего им пульса, т.е. длительность одного цикла записи - воспроизведения составит для заявляемого устройства , в то время как для известного - (2hi+M)-fc . Сравнивая две длительности, можно отметить, что в данном устройстве разрешащая способность выше в .„2уп раз. Формула изобретения Устройство для цифрового измерения, запоминания и многократного воспроизведения дискретных значений однократного процесса, содержащее аналого-цифровой преобразователь, первый и второй блоки памяти, индикатор, синхронизатор, мультиплексор, блок определения границ сообщений, первый и второй счетчики адресов, причем выход аналого-цифрового преобразователя подключен ко входу блока определения границ сообщений и к первому входу первого блока памяти одновременно а выход последнего соединен с первым входом мультиплексора, выход которого подсоединен ко входу индикатора, при этом выход блока определения границ сообщений соединен: с первым входом триггера, а вторые входы первого и второго блока памяти, с выходами первого и второго счетчиков .выходами первого и второго счетчиков адресов соответственно, отличающееся тем, что, с целью повышения разрешающей способности в н§го в зецены семь элементов И, счетчик объема сигнала, первый и второй счетчики объема памяти, формирователь импульсов и блок управления, причем выход аналого-цифрового преобразователя соединен с первым входом второго блока памяти, выход которого подсоединен ко второму входу мультиплексора, управляющий вход которого соединен с первым выходом блока управления, второй и третий выход которого подключены к первым входам первого и второго элементов И, соответственно, вторые входы которых объединены между собой и соединены с первым выходом блока синхронизации и с управляющим входом аналого-цифрового преобразователя одновременно, а выходы первого и второго элементов И подключены ко входам первого и второго счетчиков адреса соответственно, кроме того второ:1 выход синхронизатора подсоединен к первому входу третьего элемента И, второй вход KOTOj-oro соединен с О-выходом триггера, а выход - со входом счетчика объема сигнала, выход которого через формирователь подключен ко второму входу триггера и первому входу блока управления одновременно, причем, второй вхот блока управления соединен с управляющим выходом блока определения границ сообщений, третий вход блока управления - с клеммой Пуск, а четвертый вход блока управления - с выходом первого счетчика объема памяти, вход которого подсоединен к выходу четвертого элемента И, первый вход которого соединен с первым входом пятого элемента И и третьим выходом синхронизатора одновременно, а второй вход четвертого элемента И - с четвертым выходом блока управления, пятый выход которого подключен ко втором входу пятого элемента И, выход .которого соединен со входом второго счетчика объема памяти, выход которого соединен с пятым входом блока управления при

ЭТОМ шестой и седьмой выходы блока управления подсоединены к первым входам шестого и седьмого элементов И, вторые входы которых соединены с четвертым и пятым выходами синхронизатора соответственно, а выходы шестого и седьмого элементов И - с управляющими входами второго и первого блоков памяти соответственно.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 557392, кл. G 06 К 15/18, 1977.

2. Авторское свидетельство СССР № 617776, кл. Q Об. J 1/ОО, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового измерения,запоминания и воспроизведения дискретных значений однократного сигнала | 1983 |

|

SU1117667A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1092567A1 |

| Устройство запоминания и многократного воспроизведения электрических импульсов | 1976 |

|

SU617776A1 |

| Устройство для воспроизведения запаздывающих функций | 1985 |

|

SU1285493A1 |

| Транспониатор сигналов речевой информации | 1986 |

|

SU1372352A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| ОПТИЧЕСКИЙ ДАЛЬНОМЕР | 1999 |

|

RU2155322C1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для регистрации аналоговых сигналов | 1980 |

|

SU911577A1 |

Авторы

Даты

1981-09-30—Публикация

1980-01-28—Подача