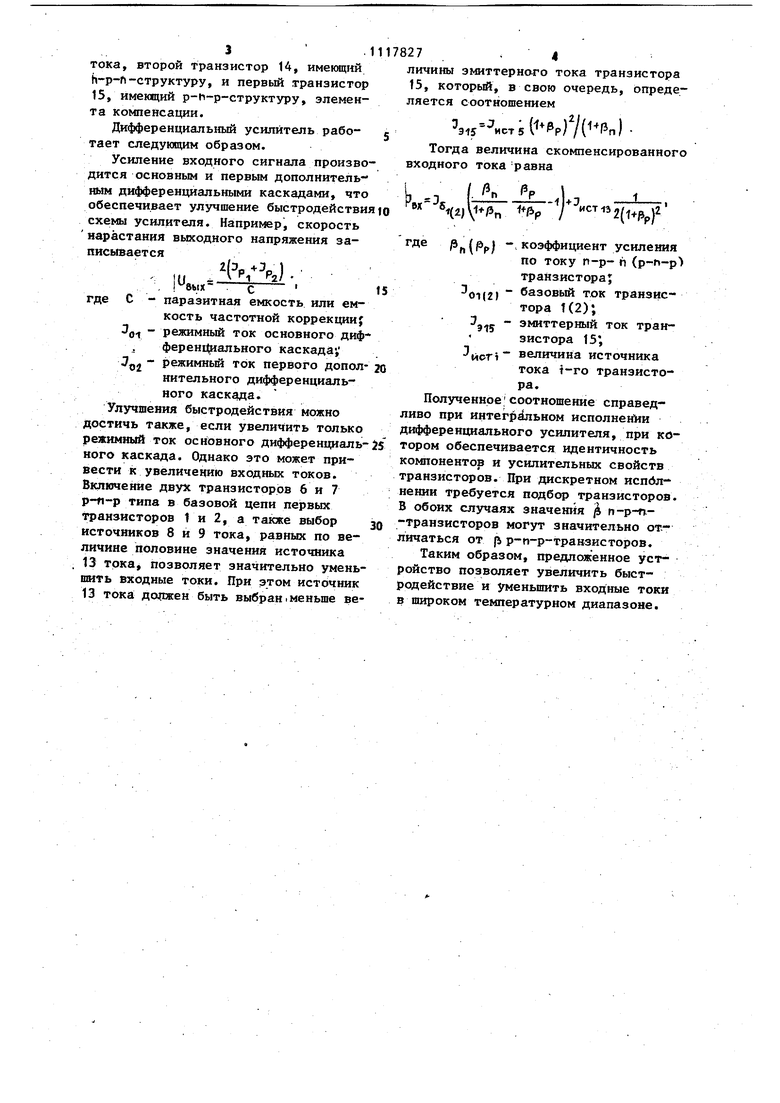

f Изобретение относится к радиотех нике и может быть использовано в ка честве входных каскадов в операционных усилителях и других аналоговых схемах. Известен дифференциальный усилитель, содержащий основной дифференци альный каскад, каждое плечо которог выполнено в виде последовательно со диненньк относительно источника пита Нин первого транзистора, включенног по -схеме с общим коллектором, и второго транзистора, включенного по сх ме с общей базой с источником тока в общей цепи баз f 1 J. Одкак6 данный дифференциальный усилитель обладает недостаточно хорошими динамическими параметрами при небольших значениях режимных токов. Наиболее близким по технической сущности к предлагаемому является дифференциальный усилитель, содержащий основной дифференциальньй каскад, каждое плечо которого выполнено в виде последовательно соединенных отнбсутельно источника питания первого транзистора, имеющего п-р-п-структуру, включенного по схеме с общим коллектором, и второго транзис тора, имеющего р-п-р-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов включен первый источник тока L2 j. Известный дифференциальный усилитель обладает недостаточно высоким быстродействием и наличием нескомпен сированных входных токов. Целью изобретения является увеличение быстродействия и уменьшение входных токов. Цель достигается тем, что в дифференциальный усилитель, содержащий основной дифференциальный каскад, каждое плечо которого выполнено в виде последовательно соединенных относительно источника питания первого транзистора, имекицего fi-p-n-структуру, включенного по схеме с общим кол лектором, и второго транзистора, имеющего р-г -р-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объе(динены, а в общей цепи без вторьк транзисторов включен первый источник тока, введены первый дополнительньй дифференциальный каскад, вьшолненный 7 ,2 на транзисторах, имеющих р-п-р-структуру, включенных по схеме с общим 1 коллектором, с вторым и третьим источниками тока в соответствующих цепях эмиттеров, второй дополнительный дифференциальный каскад, выполненный на транзисторах, имеющих p-fi-p-структуру, с четвертым источником тока в общей эмиттерной цепи, элемент компенсации, выполненный на первом транзисторе, имеющем р-п-р-структуру, с пятым источником тока в цепи эмиттера и втором транзисторе, имеющем h-p-h-структуру, коллектор которого соединен с соответствукицей шиной источника питания, эмиттер - с точкой соединения коллекторов первых транзисторов основного дифференциального каскада, базы первого и второго транзисторов элемента компенсации объединены, при этом базы транзисторов первого дополнительного дифференциального каскада подключены соответ-. ственно к базам первых транзисторов основного дифференциального каскада, коллекторы объединены и подключены к соответствующей шине источника питания и к коллектору первого транзистора элемента компенсации, эмиттер которого соединен с управляющим входом четвертого источника тока, а базы транзисторов второго дополнительного дифференциального каскада подключены к соответствукйцим эмиттерам транзисторов первого дополнительного дифференциального каскада, коллекторы - к соответствующим эмиттерам или коллекторам вторых транзисторов основного дифференциального каскада. На чертеже представлена принципиальная электрическая схема предложенного дифференциального усилителя. Дифференциальный усилитель содержит первые транзисторы 1 и 2, имеющие tt-p-t)-структуру, включенные по схеме с общим коллектором, вторые транзисторы 3 и 4 основного дифференциального каскада, имекяцие р-и-р-структуру, включенные по схеме с общей базой, первый источник 5 тока, транзисторы 6 и 7 первого дополнительного дифференциального каскада, имекнцие p-lt-p-структуру, включенные по схеме с общим коллектором, второй источник 8 тока, третий источник 9 тока,транзисторы 10 и 11 второго дополнительного дифференциального каскада, имекяцие р-л-р-структ.уру, четвертый источник 12 тока, пятый источник 13 тока, второй транзистор 14, имеющий Ь-р-Л-структуру, и первый транзистор 15, имеющий p-h-p-структуру, элемента ко шенсации. Дифференциальный усилитель работает следующим образом. Усиление входного сигнала произво дится основным и первым дополнительным дифференциальными каскадами, что обеспечивает улучшение быстродействи схемы усилителя. Например, скорость нарастания выходного напряжения записывается.Р.) . вых с С - паразитная емкость или емкость частотной коррекции; 30 - режимный ток основного диф , ферени ального каскад а i режимный ток первого допол нительного дифференциального каскада. Улучшения быстродействия можно достичь также, если увеличить только режимный ток основного дифференциапь ного каскада. Однако это может привести к увеличению входных токов. Включение двух транзисторов 6 и 7 p-fi-p типа в базовой цепи первых транзисторов 1 и 2, а также выбор источников 8 и 9 тока, равных по величине половине значения источника 13 тока, позволяет значительно умень шить входные токи. При этом источник 13 тока должен быть выбран.меньше ве личины эмиттернаго тока транзистора 15, которьй, в свою очередь, определяется соотношением )) J 315 ист 5 Тогда величина скомпенсированного входного токаравна (,l , +й / 2{t.pp)2 п(Рр) -. коэффициент усиления по току п-р- 11 (p-h-p) транзистора; базовый ток транзистора 1(2); эмиттерный ток транзистора 15; величина источника тока f-ro транзистора. Полученноесоотношение справедливо при интегр ьном исполне1{Ии дифференциального усилителя, при котором обеспечивается идентичность компонентов и усилительных свойств транзисторов. При дискретном испблнеш1и требуется подбор транзисторов. В обоих случаях значешЫ п-р-п-транзисторов могут значительно отличаться от р р-п-р-транзисторов. Таким образом, предложенное устройство позволяет увеличить быстродействие и уменьшить входные токк в широком температурном диапазоне.

..-iMrfV..

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный усилитель | 1984 |

|

SU1202025A1 |

| Операционный усилитель | 1986 |

|

SU1319245A1 |

| Дифференциальный усилитель | 1983 |

|

SU1138922A1 |

| Дифференциальный усилитель | 1978 |

|

SU1103347A1 |

| Дифференциальный усилитель | 1984 |

|

SU1218446A1 |

| Дифференциальный усилитель | 1982 |

|

SU1084964A1 |

| Усилитель с компенсацией входного тока | 1985 |

|

SU1218445A1 |

| Усилитель мощности | 1983 |

|

SU1123092A1 |

| Повторитель | 1979 |

|

SU785952A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2319290C1 |

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий основной дифференциальный каскад, каждое плечо которого вьшолнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего h-p-n-структуру, включенного по схеме с общим коллектором, и второго транзистора, имеющего p-f-p-структуру, включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов включен первый источник тока, о т л и ч а ю щ и и с я тем, что, с целью увеличения быстродействия и уменьшения входных токов, в него введены первый дополнительный дифференциальньй каскад, выполненный на транзисторах, имеющих р-ц-р-структзфу, включенных по схеме с общим коллектором, с вторым и третьим источниками тока в соответствуЮ1ЦИХ цепях эмиттеров, второй дополнительный дифференциальный каскад, вы- полненйьй на транзисторах, имеющих р-п-р-структуру, с четвертым источником тока в общей эмиттерной цепи, элемент компенсации, выполненный на . первом транзисторе, имекщем р-п-р-структуру, с пятым источником тока в цепи эмиттера и втором транзисторе, имеющем п-р-п-структуру, коллектор которого соединен с соответствующей шиной источника питания, эмиттерс точкой соединения коллекторов первых транзисторов основного дифференциального каскада, базы первого и второго транзисторов элемента компенсации объединены, при этом базы тран(Л зисторов первого дополнительного дифференциального каскада подключены соответственно к. базам первых транзисторов основного дифференциального каскада, коллекторы объединены и подключены к соответствующей шине источника питания и к коллектору первого транзистора элемента компенсации, эмиттер которого соединен с управляющим входом четвертого источника тока, а базы транзисторов второго дополнительного дифференциального каскада подключены к соответствующим эмиттерам транзисторов первого дополнительного дифференциального каскада, коллекторы - к соответствующим эмит- . терам или коллекторам вторых транзисторов основного дифференциального каскада.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шило В.Л | |||

| Линейные интегральные схемы | |||

| М., Советское радио, 1979, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Проектирование аналоговых интегральных схем | |||

| М., Энергия | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

Авторы

Даты

1984-10-07—Публикация

1983-06-15—Подача