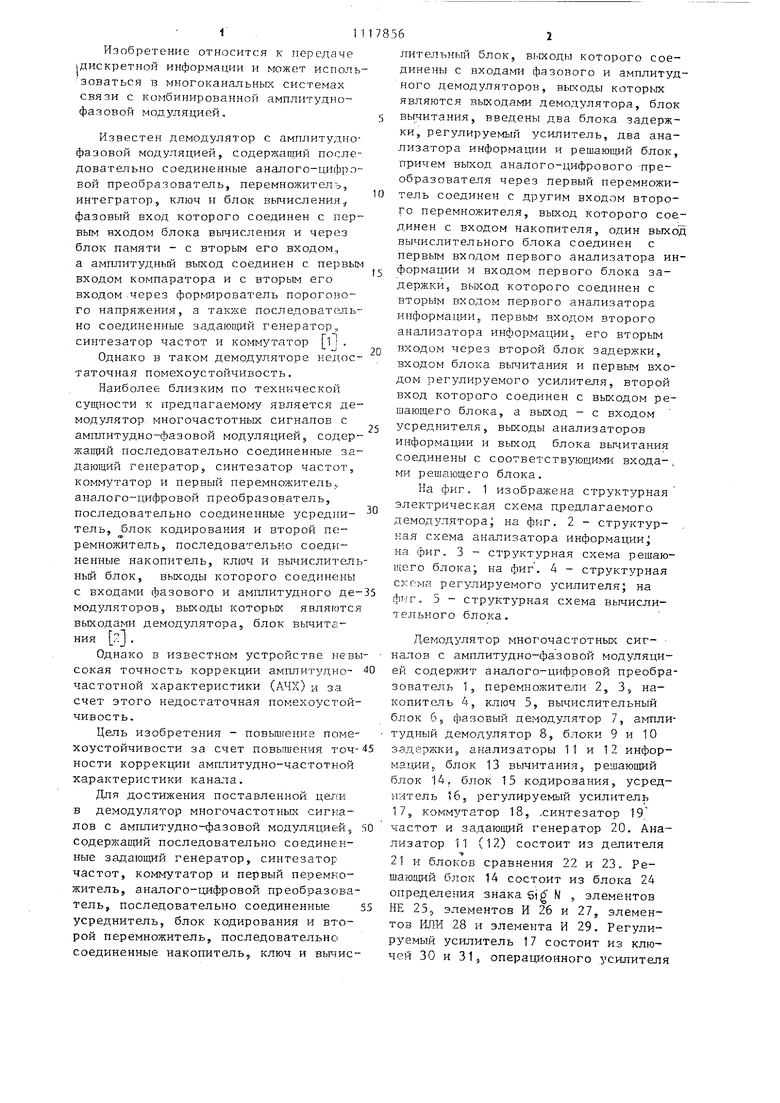

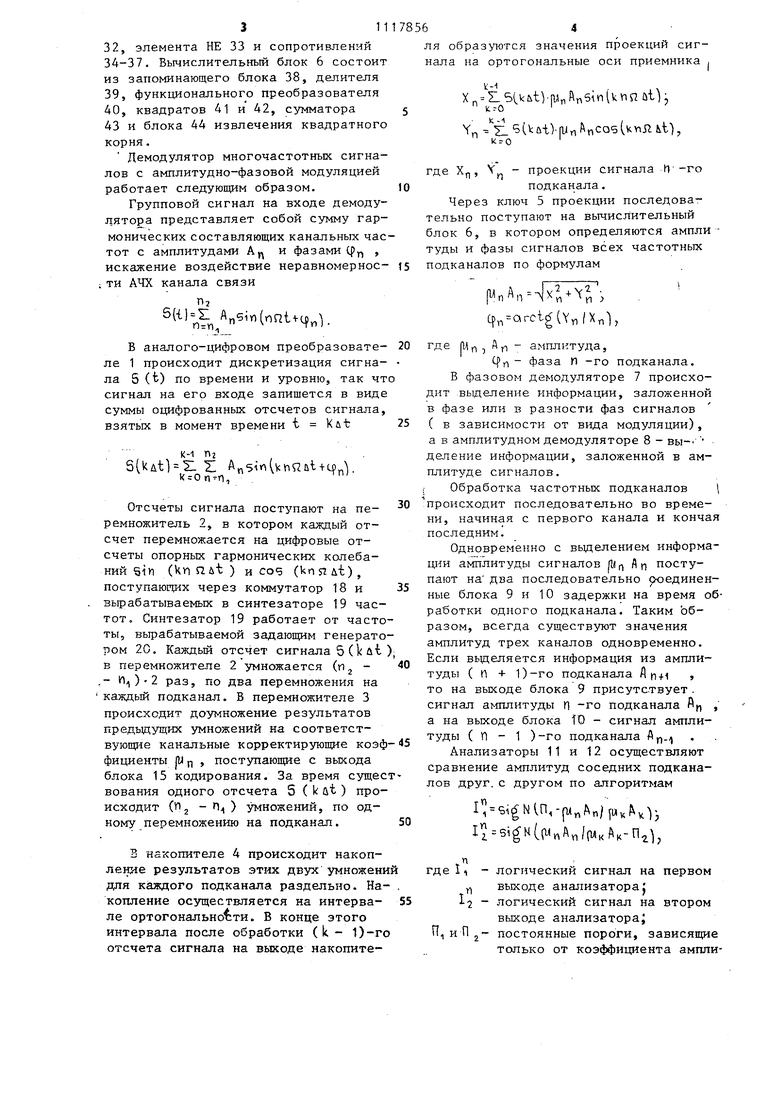

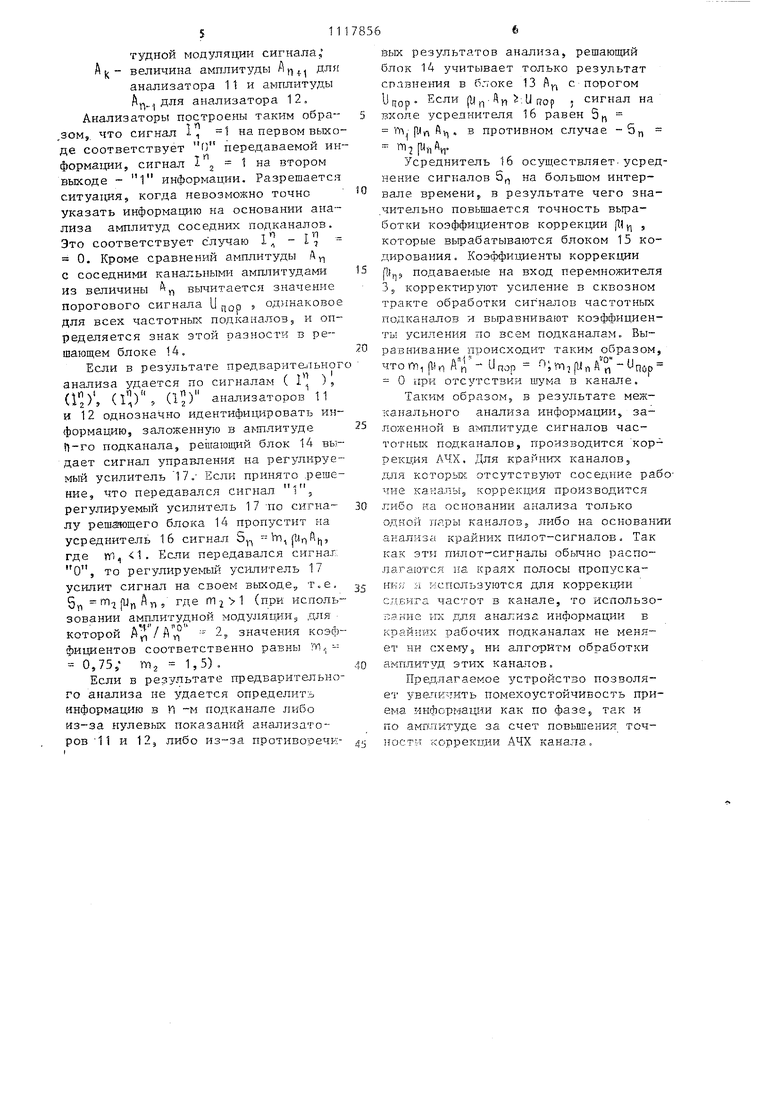

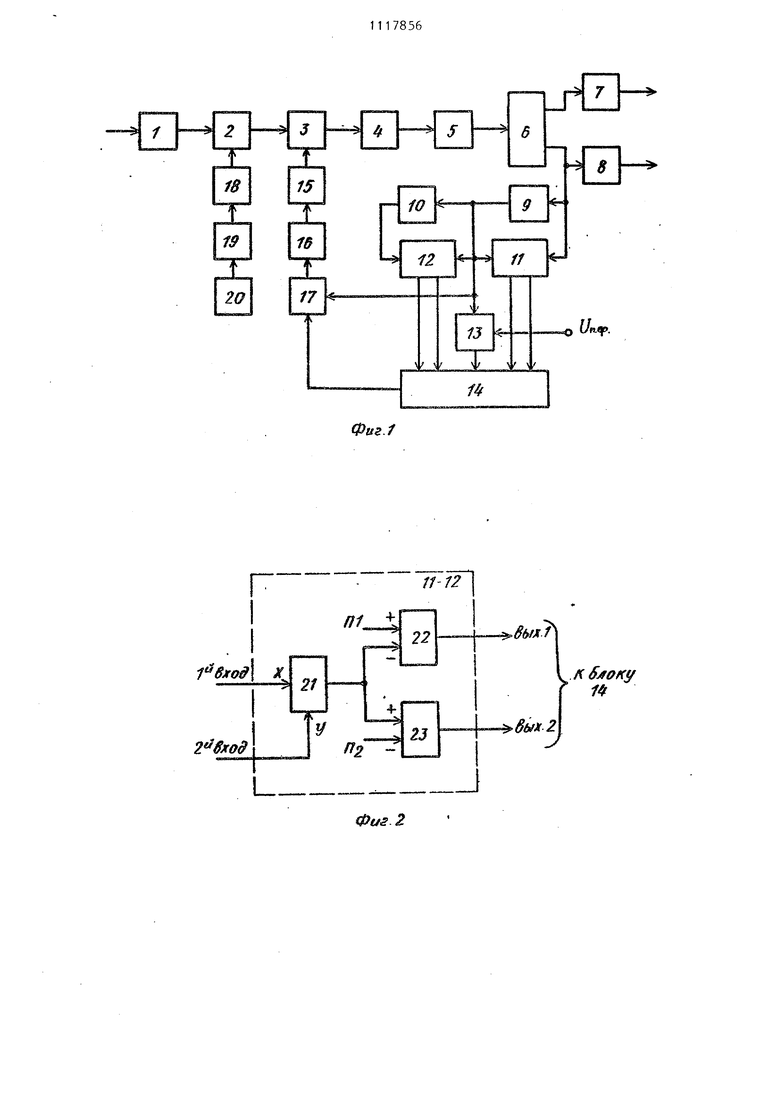

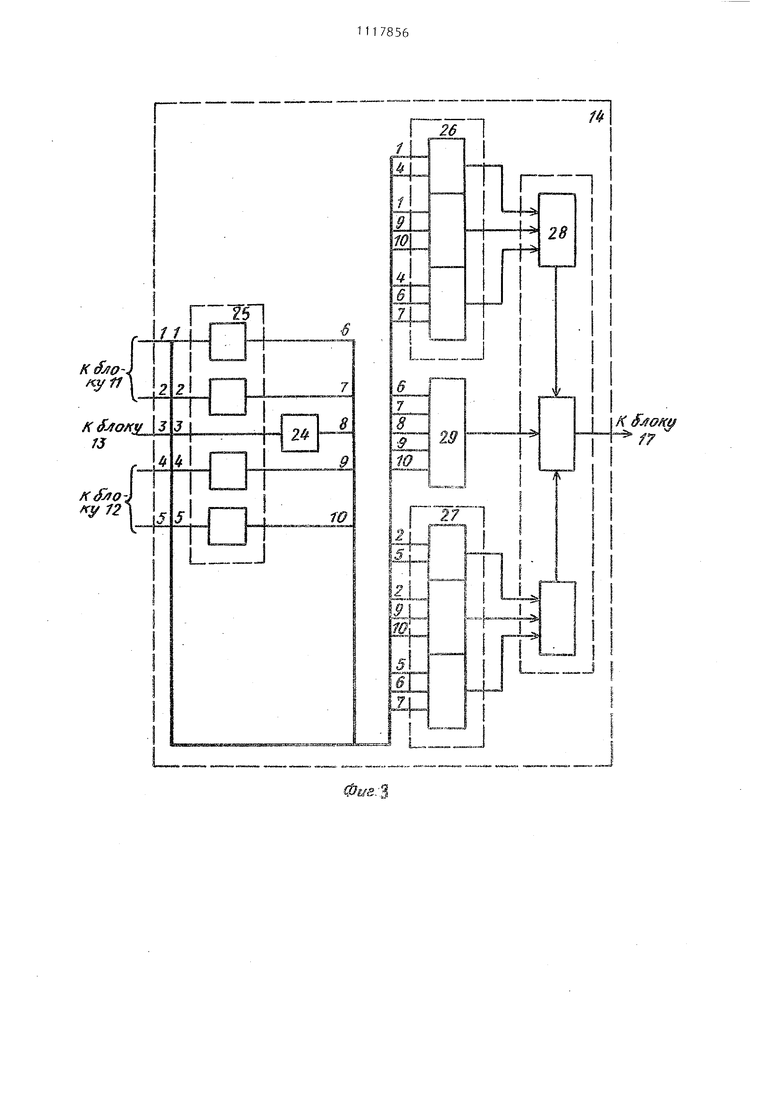

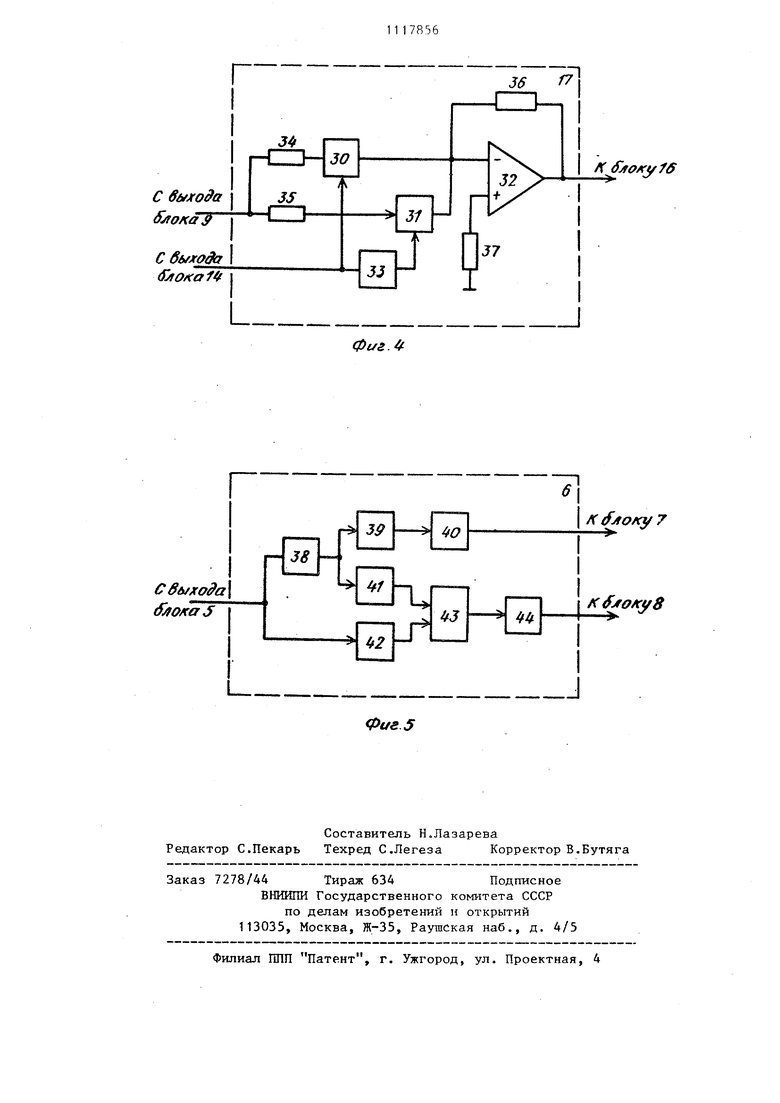

i1 Изобретение относится к передаче jдискретной информации и может исполь зеваться в тногоканальных системах связи с комбинированной амплитуднофазовой модуляцией. Известен демодулятор с амнлитуднофазовой модуляцией, содержащий последовательно соединенные аналого-цифровой преобразователь, перемножителъ, интеграторJ ключ и блок вычисления,, фазовый вход которого соединен с первым входом блока вычисления и через блок памяти - с вторым его входом,, а амплитудный выход соединен с первым входом компаратора и с вторьтм его входом .через формирователь порогового напряжения, а также последоват(2льно соединенные задаюищй генератор, синтезатор частот и коммутатор 1 I . Однако в таком демодуляторе недостаточная помехоустойчивость. Наиболее близким по технической сущности к предлагаемому является демодулятор многочастотных сигналов с амплитудно-фазовой модуляцией, содержа1ций последовательно соединенные задающий генератор, синтезатор частот, коммутатор и первый перемножитель,, аналого-цифровой преобразователь, последовательно соединенные усредни тель, блок кодирования и второй перемножитель, последовательно соединенные накопитель, ключ и вычислител ный блок, выходы которого соединены с входами фазового и ам1гпитудного демодуляторов, вь1ходы которых являются выходами демодулятора, блок вычитания 2 . Однако в известном устройстве гевы сокая точность коррекции амплитудночастотной характеристики (АЧХ) и за счет этого недостаточная помехоустой чивость. Цель изобретения - повьшгение помехоустойчивости за счет повьшения точ ности коррекции амплитудно-частотной характеристики канала. Лп достижения поставленной в демодулятор многочастотных сигналов с амплитудно-фазовой модуляцией, содержап ий последовательно соединенные задающий генератор, синтезатор частот, коммутатор и первый перемножитель, аналого-цифровой преобразова тель, последовательно соединенные усреднитель, блок кодирования и второй перемножительг последовательно соединенные накопитель ключ и вычис 62 лителъный блок, выходы которого соединены с входами фазового и амплитудного демодуляторов, выходы которых являются выходами демодулятора, блок вьгчитания, введены два блока задержки, регулируемый усилитель, два анализатора информации и решающий блок, причем выход аналого-цифрового преобразователя через первый перемножитель соединен с другим входом второго перемножителя, выход которого соединен с входом накопителя, один выход вычислительного блока соединен с первым входом первого анализатора информации и входом первого блока задержки, вьосод которого соединен с вторым входо{.з первого анализатора информации5 первым входом второго анализатора информации, его вторым входом через второй блок задержки, входом блока вьп-штания и первым входом регулируемого усилителя, второй вход которого соединен с вькодом решающего блока, а выход - с входом усреднителя, выходы анализаторов информации и выход блока вьгчитания соединены с соответствующими входами решающего блока. На фиг. 1 изобралсена структурная электрическая схема предлагаемого демодулятораJ на фиг. 2 - структурная схема анализатора информацииj на фиг. 3 - структурная схема решающего блока; на фиг. 4 - структурная схема регулируемого усилителя; на фиг. 5 - структурная схема вычислительного блока. Д.емодулятор многочастотных сигналов с амплитудно-фазовой модуляцией содержит аналого-цифровой преобразователь 1, перемножит ели 2, 3, накопитель 4, ключ 5, вычислительный блок бд фазовый демодулятор 7, амплитудный демодулятор 8, блоки 9 и 10 задержки, анализаторы 11 и 12 информаи,ии,, блок 13 вычитания, решающий блок 14, блок 15 кодирования, усреднитель 16, регулируемый усилитель 17, коммутатор 18, .синтезатор 19 частот и задающий генератор 20. Анализатор 11 (12) состоит из делителя 21 и блоков сравнения 22 и 23, Решающий блок 14 состоит из блока 24 определения знака Si N ,, элементов НЕ 25s элементов И 26 и 27, элементов НИИ 28 и элег-1ента И 29. Регулируемый ус11литель 17 состоит из ключей 30 и 31- операщ-сонного усилителя

32, элемента НЕ 33 и сопротивлений 34-37. Вычислительный блок 6 состоит из запоминающего блока 38, делителя

39,функционального преобразователя

40,квадратов 41 и 42, сумматора 43 и блока 44 извлечения квадратного корня.

Демодулятор многочастотных сигналов с амплитудно-фазовой модуляцией работает следующим образом.

Групповой сигнал на входе демодулятора представляет собой сумму гармонических составляющих канальных частот с амплитудами А и фазами ср , искажение воздействие неравномерное; ти АЧХ канала связи

П2

SHl;f;,An5i4nnl q)l.

в аналого-цифровом преобразователе 1 происходит дискретизация сигнала 5 (t) по времени и уровню, так что сигнал на его входе запишется в виде суммы оцифрованных отсчетов сигнала, взятых в момент времени t Rut

к-1

S( r. Ц (и«й1+а)„ , .

Отсчеты сигнала поступают на перемножитель 2, в котором каждый отсчет перемножается на цифровые отсчеты опорных гармонических колебаний Sin (kn nut ) и cog (knsiAt), поступающих через коммутатор 18 и вырабатываемых в синтезаторе 19 частот. Синтезатор 19 работает от частоты, вырабатываемой задающим генератором 20. Каждый отсчет сигнала 5 (k ui ) в перемножителе 2 умножается (п ,- Н)2 раз, по два перемножения на каждый подканал. В перемножителе 3 происходит доумножение результатов предъщутцих умножений на соответствующие канальные корректирующие коэффициенты JU п поступающие с выхода блока 15 кодирования. За время существования одного отсчета 5 (k ut) происходит (И 2 - П ) умножений, по одному перемножению на подканал.

В накопителе 4 происходит накопление результатов этих двух умножени для каждого подканала раздельно. Накогшение осутцествляется на интернале ортогональности, В конце этого интервала после обработки (k- 1)-го отсчета сигнала на выходе накопителя образуются значения проекций сигнала на ортогональные оси приемника

t-i

X., 5l5ik&t)-m fin5in(kVinQt), к-о

Y., «SCkut). „005(пл Kt),

1У /л

где Хр, У - проекции сигнала Ц--го

подканала.

Через ключ 5 проекции последовательно поступают на вычислительный блок 6, в котором определяются ампли туды и фазы сигналов всех частотных подканалов по формулам

ЦА, q,,,arct(Yr,|Xnl,

где п амплитуда,

Ср - фаза И -го подканала.

В фазовом демодуляторе 7 происходит вьщеление информации, заложенной в фазе или в разности фаз сигналов ( в зависимости от В1ада модуляции), а в амплитудном демодуляторе 8 - выделение информации, заложенной в амплитуде сигналов.

; Обработка частотных подканалов происходит последовательно во времени, начиная с первого канала и конча последним.

Одновременно с вьщелением информащ-ги амплитуды сигналов /И АП поступают на два последовательно соединенные блока 9 и 10 задержки на время оработки одного подканала. Таким образом, всегда существуют значения амплитуд трех каналов одновременно. Если вьщеляется информация из амплитуды ( П + 1)-го подканала А n-fi то на выходе блока 9 присутствует . сигнал амплитуды П -го подканала А, а на выходе блока ТО - сигнал амплитуды ( П - 1 ) -го подканала А р. .

Анализаторы 11 и 12 осуществляют сравнение амплитуд соседних подканалов друг, с другом по алгоритмам

I Si Nin -p ftn/ju). ((К„А(гд,А,-П:

т где 11 - логический сигнал на первом

Y) выходе анализатора I логический сигнал на втором

выходе анализатора

П, и П - постоянные пороги, зависящи только от коэффициента ампл1тудной модуляции сигнала; А),- величина амплитуды А цпа анализатора 11 и амплитуды А,„. для анализатора 12. Анализаторы построены таким обраt п , ,зом, что сигнал i, i на. первом выхо де соответствует П передаваемой ин форматдии, сигнал 1 1 на втором выходе 1 информапии. Разрешается ситуация, когда невозможно точно указать информацию на основании анализа амплитуд соседних подканалов. Это соответствует спучаю 1 -г 0. Кроме сравнений амплитуды Ду G соседними канальными амплитудами из величины Y вычитается значение порогового сигнала U цдо , одинаковое для всех частотных подканалов, и определяется знак этой разности в решающем блоке 14, Если в результате предваритеяьног анализа удается по сигналам (1 ), С) (l) () анализаторов 11 и 12 однозначно идентифицировать информацию, заложенную в амплитуде П-го подканала, решающий блок 14 выдает сигнал управления на регулируемый усилитель 17. Если принято .решение, что передавался сигнал 1, регулируемый усилитель 17 По сигналу решающего блока 14 пропустит на усреднитепь 16 сигнал 5 bi fUnAf, где П1, 1. Если передавался сигнат;. О, то регулируемый усилитель 17 усилит сигнал на своем выходе, т.е. 5п Д (при исполь зовании амплитудной модуляцнИд для которой / - 2., значения коэф фициентов соответственно равны т, 0,75,- mj 1,5) . Если в результате предварительно го анализа не удается определить информацию в П -м подканале либо из-за нулевых показаний анализаторов 11 и 12, либо из-за противоречи6вьк результатов анализа, решающий блок 14 учитывает только результат сравнения в блоке 13 А, с порогом IJtjop. Если tl пор 5 сигнал на вхоле усреднителя 16 равен 5f, (г. Uf, ftv(. в противном случае - 5f, - ,A. Усреднитель 16 осуществляет-усреднение сигналов Sf, на большом интервале времени в результате чего зна.чительно повьшается точность выработки коэффигдиентов коррекции 1Ц , которые вырабатываются блоком 15 кодирования. Коэффициенты коррекции ,5 подаваемые на вход перемножителя 3, корректируют усиление в сквозном тракте обработки сигналов частотных подканалов и выравнивают коэффициенты усиления по всем подканалам, Выравнивание происходит таким образом, 4Tomijiin Unop ;m fiinA°n-Unop О при отсутствии в канале. Таким образом, в результате межканального анализа информации, заложенной в амплитуде сигналов частотных подканалов, производится коррекция ЛЧХ. Для крайних каналов, для всоторьк отсутствуют соседние рабочие каналы, коррекция производится либо ка основании анализа только одной пары каналов, либо на основании анализа крайних пилот-сигналов. Так как эти пилот-сигналы обычно располагаются па краях полосы пропусканкя я используются для коррекции сдвига частот в канале, то использование их для анализа информации в рфай; их рабочих подканалах не меняет ни схему, ни алгоритм обработки амплитуд этих каналов. Предлагаемое устройство позволяет уве. помехоустойчивость приема информации как по фазе, так и по амгтлитуде за счет повышения точHocTiT г-;оррекпд-1И АЧХ канала.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки качества канала связи | 1982 |

|

SU1075425A1 |

| Устройство для детектирования многочастотных сигналов | 1987 |

|

SU1427596A1 |

| Демодулятор многоканального модема с амплитудно-фазоразностной манипуляцией | 1981 |

|

SU1019662A1 |

| Способ когерентного приема сигналов амплитудно-фазовой модуляции и устройство для его осуществления | 1983 |

|

SU1185640A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| ДЕМОДУЛЯТОР ДВУХПОЗИЦИОННЫХ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2699066C1 |

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

| ЦИФРОВОЙ АДАПТИВНЫЙ КОРРЕКТОР | 1983 |

|

RU2024199C1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1987 |

|

SU1499468A1 |

ДЕМОДУЛЯТОР МНОГОЧАСТОТНЫХ СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦ11ЕЙ, содержащий последовательно соединенные задающий генератор, синтезатор частот, коммутатор и первый перемножитель, аналого-цифровой преобразователь, последовательно соединенные усреднитель, блок кодирования и второй перемножитель, цоследовательно соединенные накопитель, ключ и вычислительный блок, выходы которого соединены с входами фазового и амплитудного демодуляторов, выходы которых являются выходами демодулятора, блок вычитания, отличающийся тем, что, с целью повышения помехоустойчивости за счет повышения точности коррекшта амплитудно-частотной характеристики канала, в него введены два блока задержки, регулируемый усилитель, два анализатора информации и решающий блок, причем выход аналого-цифрового преобразователя через первый перемножитель соединен с другим входом второго перемножителя, выход которого соединен с входом накопителя, один выход вычислительного блока соединен с первым входом первого анализатора информации и входон первого блока за держки, выход которого соединен с вторым входом первого анализатора информации, первым входом второго анализатора информации, его вторым входом через второй блок задержки, входом блока вычитания и первым входом регулируемого усилителя, второй вход которого соединен с выходом решающего блока, а выход - с входом усреднителя, выходы анализаторов ин-ч1 формации и выход блока вычитания эо ел соединены с соответствующими входами решающего блока.

П1.

X

21

вых1

.К 6jfOf(y

Iff

П2

дых2 J

23

Фиё 2

Г

rzin

К ю/И

/J

/(

Фи&:Ъ

г1

г 26 1

f7

nu

I

фиг Л

dffO/fffJ

Фиг 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Kawai Т | |||

| К; Time division processed multicarrier multi PSR ASK modem Proc | |||

| Nat Slectron Conf | |||

| Chicago, 1970, vol | |||

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

| Устройство для управления параметрами газовой среды | 1975 |

|

SU589594A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Демодулятор многоканального модема с амплитудно-фазоразностной манипуляцией | 1981 |

|

SU1019662A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-10-07—Публикация

1983-06-24—Подача