смещения и первого токоограничительного резистора, база второго усилительного транзистора соединена с первыми выводами второго резистора смещения и второго токоограничительного резистора и с базой четвертого усилительного транзистора, эмиттер которого соединен с вторым выводом токозадающего резистора и с эмиттером третьего усилительного транзистора, база которого подключена к первому выводу третьего резистора смещения, второй вывод которого соединен с вторыми выводами, первого и второго резисторов смещения и с щиной нулевого потенциала, второй вывод первого то-коограничительного резистора подключен к среднему выводу балансировочног потенциометра, второй вывод второго токоограничительного резистора соединен с первым выводом терморезистора, второй вывод которого является, вторым входом устройства, коллекторы третьего и четвертого усилительных

транзисторов через соответствующие третий и четвертый резисторы нагрузки подключены к первому выходу источника напряжения, второй вькод которого через восьмой масштабньй резистор соединен с инвертируКщим входом первого операционного усилителя, между инвертирующим входом и выходом третьего операционного усилителя включен девятый масштабный резистор, второй вывод седьмого масштабного резистора соединен с выходом третьего операционного усилителя, неинвертирующий вход которого через десятый масштабньй резистор подключен к шине нулевого потенциала, коллекторы третьего и . четвертого усилительных транзисторов соединены соответственно с инвертируйщим и неинвертирукицим входами третьего операционного усилителя, первьм и второй выводы блока коррекции соединены соответственно с первым и вторым выводами первого масштабного резистора .

| название | год | авторы | номер документа |

|---|---|---|---|

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Устройство для перемножения напряжений | 1983 |

|

SU1095197A1 |

| Аналоговый делитель | 1982 |

|

SU1022180A1 |

| Логарифмический усилитель | 1982 |

|

SU1088019A1 |

| Функциональный преобразователь напряжение - ток | 1989 |

|

SU1672479A1 |

| Устройство для ограничения | 1986 |

|

SU1341656A1 |

| ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2252452C1 |

| ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ | 1991 |

|

RU2094942C1 |

МНОЖИТЕЛЬНОЕ УСТРОЙСТВО, содержащее первый операционный усилитель; инвертирующий вход которого соединен с первым выводом первого масштабного резистора, второй вывод которого является первым входом устройства, между инвертирующим входом и выходом первого операционного усилителя включен второй масштабный резистор, неинвертирующий вход первого операционного усилителя через третий масштабный резистор соединен с шиной нулевого .потенциала, выход первого операционного усилителя подключен к первому выводу четвертого масштабного резистора, второй вывод которого соединен с первым выводом пятого масштабного резистора, второй вывод которого подключен к неинвертирующему входу первого операционного усилителя, первый и второй усилительные транзисторы, эмиттеры которых подключены к второму выводу четвертого масштабного резистора, коллекторы первого и второго усилительных транзисторов через соответствующие первый и второй резисторы нагрузки соединены с первым выходом источника напряжения, второй операционньм усилитель, между инвертирующим входом и выходом которого включен шестой масштабный резистор, цервый вывод седьмого масштабного резистора подключен к неинвертирующему входу второго операционного усилителя, выход которого является выходом устройства, источник напряжений смещения, к выхот дам которого подключены первый и второй выводы балансировочного потенциометра, к первому выходу источника нашряжений смещения подключен первый г вывод токозадающего резистора, первый и второй резисторы смещения, первьй и второй токоограничительные резисторыJ коллекторы первого и второго усилительньк транзисторов подключены соответственно к неинвертирукяцему и инвертирующему входам второго операционного усилителя, отличающееся со тем, что, с целью расширения области о применения за счет возможности пере&9 множения гармонических сигналов и 1 повышения точности работы, в него введены третий и четвертый усилительные транзисторы, третий операционный усилитель, третий и четвертый резисторы нагрузки, третий резистор смеп ения, восьмой, девятый и десятьй масштабные резисторы, терморезистор и блок коррекции, выполненный в виде последовательно соединенных выпрямительного диода и токоограничительного резистора, причем база первого усилительного транзистора соединена с первыми выводами первого резистора

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Известно множительное устройство, содержащее дифференциальные пары усилительных транзисторов, генераторы стабильных токов LlJ

Однако данное устройство характеризуется невысокой точностью работы и невозможностью перемножения переменных сигналов.

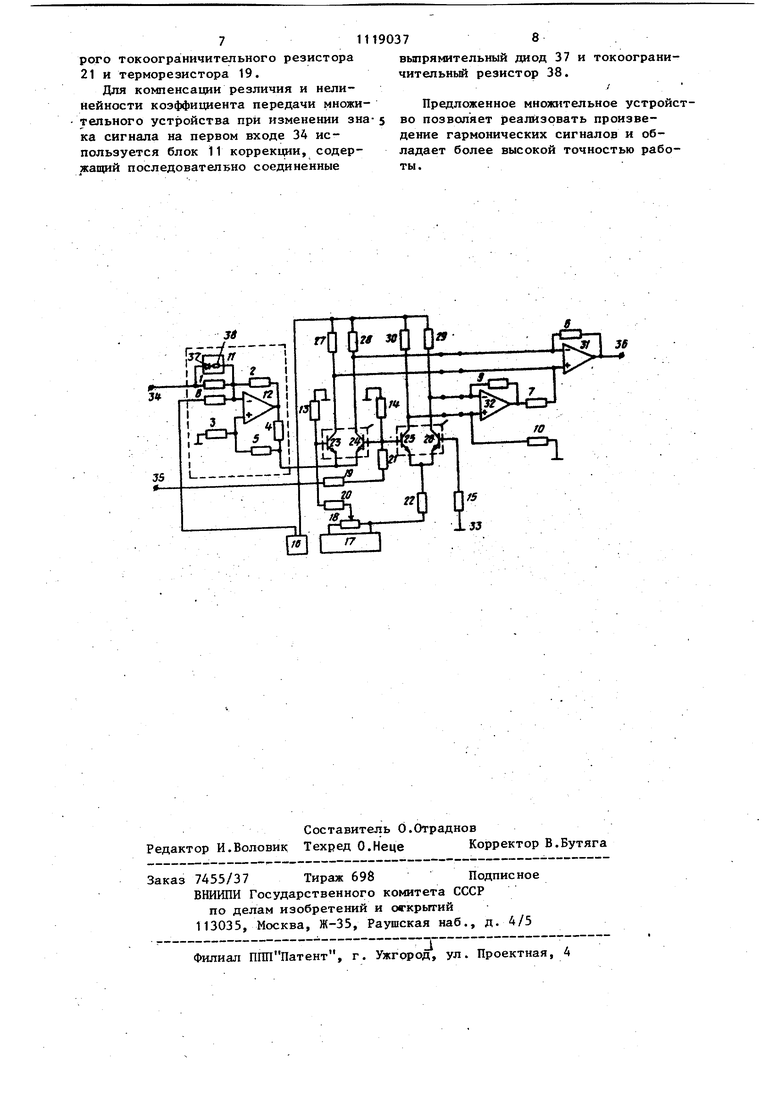

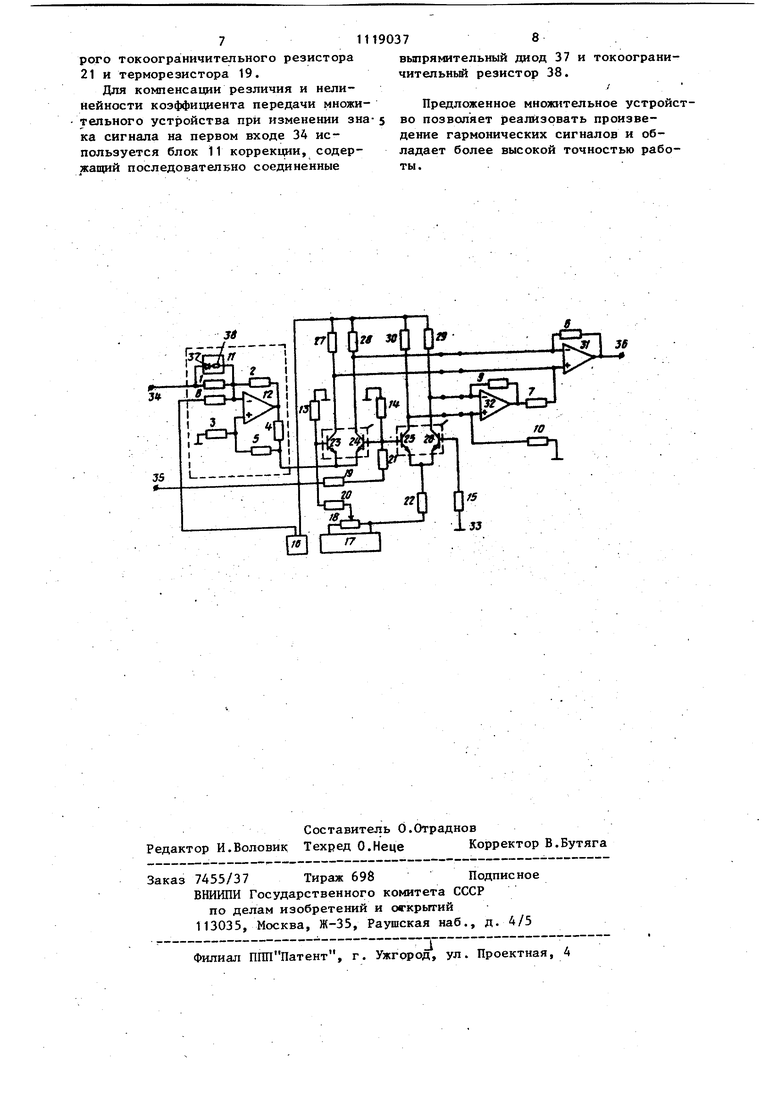

Наиболее близким к предложенному является множительное устройство, содержащее первый операционный усилитель, инвертирующий вход которого соединен с первым выводом первого масштабного резистора, между инвертирующим входом и выходом первого операционного усилителя включен второй масштабный резистор, к неинвертирующему входу первого операционного усилителя подключен первый вывод третьего масштабного резистора, второй вывод которого соединен с шиной нулевого потенциала, к выходу первого операционного усилителя подключен первый вывод четвертого масштабного резистора, второй вывод которого через пятьй масштабный резистор соединен с неинвертирующим входом . первого операционного усилителя, первьА и второй усилительные транзисторы, эмиттеры которых подключены к второму выводу четвертого масштабного резистора, коллекторы первого И второго усилительных транзисторов соединены соответственно с инвертирующим и неинвертирующим входами второго операционного усилителя, а через соответствую1Щ1е нагрузочные резисторы подключены к источнику напряжения, база второго усилительного транзистора подключена к среднему выводу балансировочного резистора, второй вывод первого масштабного резистора является первым входом, а база первого усилительного транзистора является вторым входом устройства, между инвертирующим входом и выходом второго операционного усилителя включен шестой масштабный резистор, неинвертирующий вход второго операционного усилителя через седьмой масштабный резистор подключен k шине нулевого потенциала, а выход является выходом устройства, токоограничительные резисторы и резисторы смещения 23. Однако с помощью известного устройства невозможно перемножить гармонические сигналы, кроме того, устройст во характеризуется невысокой точностью работы. Цель изобретения - расширение об ласти применения за счет возможности перемножения гармонических сигналов и повьшение точности работы. Поставленная цель достигается тем что в множительное устройство, содержащее пер.вый операционный усилитель, инвертирующий вход которого соединен с первым выводом первого масштабного резистора, второй вывод которого является первым входом устройства, между инвертирующим входом и выходом nejpBoro операционного усилителя включен второй масштабный резистор, неинвертирующий вход первого операционного усилителя через третий масштабный резистор соединен с шиной нулевого потенциала, выход первого операционного усилителя подключен к первому выводу четвертого масштабного резистора, второй вывод которого соединен с первым выводом пятого мас штабного резистора, второй вывод которого подключен к неинвертирующему входу первого операционного усилителя, первый и второй усилительные транзисторы, эмиттеры которых подключены к второму выводу четвертого масштабного резистора, коллекторы первого и второго усилительных транзисторов че рез соответствующие первый и второй резисторы нагрузки соединены с первым выходом источника напряжения, вт рой операционный усилитель, между инвертирующим в и выходом которого включ.ен шестой масштабный резистор, первый вывод седьмого масштабно го резистора подключен к неинвертиругацему входу второго операционного усилителя, выход которого является выходом устройства, источник напряжений смещения, к выходам которого подключены первый и второй выводы балансировочного потенциометра, к первому выходу источника напряжений смещения подключен первьй вывод токозадаюшего резистора, первый и второй резисторы смещения, первый и второй токоограничительные резисто374ры, коллекторы первого и второго усилит,ельных транзисторов, подключены соответственно к неинвертирующему и инвертирукщему входам второго операционного усилителя, введены третий. и четвертый усилительные транзисторы, третий операционный усилитель,третий и четвертьй резисторы нагрузки,третий резистор смещения , восьмой, девятый и десятый масштабные резисторы,терморезистор и блок коррекции, выполненный в виде последовательно соединенных выпрямительного диода и токоограничительного резистора, причем база первого усилительного транзистора соединена с первыми выводами первого резистора смещения и первогоотокорграничительного резистора, база второго усилительного транзистора соединена с первыми выводами второго резистора смещения и второго токоограничительного резистора и с базой четвертого усилительного транзистора, эмиттер которого соединен с вторым выводом токозадающего резистора и с эмиттером третьего усилительного транзистора, база которого подключена к первому выводу третьего резистора смещения, второй вывод которого соединен с вторыми выводами первого и второго резисторов смещения и с шиной нулевого потенциала, второй вывод первого токоограничительного резистора подключен к среднему выводу балансировочного потенциометра, второй вывод второго токоограничительного резистора соединен с первым выводом терморезистора, второй вывод которого является вторым входом устройства, коллекторы третьего и четвертого усилительньос транзисторов через соответствующие третий и четвертый резисторы нагрузки подключены к первому выходу источника напряжений, второй выход которого через восьмой масштабный резистор соединен с инвертирукщим входом первого операционного усилителя, между инвертирующим входом и выходом третьего операционного усилителя включен девятый масштабный резистор, второй ВЫВОД седьмого масштабного резистора соединен с выходом третьего операционного усилителя, неинвертирукхций вход которого через десятьй масштабньй резистор подключен к щине нулевого потенциала, коллекторы третьего и четвертого усилительных транзисторов соединены соответстг венно с инвертирукяцим и неинверти5рукхцим входами третьего операционно го усилителя, первый и второй вывод блока коррекции соединены соответст венно с первым и вторым выводами первого масштабного резистора. На чертеже изображена функционал ная схема предложенного множительног устройства. Устройство содержит первый, второй, третий, четвертьв1, пятый, шестой, седьмой, восьмой, девятый и дес тый масштабные резисторы 1-10, блок 11 коррекции, первьй операционньй усилитель 12, первый, второй и третий резисторы смещения 13-15, источ ник 16 напряжения, источник 17 напряжений смещения, балансировочный потенциометр 18, терморезистор 19, первый и второй токоограничительные резисторы 20 и 21, токозадающий резистор 22, первый, второй, третий и четвертьй усилительные транзисторы 23-26, первый, второй, третий и четвертьй резисторы нагрузки 27-30, вто рой и третий операционные усилители 31 и 32, шину 33 нулевого потенциала первый и второй входы 34 и 35 и выхо 36устройства, вьшрямительньй диод 37и токоограничительньй резистор 38 Множительное устройство работает следующим образом. Сигналом, подаваемым на. второй вход 35, изменяется внутреннее сопротивление одного из пары первого и второго усилительных транзисторов 23 и 24. Поэтому ток, поступающий в их эмиттерные цепи от преобразователя напряжение-ток, образованного первым операционным усилителем 12 совместно с первым, вторым, третьим четвертым и пятым масштабными резисторами 1-5, при подаче на первый вход 34 напряжения, перераспределяется между первым и вторым усилитель ными транзисторами 23 и 24, а возникающий между их коллекторами дифференциальньй сигнал усиливается вто рым операционным усилителем 31. Так как коэффициент усиления дифферендаального каскада, образованного первым и вторым усилительными транэисторами 23 и 24, зависит от величины выходного тока преобразователя напряжение-ток, задаваемого напряжение на первом входе 34, то дифференциаль ный сигнал оказывается пропорциональ ным произведению сигналов на первом и втором входах 34 и 35. Этот сигнал можно запсать в виде: 7 где ормированные велиток KOjmeKTOpa при отсутствии сигнала полное приращение тока коллектора. где п„ - коэффициент. (1 и 4); тепловой потенциал; коэффициент передачи Делителя, образованного вторым резистором смещения 14, вторым токоорганичительным резистором 21 и терморезистором 19. Последний член в выражении (1) характеризует пролезание сигнала с второго входа 35 на выход 36. Аналогично работает дифференциальный каскад, образованньй трет1жм и четвертым усилительными транзисторами 25 и 26, совместно с третьим операционным усилителем 32, с той лишь разницей, что ток, поступающий в общую эмиттерную цепь через токозадающий резистор 22, постоянен. Дифференциальный сигнал, снимаемьй с коллекторов третьего и четвертого усилительных тразисторов 25 и 26, определяется выражением: IS.- Так как сигнал с выхода третьего операционного усилителя 32 поступает на неинвертирумций вход второго операционного усилителя 31, то на его выходе формируется разностной сигнал: th --S-- s ки.и, где U,Uj - напряжение на первом и втором входах 34 и 35. Влияние гиперболического тангенса в произведении сводится к минимуму подбором в.еличин сопротивлений второго резистора 14 смещения, вто711190378

2° «р™;.:™Го;гг° -р-ль, „„„„ з „ .„к„„.ра„„Для кошенсации резличия „ иел„-- « Ринстор 38.

г НН --ч:г ToeL:-Lir-b Sr- /.: pi..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент Великобритании № 1440093, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Шило В.Л | |||

| Линейные интегральные схемы в радиоэлектронной аппаратуре, М., Советское радио, 1979, с | |||

| Способ получения кодеина | 1922 |

|

SU178A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-10-15—Публикация

1982-12-31—Подача