управляющего регистра, информационны выходы мультиплексоров первой группы соединены с информационным входом регистра номера и информационным выходом первого входного регистра, информационный выход которого подключен к адресному входу первого блока постоянной памяти, первый и второй входы i -го (,2) узла анализа счетчика базовых операций соединены соответственно с информационным выходом 1 -го счетчика базовых операци и выходом ( +2)-го элемента И, первый и второй выходы i -го узла анализа счетчика базовых операций соединены соответственно с управляющим входом i -го счетчика базовых операций и счетным входом i -го счетчика стадий, выход старшего разряда сдвигового регистра соединен с управляющими входами мультиплексоров первой, второй и третьей групп, входом старшего разряда регистра индикаторов режима, первым входом третьего элемента И и третьим входом второго узла анализа кодов счетчика базовых операций, счетный вход первого триггера подключен к выходу первого элемента И, первый вход которого подключен к выходу старшего разряда первого счетчика шагов, выход первого триггера подключен к входам младших разрядов сдвигового регистра, регистра индикаторов режима, первому входу второго элемента И и третьему входу первого узла анализа счетчика базовых операций, первый и второй входы -го (,2) узла анализа счетчика соединены соответственно с информационным выхо дом -го счетчика и счетным входом -го счетчика, первый и второй выходы -го узла анализа кодов счетчика соединены со счетными входами соответственно 1 -го. счетчика шагов и i -го счетчика групп, первый и второй входы 1 -го ( 1,2) узла

анализа счетчика стадий соединены соответственно с информационным

выходом 1 -го счетчика стадий и счетным входом i -го счетчика стадий, выход 1 -го узла анализа кодов счетчика подключен к счетному входу 1 -гр счетчика, первый и второй информационные входы мультиплексоров первой группы соединены с информационными выходами соответственно первого и второго счетчиков первый и второй информационные входы мультиплексоров второй группы соединеныс информационными выходами соответственно первого и второго счетчиков базовых операций, информационные выходы мультиплексоров второ группы соединены с информационным входом второго входного регистра, информационный выход которого под ключен к адресным входам второго, третьего, четвертого и пятого блоков постоянной памяти, информационные выходы счетчиков групп, счетчиков стадий, второго и третьего триггеров подключены к соответствующим информационным входам мультиплексоров третьей группы, информационные выход которых соединены с информационным входом третьего вхрдного регистра, информационный выход которого соединен с информационным входом управляющего блока постоянной памяти, информационный выход которого соединен с входами параллельного занесения информации первого и второго счетчиков базовьк операций, выход третьего триггера подключен к входу первого разряда i -го (1,4) регистра первого поля адреса, входы второго и третьего разрядов которого соединены соответственно с выходом

(i+1)-ro разряда первого блока постоянной памяти и выходом второго разряда 1 -го блока постоянной памяти,

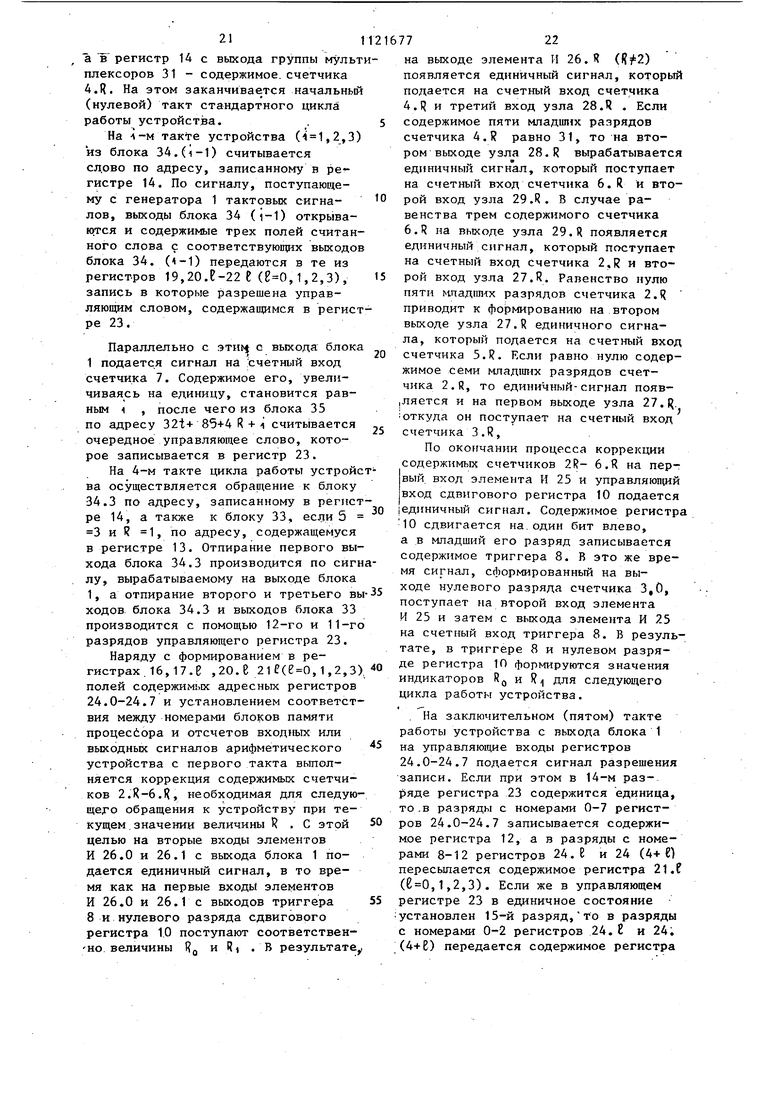

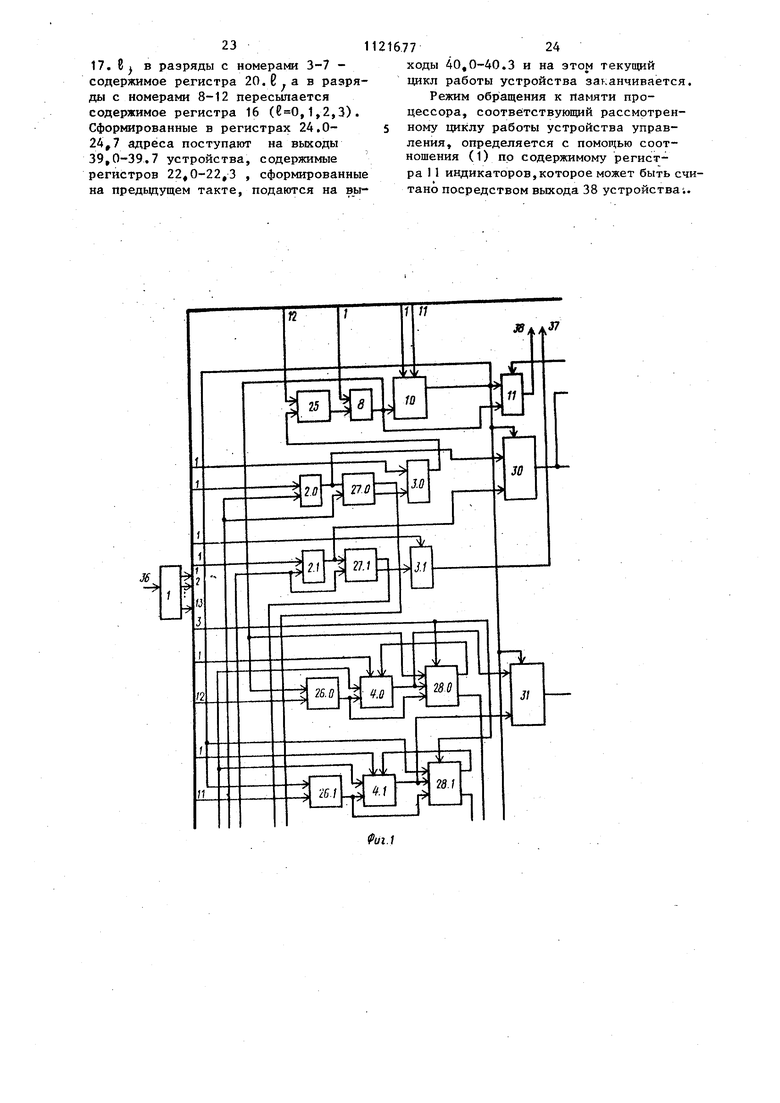

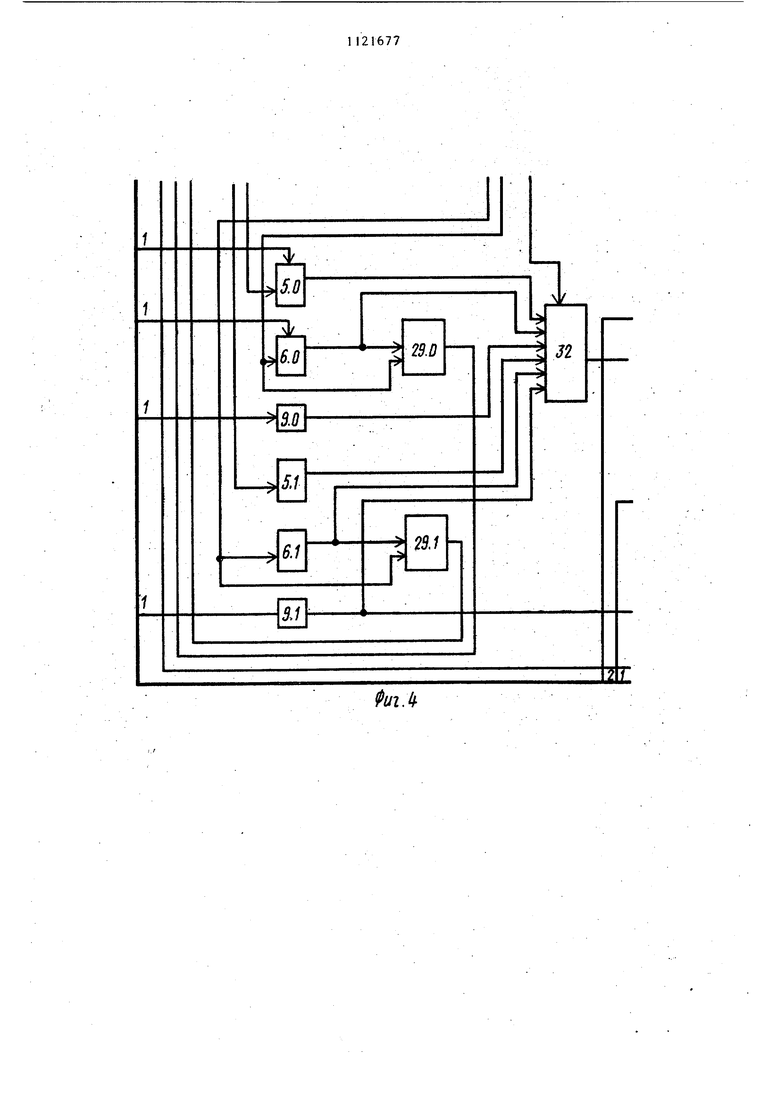

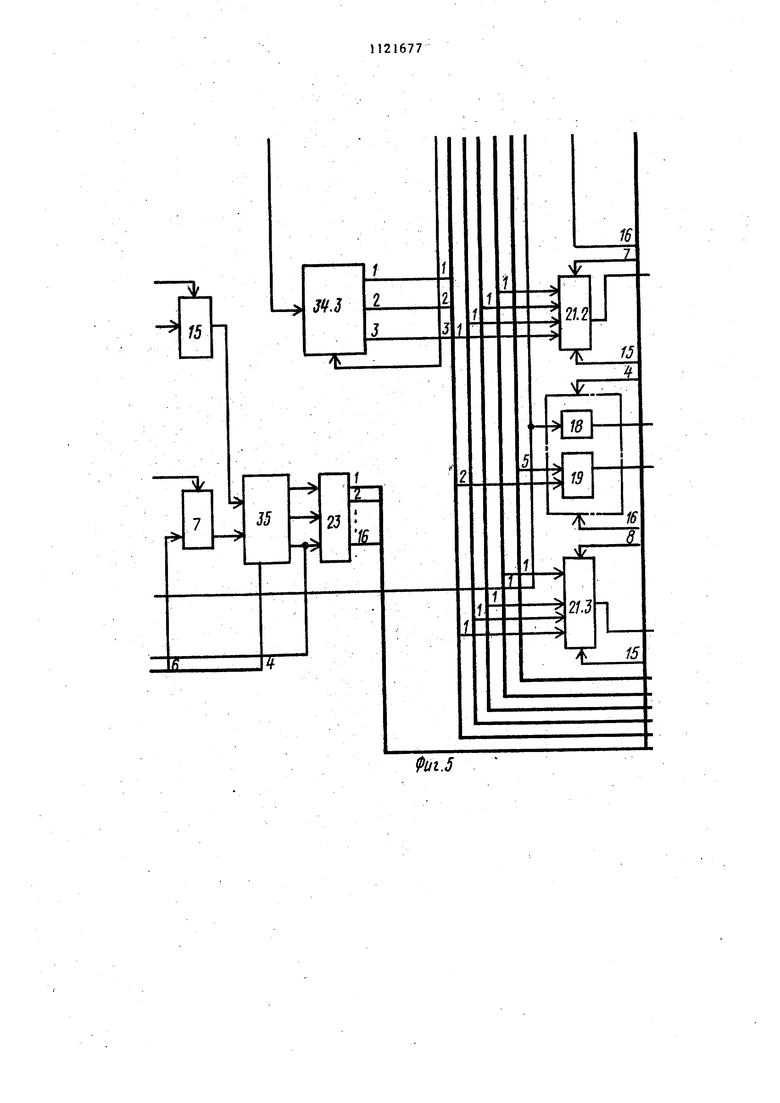

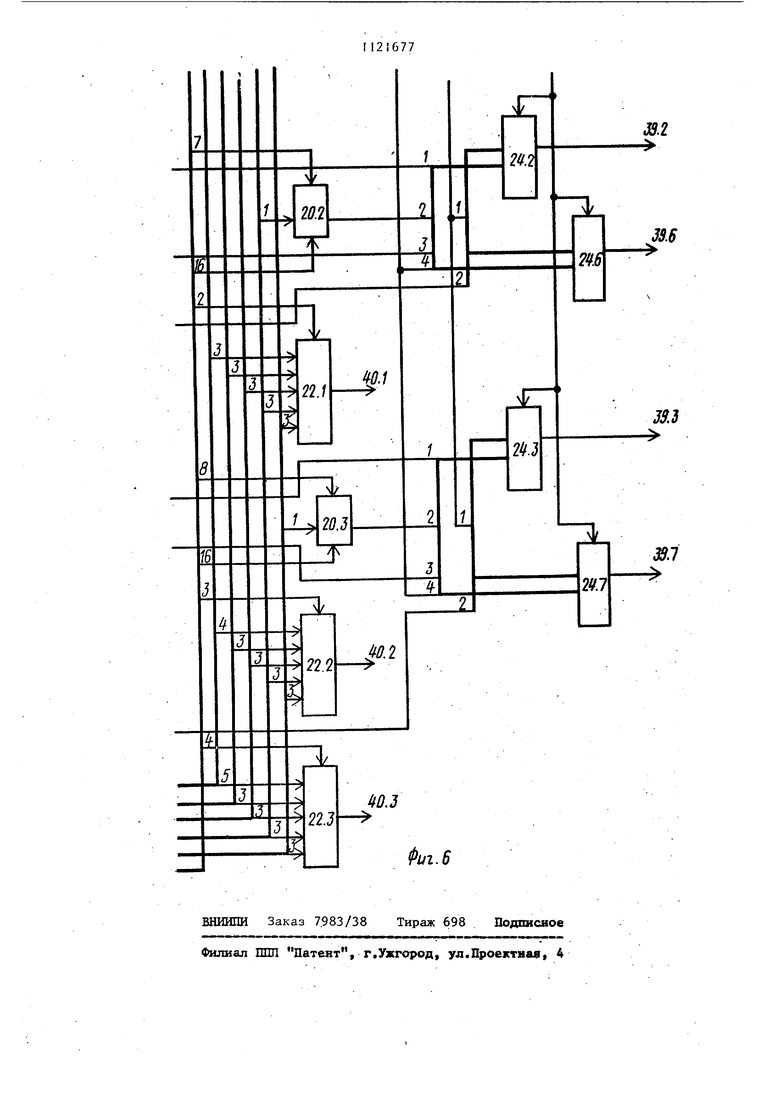

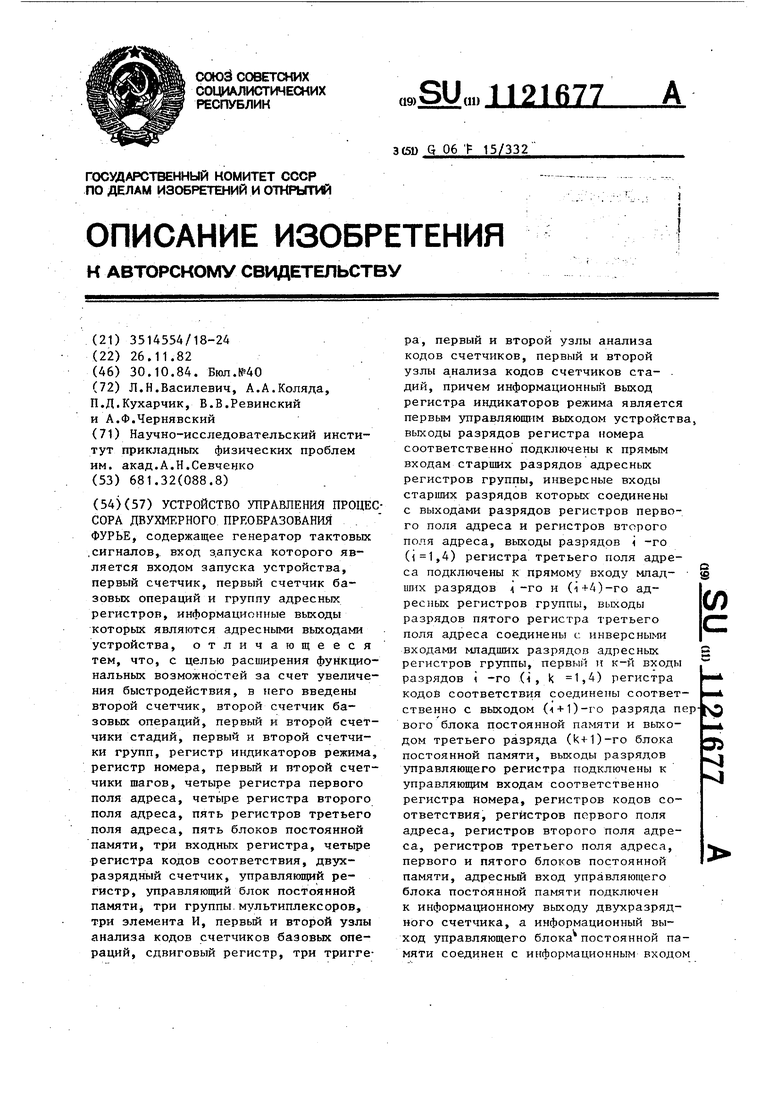

; выход первого разряда i -го блока постоянной памяти соединен с информационным входом 1 -го регистра второго йоля адреса и входами i -го разряда первого, второго, третьего и четвертого регистров третьего поля адреса, выход генератора тактовых сигналов подключен к вторым входам первого, второго и третьего элементов И, управляющим входам первого, второго, и третьего триггеров, управляющему входу сдвигового регистра, управляющему входу регистра индикаторов режима, управляющим входам адресных регистров групп управляющим входам первого, второго, третьего, четвертого и пятого блоко.в постоянной памяти, управляющему вход регистра номера, управляющим входам первого, второго и третьего входных регистров, выход старшего разряда второго счетчика шагов является вторьм управляющим выходом устройства, а информационные выходы первого, второго, третьего и четвертого регистрокодов соответствия являются кодовыми выходами устройства. Изобретение относится к вычислительной технике и предназначено для использования в процессорах быстрого преобразования Фурье (БПФ) конвейерного типа, осуществляющих обработку двухмерных комплексных сигналов. Известно устройство управления дл процессоров БПФ. Однако это устройство ориентировано на алгоритмы БПФ с основанием 2 и не может быть использовано для реализации алгоритмов с основанием 4 (или со смешанными основаниями), характеризующихся повышенной точностью и более высокой производительностью. Кроме того, это устройс во непригодно для работы в конвейерном режиме, что сужает сферу его при менения. Наиболее близким к изобретению является устройство управления процессора БПФ, содержащее регистр, первую и вторую группы .элементов И, первый и второй коммутаторы, узел задания режима,, первый и второй выходы которых соединены с первыми входами элементов И соответственно первой и второй групп, а первые входы подключены к третьему выходу, регистра, счетчик строк или столбцов и счетчик элементов строк или столбцов, входы которых подключены соответственно к четвертому и третьему выходам узла задания режима, первые выходы соединены соответственно с третьим и вторым входами узла задания режима, а вторые выходы подклю чены к первым входам первого и второ го коммутаторов соответственно, входы которых подключены к выходам элементов И первой И второй групп соответственно, регистр хранения адреса, узел обращения кода адреса, сумматор выход которого через узел обращения кода адреса соединен с выходом устройства и через регистр хранения адреса со своим вторым входом, а первь1й вход соединен с вторым выходо регистра. Этому устройству присущи перечнеле ные недостатки. Цель изобретения - увеличение быстродействия. Поставленная цель достигается тем что в устройство управления процессора двухмерного преобразования Фурье, содержащее генератор тактовых сигналов, вход запуска которого является ВХОДОМ запуска устройства, первый счетчик, первый счетчик базовых операций и группу адресных регистров, информационные выходы которых являются адресными выходами устройства, введены второй счетчик, второй счетчик базовых операций, первый и второй счетчики стадий, первый и второй счетчики групп, регистр индикаторов режима, регистр номера, первый и второй счетчики шагов, четыре регистра первого поля адреса, четыре регистра второго поля адреса, пять регистров третьего поля адреса, пять блоков постоянной памяти, три входных регистра, четыре регистра кодов соответствия, двухразрядный счетчик, управляющий регистр, управляющий блок постоянной памяти, три группы мультиплексоров,, три элемента И, первый и второй узлы анализа кодов счетчиков базовь.к операций, сдвиговый регистр, три триггера, первый и второй узлы анализа кодов счетчиков, первый и второй узлы анализа кодов с.чстчиков стадий, причем. информащюнный выход регистра индикаторов режима является первым управ- ляющим вькодом устройства, выходы разрядов регистра номера соответственно подключены к прямым входам старших разрядов адресньгх регистров группы, инверсные входы старщих разрядов которых соединены с выходами разрядоп регистров первого поля адреса и регистров второго поля адреса, выходы разрядов -го (,A) регистра третьего поля адреса подклю- чень к прямому входу младших разрядов 1 -го и (i+4)-ro адресных регистров группы, выходы разрядов пятого регистра третьего поля адреса соединены с инверсными входами младших разрядов адрес.ных регистров группы, первый и к-й входы разрядов -го(, К 1,4) регистра .кодов соответствия соединения соответственно с выходом (+1)-го разряда первого блока постоянной памяти и выходом третьего разряда (k+1)-ro блока постоянной памяти, выходы разрядов управляющего регистра подключены к управляющим входам соответственно егистра номера, регистров кодов соответствия, регистров первого поля адреса, регистров второго поля адреса, регистров третьего поля адеса, первого и пятого блоков постоянной памяти, адресный вход управ3 . ляющего блока постоянной.памяти подключен к информационному выходу двухразрядного счетчика, а информационный выход управляющего блока пос тоянной памяти соединен с информационным входом управляющего регистр информационные выходы мультиплексоров первой группы соединены с инфор мационным входом регистра номера и с информационным входом первого входного регистра, информационный выход которого подключен к адресному входу первого блока постоянной памяти, первый и второй входы -го ;(1,2) узла анализа кодов счетчика 1базовых операций- соединены соответс венно с информационным выходом -г счетчика базовых оцераций и выходом (i+2)-ro элемента И, первый и второй выходы 1 -го узла анализа кодов счетчика базовых операций соединены соответственно с управляюп(им входом i-го счетчика базовых операций и счетным входом i -го счетчика стадий, выход старшего разряда сдвигового регистра соединен с управляющими входами мультиплексоров первой второй и третьей групп, входом старшего разряда регистра индикаторов режима, первым входом третьего элемента И и третьим входом второго узла анализа кодов счетчика базовых операций, счетный вход первого триг гера, подключен к выходу первого элемента И, первый вход которого подключен к выходу старшего разряда первого счетчика шагов, выход первого триггера подключен к входам младших разрядов сдвигового регистра, регистра индикаторов режима, первому входу второго элемента И и третьему входу первого узла анализа счетчика базовых операций, первый и второй входы 1 -го (,2) узла анализа счетчика соединены соответственно с информационным выходом 1 -го счетчика и счетным входом 1 -го счетчика, первый и второй выходы 1 -го узла анализа кодов счетчика соединены со счетными входами соответственно i -го счетчи ка шагов и i -го счетчика групп, первый и второй входы л -го (-1 1,2) узла анализа счетчика стадий соединены соответственно с информационны выходом 1 -го счетчика стадий. и счетным входом i -го счетчика ста дий, выход 1 -го узла анализа кодов счетчика стадий подключен к 774 счетному входу i -го счетчика, первый и второй информационные входы мультиплексоров первой группы соединены с информационными выходами соотв.етственно первого и второго счетчиков, первый и второй информационные входы мультиплексоров второй группы соединены с информа- ционными выходами соответственно первого и второго счетчиков базовых операций, информационные выходы мультиплексоров второй группы соединены с информационным входом второго входного регистра, информационньш выход которого подключен к адресным входам второго, третьего, четвертого и пятого блоков постоянной памяти, информационные выходы счетчиков групп, счетчиков стадий-, второго и третьего триггеров подключены к соответствующим информационным входам мультиплексоров третьей группы, информационные выходы которых соединены с информационным входом третьего входного регистра, информационный выход которого соединен с информационным входом управляющего блока постоянной памяти, информационный выход которого соединен с входами параллельного занесения информации первого и второго счетчиков базовых операций, выход третьего триггера подключен к входу первого разряда 1 -го (,4) регистра первого поля адреса, входы второго и третьего разрядов которого соединены соответственно с выходом (+1)-го разряда первого блока постоянной памяти и выходом второго разряда 1-го блока постоянной памяти, выход первого разряда i -го блока постоянной памяти соединен с информационным входом 1 -го регистра второго поля адреса и входами i -го раз - ряда первого, второго, .третьего и четвертого регистров третьего по- . ля адреса, выход первого разряда первого блока постоянной памяти соединен с информационным входом пятого регистра третьего поля ацреса, выход генератора тактовых сигналов подключен к вторым входам первого, второго и .третьего элементов И, управляющим входам первого, второго и третьего триггеров, управляющему входу сдвигового регистра, управляющему входу регистра индикаторов режима, управляющим входам адресных регистров. группы, управляющим входам первого, второго, третьего,четвертого и пятого блоков постоянной памяти, упра Ляющему входу регистра номера, iуправляющим входам первого,, второго и третьего входных регистров, выход старшего разряда второго счетчика шагов является вторым управляю щим выходом устройства, а информационные выходы первого, второго, тр тьего и четвертого регистров кодов соответствия являются кодовыми выходами устройства. На фиг.1-6 представлена функхщональная схема устройства управления процессора двухмерного преобразован Фурье. Устройство содержит генератор 1 тактовых сигналов, декрементные вос миразрядные счетчики и 2,1 (одномерных преобразований Фурье), . двухразрядные счетчики 3,0 и 3,1 шагов (двухмерного преобразования Фурье), восьмиразрядные счетчики 4,0 и 4;1 базовых операций трехразрядные счетчикй 5.0 и. 5.1 групп (одномерных преобразований Фурье) двухразрядные счетчики 6.0 и 6.1 стадий (алгоритма БПФ) вспомогатель ный двухразрядный счетчик 7, тригге ры 8,9.0 и 9.1 сдвиговый регистр 10 двухразрядный регистр 11 индикаторо режима работы устройства, восьмираз рядный регистр 12 номера .(текущего одномерного преобразования Фурье), входные регистры 13,14. и 15, регис ры первого, второго и третьего поле адресов .1, 18,19 20 и 21 ( 0,3) двухразрядные регистры 22.022.3 кодов соответствия (номеров блоков памяти процессора и отсчетов входных и выходных сигналов арифметического устройства), шестнадцатиразрядный управляющий регистр 23, одиннадцатиразрядные адресные регис ры 24.0-24.7 элементы И 25,26.0 и 26.1 узлы 27.0 и 27.1 анализа содержимого счетчиков (одномерных преобразований), узлы 28.0 и 28.1 анализа содержимого счетчиков базовых операций, узлы 29.0 и 29.1 анализа содержимого счетчиков стадий (алгоритма БПФ), группы мультиплексоров 30-32, блоки 33,34.034.3 постоянной памяти (формировани полей адресов), управляющий блок 35 постоянной памяти, вход 36 устройства, управляющие выходы 37 и 38 устройства, выходы 39.0-39.7 адре77 , сов, выходы 40.0-40.3 кодов соответствия номеров блоков памяти процессора и отсчетов входных и выходных сигналов арифметического устройства. В устройстве с помощью регистра ПО и триггера 8 реализуется имеющий место при конвейерном режиме работы сдвиг во времени последовательности обращения к памяти процессора в режиме записи относительно последовательности обращений к памяти процессора в режиме чтения на Ь циклов чтения и записи. С этой целью выход триггера 8 соединен с входом младшего разряда сдвигового регистра 10, его счетный вход соединен с выходом элемента И 25, второй вход которого подключен к выходу старшего разряда счетчика 3.0. Содержимое (, триггера 8 и RI старшего разряда регистра 10 являются индикаторами режима работы устройства управления. Возможные режимь работы устройства описываются величинойО, если и R 0; R 1, если и R, 1j 2, если При R 0 устройство управление осуществляет формирование содержимых адресных регистров 21.0 до 21.7 для обращения к памяти процессора в режиме чтения, случай 1 1 соответствует обращению к памяти процессора в ре жиме записи, при устройство управления выполняет роль своеобразной задержки на время одного цикла работы устройства. Узел 27. (,1) предназначен . для анализа содержимого счетчика 2- с целью формирования на первом и втором своих выходах соответственно булевьгх величин 2i , (3) де X g - содержимое 8 -го разряда четчика 2.i (Р 1,2,...,7), ij - величина, поступающая на четный вход счетчика 2.i. Узел 28 (,1) производит нализ содержимого счетчика 4 i предназначен для формирования на ервом и втором своих выходах соотетственно булевых величин RjXjX... XjY j Z,.R.XjX4,..)(,Y2, ;.(5) где Х - содержимое 6 -го разряда счетчика 4 ( В « 3,4,.. .7) ij( - величина, поступающая на вход узла 28.1,|J2 .величина, поступающая на счетный вход счетчика 4,1. Узел. 29. (,1) осуществляет анализ содержимого счетчика 6.1 формируя на своем выходе величину 2;.х„х,Х2У, (6) где Xg - содержимое 6 -го разряда счетчика 6. i (,1,2), у - величина, формируемая на счетном входе счетчика 6.1. Как видно из соотношений (2)-(6 узлы 27., 28.1, 2. ( 0,1) могу быть реализованы с помощью инверто ров и элементов И. Для того, чтобы пояснить назначение блоков 33,34.0-34.3,35 постоянной памяти и рассмотреть струк ры записанной в их памяти информац рассматривается общая характеристи ка процесса выполнения двухмерного преобразования Фурье. Двухмерное преобразование Фурье объема N N, + N t )может быть выполнено за два шага (шаг О и шаг 1), на каждо из которых производятся М одномерных преобразований Фурье с помощью алгоритма БПФ со смешанными основа ниями 2 и 4 J при этом отдельное одн мерное преобразование Фурье выполняется за m последовательных 778 стадий (нумерация 0,1,...т-1). На каждой из первых m стадий выполняются п- четырехточечных 2 преобразований, а на последней стадии - - пар двухточечных преобразований Фурье. Предлагаемое устройство управле- ния ориентировано на использование процессора двухмерного преобразования Фурье объема N 128x128 (), причем предполагается, что в состав процессора входят восемь блоков памяти емкостью 2слов каждый. В соответствии с этим матрицы отсчетов входного двухмерного сигнала занимают 2 первых ячеек каждого блока памяти, а отсчеты выходного сигнала помещаются во вторых половинах блоков памяти, т.е. в ячейках с ад 22- 25-1 ресами Строки и столбцы матриц нумеруются цифрами 0,1,... 127, а блоки памяти - цифрами 0,1,... 7. Действительные части отсчетов как входного, так и выходного сигналов помещаются в блоки памяти с номерами 0,1,2,3, а мнимые части отсчетов в блоки памяти с номерами 4,5,6 и 7. Работа как с действительными.так и с мнимыми частями производится идентично, В табл.1 приведена структура -х строк (i 0,1,... 127) массивов действительных частей отсчетов входного и выходного сигналов. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Многопроцессорная вычислительная система | 1982 |

|

SU1168960A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Логическое запоминающее устройство | 1987 |

|

SU1566411A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

УСТРОЙСТВО УПРАВЛЕНР1Я ПРОЦЕССОРА ДВУХМЕРНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее генератор тактовых .сигналов,, вход з.апуска которого является входом запуска устройства, первый счетчик, первый счетчик базовых операций и группу адресных регистров, информационные выходы которых являются адресными выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения быстродействия, в него введены второй счетчик, второй счетчик базовых операций, первый и второй счетчики стадий, первый и второй счетчики групп, регистр индикаторов режима, регистр номера, первый и второй счетчики шагов, четыре регистра первого поля адреса, четыре регистра второго поля адреса, пять регистров третьего поля адреса, пять блоков постоянной памяти, три входных регистра, четыре регистра кодов соответствия, двухразрядный счетчик, управляющий регистр, управляющий блок постоянной памяти, три группы.мультиплексоров, три элемента И, первый и второй узлы анализа кодов счетчиков базовых операций, сдвиговый регистр, три триггера, первый и второй узлы анализа кодов счетчиков, первый и второй узлы анализа кодов счетчиков ста- . дий, причем информационный выход регистра индикаторов режима является первым управляющим выходом устройства, выходы разрядов регистра номера соответственно подключены к прямым входам старших разрядов адресных регистров группы, инверсные входы CTapiJJHX разрядов которых соединены с выходами разрядов регистров первого поля адреса и регистров второго поля адреса, выходы разрядов i -го (,4) регистра третьего поля адреса подключены к прямому входу млад- пшх разрядов -i -го и (i+A)-ro ад(Я ресных регистров группы, выходы разрядов пятого регистра третьего поля адреса соединены с инверсными входами младших разрядов адресных регистров группы, первый и к-й входы разрядов i -го (i, k 1,4) регистра кодов соответствия соединены соответственно с выходом (-1 + 1)-го разряда первого блока постоянной памяти и выходом третьего разряда (k+1)-ro блока 35 1 постоянной памяти, выходы разрядов управляющего регистра подключены к управляющим входам соответственно регистра Номера, регистров кодов соответствия, регистров первого поля адреса, регистров второго поля адреса, регистров третьего поля адреса, первого и пятого блоков постоянной памяти, адресный вход управляющего блока постоянной памяти подключен к информационному выходу двухразрядного счетчика, а информационный выход управляющего блока постоянной памяти соединен с ИЕ{формационным входом

О 1 ,1+1

1+1

1+31

31

96 97

64 65

32 33

127

95

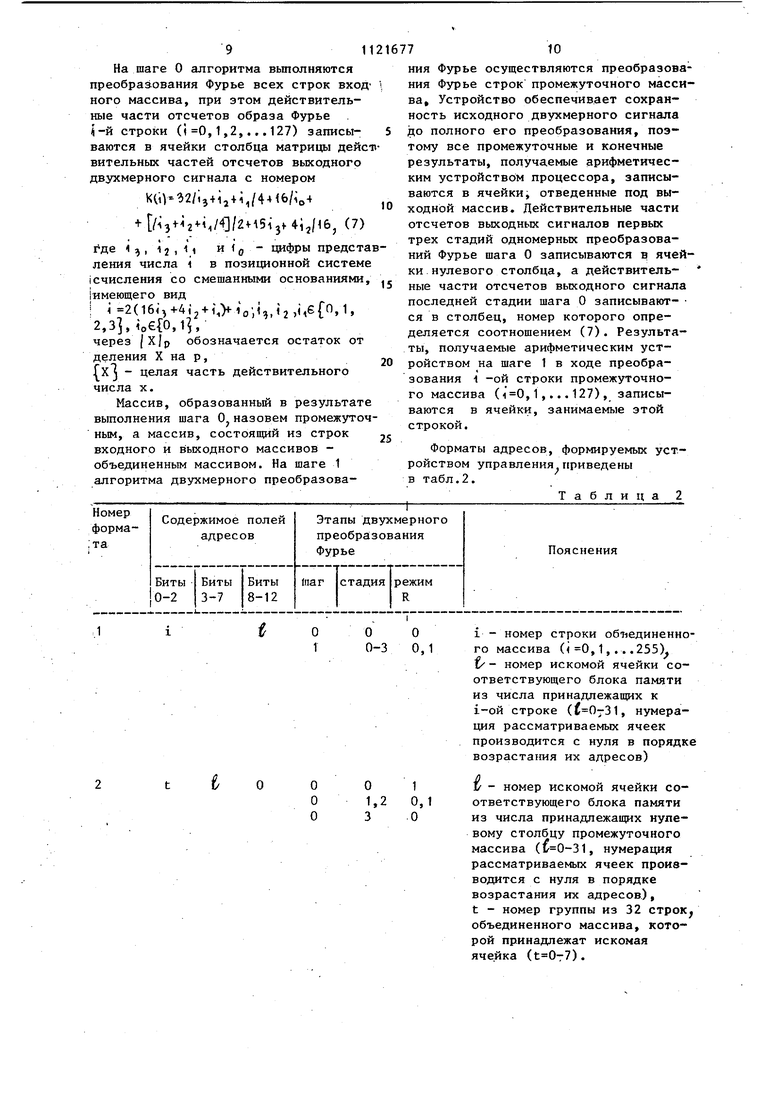

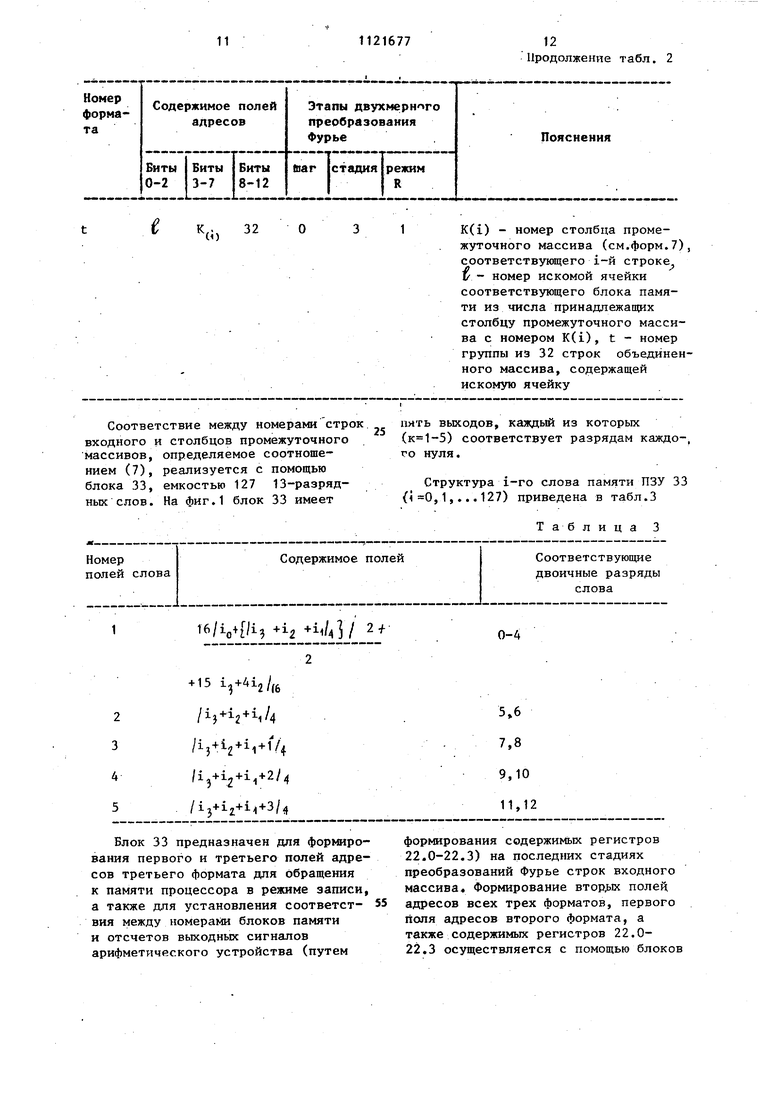

63 На шаге О алгоритма вьшолняются преобразования Фурье всех строк вход ного массива, при этом действительные части отсчетов образа Фурье J-й строки ((0,1,2,...127) записываются в ячейки столбца матрицы деис вительных частей отсчетов выходного двухмерного сигнала с номером K( + ij + ;,/4 + 6/io - /А3 2 ,/С1/2И5дз 412/16, (7) где i , , ij , 1,1 и fо - цифры предста ления числа i в позиционной системе iсчисления со смешанными основаниями jимеющего вид i 2(l643+4i2 + ,,i2,(efn,1, 2,з,1ое(о,1, через |Х/р обозначается остаток от деления X на р, Гх - целая часть действительного числа X. Массив, образованный в результате выполнения шага О, назовем промежуточ ным, а массив, состоящий из строк входного и выходного массивов объединенным массивом. На шаге 1 алгоритма двsxмepнoгo преобразоваV 00 О Т 0-3 0, «/О О 01 0 1,2 0, О 30 ния Фурье осуществляются преобразования Фурье строк промежуточного массива. Устройство обеспечивает сохранность исходного двухмерного сигнала до полного его преобразования, поэтому все промежуточные и конечные результаты, получаемые арифметическим устройством процессора, записываются в ячейки, отведенные под выходной массив. Действительные части отсчетов выходных сигналов первых трех стадий одномерных преобразований Фурье шага О записываются ячейки нулевого столбца, а действительные части отсчетов выходного сигнала последней стадии шага О записывают- ся в столбец, номер которого определяется соотношением (7). Результаты, получаемые арифметическим устройством на шаге 1 в ходе преобразования -1 -ой строки промежуточного массива (,1,... 127) , записываются в ячейки, занимаемые этой строкой. Форматы адресов, формируемых устройством управления приведены в табл.2. Таблица 2 i - номер строки обт1единенного массива (i 0,1, .. .255) t/ - номер искомой ячейки соответствующего блока памяти из числа принадлежащих к i-ой строке (0-31, нумерация рассматриваемых ячеек производится с нуля в порядке возрастания их адресов) I/ - номер искомой ячейки соответствующего блока памяти из числа принадлежащих нулевому столбцу промежуточного массива (, нумерация рассматриваемых ячеек производится с нуля в порядке возрастания их адресов.), t - номер группы из 32 строк объединенного массива, которой принадлежат искомая ячейка ().

32

О

40

Соответствие между номерами строк. входного и столбцов промежуточного массивов, определяемое соотношением (7), реализуется с помощью блока 33, емкостью 127 13-разряднык слов. На фиг.1 блок 33 имеет

Блок 33 предназначен для формирования первого и третьего полей адресов третьего формата для обращения к памяти процессора в режиме записи, а также для установления соответст- 55 ВИЯ между номерами блоков памяти и отсчетов выходных сигналов арифметического устройства (путем

K(i) - номер столбца промежуточного массива (см.форм.7), соответствующего i-й строке t - номер искомой ячейки соответствующего блока памяти из числа принадлежащих столбцу промежуточного массива с номером K(i), t - номер группы из 32 строк объединенного массива, содержащей искомую ячейку

пять выходов, каждый из которых () соответствует разрядам каждо-, го нуля.

Структура i-ro слова памяти ПЗУ 33 ,1,...127) приведена в табл.3

Таблица 3

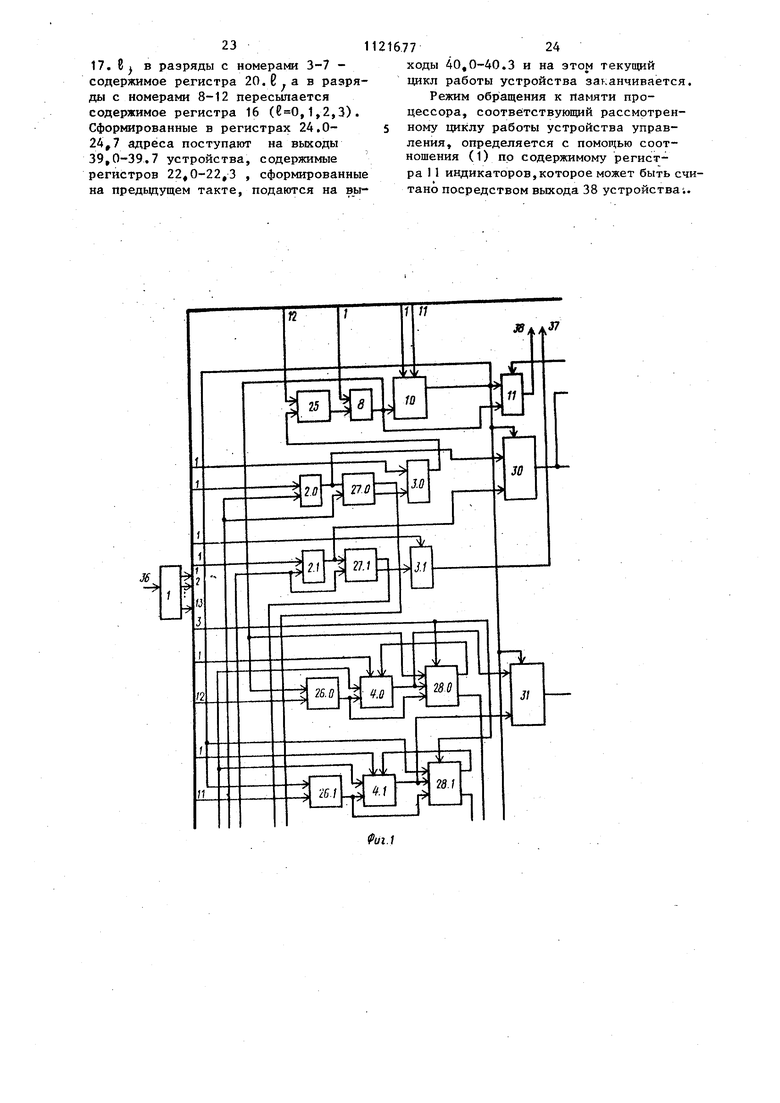

формирования содержимьк регистров 22.0-22.3) на последних стадиях преобразований Фурье строк входного массива Формирование вторд к полей адресов всех трех форматов, первого поля адресов второго формата, а также содержимых регистров 22.022.3 осуществляется с помощью блоков 34.0-34.3 емкостью 256 девятиразрядных слов каждое. Структура и правила формирования содержимого памяти этих устройств представлены в табл.4, где через 2 и о обозначают- 5 ся цифры представления числа (0,1...,31 вида

Формирование первых полей адресов Управление потоками информации, первого формата и третьих полейпоступаюпщми через регистры 12,16, адресов второго формата производится 5517.,20,i и 21,i (,1,2,3) в адреспосредством регистров 12 и 16 соот-ные регистры 24.0-24.7 и на выходы ветственно, причем без участия бло-40.0-40.3 устройства, осуществляет ков 33 и 34. 1 (,1,2,3).блок 35 емкостью 256 16-разрядных К 8,6., , 1,2,3, &д€ jTo, 1J. На фиг.1 блок 34. i (,1,2,3) имеет три выхода, каждый из которых (,2,3) соответствует разрядам каждого поля. Т а б л и ц а 4

15

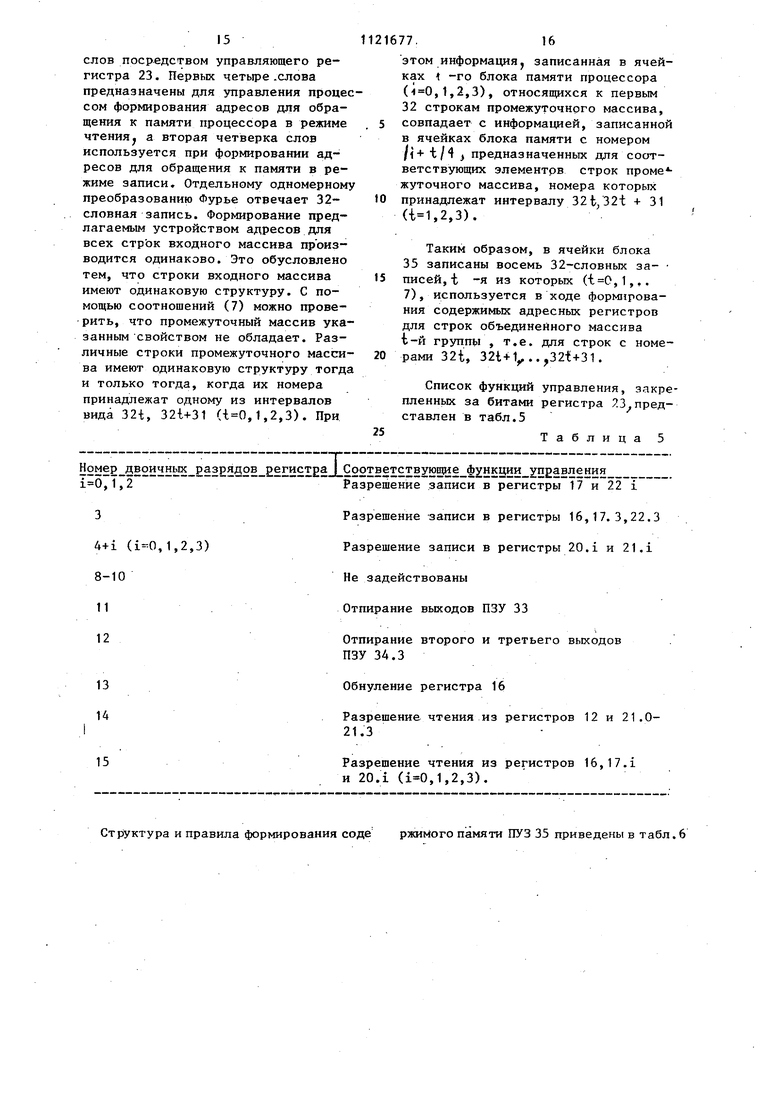

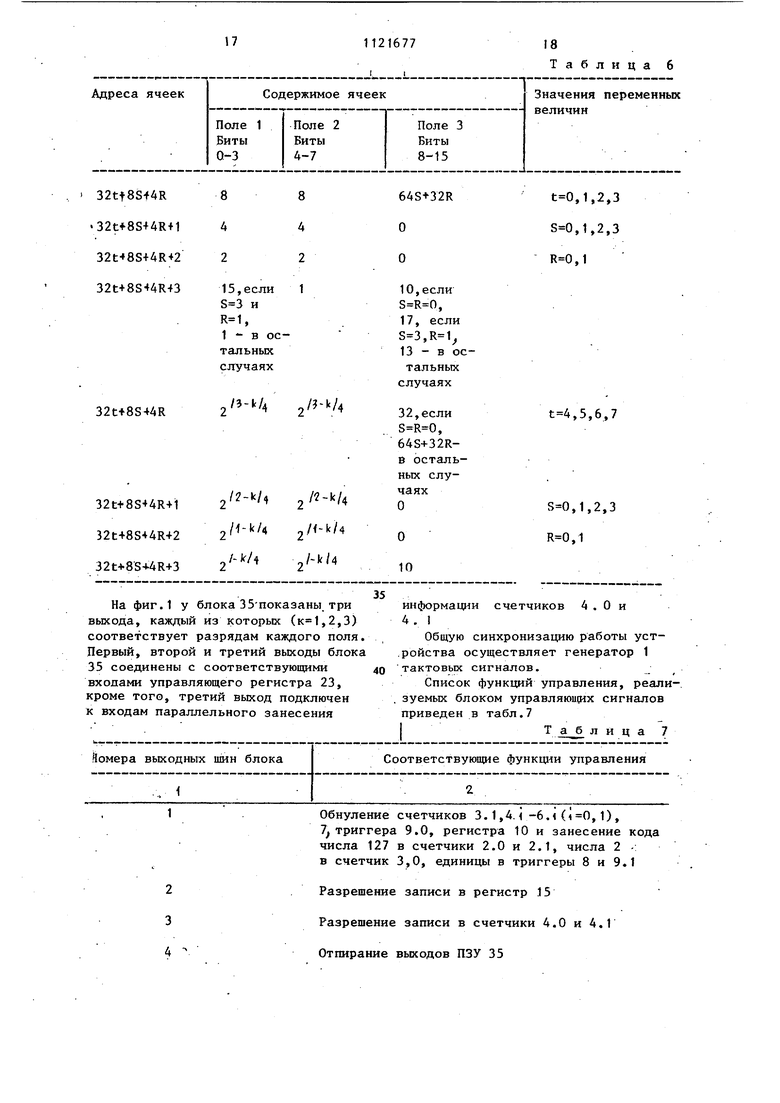

слов посредством управляющего регистра 23. Первых четыре .слова предназначены для управления процессом формирования адресов для обращения к памяти процессора в режиме чтенияJ а вторая четверка слов используется при формировании адресов для обращения к памяти в режиме записи. Отдельному одномерному преобразованию Фурье отвечает 32словная запись. Формирование предлагаемым устройством адресов для всех строк входного массива производится одинаково. Это обусловлено тем, что строки входного массива имеют одинаковую структуру. С помощью соотношений (7) можно проверить, что промежуточный массив указанным СВОЙСТВОМ не обладает. Различные строки промежуточного массива имеют одинаковую структуру тогда и только тогда, когда их номера принадлежат одному из интервалов вида 32i, 32i+31 (,1,2,3). При Номер двоичных ра ,1,2 3 4+1 (,1,2,3) 8-10 11 12 Структура и правила формирования соде

этом информацияJ записанная в ячейках -го блока памяти процессора (,1,2,3), относящихся к первым 32 строкам промежуточного массива, 5 совпадает с информацией, записанной в ячейках блока памяти с номером /1+ t/4 предназначенных для соответствующих элементов строк проме жуточного массива, номера которых 10 принадлежат интервалу 32t/32t + 31 (,2,3).

Таким образом, в ячейки блока 35 записаны восемь 32-словных за- писей,t -я из которых (,1,.. 7), используется в ходе формирования содержимых адресных регистров для строк объединенного массива t-й группы , т.е. для строк с номерами 32t, 32t + V..,32t+31.

Список функций управления, закрепленных за битами регистра 7.3 представлен в табл.5

Таблица 5 Соответствующие функции управления Разрешение записи в регистры 17 и 22 1 Разрешение записи в регистры 16,17.3,22.3 Разрешение записи в регистры 20.1 и 21.1 Не задействованы Отпирание выходов ПЗУ 33 Отпирание второго и третьего выходов ПЗУ 34.3 Обнуление регистра 16 Разрешение чтения из регистров 12 и 21.021.3 Разрешение чтения из регистров 16,17.1 и 20.1 (,1,2,3). ржимого памяти ПУЗ 35 приведены в табл.6

8

8 4 2

4 2

15,если 1 и ,

1 - в остальныхслучаях

„/3-1//

,

2/2-k/4 ,/-k/4

На фиг.1 у блока 35показаны три

выхода, каждый из которых (,2,3) соответствует разрядам каждого поля. Первый, второй и третий выходы блока 35 соединены с соответствующими входами управляющего регистра 23, кроме того, третий выход подключен к входам параллельного занесения

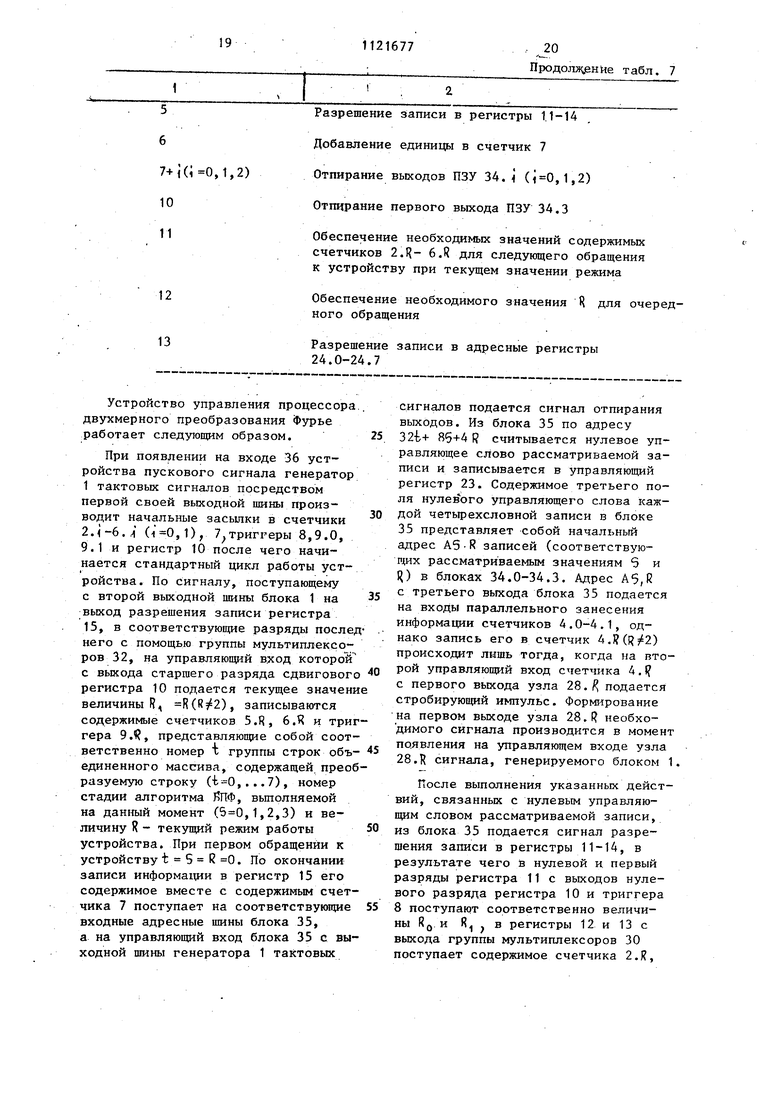

Обнуление счетчиков 3.1,4. г-6.1(0,1), 7 триггера 9.0, регистра 10 и занесение кода числа 127 в счетчики 2.0 и 2.1, числа 2 ; в счетчик 3,0, единицы в триггеры 8 и 9.1

Разрешение записи в регистр 15 Разрешение записи в счетчики 4.0 и 4.1 Отпирание выходов ПЗУ 35

Таблица 6

,1,2.3 ,1,2,3 ,1 ,5,6,7

,1,2,3 ,1

информации счетчиков 4 . О и

. 1

Общую синхронизацию работы уст.ройства осуществляет генератор 1 тактовых сигналов.

Список функций управления, реали, зуемых блоком управляющих сигналов

приведен в табл.7

IТ а б лица 7 7+i(,1,2) Устройство управления процессора двухмерного преобразования Фурье работает следующим образом. При появлении на входе 36 устройства пускового сигнала генератор 1 тактовых сигналов посредством первой своей выходной шины производит начальные засылки в счетчики 2.1-6. и (,1), 7 триггеры 8,9.0, 9.1 и регистр 10 после чего начинается стандартный цикл работы устройства. По сигналу, поступающему с второй выходной шины блока 1 на выход разрешения записи регистра 15, в соответствующие разряды после него с помощью группы мультиплексоров 32, на управляющий вход которой с вькода старшего разряда сдвиговог регистра 10 подается текущее значен величины R, R(), записываются содержимые счетчиков 5.R, 6.Я и три гера 9., представляющие собой соот ветственно номер t группы строк объ единенного массива, содержащей прео разуемую строку (,...7), номер стадии алгоритма ЙПФ, выполняемой на данный момент (,1,2,3) и величину R- текущий режим работы устройства. При первом обращении к устройству t 5 R 0. По окончании записи информации в регистр 15 его содержимое вместе с содержимым счет чика 7 поступает на соответствующие входные адресные шины блока 35, а на управляющий вход блока 35 с вы ходной шины генератора 1 тактовых Разрешение записи в регистры 11-14 Добавление единицы в счетчик 7 Отпирание выходов ПЗУ 34. i (,1,2) Отпирание первого выхода ПЗУ 34.3 Обеспечение необходимых значений содержимых счетчиков 2.R- 6.R для следующего обращения к устройству при текущем значении режима Обеспечение необходимого значения R для очередного обращения Разрешение записи в адресные регистры 24.0-24.7 сигналов подается сигнал отпирания выходов. Из блока 35 по адресу 32-t+ 85+4 R считывается нулевое управляющее слово рассматриваемой записи и записывается в управляющий регистр 23. Содержимое третьего поля нулевого управляющего слова каждой четьфехсловной записи в блоке 35 представляет собой начальный адрес А5 R записей (соответствующих рассматриваемьш значениям 5 и I) в блоках 34.0-34.3. Адрес А5,К с третьего выхода блока 35 подается на входы параллельного занесения информации счетчиков 4.0-4.1, однако запись его в счетчик 4.I() происходит лишь тогда, когда на второй управляющий вход счетчика 4 . с первого вькода узла 28. подается стробирующий импульс. Формирование на первом выходе узла 28,R необходимого сигнала производится в момент появления на управляющем входе узла 28.К сигнала, генерируемого блоком 1. После выполнения указанных действий, связанных с нулевым управляющим словом рассматриваемой записи, из блока 35 подается сигнал разрешения записи в регистры 11-14, в результате чего в нулевой и первый разряды регистра 11 с выходов нулевого разряда регистра 10 и триггера 8 поступают соответственно величины RO и RI , в регистры 12 и 13 с выхода группы мультиплексоров 30 поступает содержимое счетчика 2.1, а в регистр 14 с выхода группы fyльт плексоров 31 - содержимое, счетчика 4.R. На этом заканчивается начальньй (нулевой) такт стандартного цикла работы устройства. . На л-м такте устройства (,2,3) из блока 34.(i-1) считывается слово по адресу, записанному в регистре 14, По сигналу, поступающему с генератора 1 тактовых сигналов, выходы блока 34 (i-1) открываются и содержимые трех полей считанного слова с соответствующих выходов блока 34. (-1) передаются в те из регистров 19,20.е-22 6 (0,1,2,3), запись в которые разрешена управляющим словом, содержащимся в регист ре 23 . Параллельно с этт с выхода блока 1 подается сигнал на Учетный вход счетчика 7. Содержимое его, увеличиваясь на единицу, становится равным 1 , после чего из блока 35 по адресу 321+ 85+4 R +-j считывается очередное управляющее слово, которое записывается в регистр 23. На 4-м такте цикла работы устройс ва осуществляется обращение к блоку 34.3 по адресу, записанному в регист ре 14, а также к блоку 33, если 5 3 и R 1, по адресу, содержащемуся в регистре 13. Отпирание первого выхода блока 34.3 производится по сигн лу, вырабатываемому на выходе блока 1, а отпирание второго и третьего вы ходов блока 34.3 и выходов блока 33 производится с помощью 12-го и 11-го разрядов управляющего регистра 23. Наряду с формированием в регистрах , 16, 17.8 ,20.8 2ie(,1,2,3 полей содержимых адресных регистров 24.0-24.7 и установлением соответствия между номерами блоков памяти процессора и отсчетов входных или выходных сигналов арифметического устройства с первого такта выполняется коррекция содержимых счетчиков 2.R-6.R, необходимая для следую обращения к устройству при текущем , значении величины . С этой целью на вторые входы элементов И 26.0 и 26.1 с выхода блока 1 подается единичный сигнал, в то время как на первые входы элементов И 26.0 и 26.1 с выходов триггера 8 и нулевого разряда сдвигового регистра 1.0 поступают соответственно. величины R и RI .В результате на выходе элемента И 26. () появляется единичный сигнал, который подается на счетный вход счетчика 4.R и третий вход узла 28.R . Если содержимое пяти мпадших разрядов счетчика 4.1 равно 31, то на втором выходе узла 28.R вьфабатывается единичный сигнал, который поступает на счетный вход счетчика 6.R и второй вход узла 29.R. В случае равенства трем содержимого счетчика 6.R на выходе узла 29.R появляется единичный сигнал, который поступает на счетный вход счетчика 2,,R и второй вход узла 27.R. Равенство нулю пяти мпад1тта разрядов счетчика 2.R приводит к формированию на втором выходе узла 27.R единичного сигнала, который подается на счетный вход счетчика 5.R. Если равно нулю содержимое семи млад1Ш1х разрядов счетчика 2.R, то единичный-сигнал появ|Ляется и на первом выходе узла 27.1. :откуда он поступает на счетный вход счетчика 3.R, По окоргчании процесса коррекции содержимых счетчиков 2R- 6.R на первый вход элемента И 25 и управляющий |вход сдвигового регистра 10 подается единичный сигнал. Содержимое регистра 10 сдвигается на.один бит влево, а в младший его разряд записывается содержимое триггера 8. В это же время сигнал, сформированный на выходе нулевого разряда счетчика 3,0, поступает на второй вход элемента И 25 и затем с выхода элемента И 25 на счетный вход триггера 8. В результате, в триггере 8 и нулевом разряде регистра 10 формируются значения индикаторов RQ и для следующего цикла работы устройства. . На заключительном (пятом) такте работы устройства с выхода блока 1 на управляющие входы регистров 24.0-24.7 подается сигнал разрешения записи. Если при этом в 14-м раз-ряде регистра 23 содержится единица, то .в разряды с номерами 0-7 регистров 24.0-24.7 записывается содержимое регистра 12, а в разряды с номерами 8-12 регистров 24. В и 24 (4+€) пересыпается содержимое регистра 21.6 (,1,2,3). Если же в управляющем регистре 23 в единичное состояние установлен 15-й разряд,то в разряды с номерами 0-2 регистров 24. и 24; (4+В) передается содержимое регистра 17. 8 в разряды с номерами 3-7 содержимое регистра 20.6. а в разряды с номерами 8-12 пересылается содержимое регистра 16 (,1,2,3). Сформированные в регистрах 24.024,7 адреса поступают на выходы 39,0-39.7 устройства, содержимые регистров 22,0-22,3 , сформированные на предьщущем такте, подаются на вы724ходы 40,0-40.3 и на этом текущий цикл работы устройства заканчивается. Режим обращения к памяти процессора, соответствующий рассмртренному циклу работы устройства управления, определяется с помощью соотношения (1) по содержимому регистра 1 1 индикаторов,которое может быть считано посредством выхода 38 устройства;.

Jf.3

/5

-

35

23

к.

I 1

± 1

JE:

21,2

15 ЦЖ

М/

-

-ж

6 в

. V7

Авторы

Даты

1984-10-30—Публикация

1982-11-26—Подача