8 9 W171i1

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1987 |

|

SU1442996A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство обмена данными | 1988 |

|

SU1649556A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

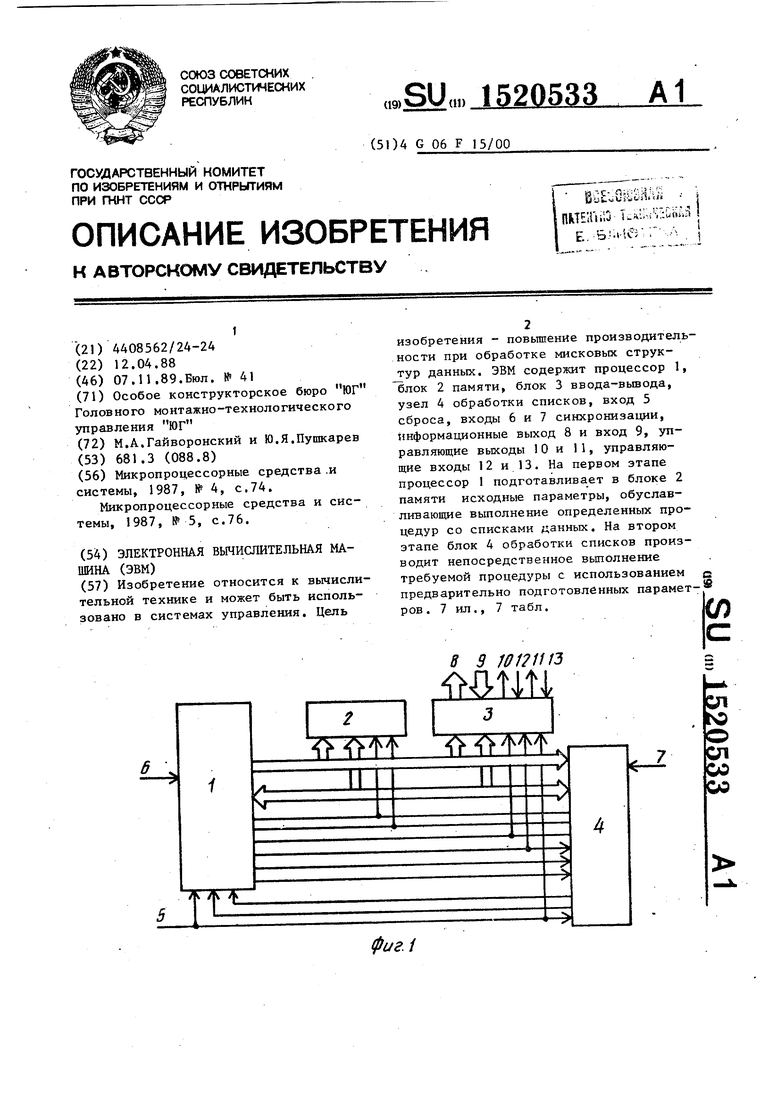

Изобретение относится к вычислительной технике и может быть использовано в системах управления. Цель изобретения - повышение производительности при обработке мисковых структур данных. ЭВМ содержит процессор 1, блок 2 памяти, блок 3 ввода-вывода, узел 4 обработки списков, вход 5 сброса, входы 6 и 7 синхронизации, информационные выход 8 и вход 9, управляющие выходы 10 и 11, управляющие входы 12 и 13. На первом этапе процессор 1 подготавливает в блоке 2 памяти исходные параметры, обуславливающие выполнение определенных процедур со списками данных. На втором этапе блок 4 обработки списков производит непосредственное выполнение требуемой процедуры с использованием предварительно подготовленных параметров. 7 ил., 7 табл.

фигЛ

3

Изобретение относится к вычислительной технике и может быть использовано в системах управления.

Цель изобретения - повышение производительности ЭВМ при обработке списковых структур данных.

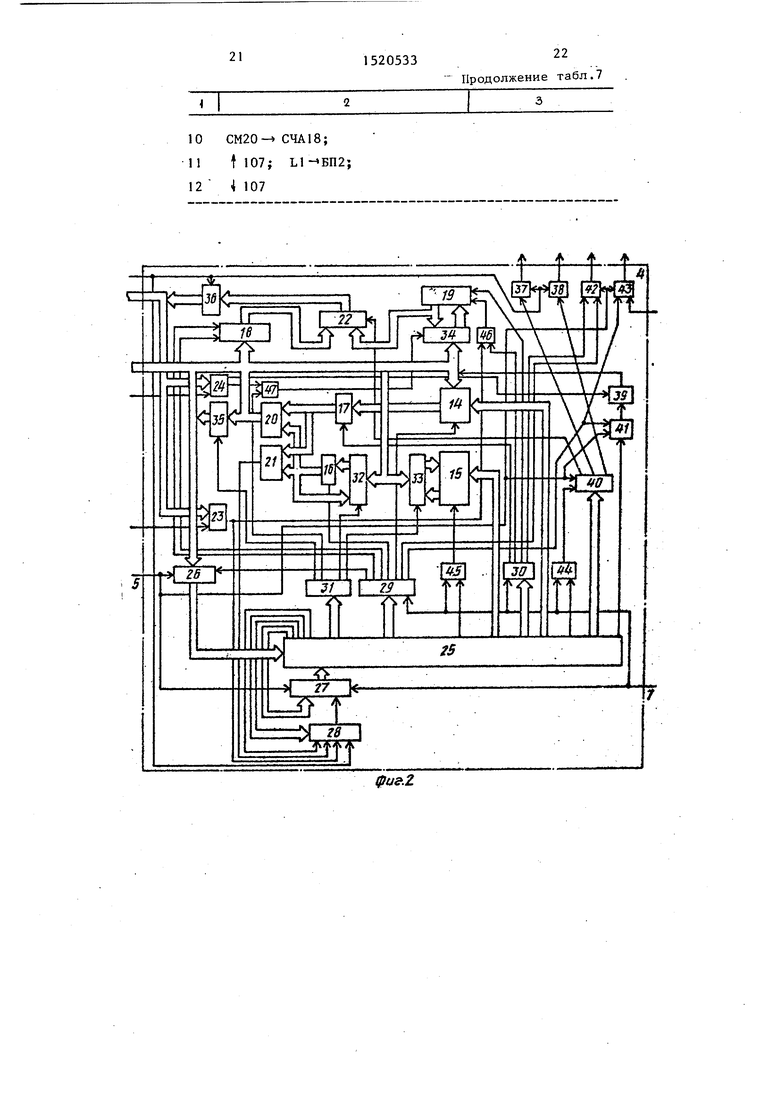

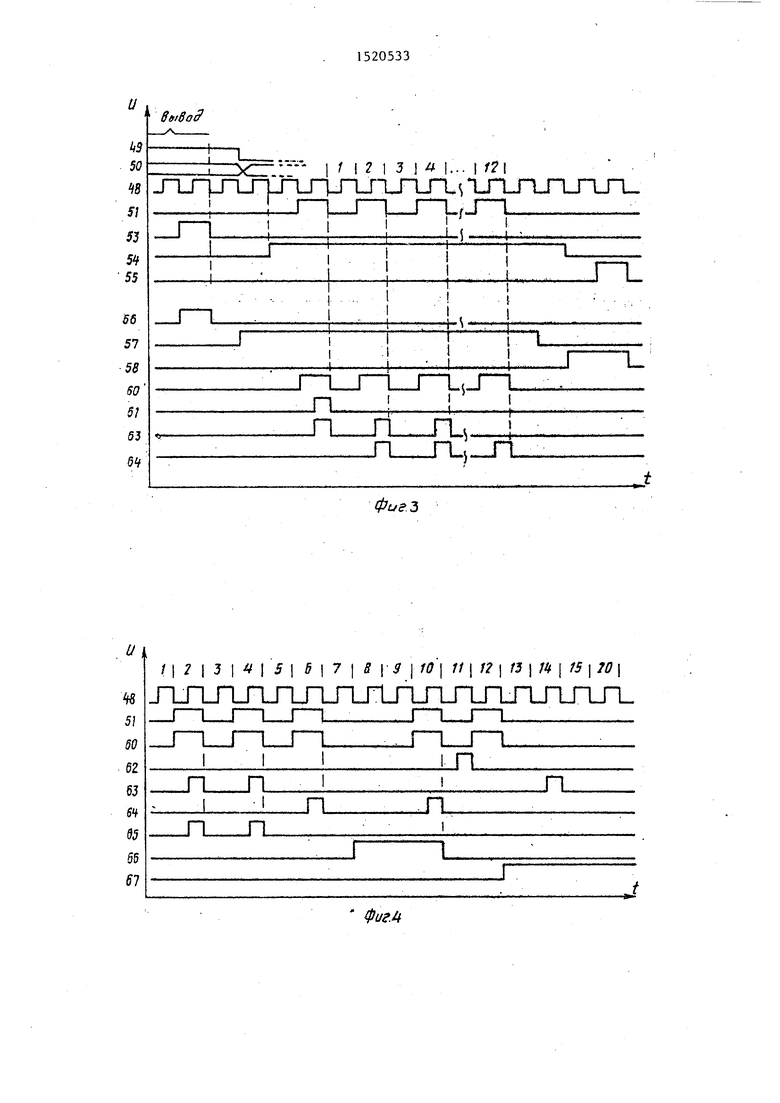

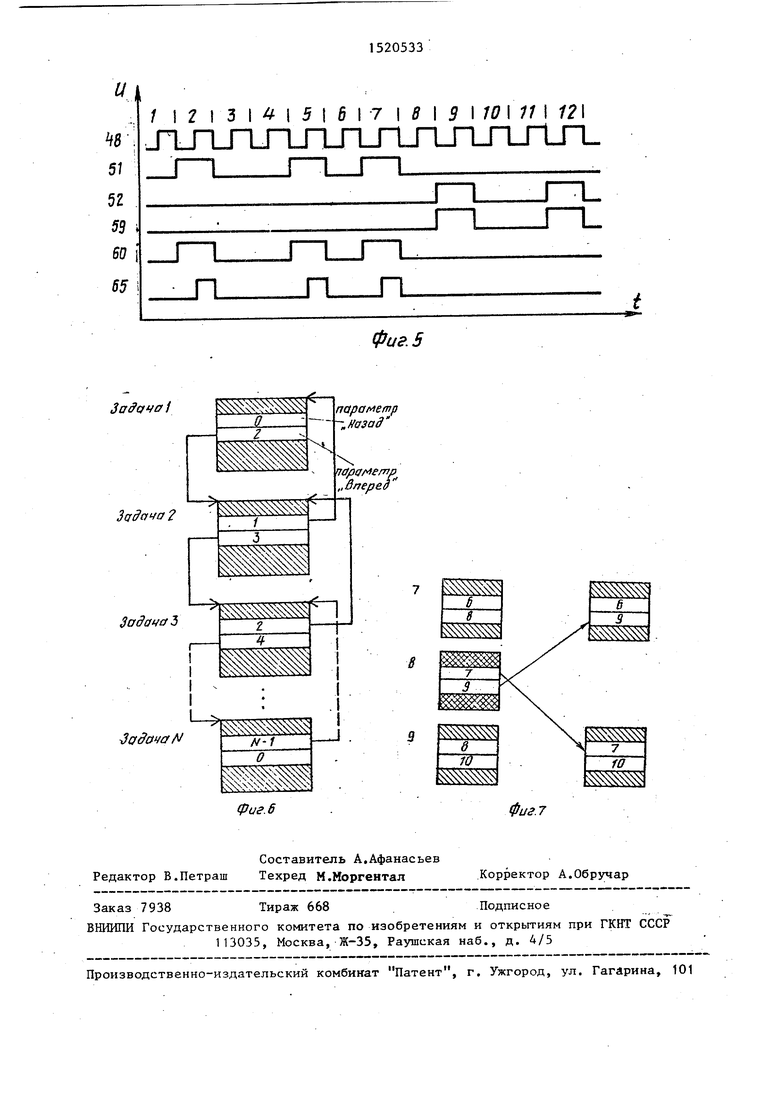

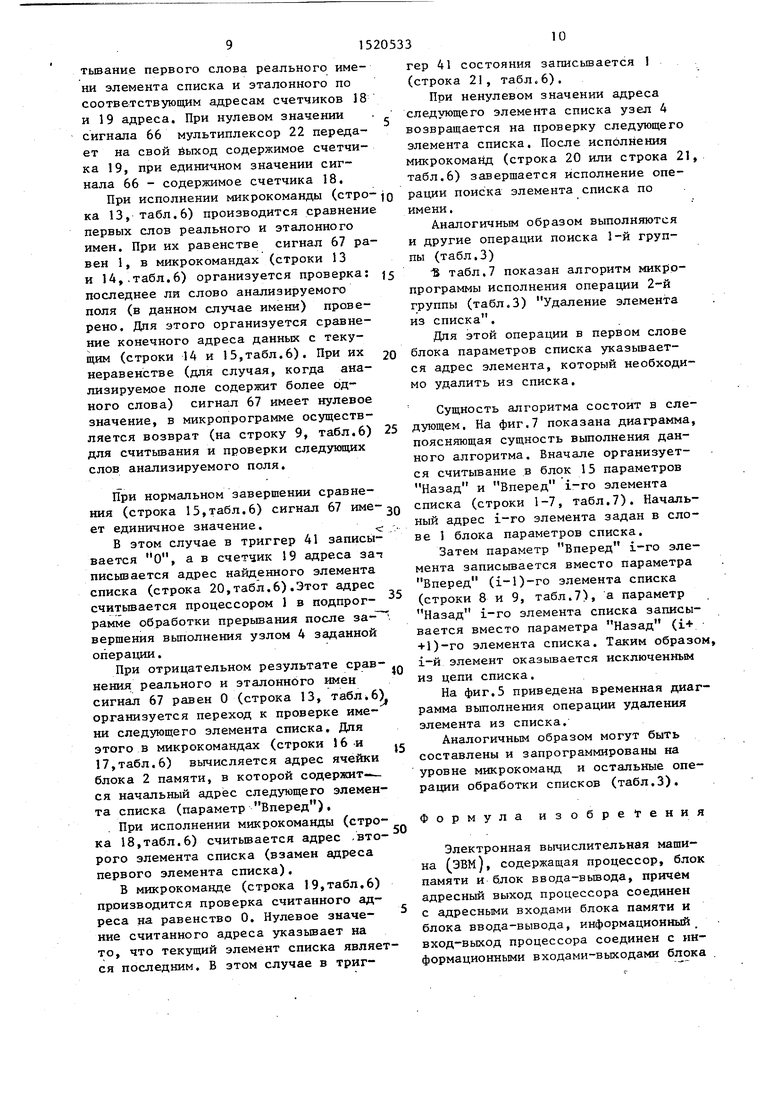

На фиг.1 изображена схема ЭВМ; на фиг.2 - схема блока обработки списков; на фиг.З - 5 - временные диаграммы работы ЭВМ; на фиг.6 - структура списка;на фиг.7 - диаграмма выполнения операции со списком.

ЭВМ (фиг.) содержит процессор 1, блок 2 памяти, блок 3 ввода-вывода, узел 4 обработки списков. ЭВМ имеет вход 5 сброса, вхиды 6 и 7 синхронизации, информационные выходы 8 и вхо 9, управляющие вькоды 10 и 11, управляющие входы 12 и 13,

Узел 4 обработки списков (фиг.2) содержит блок 14 памяти параметров, блок 15 памяти операндов, информационые регистры 16 и 17, счетчики 18 и 19 адреса, сумматор 20, блок 21 срав

нения, мультиплексор 22 адреса, дешифраторы 23 и 24 адреса, блок 25 памяти микрокоманд регистр 26 операций, регистр 27 адреса микрокоманд, мультиплексор 28 условий, управляющие дешифраторы 29 - 31, шиннне коммутаторы 32 - 34, шинные формирователи 35 - 39, управляющий регистр 40 триггер 41 состояния, триггер 42 захвата, триг гер 43 прерывания, элементы И 44 и 45, элементы ИЛИ 46 и 47.

На временных диаграммах работы микроэвм (фиг.3-5) обозначены: 48 - импульсы на входах 6 и 7 синхронизации ЭВМ; 49 - сигнал на адресном выходе процессора 1; 50 - сигнал данны на информационном входе-выходе процессора 1; 5 и 52 - сигналы на входах чтения и записи блока 2 памяти соответственно; 53 - сигнал на выход управления вьшодом процессора 1; 54 и 55 - сигналы на входе подтверждения захвата и выходе подтверждения микропроцессора 1 соответственно; 56 - сигнал на выходе дешифратора 23 адреса; 57 и 58 - сигналы на выходах триггеров 42 и 43 соответственно; 59 и 60 - сигналы на втором и третье выходах управляющего регистра 40. соответственно; 61 - сигнал на входе записи регистра 26 операций; 62 и 63 - сигналы на счетных входах прибавления счетчиков 18 и 19 адреса со

o

0

5

5

ответственно; 64 и 65 - сигналы на входах управления записью-чтением блоков 14 и 15 памяти соответственно; 66 - сигнал на входе управления мультиплексора 22 адреса; 67 - сигнал на выходе блока 21 сравнения. ЭВМ работает следующим образом. Для приведения ЭВМ в исходное состояние на вход 5 сброса подается сигнал сброса, в результате чего регистры 26, 27 и 40, триггеры 41-43 устанавливаются в ноль.

На входы 6 и 7 синхронизации ЭВМ подается серия импульсов.

Работа ЭВМ основана на вьшолнении программ (набора команд), хранимой в блоке 2 памяти. В свою очередь, каждый цикл операции вьшолняется в течение нескольких тактов. Длительность такта определяется периодом следования импульсов 48. Процессор 1 осуществляет потактовое выполнение команд на уровне микрокоманд.

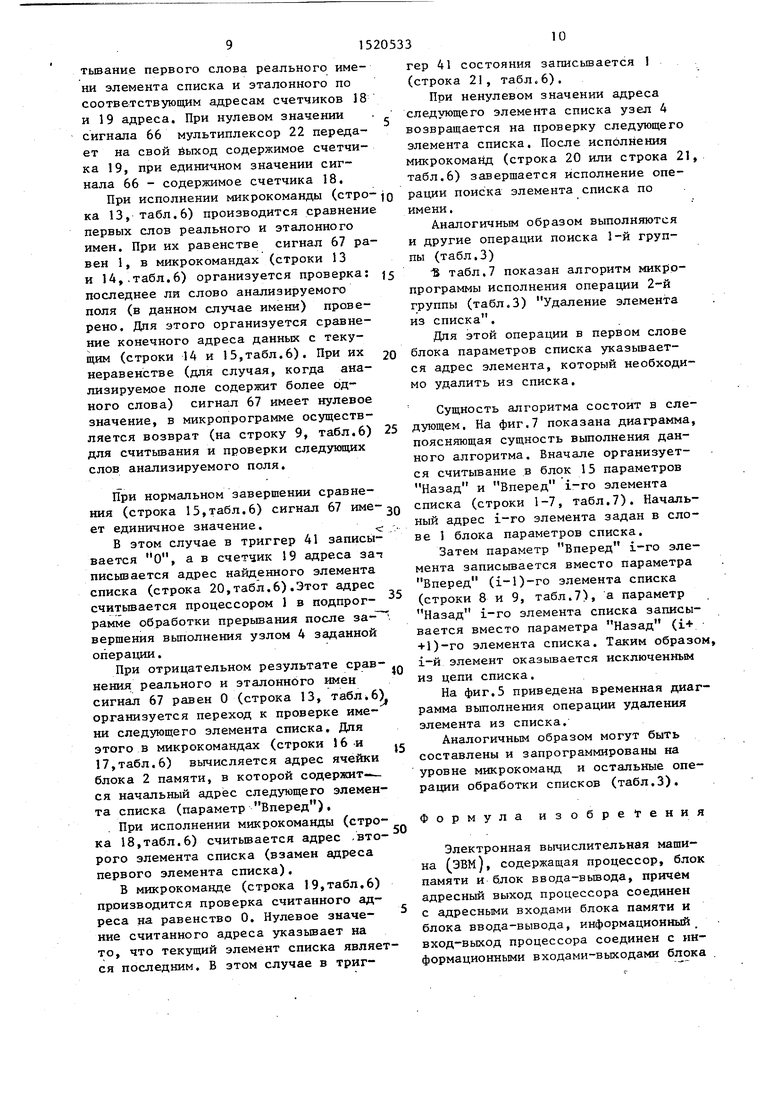

Рассмотрим работу ЭВМ с учетом узла 4. На фиг.6 показана очередь задач, представленная в виде двухсвязного реверсивного списка. В каждом элементе списка имеются определен0 ные поля, используемые при выполнении процедур со списками. В поле параметра Вперед и в поле параметра Назад указываются начальные адреса соответственно следующего

5 и предьздущего элементов списка. На фиг.6 (для наглядности) в этих полях указаны номера соответствующих элементов списка. Поле параметра Назад первого элемента списка

0 равно О, и, соответственно, равно

нулю поле параметра Вперед последнего элемента списка.

Кроме того, различные информационные поля, например, имя, приоритет

5 и другие могут использоваться при вьтолнении операций со списками.

Какая-либо операция со списками выполняется в следующем порядке. Основная программа (программа операци0 онной системы) формирует в оперативной области блокА 2 памяти блок параметров списка.

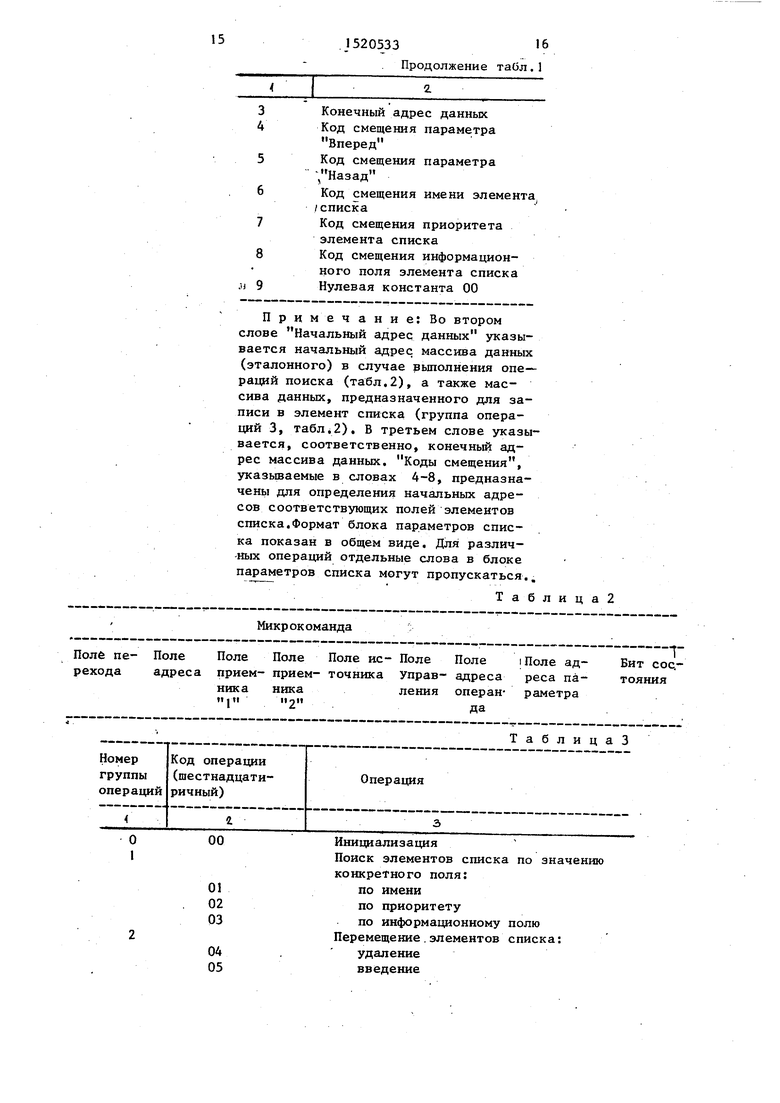

Структура и формат этого блока приведены в табл.1.

После этого для указания узлу 4 о, необходимости выполнения операции со списками данных в основной программе предусматривается выполнение

51

команды Вьшод. Процессор 1 приступает к выполнению этой команды (фиг.З), Для упрощения выполнение этой команды (фиг.З) показано только функционально. На шину адреса процессор 1 устанавливает адрес узла 4

из адресов устройств ввода-вы- зарезервированный за узлом 4) шину данных процессор 1 вьщает

(один вода,

На

адрес блока параметров списка (местонахождение его в блоке 2 памяти) . При вьщаче процессором 1 сигнала 53 дешифратор 23 адреса вырабатьшает сигнал 56.

До этого момента времени узел 4 находится в пассивном режиме в ожидании единичного значения сигнала 56 - сигнала Старт. Единичным сигналом 56 адрес блока параметров спис ка записьшается в счетчик 19 адреса. Из блока 25 памяти микрокоманд считывается первая микрокоманда активного режима работы узла 4.

Формат микрокоманды показан в табл.2.

В поле адреса задается адрес следующей микрокоманды. Младший разряд поля адреса поступает с третьего выхода блока 25 памяти микрокоманд на первый информационный вход мультиплексора 28. Остальная часть поля адреса поступает с первого выхода блока 25 памяти микрокоманд на информационный вход (без младшего разряда) регистра 27.

Поле перехода поступает с второго выхода блока 25 памяти микрокоманд на управляющий вход мультиплексора 28 условий.

В полях приемников 1 и 2 содержится номер компонента (регистра счетчика или триггера), куда в данной микрокоманде должен быть занесен соответствующий операнд или куда должно быть вьодано управляющее воздействие.

Поля приемников 1 и 2 поступают с четвертого и пятого выходов блока 25 на управляющие входы дешифраторов 29 и 30 соответственно. В поле источника содержится номер шинного коммутатора или формирователя, который в данной микрокоманде выдает информацию на шину данных.

Доле источника поступает на управляющий вход дешифратора 31.

В поле адреса операнда и в поле адреса параметра указьшаются адреса

0

5

5

0

0

5

0

5

0

5

операндов и параметров, содержащихся в блоках 15 и 14 памяти соответственно .

В поле управления содержатся коды, используемые для вьщачи управляющих сигналов. Поле управления поступает на информационный вход управляющего регистра 40.

Бит состояния характеризует зультат выполнения операций со списками. Бит состояния поступает на вход триггера 41.

На временной диаграмме (фиг.3-6) работы узла 4 обработки списков по выполнению алгоритмов операций (табл.4,6 и 7) обозначены арабскими цифрами (каждому такту соответствует выполнение определенной микрокоманды) . Длительность такта определяется периодом следования импульсов 48.

По импульсу с выхода дешифратора 30 устанавливается в единицу триггер 42 захвата (сигнал 57). Узел 4 переходит в режим ожидания единичного значения сигнала 54. После завершения выполнения очередного цикла операции процессор 1 анализирует состояние сигнала 57 на входе захвата. ; При единичном значении сигнала 57 про- цессор 1 вырабатьшает сигнал 54 и переходит в режим ожидания (режим ожида-. ния обнуления сигнала 57) и освобождает адресную шину, шину данных и шину управления.Одновременно по единичному сигналу 54 открываются шинные формирователи 36 - 38.Адрес с выхода счетчика 19 адреса поступает через мультиплексор 22 на шину адреса.

По единичному сигналу 60 и, соответственно, сигналу 51 из блока 2 памяти считывается первое слово блока параметров списка (код операции) и сигналом 61 записывается в регистр 26 операций. До коду в регистре 26 из блока 25 памяти микрокоманд считьюа- ется первая микрокоманда выполнения требуемой операции,

Перечень операций над списками, выполняемых блоком 4, представлен в табл.3.

В начале работы ЭВМ первой опера- цией выполняемой блоком 4, является Инициализация. Блок параметров с пис- ка для данной операции не содержит 1, 2,и 3-го слов (та6л,1). Слова с 4-го по 8-е для каждой определенной структуры списков имеют постоянные значения. Перед началом работы со спискми при выполнении операции Инициализация эти константы (а также константа 00, слово 9) вводятся в блок 14 памяти параметров (фиг.З).

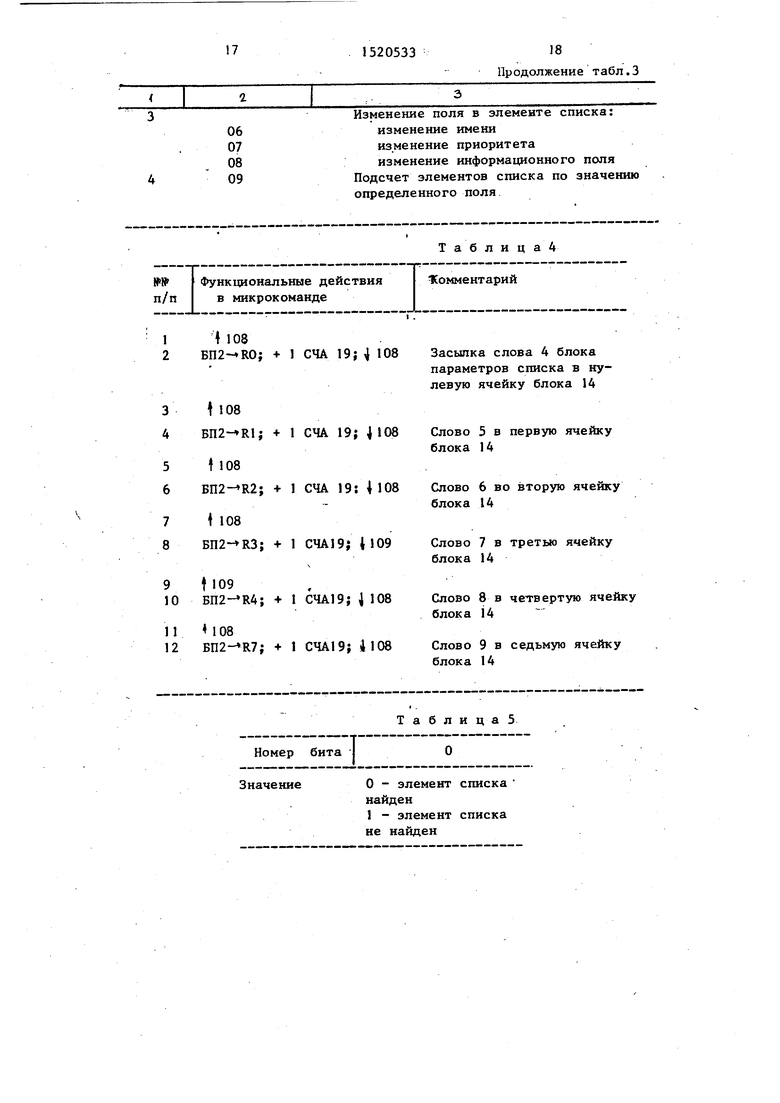

В табл.4 показан алгоритм микропрограммы выполнения операции Инициализация.

В табл.4 и последующих таблицах с алгоритмами микропрограмм приняты следующие обозначения:

Ri 0,1,2... - обозначение и нумерация ячеек бло ка 14;

Li Of,2.,, - обозначение и нумерация ячеек блока 15j

т - установка в 1 соответствующего сигнала;

I - установка в О соответствующего сигнала;

- - пересылка операнда;

+1 - прибавление единицы к содержимому счетчиков. Остальные обозначения.составлены из сокращенных наименований компонентов ЭВМ и их позиционных номеров (например, ИР16 - информационный регистр 16; СМ20 - сумматор 20 и т.д.). Каж- дои строке в алгоритме соответствует определенная микрокоманда.

По сигналу 63 производится пересчет счетчика 19 адреса, по сигналам 60 и 51 считывается необходимое ело- во и единичным сигналом 64 записывается в соответствующую ячейку блока 14, адрес которой в каждом такте определяется полем адреса параметра соответствующей микрокоманды. После записи параметров в блок 14 завершается выполнение операции Инициализация.

После завершения выполнения каждой операции сигналом с выхода дешиф ратора 29 устанавливается в ноль триггер 42 (сигнал 57). Узел 4 освобождает системные шины для процессора 1 .

В следующем такте по сигналу с вы хода дешифратора 29 устанавливается в единицу триггер 43 (сигнал 58), а в триггер 41 записывается бит состояния, определяющий условия завершения

заданной операции. При нормальном завершении операции бит состояния имеет нулевое значение.

Формат бита состояния узел 4 показан в табл.5.

Узел 4 переходит в режим ожидания следующей команды на выполнение какой-либо операции.со списками.

При нулевом значении сигнала 57 процессор 1 устанавлив ает в ноль сигнал 54 и переходит в активный режим. При единичном сигнале 58 процессор 1 вырабатывает сигнал 55 и переходит на подпрограмму обработки прерьша- ния. По сигналу 55 устанавливается в ноль триггер 43. В процессе обработки прерьгоания процессор 1 считьшает бит состояния из триггера 41 для анализа (для упрощения на временной диаграмме данная процедура не показана).

Рассмотрим выполнение одной из операций 1-й группы (табл.3), например Поиск элемента списка по имени.

Блок параметров списка (табл.1) для данной группы операций содержат первые 4 слова (с 0-го по 3-е). Во 2-м и 3-м словах блока параметров списка содержатся начальный и конеч- ный адреса местонахождения в блоке 2 памяти информационного поля (эталонного) , по которому производится поиск .

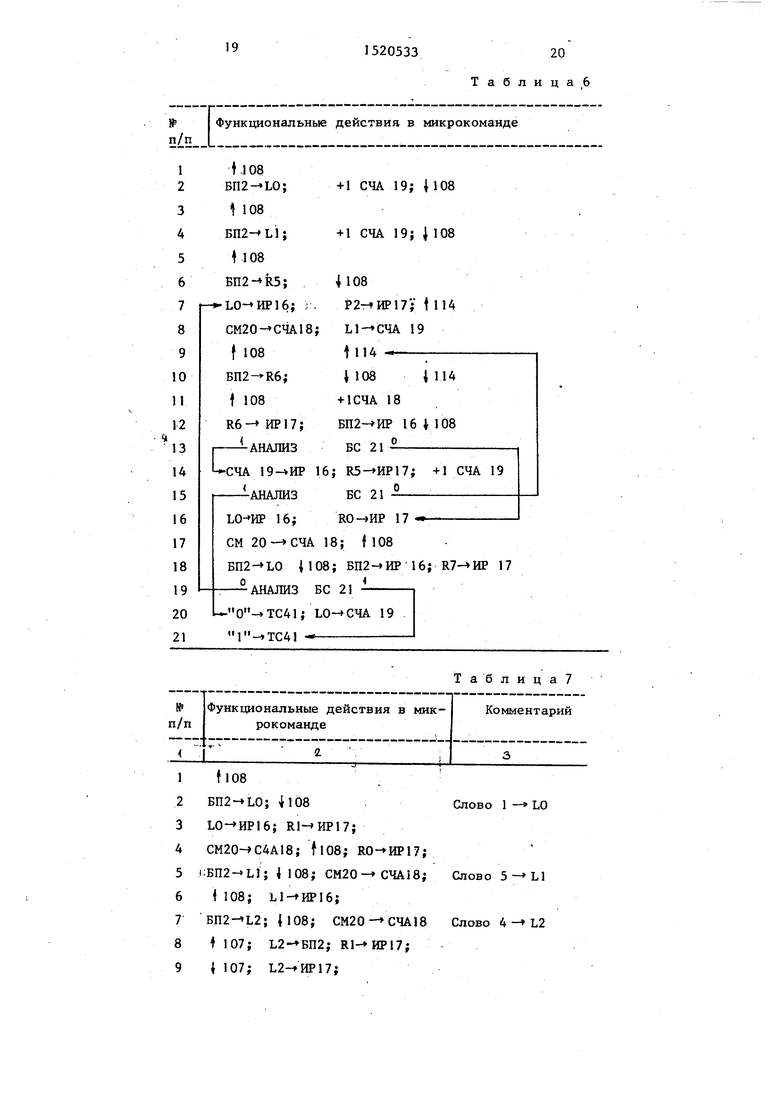

в табл.6 показан алгоритм микропрограммы выполнения рассматриваемой операции поиска.

На фиг.4 показана временна диаграмма выполнения этого алгоритма.

Вначале вьшолнения микропрограм- - мы (строки 1-6, табл.10) производится считьтание соответствующих слов блока параметров списка из блока 2 памяти в соответствующие ячейки блоков 14 и 15 (слово , слово слово ).

При выполнении микрокоманд (строки 7 и 8, табл.6) определяется адрес имени анализируемого элемента списка. Этот адрес определяется путем . суммирования начального адреса элемента списка с постоянным кодом соответствующего смещения. Полученный . адрес засылается в счетчик 18 адреса. В счетчик 19 адреса засылается адрес эталонного имени, по которому производится поиск.

При выполнении микрокоманд (строки 9 - 12, табл.6) производится считывание первого слова реального имени элемента списка и эталонного по соответствующим адресам счетчиков 18 и 19 адреса. При нулевом значении сигнала 66 мультиплексор 22 передает на свой быход содержимое счетчика 19, при единичном значении сигнала 66 - содержимое счетчика 18,

При исполнении микрокоманды (стро- д рации поиска элемента списка по

ка 13, табл,6) производится сравнение первых слов реального и эталонного имен. При их равенстве сигнал 67 равен 1, в микрокомандах (строки 13 и 14,.табл,6) организуется проверка: 5 последнее ли слово анализируемого поля (в данном случае имени) проверено. Для этого организуется сравнение конечного адреса данных с текущим (строки 14 и 15,табл.6). При их 20 неравенстве (для случая, когда анализируемое поле содержит более одного слова) сигнал 67 имеет нулевое значение, в микропрограмме осуществляется возврат (на строку 9, табл,6) 25 для считьшания и проверки следующих слов анализируемого поля.

При нормальном завершении сравнения (строка 15,табл,6) сигнал 67 ет единичное значение,. ,

В этом случае в триггер 41 записывается О, а в счетчик 19 адреса за-г письшается адрес найденного элемента списка (строка 20,табл.6).Этот адрес считьшается процессором 1 в подпрограмме обработки прерьшания после вершения вьтолнения узлом 4 заданной операции.

При отрицательном результате сравнения реального и эталонного имен сигнал 67 равен О (строка 13, ) организуется переход к проверке имени следующего элемента списка. Для этого в микрокомандах (строки 16 и 17,табл,6) вычисляется адрес ячейки блока 2 памяти, в которой содержит-- ся начальный адрес следующего элемента списка (параметр Вперед),

. При исполнении микрокоманды (строка 18,табл,6) считьгоается адрес .второго элемента списка (взамен адреса первого элемента списка).

В микрокоманде (строка 19,табл,6) производится проверка считанного адреса на равенство 0. Нулевое значение считанного адреса указьшает на то, что текущий элемент списка является последним. В этом случае в тригW

t5

50

имени.

Аналогичным образом выполняют и другие операции поиска 1-й гру пы (табл.3)

В табл,7 показан алгоритм мик программы исполнения операции 2группы (табл.3) Удаление элемен из списка.

Для этой операции в первом сл блока параметров списка указьшае ся адрес элемента, который необх мо удалить из списка.

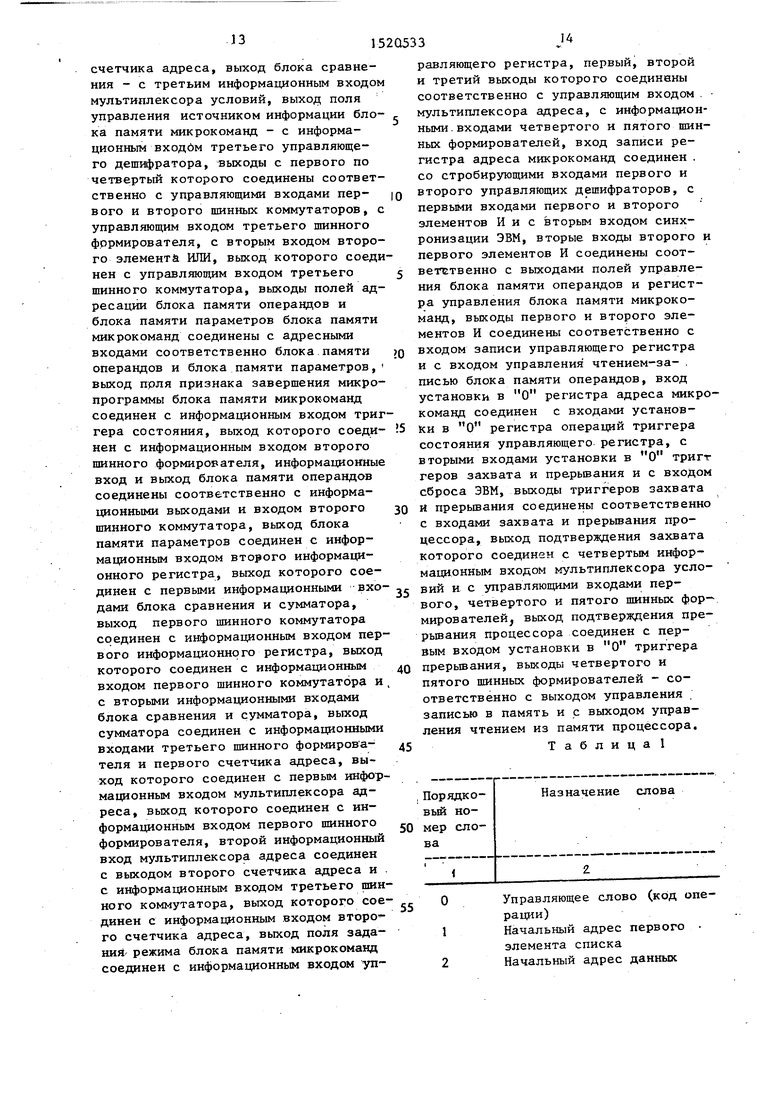

Сущность алгоритма состоит в дующем. На фиг,7 показана диагра поясняющая сущность выполнения д ного алгоритма. Вначале организу ся считывание в блок 15 параметр Назад и Вперед i-ro элемента списка (строки 1-7, табл,7), Нач ный адрес i-ro элемента задан в ве 1 блока параметров списка.

Затем параметр Вперед i-ro мента записьшается вместо параме Вперед (i-l)-ro элемента списк (строки 8 и 9, табл.7), а параме Назад i-ro элемента списка зап вается вместо параметра Назад +1)-го элемента списка. Таким об i-и элемент оказывается исключен из цепи списка,

На фиг,5 приведена временная рамма выполнения операции удален элемента из списка.

Аналогичным образом могут быт составлены и запрограммированы н уровне микрокоманд и остальные рации обработки списков (табл,3)

Формула изобретен

Электронная вычислительная ма на (ЭВМ), содержащая процессор, памяти и блок ввода-вьшода, прич адресный выход процессора соедин с адресными входами блока памяти блока ввода-вывода, информационн вход-выход процессора соединен с формационными входами-выходами бл

гер 41 состояния записьшается 1 (строка 21, табл.6).

При ненулевом значении адреса следующего элемента списка узел 4 возвращается на проверку следующего элемента списка. После исполнения микрокоманд (строка 20 или строка 21, табл.6) завершается исполнение опе50 5

Q ,

5

0

имени.

Аналогичным образом выполняются и другие операции поиска 1-й группы (табл.3)

В табл,7 показан алгоритм микропрограммы исполнения операции 2й группы (табл.3) Удаление элемента из списка.

Для этой операции в первом слове блока параметров списка указьшает- ся адрес элемента, который необходимо удалить из списка.

Сущность алгоритма состоит в следующем. На фиг,7 показана диаграмма, поясняющая сущность выполнения данного алгоритма. Вначале организуется считывание в блок 15 параметров Назад и Вперед i-ro элемента списка (строки 1-7, табл,7), Начальный адрес i-ro элемента задан в слове 1 блока параметров списка.

Затем параметр Вперед i-ro элемента записьшается вместо параметра Вперед (i-l)-ro элемента списка (строки 8 и 9, табл.7), а параметр Назад i-ro элемента списка записывается вместо параметра Назад (i+ +1)-го элемента списка. Таким образом, i-и элемент оказывается исключеннь М из цепи списка,

На фиг,5 приведена временная диаграмма выполнения операции удаления элемента из списка.

Аналогичным образом могут быть составлены и запрограммированы на уровне микрокоманд и остальные операции обработки списков (табл,3),

Формула изобретения

Электронная вычислительная машина (ЭВМ), содержащая процессор, блок памяти и блок ввода-вьшода, причем адресный выход процессора соединен с адресными входами блока памяти и блока ввода-вывода, информационный вход-выход процессора соединен с информационными входами-выходами блока .

памяти и блока ввода-вывода, выход управления чтением из памяти и выход управления записью в память процессора соединены соответственно с входом чтения и с входом записи блока , выход управления вводом и выход управления вьшодом процессора соединены соответственно с входом

чтения и с входом записи блока ввода-; Q входом-выходом процессора, второй вывьшода, информационные выход и вход которого соединены соответственно с информационными входом и выходом ЭВМ, выход сопровождения вьтода и выход квитирования ввода блока ввода-вьшода |5 соединены соответственно с дополнительными вькодами ЭВМ, вход квитирования вывода и вход сопровождения . ввода блока ввода-вывода соединены соответственно с одноименными входами ЭВМ, вход сброса процессора соединен с входом сброса блока ввода-вьшо- да и с входом сброса ЭВМ, вход синхронизации процессора соединен с вхо-5 дом синхронизации ЭВМ, о т л и ч а ю- щ а я с я тем, что, с целью повышения производительности ЭВМ при обработке списковых структур данных, она дополнительно содержит блок памяти

20

25

ход второго дешифратора адреса соединен с первым входом второго элемента ИЛИ, выход регистра операций соединен с входом старших разрядов адреса блока памяти микрокоманд, выход поля адреса следующей микрокоманды которог го соединен с информационным входом старших разрядов регистра адреса микрокоманд, выход поля выбора логического условия блока памяти микрокоманд соединен с управляющим входом мультиплексора услов ий, выход которого соединен с информационным входом младшего разряда регистра адреса микрокоманд, выход которого соединен с входом младших разрядов адреса блока памяти микрокоманд, поля младшего разряда адреса микрокоманды которого соединены с вторым информационным входом мультиплексора условий, выход поля управления первым приемником результата блока памяти микрокоманд соединен с информационным входом первого управляющего дешифратора, выходы с первого по седьмой которого соединены соответственно с входом записи регистра операций, с входом записи первого счетчика адрепса, со счетным входом первого счетчика адреса, с входом управления записью- чтением блока памяти параметров, с первым входом установки в О триггера захвата, с входом записи первого информационного регистра, с входом зациси триггера состояния и с входом установки в 1 триггера прерьшания, выход поля управления вторым приемником результата блока памяти микрокоманд соединен с информационным входом второго управляющего дешифратора , выходы с первого по четвертый которого соединен соответственно с вторым входом первого элемента ИЛИ, со счетным входом второго счетчика адреса, с входом записи второго информационного регистра, и с входом установки в 1 триггера захвата, выход первого элемента ИЛИ соединен с входом записи второго

параметров, блок памяти операндов, первый и второй информационные регистры, первый и второй счетчики адреса, сумматор, блок сравнения, мультиплексор адреса, первый и второй дешифраторы адреса, блок памяти микрокоманд, регистр операций, регистр адреса микрокоманд, мультиплексор условий, первый, второй и третий управляющие дешифраторы, первый,ивторой и третий шинные коммутаторы, пер-; вый - пятый пшнные формирователя, управляющий регистр, триггер состояния,, триггер захвата, триггер прерывания, первый и второй элементы И, первый и второй элементы ИЛИ, причем информационные входы первого и второго дешифраторов адреса соединены с выходом первого шинного формирователя и с адресным выходом процессора, стробирующие входы первого и второго дешифраторов адреса соединены соответственно с выходом упраления вьшодом и с выходом управления вводом процессора, выход первого дешифратора адреса соединен с первым , информационным входом мультиплексора условий и с первым входом первого элемента ИЛИ, первый выход второго . дешифратора адреса соединен с управляющим входом второго шинного формирователя, выход которого соединен с выходом первого шинного формировате- .ля, с информационными входами-выходами первого, второго и третьего шинных коммутаторов, с информационными, входами блока памяти параметров и регистра операций, с информационным

5

0

5

0

5

0

5

0

5

ход второго дешифратора адреса соединен с первым входом второго элемента ИЛИ, выход регистра операций соединен с входом старших разрядов адреса блока памяти микрокоманд, выход поля адреса следующей микрокоманды которог го соединен с информационным входом старших разрядов регистра адреса микрокоманд, выход поля выбора логического условия блока памяти микрокоманд соединен с управляющим входом мультиплексора услов ий, выход которого соединен с информационным входом младшего разряда регистра адреса микрокоманд, выход которого соединен с входом младших разрядов адреса блока памяти микрокоманд, поля младшего разряда адреса микрокоманды которого соединены с вторым информационным входом мультиплексора условий, выход поля управления первым приемником результата блока памяти микрокоманд соединен с информационным входом первого управляющего дешифратора, выходы с первого по седьмой которого соединены соответственно с входом записи регистра операций, с входом записи первого счетчика адрепса, со счетным входом первого счетчика адреса, с входом управления записью- чтением блока памяти параметров, с первым входом установки в О триггера захвата, с входом записи первого информационного регистра, с входом зациси триггера состояния и с входом установки в 1 триггера прерьшания, выход поля управления вторым приемником результата блока памяти микрокоманд соединен с информационным входом второго управляющего дешифратора , выходы с первого по четвертый которого соединен соответственно с вторым входом первого элемента ИЛИ, со счетным входом второго счетчика адреса, с входом записи второго информационного регистра, и с входом установки в 1 триггера захвата, выход первого элемента ИЛИ соединен с входом записи второго

счетчика адреса, выход блока сравнения - с третьим информационным входом мультиплексора условий, выход поля управления источником информации блока памяти микрокоманд - с информационным в ход 6м третьего управляющего дешифратора, вькоды с первого по четвертый которого соединены соответственно с управляющими входами пер- вого и второго шинных коммутаторов, с управляющим входом третьего шинного формирователя, с вторым входом второго элемента ИЛИ, вькод которого соединен с управляющим входом третьего шинного коммутатора, выходы полей адресации блока памяти операндов и блока памяти параметров блока памяти микрокоманд соединены с адресными входами соответственно блока памяти операндов и блока памяти параметров, выход прля признака завершения микропрограммы блока памяти микрокоманд соединен с информационным входом триггера состояния, выход которого соеди- иен с информационным входом второго шинного формирователя, информационные вход и выход блока памяти операндов соединены соответственно с информационными выходами и входом второго шинного коммутатора, выход блока памяти параметров соединен с информационным входом второго информационного регистра, выход которого соединен с первыми информационными вхо- дами блока сравнения и сумматора, выход первого шинного коммутатора соединен с информационным входом первого информационного регистра, выход которого соединен с информационным входом первого шинного коммутатора и с вторыми информационными входами блока сравнения и сумматора, выход сумматора соединен с информационными входами третьего шинного формирова- теля и первого счетчика адреса, выход которого соединен с первым информационным входом мультиплексора адреса, выход которого соединен с информационным входом первого шинного формирователя, второй информационный вход мультиплексора адреса соединен с выходом второго счетчика адреса и . с информах ионным входом третьего шинного коммутатора, выход которого сое- динен с информационным входом второ- го счетчика адреса, выход поля зада- ниЯ режима блока памяти микрокоманд соединен с информационным входом управляющего регистра, первый, второй и третий выходы которого соединены соответственно с управляющим входом , мультиплексора адреса, с информационными, входами четвертого и пятого шинных формирователей, вход записи регистра адреса микрокоманд соединен . со стробирующими входами первого и второго управляющих дешифраторов, с первыми входами первого и второго элементов И и с вторым входом синхронизации ЭВМ, вторые входы второго и первого элементов И соединены соответственно с выходами полей управления блока памяти операндов и регистра управления блока памяти микрокоманд, выходы первого и второго элементов И соединены соответственно с входом записи управляющего регистра и с входом управления чтением-за- . писью блока памяти операндов, вход установки в О регистра адреса микрокоманд соединен с входами установки в О регистра операций триггера состояния управляющего регистра, с вторыми входами установки в О тригт геров захвата и прерьшания и с входом сброса ЭВМ, выходы триггеров захвата и прерьшания соединены соответственно с входами захвата и прерьшания процессора, выход подтверждения захвата которого соединен с четвертым информационным входом мультиплексора условий и с управляющими входами первого, четвертого и пятого шинных формирователей, выход подтверждения пре- рьюания процессора соединен с первым входом установки в О триггера прерьтания, выходы четвертого и пятого шинных формирователей - соответственно с выходом управления . записью в память и с выходом управления чтением из памяти процессора. Таблица 1

Управляющее слово (код операции)

Начальный адрес первого элемента списка

Начальный адрес данных

15

j520533 6

Продолжение табл.1

3Конечный адрес данных

4Код смещения параметра Вперед

5Код смещения параметра ; Назад

6Код смещения имени элемента /списка

7Код смещения приоритета элемента списка

8Код смещения информационного поля элемента списка

:ч 9 Нулевая константа 00

При м е ч а и и е: Во втором слове Начальный адрес данных указывается начальный адрес массива данных (эталонного) в случае рыполнеиия операций поиска (табл.2), а также массива данных, предназначенного для записи в элемент списка (группа операций 3, таблi2). В третьем слове указывается, соответственно, конечный адрес массива данных. Коды смещения, указьшаемые в словах 4-8, предназначены для определения начальных адресов соответствующих полей элементов списка.Формат блока параметров списка показан в общем виде. Для различ- -ных операций отдельные слова в блоке параметров списка могут пропускаться.

Та

Микрокоманда

Полб пе- Поле Поле Поле Поле ис- ПолеПоле|Поле ад- рехода адреса прием- прием- точника Управ-адресареса паника ника ленияоперан-раметра 1 2 да

конкретного поля:

по имени

по приоритету

по информационному полю Перемещение.элементов списка:

удаление

введение

Г

Бит сос.- тояния

ТаблицаЗ

17

1Ч 108

2БП2- ЕО; + 1 СЧА 19; 4 108

t 108

+ 1 СЧА 19; 4108

i 108

+ 1 СЧА 19: 108

И08

+ 1 СЧА19; И09

t 109

+ 1 СЧА19; 108

108

+ 1 СЧА19; 4108

Номер бита

Значение

1520533

18

Продолжение табл.3

Засыпка слова 4 блока параметров списка в нулевую ячейку блока 14

Слово 5 в первую ячейку блока 14

Слово 6 во вторую ячейку блока 14

Слово 7 в третью ячейку блока 14

Слово 8 в четвертую ячейку блока 14

Слово 9 в седьмую ячейку блока 14

Т а б л и ц а 5 О

0- элемент списка найден

1- элемент списка не найден

19

1tl08

2БП2- ЬО; 108

3LO- HP16; RMHP17;

4СМ20- С4А18; fl08; RO- HP17;

5|. И08; CM20- C4Ai8;

6 108; L1- HP16;

7БП2- Ь2; (108; СМ20- СЧА 8

8f 107; R1- HPI7;

9( 107; Ь2- ИР17;

152053320

Таблица 6

Таблица

Слово 1 - LO

Слово 5 - L1

Слово 4 - L2

10СМ20- СЧА18;

11f 107;

12 4 107

Продолжение табл.7

фиеЪ

Saffcf o /

napar emp

, Назад

af)c f4emp „Bftepea

a ovff/

Фиг. 5

8

| Микропроцессорные средства .и системы, 1987, № 4, с.74 | |||

| Микропроцессорные средства и системы, 1987, № 5, с.76. |

Авторы

Даты

1989-11-07—Публикация

1988-04-12—Подача