мого счетчиков, выходы переносов второго счетчика соединены соответственно с информационными входами второго коммутатора, выход которого подключён к счетному входу третьего счетчика и к нулевому входу триггера, выходы переносов третьего-счетчика подключены еоответственно к информационным входам.третьего коммутатора,, выход которого подключен к счетному входу четвертого счетчика и к единичному входу триггера, выходы разрядов четвертого счетчика подключены соответственно к информационным входам четвертого коммутатора, выходы которого соединены с второй группой входов сумматора содержимого, счетчиков, единичный выход триггера подключен к второму входу первого элемента И, выход которого соединен с входом первого элемента НЕ, выход сумматора содержимого счетчиков соединен с первым адресным входом блока памяти коэффициентов преобразования, первый управляющий вход, первый информационный вход и второй адресный вход которого являются соответственно управляющим входом запигси, вторым информационным входом и адресным входом устройства, первый и второй управляющие входы,задания режима которого подключены соответственно к четвертому и пятому входам блока буферной памяти, второй информационный вход которого является третьим информационным входом устройства, первые входы с первого по четвертый сумматоров соединены соответственно с первого по четвертый выходами кодов блока памяти коэффициентов преобразования, выходы сумматоров с первого по четвертый соединены соответственно с информационными входами с первого по четвертый регистров, пятый выход кода блока памяти коэффициентов преобразования соединен с ,|вторым входом первого сумматора и с первьп4 информационным входом пятого регистра, шестой выход кода соединен .с вторым входом второго сумматора и первым входом пятого сумматора, седьмой выход кода подключен к второму входу третьего сумматора и к первому .информационному входу шестого регистра, восьмой выход кода подключен к второму входу четвертого сумматора и к первому входу шестого сумматора, первые управляющие входы записи пятого и шестого регистров подключены к выходу второго элемента И, вторые управляющие входы записи пятого и шестого регистров подключены к выходу третьего элемента И, управляющие входы записи с первого по четвертый регистров и третьи управляющие входы записи пятого и шестого регистров соединены с выходом четвертого элемента И, выход первого регистра подключен к второму информационному входу пятого регистра и к второму информационному входу блока памяти коэффициентов .преобразования, третий, четвертый и пятый информационные входы которого соединены соответственно с выходами второго, третьего и четвертого регистров, выход третьего регистра соединен с вторым информационным входом шестого регистра, выход пятого регистра подключен к первому адресному входу блока буферной памяти и к второму входу пятого сумматора, выход которого соединен с третьим информационным входом йятого регистра, выход шестого регистра подключен к второму адресному входу блока буферной памяти и к второму входу шестого сумматора, выход которого подключен к третьему информационному входу шестого регистра, выход первого элемента НЕ соединен с первым входом четвертого элемента И, второй вход которого и вход второго эле14ента НЕ соединены с выходом первого коммутатора, управляющий выход модификации адреса блока буферной памяти подключен к счетному входх первого счетчика и к входу первого элемента задержки, выход которого соединен с первыми входами второго и третьего элементов И и с третьим входом четвертого элемента И, выход которого через второй элемент задержки соединён с вторым управляющим входом блока памяти коэффициентов.преобразования, вторые входы второго и третьего элементов И соединены соответственно с выходом первого элемента И и с выходом второго элемента НЕ. Изобретение относится к вычислительной технике и может быть испольэовано при построении систем обработ ки видеоинформации. Известна система обработки видеоинформации, содержащая электронную вычислительную машину (ЭВМ), блоки ввода и вывода элементов изображения, блок связи с ЭВМ Л . Недостатком данной системы является то, что геометрическая обработка элементов изображений может производиться только непосредственно в ЭВМ. Это ограничивает функциональные возможности системы и уменьшает ее быстродействие (из-за ограниченной емкости оперативной памяти ЭВМ системы не позволяют вести геометрическую обработку элементов изображеНИИ со сканерных датчиков, дающих значительные геометрические искажения, кроме того, система имеет ограниченное быстродействие, так как в ЭВМ операции геометрической обработки (в основном алгоритмически простые) могут занимать значительное время). Известна также система обработки видеоинформации, содержащая универсальную ЭВМ высокого быстродействия блок связи с ЭВМ, оперативное запоминающее устройство большого объема устройства коммутации контроля и управления, блоки ввода и вывода элементов изображения, специализированные устройства обработки на базе мини-ЭВМ zj . Недостатком этой системы является отсутствие в ее составе специализированных вычислительных блоков, не обходимых дпя выполнения операций геометрической обработки элементов изображения, с использованием оперативного запоминакяцего устройства большого объема, что снижает быстродействие и надежность системы. Наиболее близ|сой по технической сущности к изобретению является сис тема обработки видеоинформации со сканирующих датчиков изображений, содержащая ЭВМ, устройство управлени вводом, в состав которого входит блок буферной памяти. Наличие в системе блока буферной памяти позволяет путем промежуточной буферизации эле ментов изображений осуществить согласование скоростей датчика изображ ;ния и канала ввода ЭВМ з, Недостатком данной систеьл является отсутствие возможности геометрической обработки элементов изображения с использованием блока буферной памяти, что снижает быстродействие. Цель изобретения - повьппение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее блок ввода элементов изображения, управляющий выход записи и информационный лыход которого подключены соответст-j венно к первым управлянщему и информационному входам блока буферной памяти, управляклций вход конца записи блока ввода элементов изображения соединен с первым управляющим выходом блока буферной памяти, информационный выход, второй и третий управляющие выходы которого соединены соответственно с информационным входом, управляющим входом конца считывания и управлякяцим входом разрешения считывания блока, вывода элементов изображения, управляющий выход считывания которого соединен с вторым управляющим входом блока буферной памяти, введены блок.памяти коэффициентов преобразования, блок формирования номера фрагмента изображения, включающий с первого по четвертый счетчики, с первого по четвертый коммутаторы, триггер, сумматор содержимого счетчиков, элемент И, регистр кода управления, блок формирования адресов элементов изображения, включающий с первого по шестой сумматоры, с первого по шестой регистры, блок управления формированием адресов, включающий два элемента НЕ, два элемента задержки, и три элемента И, причем выходы переносов первого счетчика соединены соответственно с информационными .входами первого, коммутатора, выход которого подключен к счетному входу второго счетчика и к первому входу первого элемента И, управляющие входы- с первого по четвертый коммутаторов, соединены соответственно с выходами, разрядов регистра кода управления, информационный вход которого является первым информационным входом устройства, выходы разрядов второго счетчика подключены соответственно к первой группе входов сумматора содержимого счетчиков, выходы переносов второго счетчика, соединены соответственно с информационными входами второго

коммутатора, выход которого подключен к счетному входу третьего счетчиica и к нулевому входу триггера, выходы переносов третьего счетчика подключены соответственно к информационным входам третьего коммутатора, выход которого подключен к счетному входу четвертого счетчика и к единичному входу триггера, выходы разрядов четве1ртого счетчика подключены соответственно к информационным входам четвертого коммутатора, выходы которого соединены с второй группой входов сумматора содержимого счетчиков, единичный выход триггера подключен к (второму входу первого элемента И, выз{од которого соединен с входом первого элемента НЕ, выход сумматора сОде жимого счетчиков соединен с первым аресным входом блока памяти коэффициентов преобразования, первый управляющий вход, первый информационный вход и второй адресный вход которого являются соответственно управняющим входом записи, вторым информационным входом и адресным входом устройства, первый.и второй управляющие входы задания режима которого подключены соответственно к четвертому и пятому входам блока буферной

памяти, второй информационный вход I -

которого является третьим информационным входом устройства, первые входы с первого по четвертый сумматоров соединены соответственно.с первого по четвертый выходами кодов блока памяти коэффициентов преобразования, выходы сумматоров с первого по четвертый соединены соответственно с информационными входами с первого по четвертый регистров, пятый выход кода памяти коэффициентов преобразования соединен с вторым входом первого сумматора и с первым информационным ВХОДОМпятого регистра,шестой выход кода соединен с вторым входом второго сумматора и с первым входом пятого сумматора, седьмой выход кода подключен, к второму вход третьего сумматора и к первому информационному входу шестого регистра, восьмой выход кода подключен к второму входу четвертого сумматора и к первому входу шестого сумматора, первые управляющие входы записи пятого и шестого регистров подключены к выходу второго элемента И, вторые уп равлякяцие входы записи пятого и шестого регистров подключены к выходу третьего элемента И, управлякяцие входы записи с первого по четвертый регистров и третьи управляющие входы записи пятого и шестого регистров соединены с выходом четвертого элемента И, выход первого регистра подключен к второму информационному входу пятого регистра и к второму информационному входу блока памяти коэффициентов преобразования, третий четвёртый и пятый информационные входы которого соединены соответственно с выходами второго, третьего и четвертого регистров выход третьего регистра соединен с вторым информационньм входом шестого регистра выход пятого регистра подключен к первому адресному входу блока буферной памяти и к второму входу пятого сумматора, выход которого соединен с третьим информационным входом пятого регистра, выход шестого регистра подключен к второму адресному входу блока буферной памяти и к второму входу шестого сумматора, выход котоjporo подключен к третьему информационному входу шестого регистра, выход первого элемента НЕ соединен с первым входом четвертого элемента И, второй вход которого.и вход второго элемента НЕ соединены с выходом первого коммутатора, управляющий выход модификации адреса блока буферной Памяти подключен к счетному входу первого счетчика и к входу первого элемента задержки, выход которого соединен с первыми входами второго и третьего элементов И и с третьим входом четвертого элемента И, выход которого через второй элемент задержки соединен с вторь управляющим входом блока памяти коэффициентов преобразования, вторые входы второго и третьего элементов И соединены соответственно с выходом .первого элемента Икс выходом второго элемента НЕ.

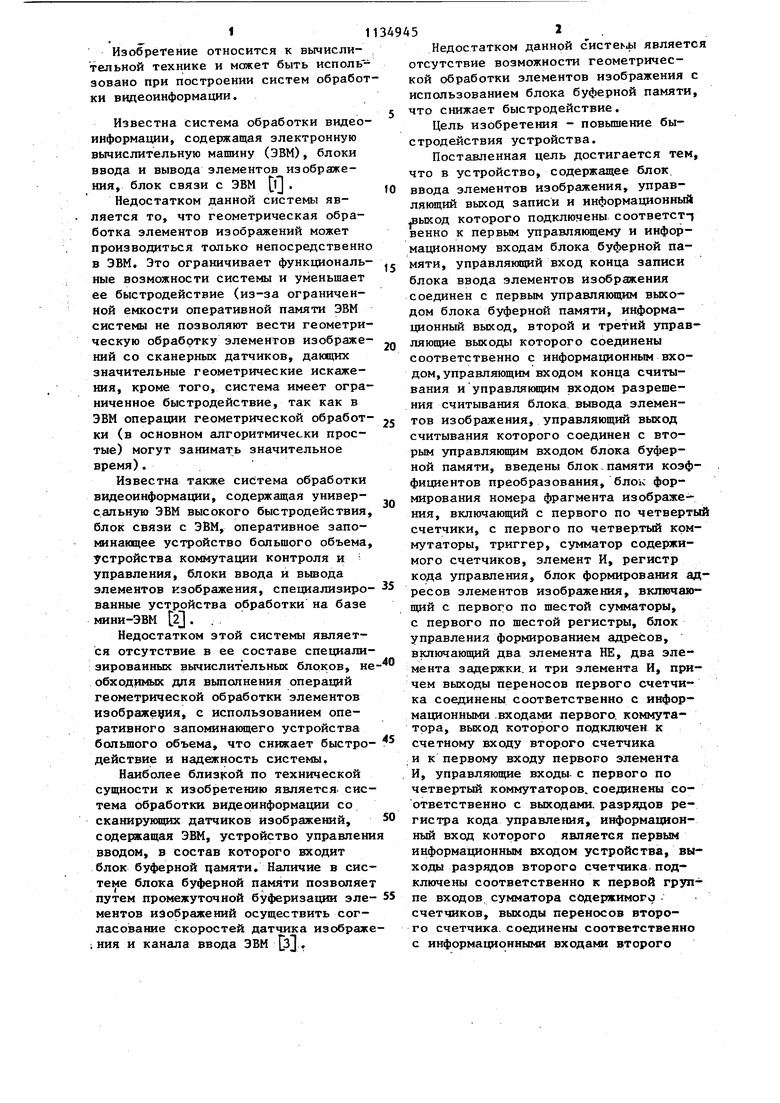

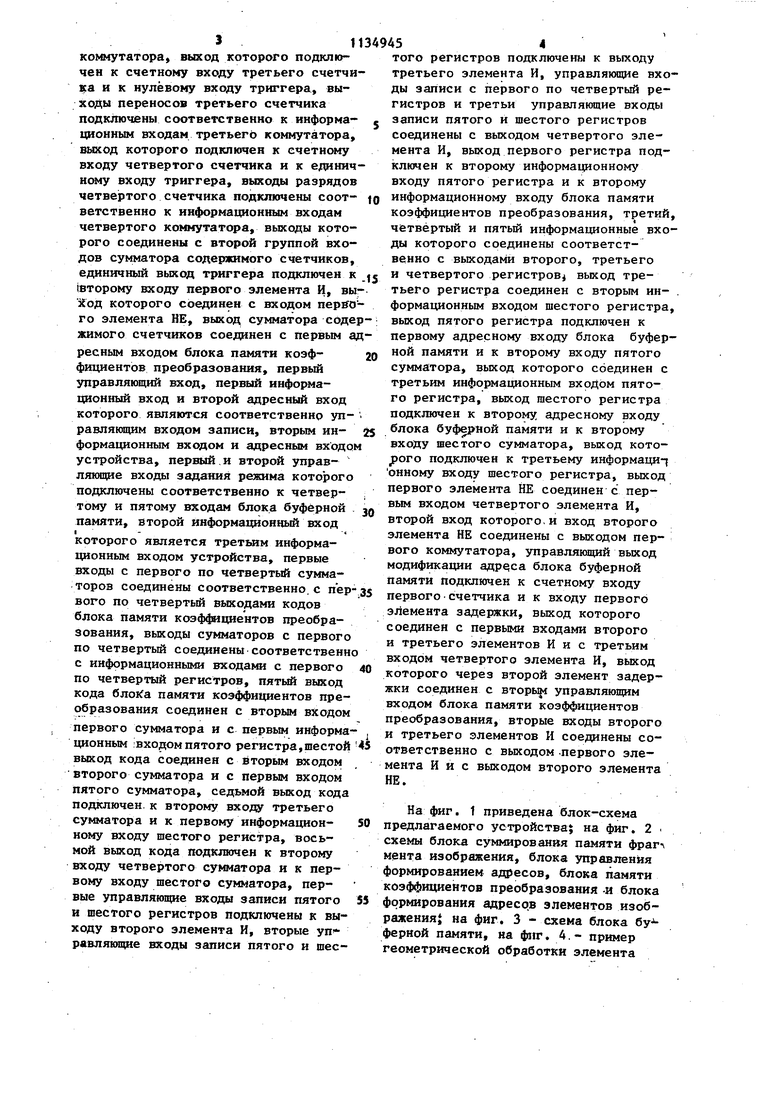

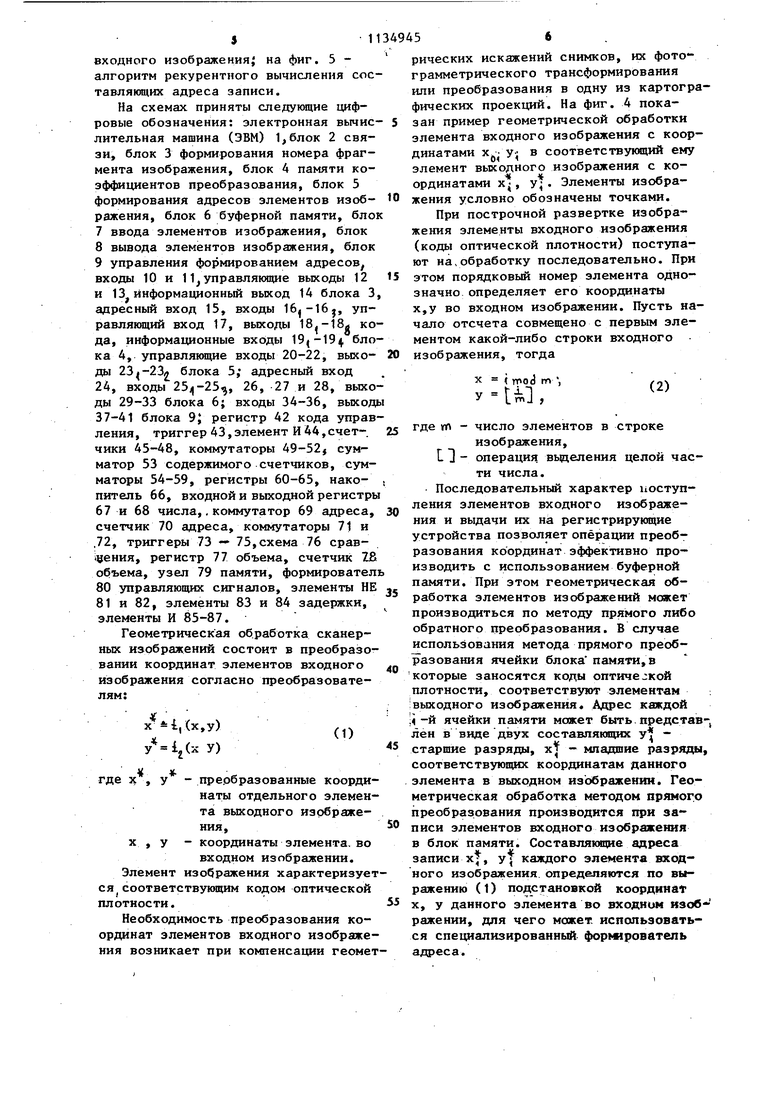

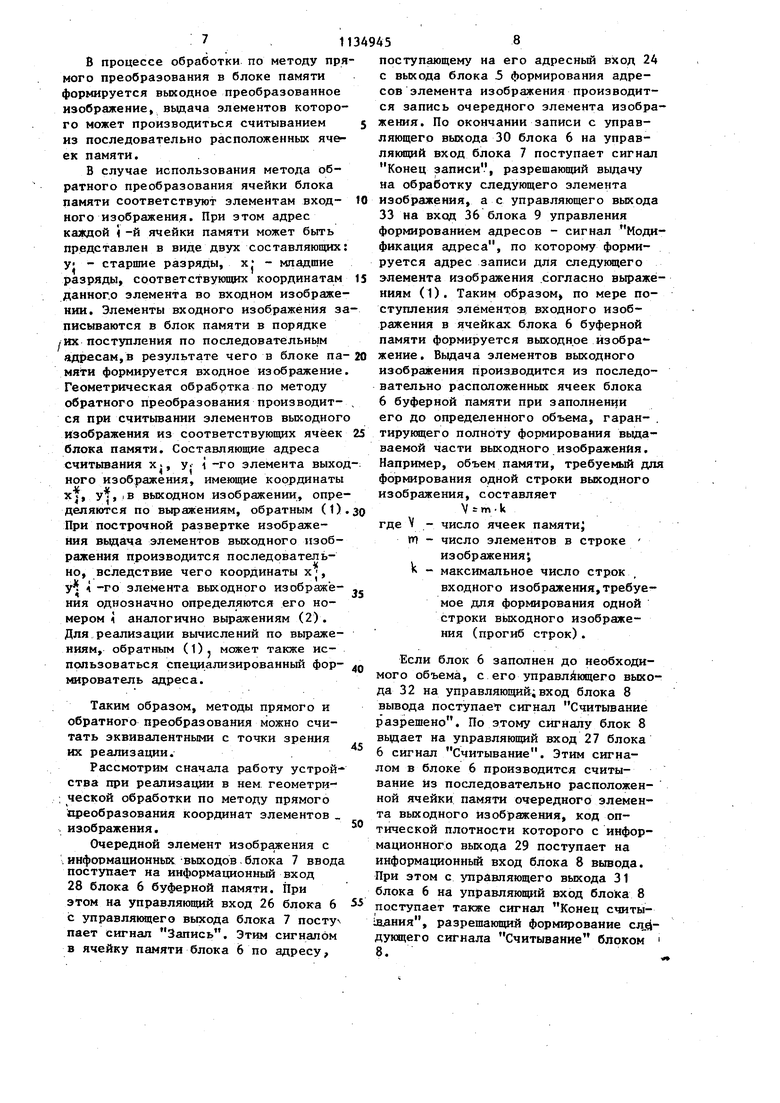

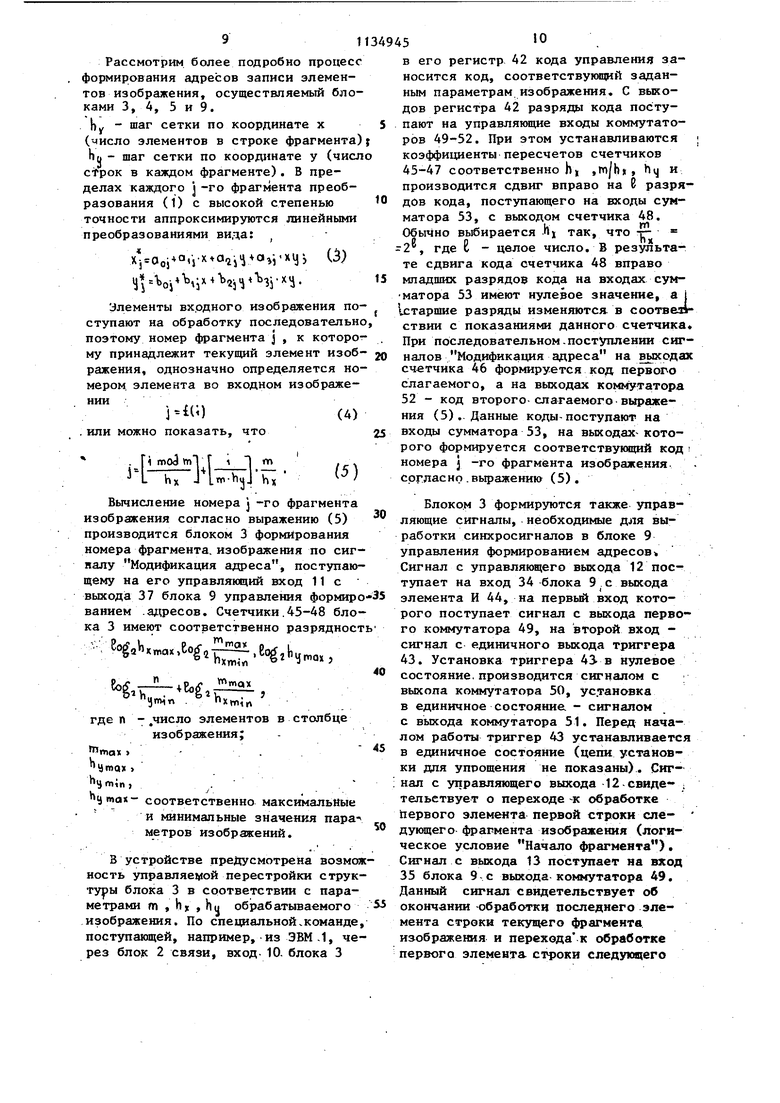

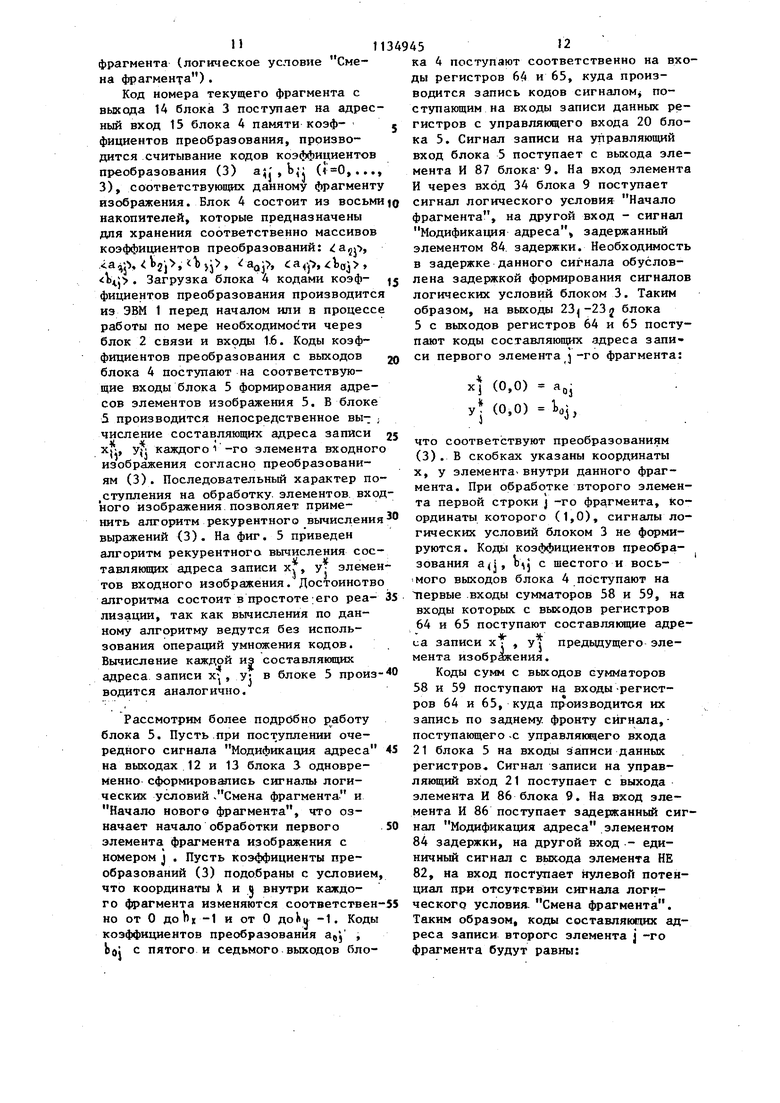

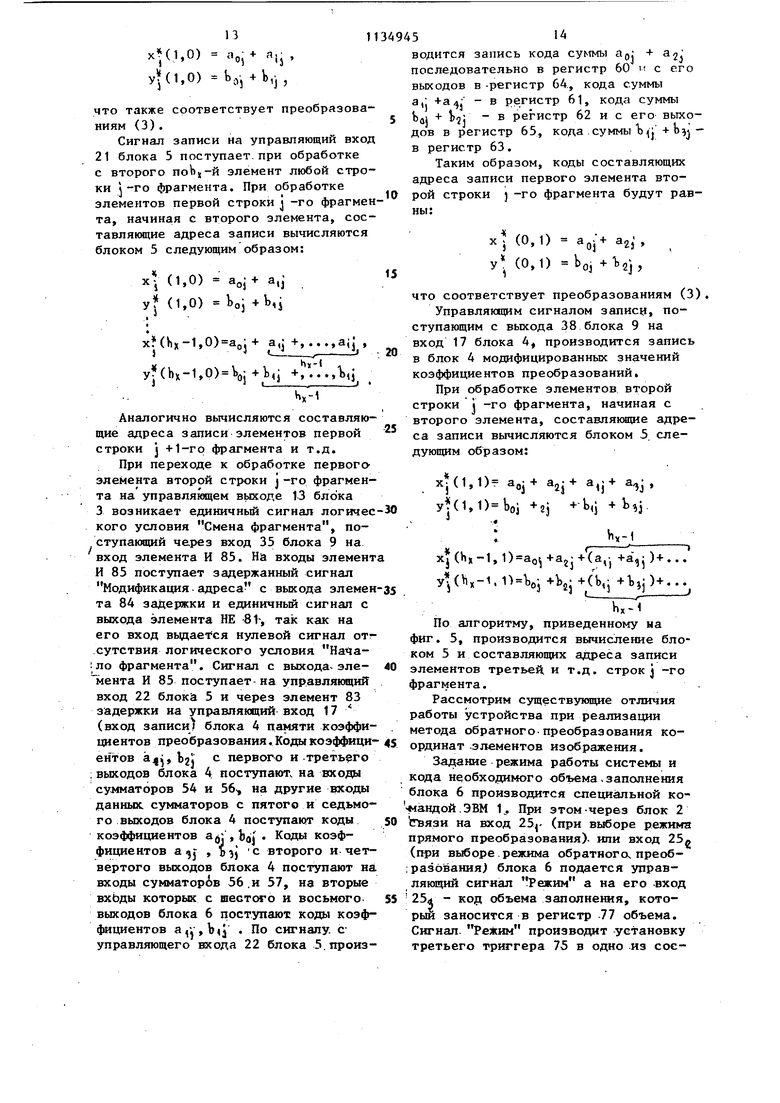

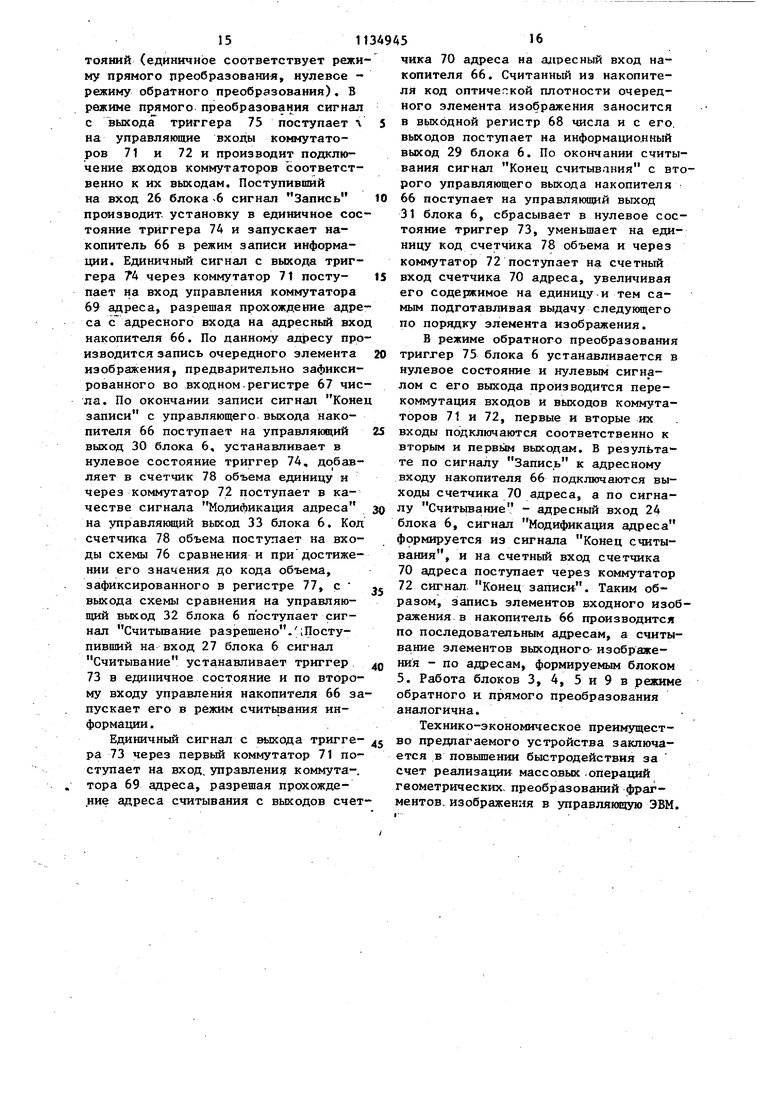

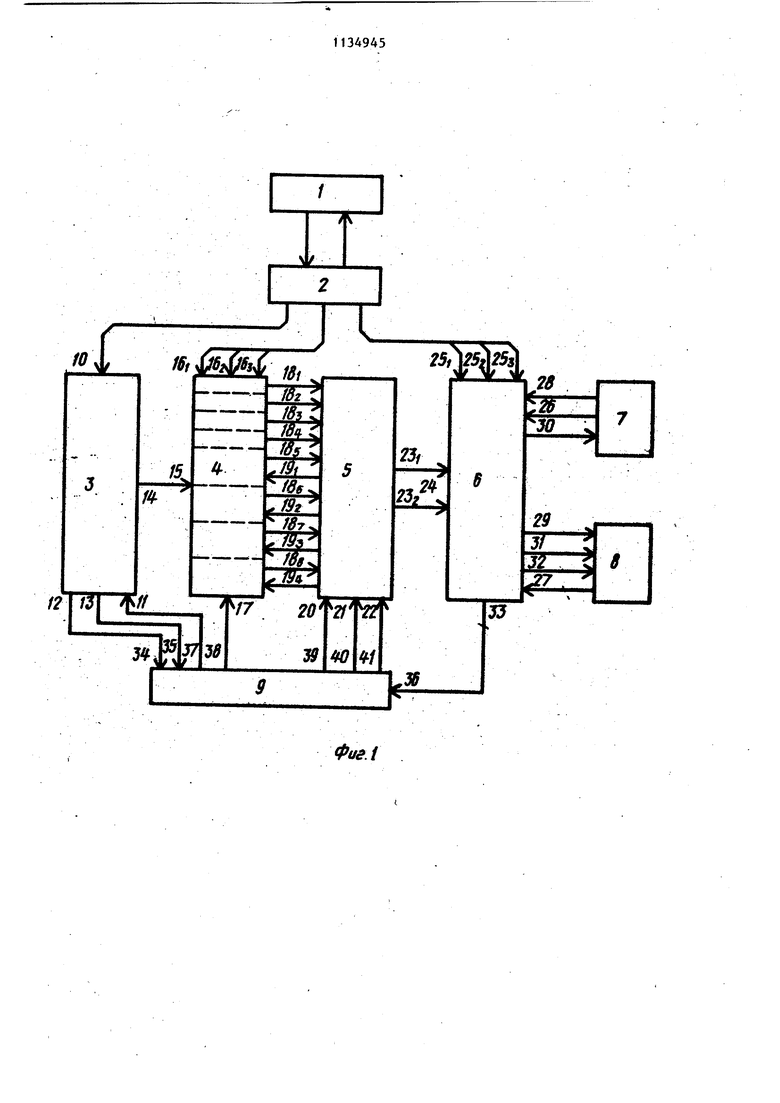

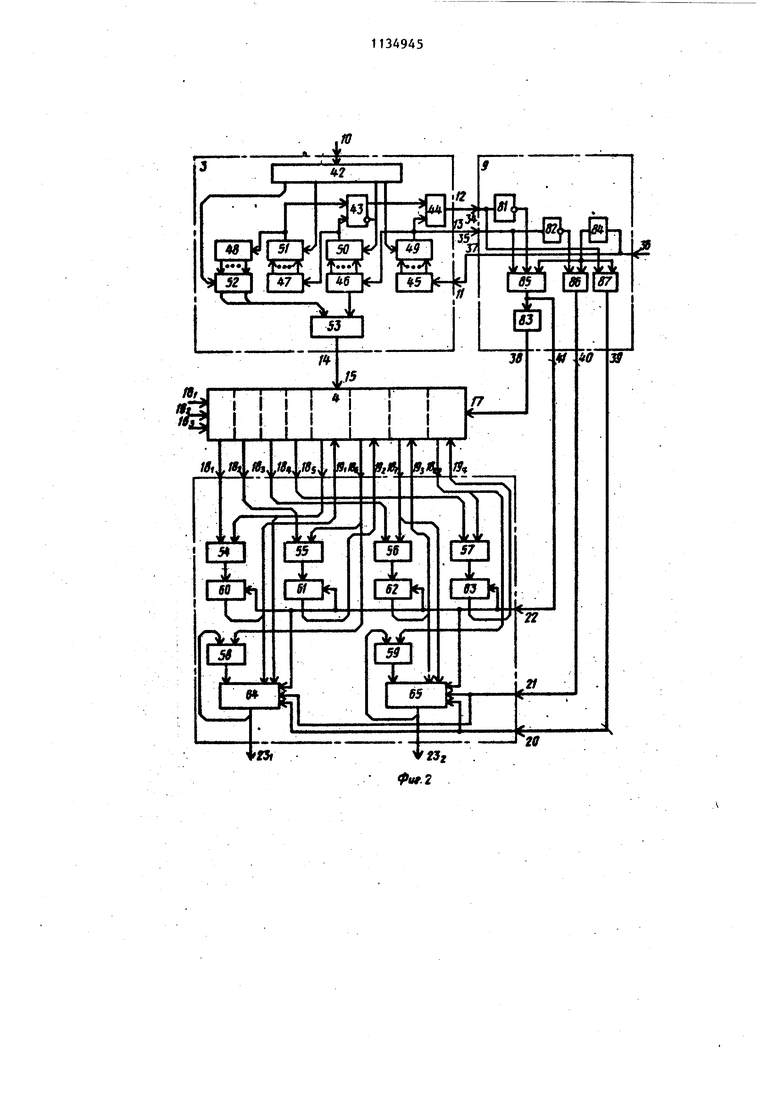

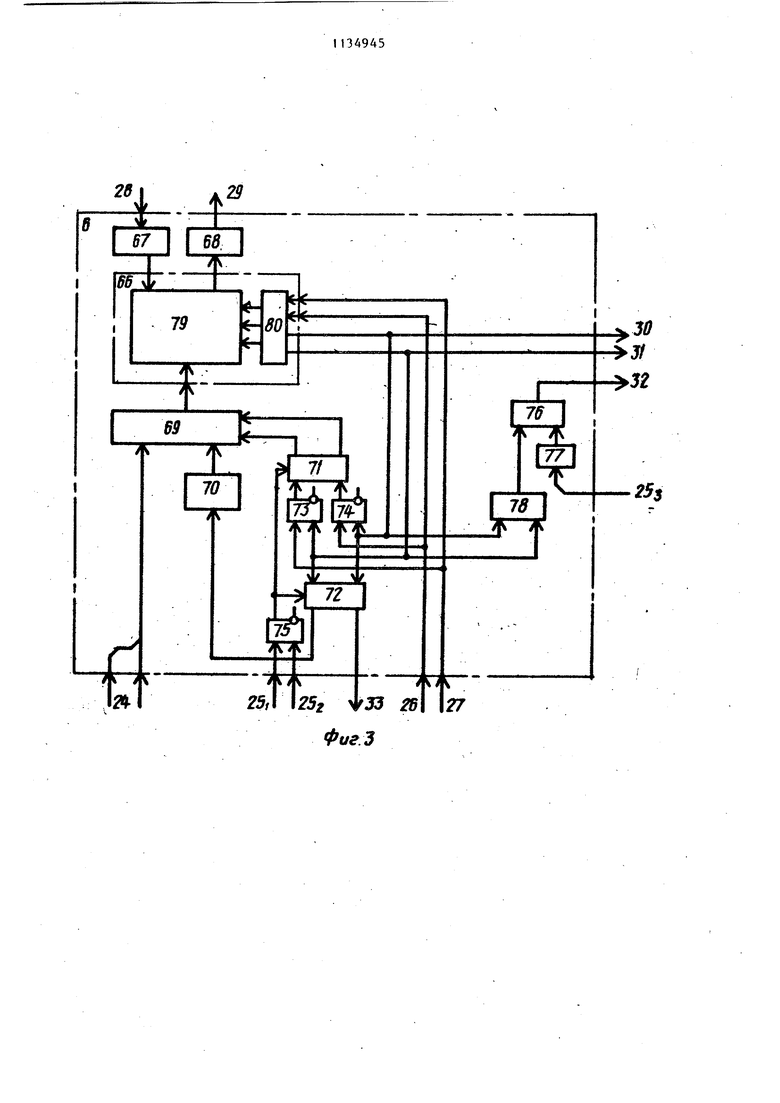

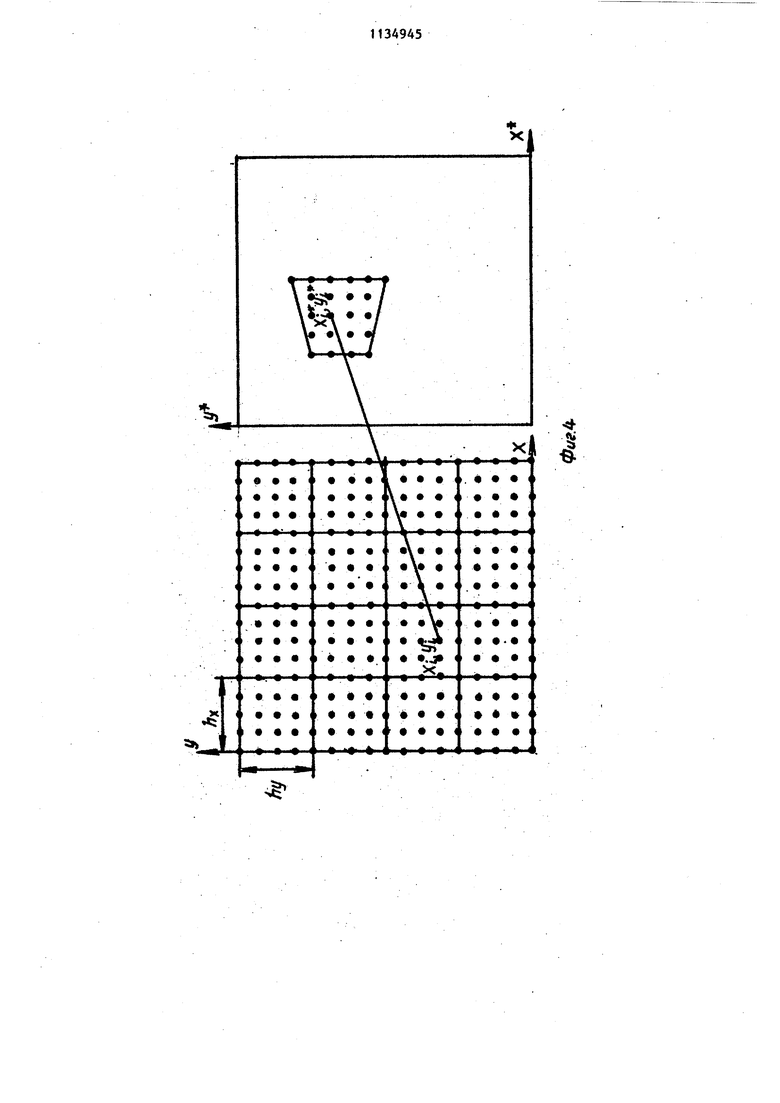

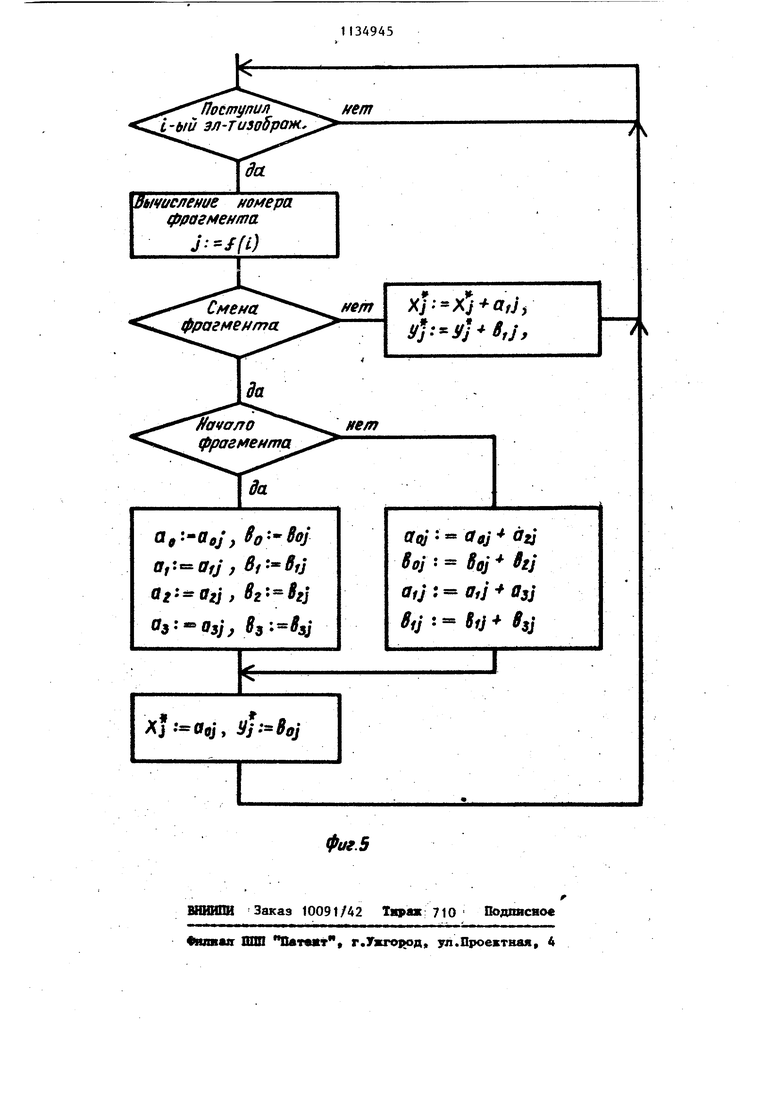

На фиг. 1 приведена блок-схема предлагаемого устройства} на фиг. 2 схемы блока суммирования памяти фраг мента изображения, блока управления формированием адресов, блока памяти коэффициентов преобразования -и блока формирования адресов элементов изображения на фиг. 3 - схема блока бу ферной памяти, на фиг. 4.- пример геометрической обработки элемента входного изображения на фиг. 5 алгоритм рекурентного вычисления составляющих адреса записи. На схемах приняты следующие цифровые обозначения: электронная вычислительная машина (ЭВМ) 1,блок 2 связи, блок 3 формирования номера фрагмента изображения, блок 4 памяти коэффициентов преобразования, блок 5 формирования адресов элементов изображения, блок 6 буферной памяти, бло 7ввода элементов изображения, блок 8вывода элементов изображения, блок 9управления формированием адресов входы 10 и 11, управляющие выходы 12 и 13 информационный выход 14 блока 3 адресный вход 15, входы , управляющий вход 17, выходы 18.-18- ко да, информационные входы бло ка 4, управляющие входы 20-22, выходы блока 5; адресный вход 24, входы 25ц-25, 26, 27 и 28, выхо ды 29-33 блока 6; входы 34-36, выходы 37-41 блока 9J регистр 42 кода управ ления, триггер 43,элемент И44,счет-. чики 45-48, коммутаторы 49-52, сумматор 53 содержимого счетчиков, сумматоры 54-59, регистры 60-65, накопитель 66, входной и выходной регистры 67 и 68 числа,, коммутатор 69 адреса, счетчик 70 адреса, коммутаторы 71 и .72, триггеры 73 - 75,схема 76 срав цения, регистр 77 объема, счетчик ТВ объема, узел 79 памяти, формировател 80управляющих сигналов, элементы НЕ 81и 82, элементы 83 и 84 задержки, элементы И 85-87. Геометрическая обработка сканерных изображений состоит в преобразовании координат элементов входного изображения согласно преобразователям:,(x,y) (- У) где х г - преобразованные координаты отдельного элемента выходного изображения, X , у - координаты элемента, во входном изображении. Элемент изображения характеризует ся соответствующим кодом оптической плотности. Необходимость преобразования координат элементов входного изображения возникает при компенсации геомет 1 56 рических искажений снимков, их фотограмметрического трансформирования или преобразования в одну из картографических проекций. На фиг. 4 показан пример геометрической обработки элемента входного изображения с координатами Xjj- у- в соответствукнций ему элемент вькодного изображения с координатами X, у. Элементы изображения условно обозначены точками. При построчной развертке изображения элементы входного изображения (коды оптической плотности) поступают на обработку последовательно. При этом порядковый номер элемента однозначно определяет его координаты х,у во входном изображении. Пусть начало отсчета совмещено с первым элементом какой-либо строки входного изображения, тогда X - ( rnod m У Ul , где rft - число элементов в строке изображения, L 1 - операция вьделения целой части числа. Последовательный характер поступления элементов входного изображения и выдачи их на регистрирующие устройства позволяет операции преобразования координат эффективно производить с использованием буферной памяти. При этом геометрическая обработка элементов изображений может производиться по методу прямого либо обратного преобразования. В случае использования метода прямого преобразования ячейки блока памяти, в которые заносятся коды оптической плотности, соответствуют элементам выходного изображения. Адрес каждой 1-и ячейки памяти может быть.представвиде двух составляющих у лен в х| - мпадшие разряды. старшие разряды, соответствующих координатам данного элемента в выходном изображении. Геометрическая обработка методом прямого преобразования производится при записи элементов входного изображения в блок памяти. Составлякицие адреса записи х, у каждого элемента входного изображения, определяются по выражению (1) подстановкой координдШ X, у данного элемента во входним изображении, для чего может использоваться специализированный фор1«1рователь адреса. В процессе обработки по методу пря мого преобразования в блоке памяти формируется выходное преобразованное изображение, вьщача элементов которого может производиться считыванием из последовательно расположенных ячеек памяти, . В случае использования метода обратного преобразования ячейки блока памяти соответствуют элементам входкого изображения. При этом адрес каждой I -и ячейки памяти может быть представлен в виде двух составляющих х| - младшие у. - старшие разряды. разряды, соответствующих координатам данного элемента во входном изображении. Элементы входного изображения за писываются в блок памяти в порядке /их поступления по последовательным адресам,в результате чего в блоке па мяти формируется входное изображение Геометрическая обработка по методу обратного преобразования производится при считьгоании элементов выходног изображения из соответствующих ячеек блока памяти. Составляющие адреса считывания х, у. 1-го элемента выхо ного изображения, имеющие координаты X, y,iB выходном изображении, опре деляются по выражениям, обратным (1) При построчной развертке изображения выдача элементов выходного изображения производится последовательно, вследствие чего координаты Xj, у { -го элемента выходного изображёния однозначно определяются его номером i аналогично выражениям (2), Для реализации вычислений по вьфажениям, обратным (1)j может также использоваться специализированный формирователь адреса. Таким образом, методы прямого и обратного преобразования можно считать эквивалентными с точки зрения их реализации. Рассмотрим сначала работу устройства при реализации в нем геометри; ческой обработки по методу прямого преобразования координат элементов . изображения. Очередной элемент изображения с .информационных выходов блока 7 ввода поступает на информационный вход 28 блока 6 буферной памяти. При этом на управляющий вход 26 блока 6 с управлякицего вьпсода блока 7 постуч пает сигнал Запись, Этим сигналом в ячейку памяти блока 6 по адресу. поступающему на его адресный вход 24 с выхода блока 5 формирования адресов элемента изображения производится запись очередного элемента изображения. По окончании записи с управляющего выхода 30 блока 6 на управляющий вход блока 7 поступает сигнал Конец записи ., разрешающий выдачу на обработку следующего элемента изображения, ас управляющего выхода 33 на вход 36 блока 9 управления формированием адресов - сигнал Модификация адреса, по которому формируется адрес записи для следукидего элемента изображения согласно выражениям (1), Таким образом по мере поступления элементов, входного изображения в ячейках блока 6 буферной памяти формируется выходное изображение , Выдача элементов выходного изображения пpoизjвoдитcя из последовательно расположенных ячеек блока 6 буферной памяти при заполнении его до определенного объема, гаран- . тирукнцего полноту формирования вьщаваемой части выходного изображения, Например, объем памяти, требуемый для формирования одной строки выходного изображения, составляет Vsm-k где V - число ячеек памяти; W - число элементов в строке изображения; - максимальное число строк , входного изображения,требуемое для формирования одной строки выходного изображения (прогиб строк). Если блок 6 заполнен до необходимого объема, с его управляющего выхода 32 на управляющий;вход блока 8 вывода поступает сигнал Считывание разрешено. По этому сигналу блок 8 вьщает на управляющий вход 27 блока 6 сигнал Считывание. Этим сигналом в блоке 6 производится считывание из последовательно расположенной ячейки памяти очередного элемента выходного изображения, код оптической плотности которого с информационного выхода 29 поступает на информационный вход блока 8 вьгоода. При этом с управляющего выхода 31 блока 6 на управляющий вход блока 8 поступает также сигнал Конец считыаания, разрешающий формирование сл дующего сигнала Считывание блоком 8. Рассмотрим более подробно процесс формирования адресов записи элементов изображения, осуществляемый блоками 3,4, 5 и 9. Ьу шаг сетки по координате х (число элементов в строке фрагмента) hq- шаг сетки по координате у (числ строк в каждом фрагменте). В пределах каждого j-го фрагмента преобразования (1) с высокой степенью точности аппроксимируются линейными преобразованиями вида: , x-,0oj ° i- a7il°i 4 ,-X4b2j..XlJ. Элементы вх.одного изображения по ступают на обработку последовательн поэтому номер фрагмента , к которо му принадлежит текущий элемент изоб ражения, однозначно определяется но мером, элемента во входном изображении-iC) . или можно показать, что . Г i тТ Г 1 1 m . . i-L-hTin Jh;; Вычисление номера j -го фрагмента изображения согласно выражению (5) производится блоком 3 формирования номера фрагмента, изображения по сигналу Модификация адреса, поступаю щему на его управляющий вход 11с выхода 37 блока 9 управления формир ванием .а фесов. Счетчики.45-48 бло ка 3 имеют соответственно разрядност m в столбце - .ЧИСЛО элементов изображения; Чтвх , ,. К ушах- соответственно максимальные и минимальные значения пара метров изображений. В устройстве предусмотрена возмо ность управляемой перестройки струк туры блока 3 в соответствии с параметрами m , hjc , hu обрабатываемого изображения. По специальной.команде поступающей, например, из ЭВМ .1, че рез блок 2 связи, вход. 10. блока 3 1 5О в его регистр 42 кода управления заносится код, соответствующий заданным параметрам изображения, С выходов регистра 42 разряды кода поЬтупают на управляющие входы коммутаторов 49-52. При этом устанавливаются i коэффициенты пересчетов счетчиков 45-47 соответственно hк ,м|Ь, hvj и производится сдвиг вправо на В разрядон кода, поступающего на входы сумматора 53, с выходом счетчика 48. Обычно выбирается hj так, что -г- 2, где 6 - целое число. В результате сдвига кода счетчика 48 вправо мпадших разрядов кода на входах сумматора 53 имеют нулевое значение, а | Ьстаршие разряды изменяются в соотвел ствии с показаниями данного счетчика При последовательном.поступлении сигналов Модификация адреса на выходах счетчика 46 формируется код первого слагаемого, а на выходах комь утатора 52 - код второго-слагаемого выражения (5).. Данные коды-поступают на входы сумматора 53, на выходах-которого формируется соответствующий код : номера j -го фрагмента изображе1ния. согласно.вьфажению (5). Блоком 3 формируются также управляющие сигналы, необходимые для выработки синхросигналов в блоке 9 управления формированием адресов« Сигнал с управляющего выхода 12 поступает на вход 34 блока 9с выхода элемента И 44, на первый вход которого поступает сигнал с выхода первого коммутатора 49, на второй вход сигнал с единичного вькода триггера 43. Установка триггера 43. в нулевое состояние, производится сигналом с выхопа коммутатора 50, установка в единичное состояние - сигналом с выхода коммутатора 51. Перед началом работы триггер 43 устанавливается в единичное состояние (цепи установки для упрощения не показаны). Сигнал с управляющего выхода 12.свидетельетвует о переходе -к обработке первого элемента первой строки еле- дующего фрагмента изображения (логическое условие Начало фрагмента). Сигнал с выхода 13 поступает на вход 35 блока 9-с выхода коммутатора 49. Данный сигнал свидетельствует об окончании -обработки последнего элемента строки текущего фрагмента изображения и перехода к обработке первого элемен-га строки следующего фрагмента (логическое условие Смена фрагмента). Код номера текущего фрагмента с выхода 14 блока 3 поступает на адрес ный вход 15 блока 4 памяти коэффициентов преобразования, производится считывание кодов коэффициентов преобразования (3) а;; , Ьц (,.. 3), соответствующих данному фрагмент изображения. Блок 4 состоит из восьм накопителей, которые предназначены для хранения соответственно массивов коэффициентов преобразований: , Ц , Ь УЗ , Здр, , Ьор , 4J . Загрузка блока 4 кодами коэффициентов преобразования производитс из ЭВМ 1 перед началом или в процесс работы по мере необходимоёти через блок 2 связи и входы 1.6. Коды коэффициентов преобразования с выходов блока 4 поступают на соответствующие входы блока 5 формирования адре сов элементов изображения 5. В блок 5 производится непосредственное вычисление составляющих адреса записи Xj-, каждого 1 -го элемента входно изображения согласно преобразованиям (3). Последовательный характер п ,ступления на обработку, элементов вх ного изображения.позволяет применить алгоритм рекурентного вычислени выражений (3). На фиг. 5 приведен алгоритм рекурентного вычисления сос тавляющих адреса записи х, , у- элеме тов входного изображения. Достоинств алгоритма состоит в простоте;его peaлизации, так как вычисления по данному алгоритму ведутся без использования операций умножения кодов. Вычисление каждой из составляющих У; в блоке 5 произ адреса записи х , У водится аналогично. Рассмотрим более подробно работу блока 5. Пусть при поступлении очередного сигнала Модификация адреса на выходах 12 и 13 блока 3 одновременно- сформировались сигналь логических условий .Смена фрагмента и Начало нового фрагмента, что означает начало обработки первого элемента фрагмента изображения с номером J . Пусть коэффициенты преобразований (3) подобраны с условием что координаты X и j внутри каждого фрагмента изменяются соответствен но от О доЬх -1 и от О доК -1. Коды коэффициентов преобразования с пятого и седьмого выходов блока 4 поступают соответственно на входы регистров 64 и 65, куда производится запись кодов сигналом поступающим на входы записи данных регистров с управляющего входа 20 блока 5. Сигнал записи на управляющий вход блока 5 поступает с выхода элемента И 87 блока- 9. На вход элемента И через вход 34 блока 9 поступает сигнал логического условия Начало фрагмента, на другой вход - сигнал Модификация адреса, задержанный элементом 84 задержки. Необходимость в задержке данного сигнала обусловлена задержкой формирования сигналов логических условий блоком 3. Таким образом, на вькоды блока 5 с выходов регистров 64 и 65 поступают коды составляющих эдреса записи первого элемента 3-го фрагмента: х (0,0) а У (0,0) bajj ЧТО соответствуют преобразованиям (3). В скобках указаны координаты X, у элементавнутри данного фрагмента. При обработке второго элемента первой строки J -го фрагмента. Координаты которого (1,0), сигналы логических условий блоком 3 не формируются. Коды коэффициентов преобразования , с шестого и восьМого выходов блока 4 поступают на первые входы сумматоров 58 и 59, на входы которых с выходов регистров 64 и 65 поступают составляющие адреса записи X предьздущего элемента изображения. Коды сумм с выходов сумматоров 58 и 59 поступают на входы-регистров 64 и 65, куда производится их запись по заднему фронту сигнала,поступающего -с управляющего входа 21 блока 5 на входы записи данных регистров.. Сигнал записи на управляющий вход 21 поступает с выхода элемента И 86 блока 9. На вход элемента И 86 поступает задержанный сигнал Модификация адреса элементом 84 задержки, на другой вход - единичный сигнал с выхода элемента НЕ 82, на вход поступает нулевой потенциал при отсутствии сигнала логическогр условия. Смена фрагмента. Таким образом, коды составляющих адреса записи второго элемента j -го фрагмента будут равны: 13 х(ЬО) a,j+ a.j , У-(1,0) b,v, + b,j, что также соответствует преобразованиям (3) . Сигнал записи на управляющий вход 21 блока 5 поступает.при обработке с второго поЬц-й элемент любой строки J-го фрагмента. При обработке элементов первой строки j -го фрагмен та, начиная с второго элемента, составляющие адреса записи вычисляются блоком 5 следующим образом: (1,0) ао; + f (1,0) Ьо; +b,i x(bx-1,0)aoj + a,j +, ...,aij, уУ(Ьх-1,0) Ьа| +b,j +,У..,Ц Аналогично вычисляются составляющие адреса записи элементов первой строки j +1-гр фрагмента и т.д. При переходе к обработке первого элемента второй строки j-го фрагмента на управляющем выходе 13 блока 3 возникает единичный сигнал логичес кого условия Смена фрагмента, поступающий через вход 35 блока 9 на вход элемента И 85. На входы элемент И 85 поступает задержанный сигнал Модификация адреса с выхода элемен та 84 задержки и единичный сигнал с выхода элемента НЕ 81-, так как на его вход вьщается нулевой сигнал отсутствия логического условия Нача:ло фрагмента. Сигнал с выхода-эле мента И 85 поступает-на управляющий вход 22 блока 5 и через элемент 83 задержки на управляющий вход 17 (вход записи) блока 4 па;мяти коэффициентов преобразования.Кодыкоэффици ентов , Ьз} с первого и третьего : выходов блока 4 поступают, на входы сумматоров 54 и 56., на другие входы данных, сумматоров с пятого и седьмого выходов блока 4 поступают коды коэффициентов , Ьо( Коды коэффициентов а : ,03) С второго и четвертого выходов блока 4 поступают на входы сумматорбв 56.и 57, на вторые

вхЬды которых с шестого и восьмого 55 25 - код объема заполнения, котовыходов блока 6 поступают коды коэф- фициентов , b(j . По сигналу, с

управляющего входа 22 блока 5. произ1

рыи заносится в регистр 77 объема. Сигнал. Режим производит установку третьего триггера 75 в одно из сое51водится запись кода ар; + ajj последовательно в регистр 60 ч с его выходов в -регистр 64., кода суммы а,: +а - в регистр 61, кода суммы Ьл1 + Ьо: - в регистр 62 и с его вьтхоJ JЛ 1 дов в регистр 65, кода . суммы Ъ {j +Ьз| - в регистр 63, Таким образом, коды составляющих адреса записи первого элемента второй строки ) -го фрагмента будут равны: оГ 32} , (0,1) Ь OJ + 2J J что соответствует преобразованиям (3). Управляющим сигналом записи, поступающим с выхода 38 блока 9 на вход 17 блока 4, производится запись в блок 4 модифицированных значений коэффициентов преобразований. При обработке элементов второй строки I -го фрагмента, начиная с второго элемента, составпякмцие адреса записи вычисляются блоком 5. следующим образом: х-(1,1) у(П1)Ьо1 -«-zj +-b,j + b,j : b,-i Xj (Ьх-1,1)ао +aj- +(а,- +a,j ) + ... У(1х-М)Ц +bjj +(b,- +l)j)+... По алгоритму, приведенному на фиг. 5, производится вычисление блоком 5 и состав.ляющих адреса записи элементов третьей, и т.д. строк j -го фрагмента. Рассмотрим существуюпще отличия работы устройства при реализации метода обратного-преобразования координат -элементов изображения. Задание режима работы системы и кода необходимого объема.заполнения блока 6 производится специальной коандой.ЭВМ 1 При этом-через блок 2 гвязи на вход 25,- (при вьйоре режима рямого преобразования), ипи вход 25 (при выборе.режима обратного преобразоваиия блока 6 подается управляющий сигнал Режим а на его -вход тояний (единичное соответствует режи му прямого преобразования, нулевое режиму обратного преобразования). В режиме прямого преобразования сигнал с выхода триггера 75 поступает на управляющие входы коммутаторов 71 и 72 и производит подключение входов коммутаторов соответственно к их выходам. Поступивший на вход 26 блока -6 сигнал Запись производит установку в единичное сос тояние триггера 74 и запускает накопитель 66 в режим записи информации. Единичный сигнал с выхода триггера 74 через коммутатор 71 поступает на вход управления коммутатора 69 адреса, разрешая прохождение адре са с адресного входа на адресный вхо накопителя 66. По данному адресу про изводится запись очередного элемента изображения, предварительно зафиксированного во входном.регистре 67 чис ла. По окончании записи сигнал Коне записи с управляющего.выхода накопителя 66 поступает на управляющий выход 30 блока 6, устанавливает в нулевое состояние триггер 74, добавляет в счетчик 78 объема единицу и через коммутатор 72 поступает в качестве сигнала Модификация адреса на управлякщий выход 33 блока 6. Код счетчика 78 объема поступает на входы схемы 76 сравнения и при достижении его значения до кода объема, зафиксированного в регистре 77, с выхода схемы сравнения на управляющий выход 32 блока 6 поступает сигнал Считьшание разрешено.;Поступивший на вход 27 блока 6 сигнал Считывание устанавливает триггер . 73 в единичное состояние и по второму входу управления накопителя 66 за пускает его в режим считьшания информации.. Единичный сигнал с выхсща триггера 73 через первый коммутатор 71 поступает на вход, управления коммута-. тора 69 адреса, разрешая прохождение адреса считывания с выходов счет чика 70 адреса на а;1ресный вход накопителя 66. Считанный из накопителя код оптической плотности очередного элемента изображения заносится в выходной регистр 68 числа и с его. выходов поступает на информационный выход 29 блока 6. По окончании считывания сигнал Конец считывания с второго управляющего выхода накопителя 66 поступает на управляющий выход 31 блока 6, сбрасывает в нулевое состояние триггер 73, уменьшает на единицу код счетчика 78 объема и через коммутатор 72 поступает на счетный вход счетчика 70 адреса, увеличивая его содержимое на единицу и тем самьм подготавливая выдачу следукидего по порядку элемента изображения. В режиме обратного преобразования триггер 75 блока 6 устанавливается в нулевое состояние и нулевым сигналом с его выхода производится перекоммутация входов и выходов коммутаторов 71 и 72, первые и вторые их входы подключаются соответственно к вторым и первым выходам. В результате по сигналу Запись к адресному входу накопителя 66 подключаются выходы счетчика 70 адреса, а по сигналу Считывание - адресный вход 24 блока 6, сигнал Модификация адреса формируется из сигнала Конец считывания, и на счетный вход счетчика 70 адреса поступает через коммутатор 72 сигнал Конец записи. Таким образом, запись элементов входного изображения в накопитель 66 производится по последоватепьным адресам, а считывание элементов выходного- изображения - по адоесам, формируемым блоком 5. Работа блоков 3, 4, 5 и 9 в режиме обратного н прямого преобразования аналогична. Технико-экономическое преимущество предлагаемого устройства заключается в повьштении быстродействия за счет реализации массовых операций геометрических, преобразований фрагментов, изображения в управлянщую ЭВМ.

IT

J

18i

Шг

/fe

WL

Ж

/1

;3г

Ж

/У4

J

Vr

12

8

W

ffO

йЧЧ

2L

ж

30

/

29

IT JT

ЗЗГ

,36

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Устройство для обработки изображений | 1986 |

|

SU1316003A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Устройство для преобразования телевизионного стандарта | 1986 |

|

SU1343562A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЭЛЕМЕНТОВ СКАНЕРНЫХ ИЗОБРАЖЕНИЙ, содержащее блок ввода элементов изобра жения. Управляющий вькод и информационный выход которого подключены соответственно к первым управляйщему и информационному входам блока буферной памяти, управляющий вход конца записи блока ввода элементов изображения соединен с первым управлякщим выходом блока буферной памяти информационный выход, второй и третий управляющие выходы которого соединены соответственно с информационным входом, управлякнцим входом конца считывания и управляющим входом разрешения считывания блока вывода элементов изображения, управляющий выход считывания .которого соединен с вторым управляю1цим входом блока буферной памяти, отличающееся тем, что, с целью повышения быстродействия, в него введены блок памяти коэффициентов преобразования, блок формирования номера фрагмент изображения, включающий с первого по четвертьй счетчики, с первого по четвер- тый коммутаторы, триггер,сумматор содержимого счетчиков, элемент И, fe регистр кода управления, блок формирЬ- вания адресов элементов изображения, g включаюо(ий с первого по шестой ,сум- , с первого по шестой регистры, блок управления формированием адресов, включающий два элемента НЕ, два.элемента задержки и три элемента :АЭ И, причем .переносов первого .( счетчика соединены соответственно с :р информационными входами первого ком. мутатора, выход КОТОРОГО подключен СП к счетному входу ВТОРОГО счетчика и к первому входу первого элемента И управляющие входы с первого по четвертый коммутаторов соегшнейы соответственно с выходами разрядов регистра кода управления, информационный вход которого является первым информационным входом устройства, выходы разрядов второго счетчика подключены соответственио к первой группе входов сумматора содержи

Фиё

i-zi

29

7J 68 ЛГ

79

т

ФигЗ

30

-;f „„ х- с/т/уд/// I/em i-ый зл-гизо5рож М1Чосление номера фрагмента J-/(i)

Of-Oej) So-Soj j

Qt-Ogj f 2 fcj

, Уг-Boj

ci9j Oti Boj Bij

Oii - Osj StJ BSJ xJ.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гришин М.П., Курбанов Ш.М., Маркелов В.П | |||

| Автоматический ввод и обработка фотографических изображений на ЭВМ, М., Энергия, 1976, с | |||

| Капельная масленка с постоянным уровнем масла | 0 |

|

SU80A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| Техника тематической автоматизированной обработки видеоинформации | |||

| Сб | |||

| Исследование земных ресурсов космическими средствами | |||

| Ч | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Методы измерения и обработки информации | |||

| Доклады советских ученых на совещании рабочей группы социалистических стран по дистанционному зондированию Земли с помощью аэрокосмических средств | |||

| Баку, 21-27 апреля 1975 г | |||

| М., АН СССР, 1975, с..136, рис | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Принципы организации ввода в ЭВМ зрительной информации с растровыходатчйков изображения.- Вопросы радиоэлектроники, сер, ЭВТ, вып | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-01-15—Публикация

1983-04-11—Подача