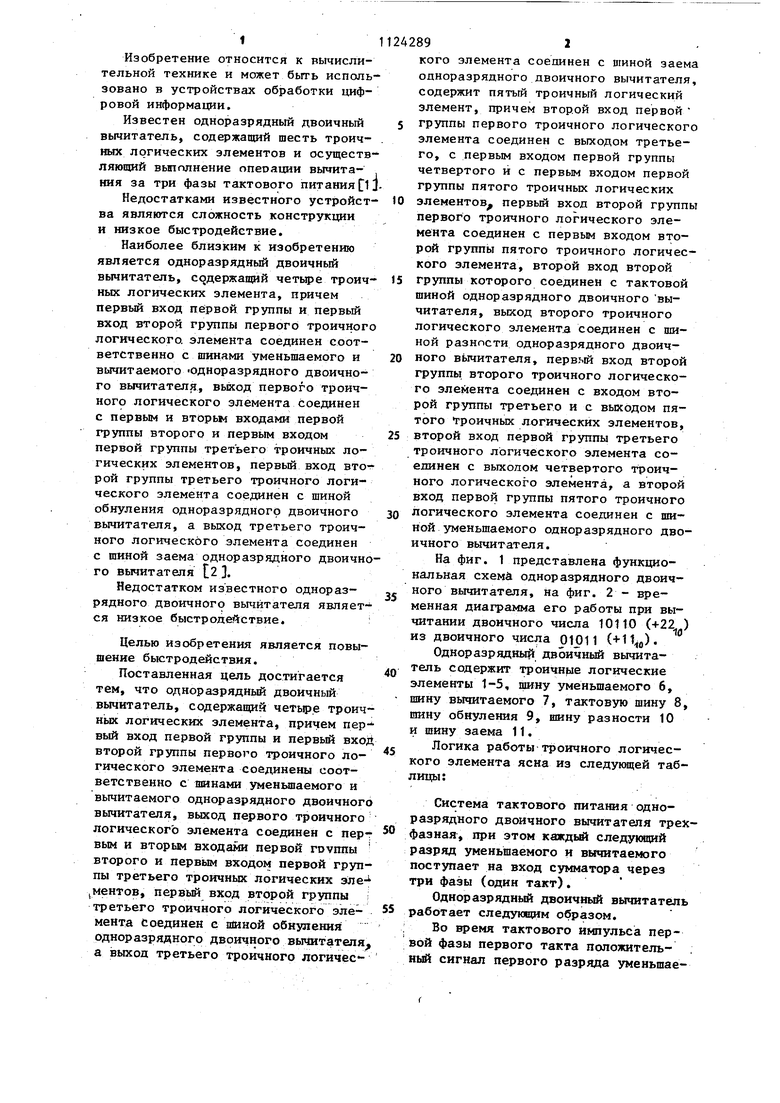

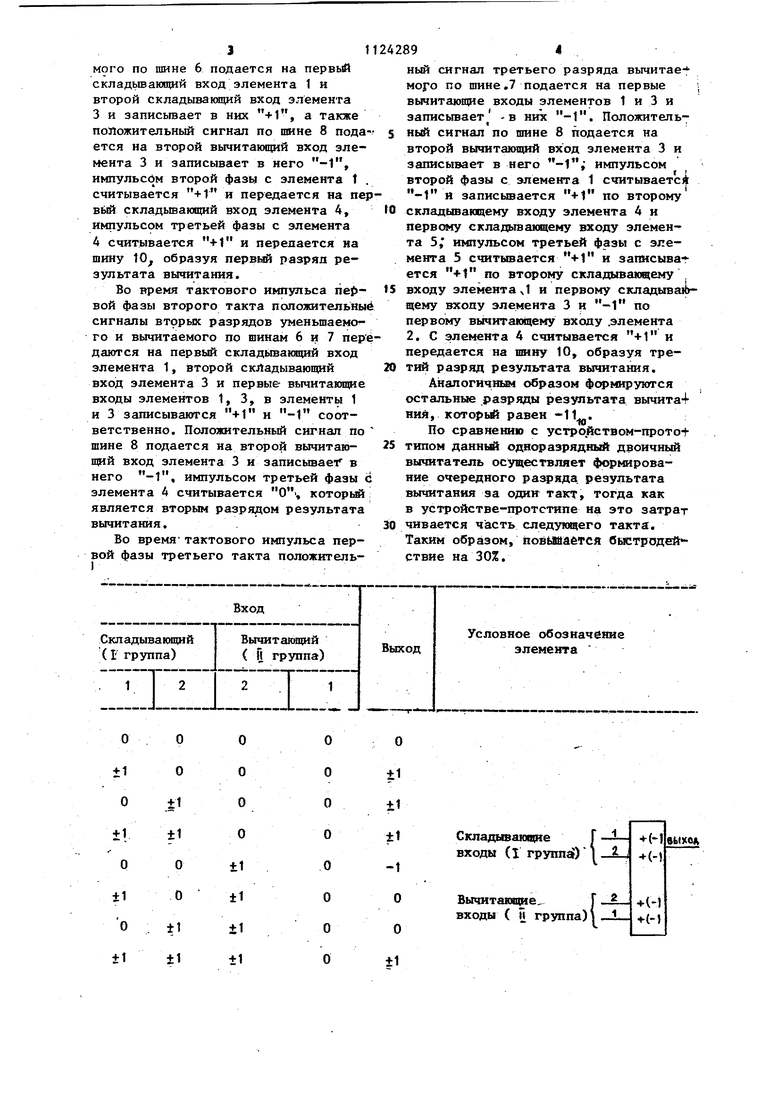

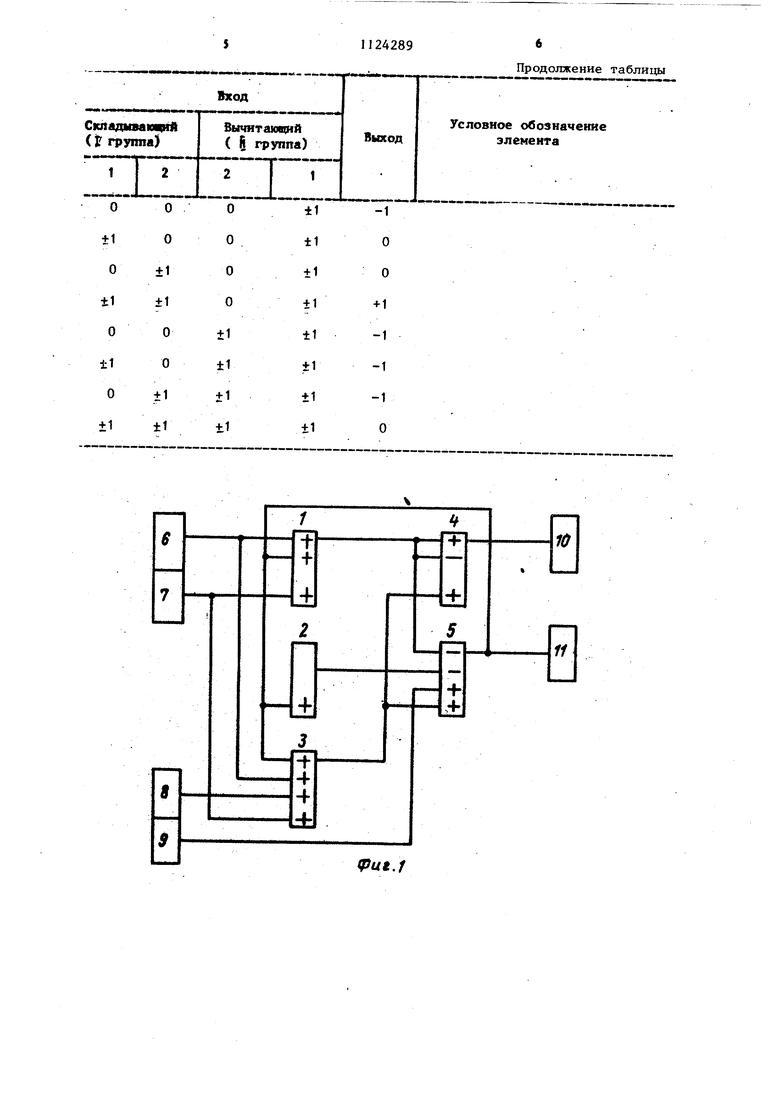

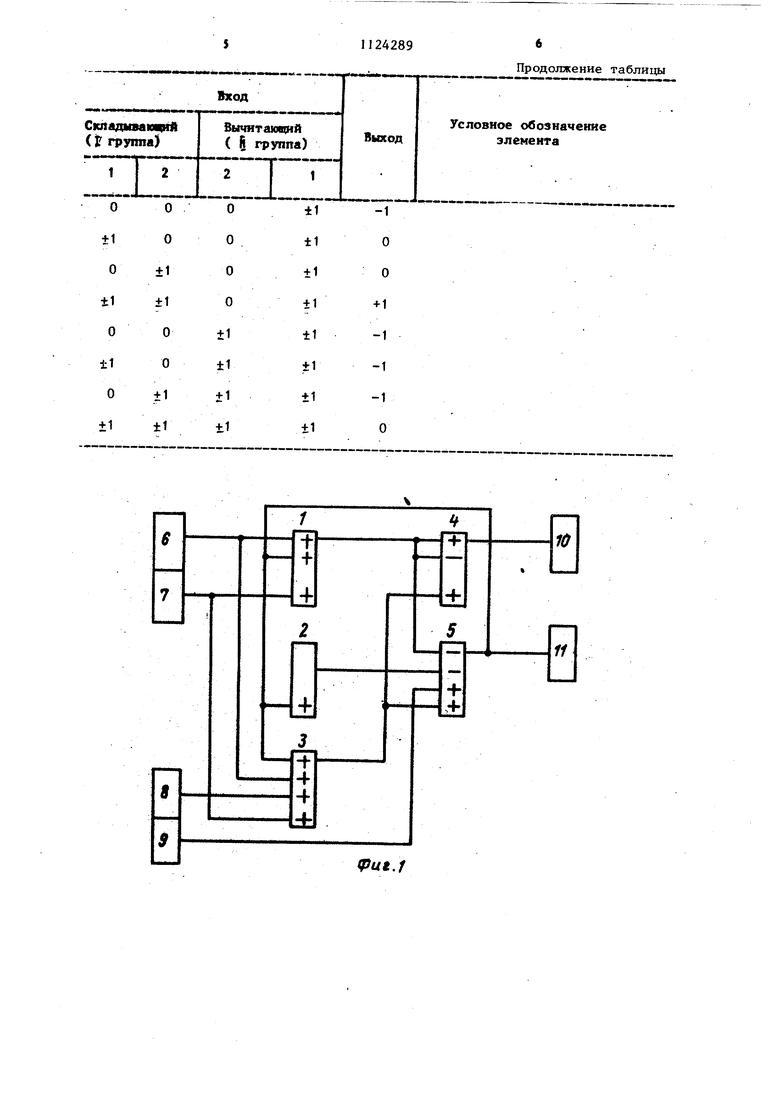

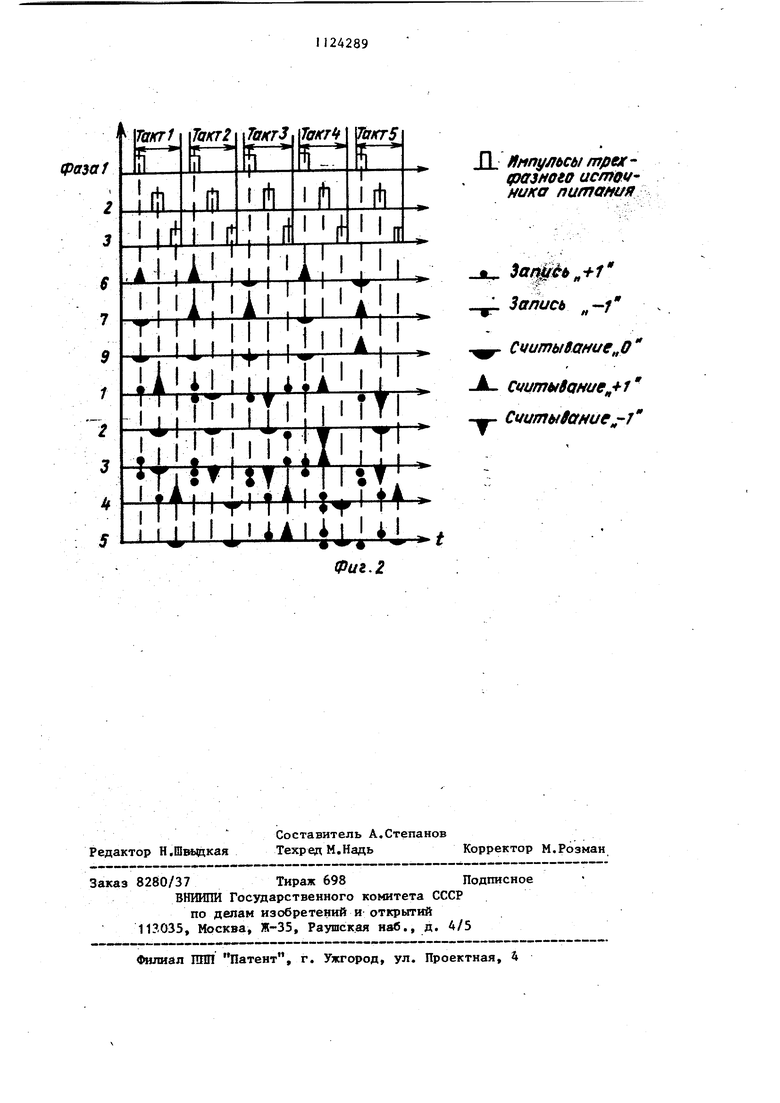

1 Изобретение относится к вычислительной технике и может быть исполь зовано в устройствах обработки циф ровой информации. Известен одноразрядный двоичный вычитатель, содержащий шесть троичных логических элементов и осуществ ляющий вьиолнение операции вычитаНИН за три фазы тактового питания Недостатками известного устройст ва являются сложность конструкции и низкое быстродействие. Наиболее близким к изобретению является одноразрядный двоичный вычитатель, содержащий четыре троич ных логических элемента, причем первый вход первой группы и первый вход второй группы первого троичног логического, элемента соединен соответственно с шинами уменьшаемого и вычитаемого -одноразрядного двоичного вычитател, вькод первого троичного логического элемента соединен с первым и вторьм входами первой группы второго и первым входом первой группы третьего троичных логических элементов, первый вход вто рой группы третьего троичного логического элемента соединен с шиной обнуления одноразрядного двоичного вычитателя, а выход третьего троичного логического элемента соединен с шиной заема одноразрядного двоичн го вычитателя 2 . Недостатком известного одноразрядного двоичного вычитателя являет ся низкое быстродействие. Целью изобретения является повышение бьютродействия. Поставленная цель достигается тем, что одноразрядный двоичный вычитатель, содержащий четыре троич ньк логических элемента, причем пер вый вход первой группы и первый вхо второй группы первого троичного логического элемента соединены соответственно с шинами уменьшаемого и вычитаемого одноразрядного двоичног вычитателя, выход первого троичного логического элемента соединен с пер Bbw и вторьм входами первой ГРУППЫ второго и первым входом первой груп пы третьего троичных логических элe ментов, первый вход второй группы третьего троичного логического элемента Соединен с пмной обнуяения одноразрядного двоичного вычитателя а выход третьего троичного логичес892кого элемента соепинен с шиной заема одноразрядного двоичного вычитателя, содержит пятый троичный логический элемент, причем второй вход первой группы первого троичного логического элемента соединен с выходом третьего, с первым входом первой группы четвертого и с первым входом первой группы пятого троичных логических элементов первый вход второй группы первого троичного логического элемента соединен с первым входом второй группы пятого троичного логического элемента, второй вход второй группы которого соединен с тактовой шиной одноразрядного двоичного вычитателя, выход второго троичного логического элемента соединен с шиной разности одноразрядного двоичного вьтитателя, первый вход второй группы второго троичного логического элемента соединен с входом второй группы третьего и с выходом пятого троичных логических элементов, второй вход первой группы третьего троичного логического элемента соединен с выходом четвертого троичного логического элемента, а второй вход первой группы пятого троичного логического элемента соединен с шиной уменьшаемого одноразрядного двоичного вычитателя. На фиг. 1 представлена функциональная схемй одноразрядного двоичного вычитателя, на фиг. 2 - временная диагр 1мма его работы при вычитании двоичного числа lOtIO (+22 ) иэ двоичного числа 01011 (+ %о Одноразрядный двоичный вычитатель содержит троичн)Ь1е логические элементы 1-5, шину уменьшаемого 6, шину вычитаемого 7, тактовую шину 8, шину обнуления 9, шину разности 10 и шину заема 11. Логика работы троичного логического элемента ясна из следукщей таблицы:Система тактового питания одноразрядного двоичного вычитателя трехфазная, при этом каждь следующий разряд уменьшаемого и вычитаемого поступает на вход сумматора через три фазы (один такт). Одноразрядный двоичный вычитатель работает следующим образом. Во время тактового импульса первой фазы первого такта положительный сигнал первого разряда уменьшавмого по шине 6 подается на первьй складьшающий вход элемента 1 и второй складывающий вход элемента 3 и записьгаает в них +1, а также положительный сигнал по шине 8 подается на второй вычитающий вход элемента 3 и записывает в него -1, импульсдм второй фазы с элемента t . +1

считывается

и передается на первый складывакяций вход элемента 4, импульсом третьей фазы с элемента 4 считывается +1 и перелается на шину 10 образуя первый разряд результата вычитания. Во время тактового импульса riejl вой фазы второго такта попожительны сигналы втррых разрядов уменьшаемо го и вычитаемого по шинам 6 и 7 пер даются на первый складывакяций вход элемента 1, второй складывающий вход элемента 3 и первые вычитающие входы элементов 1, 3, в элементы 1 и 3 записываются +1 и -1 соответственно. Положительный сигнал по шине 8 подается на второй вычитающий вход элемента 3 и записывает в него -1, импульсом третьей фазы элемента 4 считывается , которь является вторым разрядом результата вычитания. Во времятактового импульса первой фазы третьего такта положительный сигнал третьего разряда вычитаеMOfo по шине ,7 подается на первые вычитающие входы элементов 1 и 3 и записьгоает -в них -1. Положительный сигнал по шине 8 подается на второй вычитающий вход элемента 3 и записывает в него импульсом второй фазы с элемента 1 считываете -t и записывается +1 по второму складывающему входу элемента 4 и первому складывающему входу элемента 5, импульсом третьей фазы с элемента 5 считьшается +1 и записыва-г ется 4-1 по второму складывающему входу элементах и первому складыван щему входу элемента 3 и -1 по первому вычитающему входу .элемента 2. С элемента А считывается +1 и передается на 10, образуя треTt& разряд результата вычитания. Аналогичньм образом формируются остальные разряды результата вычитав НИИ, KOTopi равен 11. По сравнению с устройством-прото-fтипом данньй одноразряднь двоичный вычитатель осуществляет формирование очередного разряда, результата вычитания за один такт, тогда как в устройстве-прототипе на это затрат чивается часть следуквдего такта. Таким образом, повиаается быстр|одей ствие на 30%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| Дешифратор | 1983 |

|

SU1119167A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1383496A1 |

| Устройство для выполнения операции "Шеффера" на феррит-ферритовых троичных элементах | 1983 |

|

SU1127095A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1405110A1 |

| Реверсивный счетчик импульсов | 1982 |

|

SU1091347A1 |

| Реверсивный счетчик импульсов | 1986 |

|

SU1398092A1 |

ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ, содержащий четыре логических элемента, причем первый вход первой группы и первый вход второй группы первого троичного логического элемента соединены соответственно с шинами уменьшаемого и вычитаемого одноразрядного двоичного вычитателя, выхсЗд первого троичного логического элемента соединен с первым и вторым входами первой группы второго и первым входом первой группы третьего троичных логичес ких элементов, первый вход второй группы третьего троичного лoгичecкot го элемента соединен с шиной o6нyлef ния одноразрядного двоичного вычита теля, а вьЬсод третьего троичного логического элемента соединен с шиной заема.одноразрядного двоичного -. ,вычитателя, отличающийс я тем, что, с целью повышения быстродействия, вычитатель содержит пятый троичный логический элемент, причем второй вход первой группы первого троичного логического элемейта соединен с выходом третьего, с первым входом первой группы четвертого и с первым входом первой группы пятого троичных логических элементов, первый вход второй группы первого троичного логического элемента соединен с первым входом второй группы пятого троичного логи ческого элемента, второй вход второй группы которого соединен с тактовой шиной одноразрядного двоичного вычитателя,. выход второго троичного логического элемента соединен с шиной разности одноразрядного двоичного вычич-ателя, первый вход второй группы второго троичного логического элемента соединен с вторым входом второй группы третьего и с выходом пятого троичных логических элементов, второй вход первой группы третьего троичного логического элемента соединен с выходом четвертого троичного логического элемента, а второй вход первой группы пятого троичного логического элемента соединен с шиной уменьшаемого однрразряд-г ного двоичного вычитателя.

Вычитающий ( И группа)

О О О О О О О О

Условное обозначение

Выход элемента

Складс ающие

+(1

вЫУОА

) входы (I группа) -(-1

Вычитающие,Г.

+1-1

входы ( н группа)Ь +{-

Продолжение таблицы

Фиг, 2

П Яипульсы mfi&fipasHOto источника питат/я

ц. pi Запись -/

Считывание,0

считывание 1 r- Считы9ание-7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ферритовые логические элементы и узлы информационных систем | |||

| Под ред | |||

| Т.Н.Соколова и -Ф.А.Василье ва | |||

| Л., изл-во ВИКИ им | |||

| А.Ф.Можайского | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| -с | |||

| Питательное приспособление к трепальным машинам для лубовых растений | 1922 |

|

SU201A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ; | |||

Авторы

Даты

1984-11-15—Публикация

1983-05-11—Подача