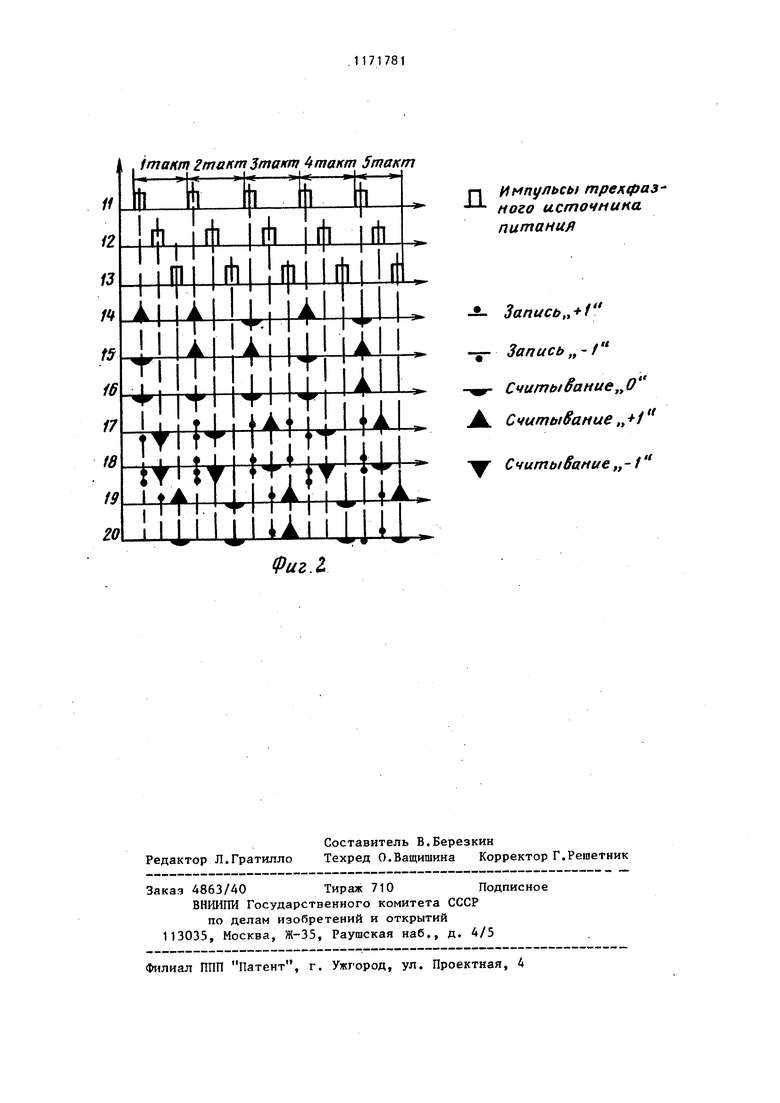

1117 Изобретение относится к области вычислительной техники и может быть использовано при проектировании сумматоров и вычитателей цифровых вычислительных устройств. Целью изобретения является сокраще ние количества оборудования. На фиг. 1 представлена функциональная схема последовательного двоично го вычитателя; на фиг. 2 - временная диаграмма его раёоты при вычитании пятиразрядного, двоичного числа 101100 (|-22|(,) из пятиразрядного двоичного числа 010112 (+11 10 ) и условные обозначения. Последовательный двоичный вычитатель содержит троичные логические элементы 1-4, шины 5-10 уменьшаемого, вычитаемого, тактовая, обнуления, результата и заема соответственно. 2 Шина 5 соединена с первыми входами вторых групп элементов 1 и 2. Шина 6 соединена с первыми входами первых групп элементов 1 и 2. Шины 7 и 8 соединены с вторым входом вто- 2 рой группы элемента 2 и первым входом второй группы элемента 4 соответственно. . Выход элемента 1 соединен с первым и вторым входами первой группы элемента 3 и первым входом первой группы элемента 4. Выходы элементов 2 и 3 соединены с первым входом второй группы элемента 3 и шиной 9 соответственно. Выход элемента А соединен с вторыми входами первых групп элементов 1 и 2 и шиной 10. Система тактового питания двоич,ного вычитателя трехфазная, при этом 40 каждый следующий разряд на шину уменьшаемого или шину вычитаемого поступает через три фазы (один такт). На фиг. 2 обозначены диаграммы 11-13, соответственно импульсов 45 первой, второй и третьей фаз тактового питания двоичного вычитателя, диаграммы 14-16 соответственно сигналов на шинах 5,6 и 8, диаграммы 17-20 соответственно сигналов на выходах 50 элементов 1-4. На шины 5-8 поступают сигналы во время тактового импульса первой . фазы.На шины 5,6,9 и 10 поступают младшими разрядами вперед соответ- 55 ственно разряды уменьшаемого, вычитаемого, результата и заема в двоичном коде, причем 1 представляется 1 сигналом положительной полярности, а О - отсутствием сигнала. На шину 7 поступают сигналы положительной полярности с тактовой частотой и при отсутствии информации на первом и втором входах первой группы и на первом входе второй группы элемента 2 он является генератором сигналов отрицательной полярности. На шину 8 поступает сигнал положительной полярности (сигнал обнуления) во время поступления старших разрядов уменьшаемого и вычитаемого. Тактовыми импульсами второй и третьей фаз считывается информация с элементов 1 и 2, 3 и 4 соответственно. Двоичный вычитатель выполнен на четырех троичных логических элементах, каждый из которых выполняет троичные операции (таблица), которые образуют полную систему логических функций. Первый и второй входы группы элемента- логически эквивалентны между собой. +10 0+1 +1 +1 О О +1 О О +1 +1 +1 О О Продолжение таблицы Рассмотрим.работу одноразрядного двоичного вычитателя на примере вычи тания положительного числа 22,о из п ложительного числа 1 1 ,Q , представленных в виде двоичных пятиразрядных чисел. Уменьшаемое число 11,Q предст ляется сигналами положительной поля ности в первом, втором и четвертом разрядах и отсутствием сигналов в третьем и пятом разрядах. Вычитаемое число 22 |(j представляется сигнгшами положительной полярности во втором, третьем и пятом разрядах и отсутствием сигналов в первом и четвертом разрядах. Во время тактового импульса пер вой фазы первого такта положительнь сигнал (первый разряд уменьшаемого)через шину 5 подается на первые входы вторых групп элементов 1 и 2, а положительный сигнал через шину 7 подается на второй вход второй группы элемента 2. Импульсом второй фазы с элемента 1 считывается отрицательный сигнал, который передается на второй вход первой группы элемента 3. Импульсом третьей фазы с элемента 3 считывается положительный сигнал, который передается на шину 9, образуя первый разряд результата вычитан.ия, Во время тактового импульса первой фазы второго такта положительный сигнал (второй разряд умень шаемого ) через шину 5 подается на первые входы вторых групп элементов 1 и 2, положительный сигнал (второй разряд вычитаемого) через шину 6 подается на первые входы первых групп элементов 1 и 2, а положи11 шину 7 подаеттельный сигнал ся на второй вход второй группы элемента 2. Во время тактового импульса первой фазы третьего такта положительный сигнал (третий разряд вычитаемого) через шину 6 подается на первые входы первых групп элементов 1 и 2, а положительный сигнал через шину 7 подается на второй вход второй группы элемента 2.Импульсом . второй фазы с элемента 1 считывается положительный сигнал,который передается на первые входы первых групп элементов 3 и 4. Импульсом третьей фазы с элемента 3 считывается положительный сигнал, который передается па шипу 9, образуя третий разряд результата вычитания, а с элемента 4 считывается положительный сигнал, который передается на шину 10 и вторые входы первых групп элементов 1 и 2. . Во время тактового импульса пер- , вой фазы четвертого такта положительный сигнал (четвертый разряд уменьшаемого) через шину 5 подается на первые входы вторых групп элементов 1 и 2, а положительный сигнал через шииу 7 подается на второй вход второй группы элемента 2. Во время тактового импульса первой фазы пятого такта положительный сигнал (пятый разряд вычитаемого) через шину 6 подается на первые входы первых групп элементов 1 и 2, положительные сигналы через шины 7 и 8 подаются на второй вход второй группы элемента 2 и первый вход второй группы элемента 4. Импульсом второй фазы с элемента 1 считывается положительньй сигнал, который передается на первые входы первых групп элементов 3 и 4. Импульсом третьей фазы с элемента 3 считывается положительный сигнал, который передается на шину 9, образуя пятый разряд результата вьшнтания. Таким образом, на шину результата. поступает отрицательное число - 11,, представленное положительньми сигналами в первом, третьем и пятом разрядах и.отсутствием сигналов во втором и четвертом разрядах.

imanrnZmaKmSmaicm такт 5та к т

Фиг. 2.

гп t nynbcb) трекфаз ного источника питания

-JL Запись., - Запись,,-/ Считы ёание „ О А Считывание „ /

Считывание „-1

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Сумматор-вычитатель | 1984 |

|

SU1171782A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Преобразователь троичного кода 1,0,1 в двоичный код | 1982 |

|

SU1078423A1 |

| Двоичный счетчик импульсов | 1981 |

|

SU1001486A1 |

| Двоичный п-разрядный счетчик импульсов | 1979 |

|

SU782166A1 |

ЦОСЛЕДОВАТЕЛЬНЬЙ ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ, содержащий четыре троичных логических элемента, причем первые входы первых групп первого и второго троичных логических элементов соединены между собой, первые входы вторых групп первого и второго троичных логических элементов соединены между собой, выход первого троичного логического элемента соединен с первым и вторым входами первой группы третьего и первым входом первой группы четвертого троичных логических элементов, выход четвертого троичного логического элемента соединен с вторыми входами первых групп первого и второго троичных логических элементов и шиной заема вычитателя, выход второго троичного логического элемента соединен с первым входом второй группы третьего троичного логического элемента выход третьего троичного логического элемента соединен с шиной результата вычитателя, тактовая шина и шина обнуления вычитателя соединены с вторым i входом второй группы второго и первым входом второй группы четвертого троич(Л ных логических элементов соответственно,о тли чающийся тем,что, с целью сокращения количества оборудования, шины уменьшаемого и вычитаемого вычитателя соединены с первым входом второй группы и первым входом первой группы первого троичного логического элемента соответственно. .

| Комбинационный двоичный сумматор-вы-чиТАТЕль | 1979 |

|

SU824205A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычитания | 1978 |

|

SU811249A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-07—Публикация

1984-02-20—Подача