та соединены соответственно с первым входом первой группы первого троичного логического элемента и с выходом четвертого троичного

логического элемента, второй вход первой группы восьмого троичного логического элемента соединен с шиной управления сумматора - вычитателя .

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный двоичный вычитатель | 1984 |

|

SU1171781A1 |

| Двоичный сумматор | 1980 |

|

SU857976A1 |

| Двоичный сумматор | 1980 |

|

SU918945A1 |

| Троичный сумматор | 1978 |

|

SU953637A1 |

| Одноразрядный двоичный вычитатель | 1983 |

|

SU1124289A1 |

| Троичный сумматор | 1983 |

|

SU1137461A1 |

| Сумматор по модулю три | 1982 |

|

SU1057941A1 |

| Одноразрядный двоичный вычитатель | 1982 |

|

SU1043639A1 |

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Сумматор по модулю три | 1976 |

|

SU669354A1 |

СУММАТОР-ВЫЧИТАТЕЛЬ, содержащий восемь троичных логических элементов, причем первый вход первой группы первого троичного логического элемента соединен с входом первого слагаемого сумматора-вычитателя, выход первого троичного логического элемента соединен с первым и вторым входами первой группы второго и с первым входом первой группы третьего троичных логических элементов, первый вход второй группы первого и первый вход первой группы четвертого троичных логических элементов соединены с входом второго слагаемого сумматора-вычитателя, выход третьего троичного логического элемента соединен с первым входом первой группы пятого троичного логического элемента, выход которого подключен к первому, входу второй группы шестого троичного логического элемента, выход которого соединен с первым входом второй группы второго троичного логического элемента, выход четвертого троичного логического элемента соединен с первым входом первой группы седьмого троичного логического элемента , первый вход второй груп-, пы которого подключен к выходу восьмого троичного логического элемента, первый вход первой группы которого соединен с шиной сброса сумматора-вычитателя, отличающийся тем, что, с целью прощения конструкции и повышения быстродействия второй вход второГ; группы первого троичного логического элемента соединен с выходом пятого троичного логического элемента, второй вход первой группы которого подключен к выходу седьмого и к второму входу первой группы четверто(Л го троичных логических элементов, выход второго троичного логического с элемента соединен с выходом суммы сумматора-вычитателя, второй вход первой группы третьего троичного логического элемента соединен с выходом восьмого троичного логического элемента, первый вход первой группы которого соединен с первым входом ч второй группы третьего троичного логического элемента, второй вход с: второй .группы которого подключен к первому входу второй группы четвертого, к первому входу первой группы шестого троичньк логических элементов и к тактовой шине сумматоравычитателя, вторые входы первой и второй групп шестого троичного логического элемента соединены соответственно с первым входом первой группы первого и с первым входом первой группы четвертого троичных логических элементов, вторые входы первой и второй групп седьмого троичного логического элемен

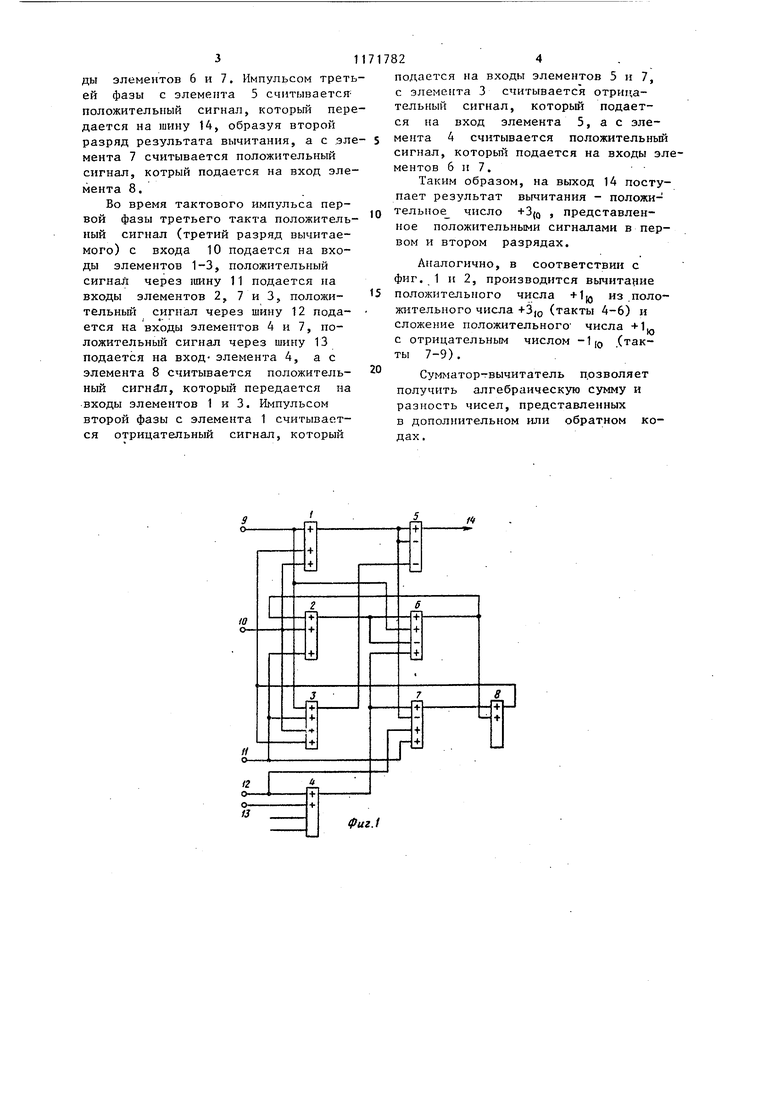

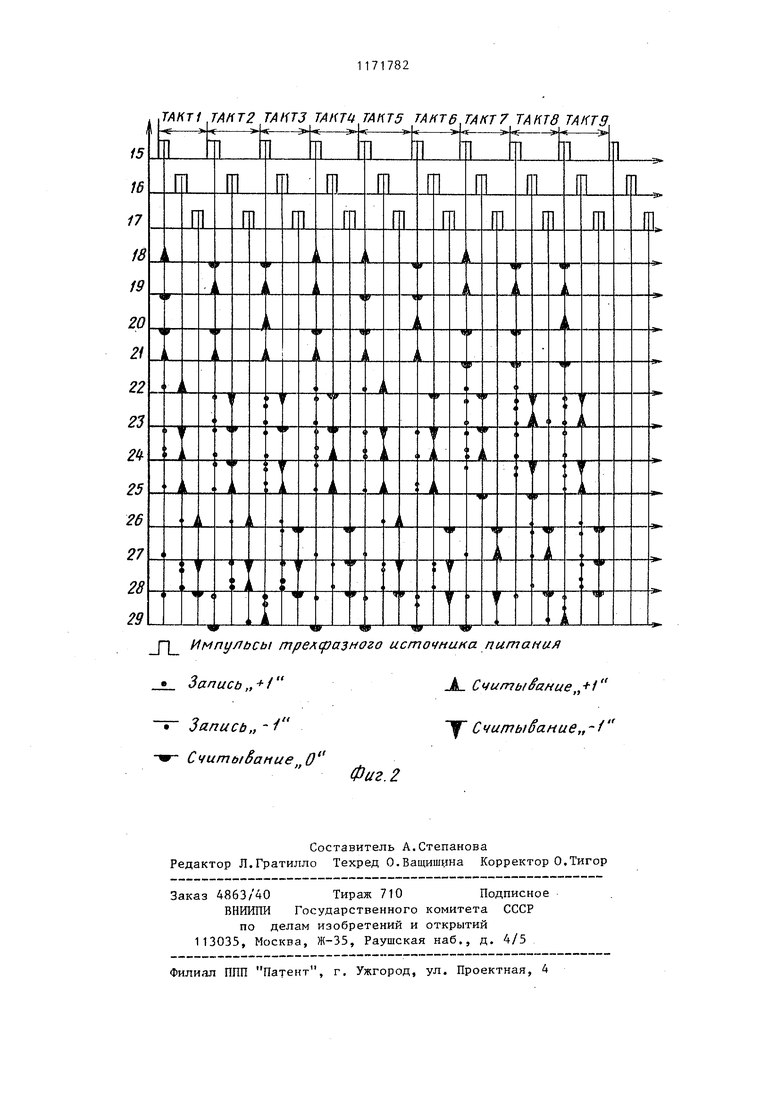

Изобретение относится к области вычислительной техники и может быть использовано в вычислительных устройствах и устройствах дискретной автоматики. Целью изобретения является упрощение конструкции и повышение быстро действия сумматора-вычитателя. На фиг. 1 представлена функциональная схема сумматора вычитателя; на фиг, 2 - временная диаграмма его работы. Сумматор-вычитатель содержит троичные логические элементы 1-8 и имеет входы 9 и 10 слагаемых; тактовую шину 11, шину 12 сброса, шину 13 управления и выход 14 суммы. На входы 9 и 10 поступают младшими .раз рядами операнды, причем 1 предста ляется сигналом положительной полярности, а О - отсутствием сигнала. По шине 11 поступают сигналы положительной полярности с тактовой частотой. По шине 12 поступает сигна положительной полярности (сигнал сброса) во время поступления старших (знаковых) разрядов на входы 9 и 10. Если на шину 13 подаются сигналы положительной полярности, то сумматор-вычитатель работает в режиме вы читания, т.е. вход 9 является входом уменьшаемого, а вход 10 - входом вычитаемого. Если на шине 13 отсутст вуют сигналы, то сумматор-вычитател работает в режиме суммирования, т. входы 9 и 10 являются входами слагаемых. Тактовыми импульсами второй и третьей фаз считывается информация с элементов 1-4 и 5-7, соответственно. Рассмотрим работу сумматора-вычи тателя на примере вычитания из пол жительного трехразрядного числа 001(,д) отрицательного трехразрядного числа 110 (-2,о). Уменьшаемое число 001 представляется сигналами положительной полярности в первом разряде и отсутствием сигналов во втором и третьем (знаковом) разрядах. Вычитаемое число 110 представляется сигналами положительной полярности во втором и третьем (знаковом) разрядах и отсутствием сигнала в первом разряде. Во время тактового импульса первой фазы первого такта положительный сигнал (певьшш разряд уменьшаемого) с входа 9 подается на первью входы элементов 1 и 3 и вход элемента 6, положительный сигнал через шину 11 подается на входы элементов 2 и 7 и вход элемента 3, а положительный сигнал через шину 13 подается на вход элемента 4.Импульсом второй фазы с элемента 1 считается положительный сигнал, который подается на вход элемента 5, с элемента 2 считывается отрицательный сигнал,который подается на вход элемента 6,. а с элемента 4 считывается положительный сигнал, который подается на входы элементов 6 и 7. Импульсом третьей фазы с элемента 5 считывается положительный.сигнал, который передается на выход 14, образуя первый разряд результата вычитания. Во время тактового импульса первой фазы второго такта положительный сигнал (второй разряд вычитаемого) с входа 10 подается на входы элементов 1-3, положительный сигнал через шину 11 подается на .входы элементов 2, 7 и 3, а положительный сигнал через шину 13 подается на вход элемента 4. Импульсом второй фазы с элемента 1 считьгоается отрицательный сигнал, который подается на входы элементов 5 и 7, а с элемента 4 считывается положительный сигнал,который подается на вхо3ды элементов 6 и 7. Импульсом трет ей фазы с элемента 5 считывается положительный сигнал, который пер дается на шину 14, образуя второй разряд результата вычитания, а с зл мента 7 считывается положительный сигнал, котрый подается на вход эле мента 8. Во время тактового импульса первой фазы третьего такта положитель ный сигнал (третий разряд вычитаемого) с входа 10 подается на входы элементов 1-3, положительный сигнал через тину 11 подается на входы элементов 2, 7 и 3, положительный сигнал через шину 12 подается на входы элементов 4 и 7, положительный сигнал через шину 13 подается на вход- элемента 4, ас элемента 8 считывается положительный сигнал, который передается на входы элементов 1 и 3. Импульсом второй фазы с элемента 1 считывается отрицательный сигнал, который 824 подается на входы элементов 5 и 7, с элемента 3 считывается отрицательный сигнал, который подается на вход элемента 5, а с элемента 4 считывается положительный сигнал, который подается на входы элементов 6 и 7. Таким образом, на выход 14 поступает результат вьгаитания - положительное число +3{Q , представленное положительными сигналами в первом и втором разрядах. А алогично, в соответствии с фиг. 1 и 2, производится вычитание положительного числа +IKJ из положительного числа +3|о (такты 4-6) и сложение положительного числа +1i с отрицательным числом -1 ты 7-9). Сумматор-вычитатель позволяет получить алгебраическую сумму и разность чисел, представленных в дополнительном или обратном кодах.

| Двоичный сумматор | 1981 |

|

SU1001088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ферритовые логические элементы и узлы .информацнонных систем./Под ред | |||

| Т.Н.Соколова и Ф.А.Васильева | |||

| - Л.: ЛВИКА им | |||

| А.Ф.Можайского, 1970, с | |||

| Эксцентричный фильтр-пресс для отжатия торфяной массы, подвергшейся коагулированию и т.п. работ | 1924 |

|

SU203A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-08-07—Публикация

1984-03-21—Подача