Изобретение относится к вычислительной технике и предназначено для преобразования множества логических адресов в .реальные адреса,

- Известно устройство преобразования адресов,содержащее регистр логи|ческого адреса, табличный буфер,ком-параторы, группу элементов И и ре- гистр реального адреса CU.

l aHHoe устройство не идентифицирует вычислительный процесс, т.е. всем процессом выделена одна виртуальная память. Целесообразно каждому процессу выделить собственную виртуальную память, что требует идентификации процесса в устройстве. Недостатком этого устройства является отсутствие таких возможностей.

Наиболее близким к изобретению является.устройство динамического преобразования адреса в системе обработки данных с виртуальной памятью, содержащее регистр ключа, ассоциативную память, регистр.реального адреса, регистр логического адреса, первый вход устройства соединен с входом регистра логического адреса, первый выход которого соединен с первым входом регистра реального адреса, выход.Которого соединен с первым выходом устройства, второй вход koTOporo соединен с первым входом ассоциативной памяти и с входом регистра ключа, выход которого соединен с вторым входом ассоциативной памяти, третий вход которой соединен с вторым выходом регистра логического адреса, первый выход ассоциативной памяти соединен с вторым входом регистра реального адреса, а второй выход ассоциативной памяти соединен с вторым выходом устройства 2.

Однако данное устройство не ориентировано для организации виртуальной памяти с блочной структурой страницы, так как каждагй блок страницы потребовал бы отдельной ячейки в ассоциативной памяти, что снижает быстродействие устройства.

Цель изобретения - повышение быстродействия за счет минимизации времени загрузки блоков страницы.

Поставленная цель достигается тем,что в устройство, содержащее регистр ключа, ассоциативную память, регистр реального адреса, регистр логического адреса, вход логического адреса устройства соединен с информационным входом регистра логического адреса, выход индексов блока и байта которого соединен с входом индексов блока и байта регистра реального адреса7 выход которого соединен с выходом реального адреса .устройства, вход загрузки которЪго соединен с входом загрузки ассоциа ивной памяти и с информационным

входом регистра ключа, выход которого соединен с входом ключа ассоциативной памяти, вход индекса страницы которой соединен с выходом индекса страницы логического адреса, выход реального адреса ассоциативной памяти соединен с адресным входом регистра реального адреса, а первый управляющий выход ассоциативной памяти соединен с первым выходом режима поиска устройства, введены мультиплексор, регистр адреса, два дешифратора и шифратор, причем выход индекса блока регистра логического адреса соединен с входом первого деЬаифратора,-выход которого соединенс входом маски ассоциативной памяти эторой управляющий выход которой соединен с управляющим входом мультиплексора, выход которого соединен с информационным входом регистра адреса, выход которого соединен с входом второго дешифратора, выход которого соединен с адресным входом ассоциативной памяти, адресный выход которой соединен с входом шифратора, выход которого соединен с первым информационным входом, мультиплексора, второй информационный вход которого соединен с входом загрузки устройства, второй выход режима поиска которого соединен с вторым управляющим выходом ассоциативной памяти.

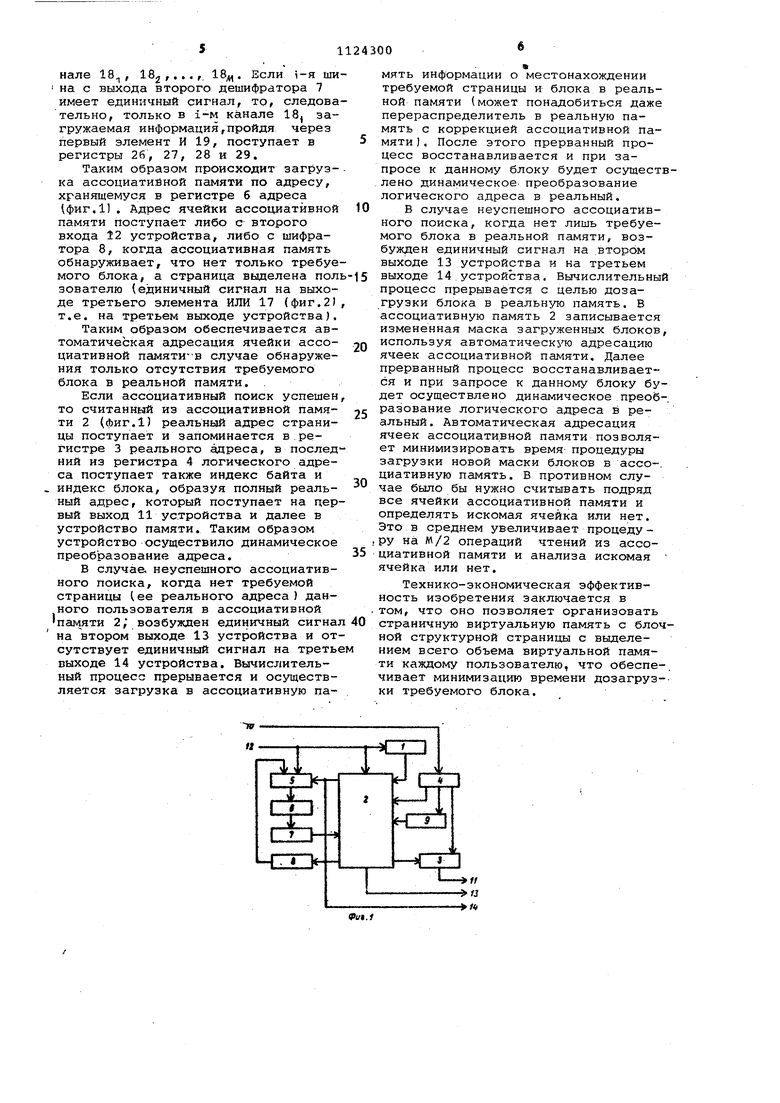

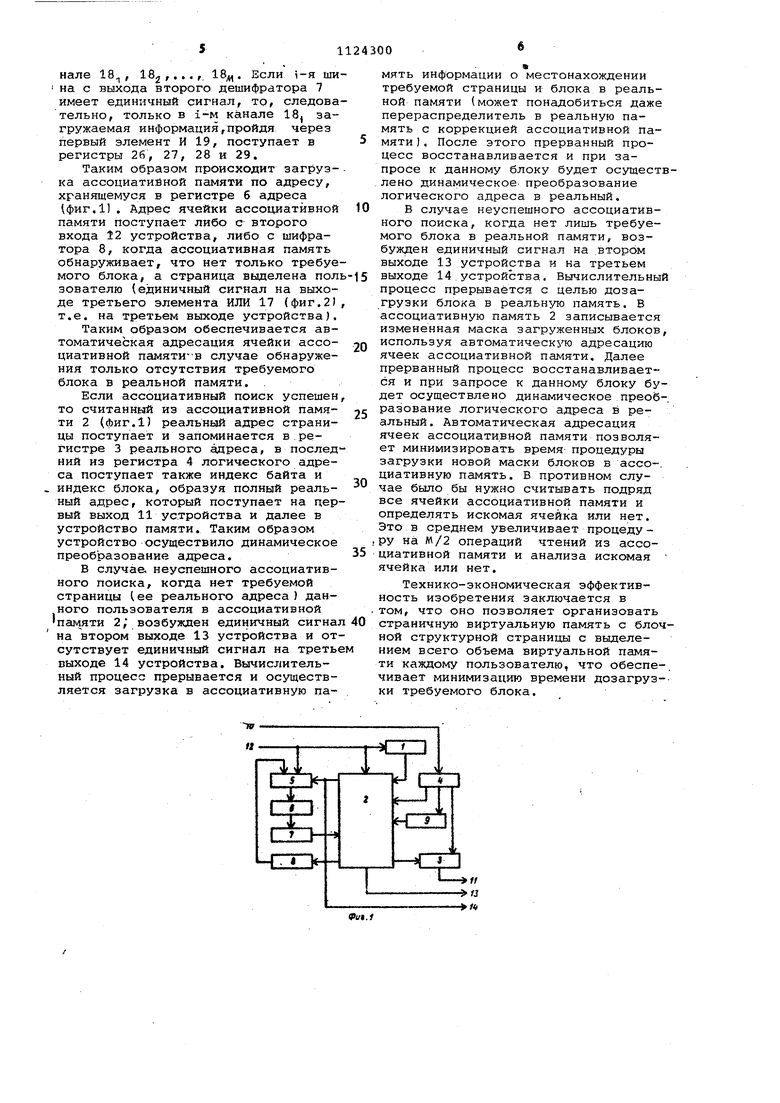

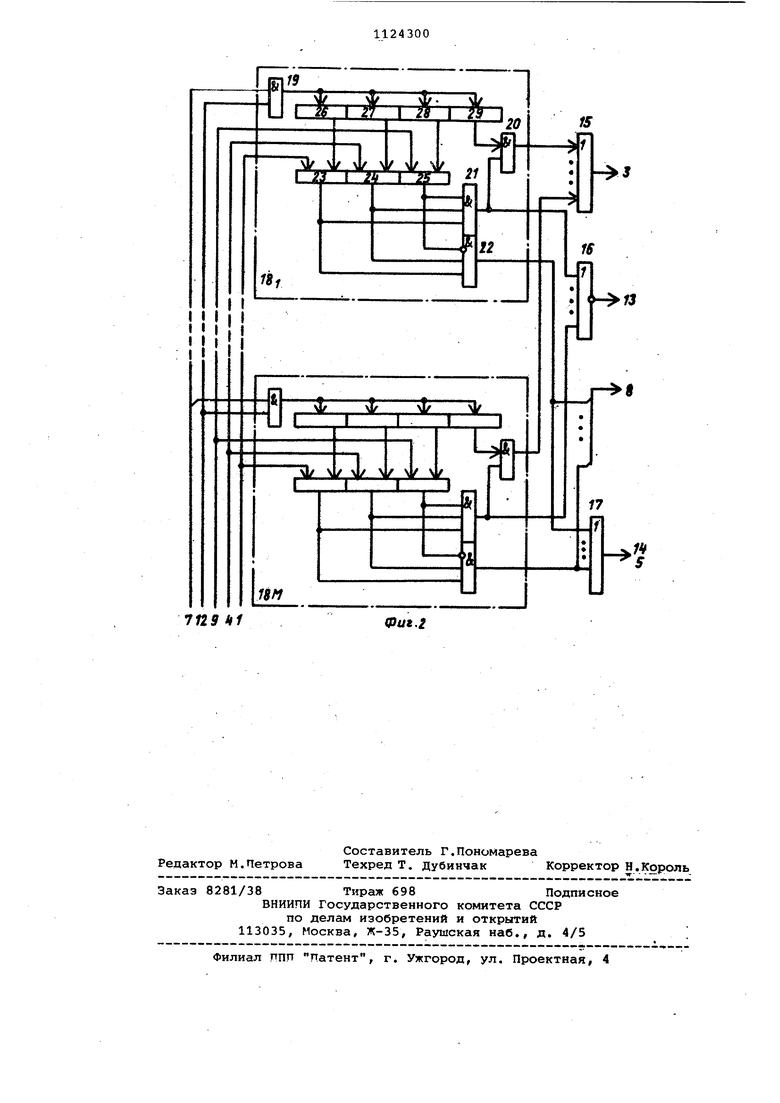

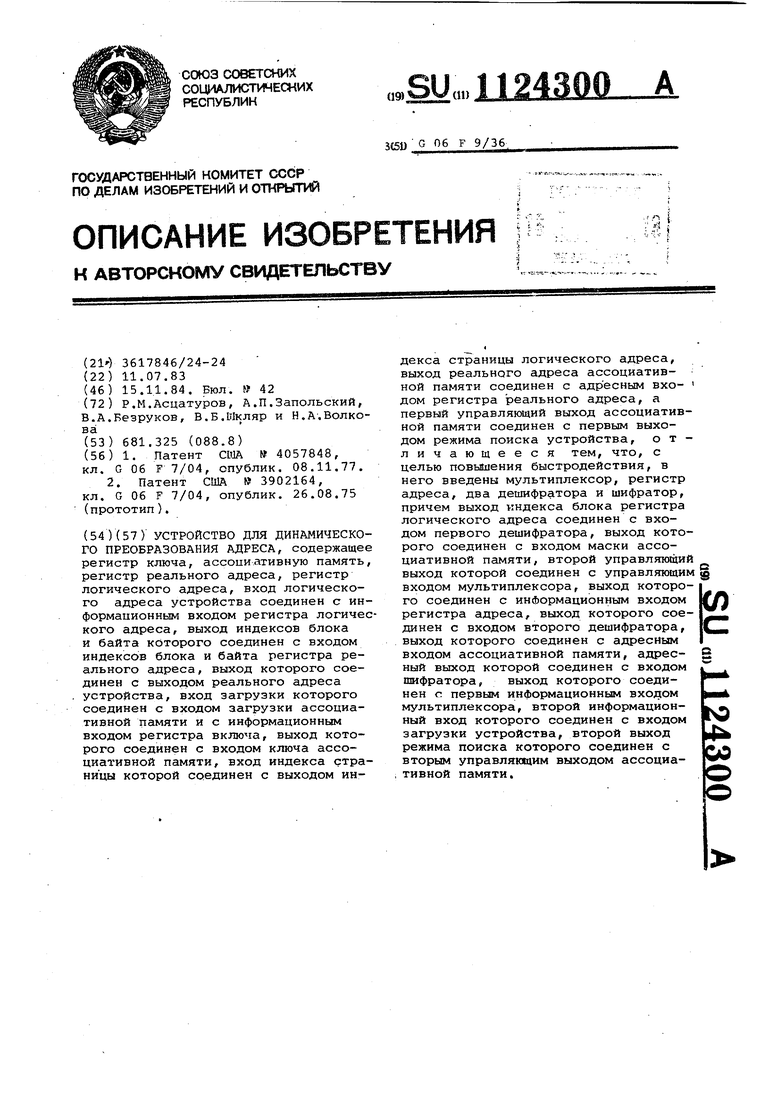

На фиг 1 приведена общая схема устройства; на фиг.2 - ассоциативная память.

Устррйство д;7я динамического преобразования адреса (фиг.11 содержит регистр 1 ключа, ассоциативную память 2, регистр 3 реального адреса, регистр 4 логического адреса, мультиплексор 5, регистр б адреса, второй дешифратор 7, шифратор 8 и дешифратор 9, первый вход 10 устройства, первый выход 11 устройства, второй вход 12 устройства, второй выход 13 устройства, третий выход 14 устройства.

Ассоциативная память 2 предназначена для хранения реальных адресов страницы и выдачи реального адреса по соответствующему ему логическому адресу и ключу, хранящемуся в регистре 1 ключа. Ассоциативная память (Фиг.2) содержит первый 15, второй 16 и третий 17 элементы ИЛИ и м каналов 18, ISg,..., 18„ , каждый из которых содержит первый 19, второй 20, третий 21 и четвертый 22 элементы И, первый 23, второй 24, третий 25 компараторы, первый 26, второй 27, третий 28 и четвертый 29 регистры.

Регистр 1 ключа (фиг.1) предназ начен для идентификации вычислительного процесса (пользователя),.В случае переключения с одного процессе

на другой в него загружается новый ключ идентифицирующий новый процесс

Первый.регистр 26 (фиг.2) содержит ключ, идентифицирующий вычислительный процесс, и предназначен для осуществления ассоциативного поиска в ассоциативной памяти 2. Второй регистр 27 содержит индекс страницы и предназначен для осуществления ассоциативного поиска. Третий регистр 2 содержит маску загруженных блоков.

Разрядность равна N - число блоков в странице. Единичное состояние разряда i. указывает на то, что i-й блок страницы загружен в реальную память, предназначен для осуществления ассоциативного поих;ка.

Четвертый регистр 29 содержит реальный адрес страницы, записанный в ассоциативную память 2. Реальный адрес страницы в случае успешного ассоциативного поиска поступает в регистр 3 реального адреса.

Устройство работает следующим образом..

Пусть реализована страничная виртуальная память с обменом между виртуальной памятью и реальной блоками. М блоков образуют одну страницу Причем различным вычислительным процессам (пользователям) предоставляется весь объем виртуальной памяти. С целью идентификации пользователя в регистр 1 ключа (фиг.1) записывается ключ, закрепленный за данным пользователем. Установка ключа происходит с второго входа 12 устройства. В ходе обработки в случае обращения к виртуальной памяти логический адрес поступает на первый вход 10 устройства и помещается в регистре 4 логического адреса. Индекс блока регистра 4 поступает в первый дешифратор 9, на выходе которого вырабатывается маска затребованного блока (наличие сигнала на i-й шине указывает, что затребован i-n блок в странице). Ключ из регистра 1 ключа (фиг.1, индекс страницы из регистра 4 логического адреса и маска затребованного блока из первого дешифратора 9 поступают в ассоциативную память 2, где осуществляется ассоциативный поиск. Ассоциативный поиск происходит следующим образом. Ключ из регистра 1 ключа поступает на второй вход первого компаратора 23 (фиг.21 в каждом канале 18, 18,..., 18,, где М. - число ячеек в ассоциативной памяти. На первый вход первого компаратора 23 поступает сигнал с первого регистра 26, содержащий ключ пользователя. В случае совпадения на выходе первого компаратора будет возбужден единичный сигнал. Аналогично, в случае совпадения индекса страницы из регистра 4 логического

адреса с содержимым второго регистра 27, на выходе второго компаратора 24 будет также возбужден единичный сигнал. Маска затребованного блока из первого .дешифратора 9 срав.нивается с маской загруженных блоков,- хранящейся в третьем регистре 28, в третьем компараторе 25. В случае совпадения масок на выходе третьего компаратора 25 Возбуждается

0 единичный сигнал.

В случае наличия на выходах всех компараторов 23, 24 и 25 канала 18. единичных сигналов на выходе третьего элемента И 21 будет единичный сигнал, который разрешит Передачу

5 сигнала регистра 29 чере.з второй элемент И 20 и далее через первый элемент ИЛИ 15 в регистр 3 реального адреса, т.е. ассоциативный поиск успешен и прочитана i-я ячейка ассо0циативной памяти.

В случае успешного ассоциативного поиска на остальных выходах ассоциативной памяти единичные сигналы отсутствуют (фиг. 2) .

5

В случае неуспешного ассоциативного поиска, т.е. на выходах всех трех компараторов 23, 24 и 25 в каждом канале 18., 18

18

нет

.

1

м

одновременно единичных сигналов, то

0 выход третьего элемента И 21 ни в 1одной группе не имеет единичного сигнала, поэтому на инверсном выходе второго элемента ИЛИ 16 будет возбужден единичный сигнал, который

5 поступает на второй выход 13 устройства и указывающий, что процесс динамического преобразования адреса невозможен.

Если в каком-то канале 18 не совпали лишь маски запрошенного блока,

0 т.е. на выходах первого 23 и второго 24 компараторов единичный сигнал, а на выходе третьего компаратора 25 нулевой сигнал, то на выходе четвертого элемента И 22 будет возбуж5ден единичный сигнал, который, пройдя через третий элемент ИЛИ 17, поступает на третий выход 14 устройства и мультиплексор 5. Наличие единичного сигнала на третьем выходе

0 устройства указывает, что нет только требуемого блока в реальной памяти, а страница выделена данному пользователю.

Одновременно с выхода четвертого

5 элемента И 22 канала 18 в шифратор 8 поступает единичный сигнал по i-й шине, указывающий, что требуемая страница данного пользователя ( ее реальный адрес) находится в i-и ячей0ке ассоциативной памяти.

Загрузка ассоциативной памяти происходит с использоваиием второго входа 12 устройства. Загружаемая информация поступает на второйвход первого злемента И 19 в каждом ка5нале 18, Если 1-я ши М на с выхода второго дешифратора 7 имеет единичный сигнал, то, следова 18. зательно, только в i-м канале гружаемая информация,пройдя через первый элемент И 19, поступает в регистры 26, 27, 28 и 29. Таким образом происходит загрузка ассоциативной памяти по адресу, хранящемуся в регистре 6 адреса 1ФИГ.1). Адрес ячейки ассоциативной памяти поступает либо с второго входа 12 устройства, либо с шифратора 8, когда ассоциативная память обнаруживает, что нет только требуе мого блока, а страница выделена пол зователю (единичный сигнал на выходе третьего элемента ИЛИ 17 (фиг.2) т.е. на третьем выходе устройства). Таким образом обеспечивается автоматическая адресация ячейки ассоциативной памяти-В случае обнаружения только отсутствия требуемого блока в реальной памяти. Если ассоциативный поиск успешен то считанный из ассоциативной памяти 2 (фиг.1) реальный адрес страницы поступает и запоминается в регистре 3 реального адреса, в послед НИИ из регистра 4 логического адреса поступает также индекс байта и . индекс блока, образуя полный реальный адрес, который поступает на пер вый выход 11 устройства и далее в устройство памяти. Таким образом устройство осуществило динамическое преобразование адреса. В случае неуспешного ассоциативного поиска, когда нет требуемой страницы (ее реального адреса) данного пользователя в ассоциативной памяти 2; возбужден единичный сигна на втором выходе 13 устройства и от сутствует единичный сигнал на треть выходе 14 устройства. Вычислительный процесс прерывается и осуществляется загрузка в ассоциативную память информации о местонахождении требуемой страницы и блока в реальной памяти (может понадобиться даже перераспределитель в реальную память с коррекцией ассоциативной памяти) . После этого прерванный процесс восстанавливается и при запросе к данному блоку будет осуществлено динамическое- преобразование логического адреса в реальный. В случае неуспешного ассоциативного поиска, когда нет лишь требуемого блока в реальной памяти, возбужден единичный сигнал на втором выходе 13 устройства и на третьем выходе 14 устройства. Вычислительный процесс прерывается с целью дозагрузки блока в реальную память. В ассоциативную память 2 записывается измененная маска загруженных блоков, используя автоматическую адресацию ячеек ассоциативной памяти. Далее прерванный процесс восстанавливается и при запросе к данному блоку будет осуществлено динамическое преобразование логического адреса в реальный. Автоматическая адресация ячеек ассоциативной памяти позволяет минимизировать время процедуры загрузки новой маски блоков в ассо-. циативную память. В противном случае было бы нужно считывать подряд все ячейки ассоциативной памяти и определять искомая ячейка или нет. Это в среднем увеличивает процеду ру на М/2 операций чтений из ассоциативной памяти и анализа исксшая ячейка или нет. Технико-экономическая эффективность изобретения заключается в том, что оно позволяет организовать страничную виртуальную память с блочной структурной страницы с выделением всего объема виртуальной памяти каждому пользователю, что обеспе-. чивает минимизацию времени дозагруз-ки требуемого блока.

7129 ffl

Фаг.I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для динамического преобразования адреса | 1985 |

|

SU1265771A1 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Устройство управления виртуальной памятью | 1980 |

|

SU1023336A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство динамического преобразования адреса | 1982 |

|

SU1022165A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

УСТРОЙСТВО ДЛЯ ДИНАМИЧЕСКОГО ПРЕОБРАЗОВАНИЯ АДРЕСА, содержащее регистр ключа, ассопиативную память, регистр реального адреса, регистр логического адреса, вход логического адреса устройства соединен с информационным входом регистра логического адреса, выход индексов блока и байта которого соединен с входом индексов блока и байта регистра реального адреса, выход которого соединен с выходом реального адреса устройства, вход загрузки которого соединен с входом загрузки ассоциативной памяти и с информационным входом регистра включа, выход которого соединен с входом ключа ассоциативной памяти, вход индекса страницы которой соединен с выходом индекса страницы логического адреса, выход реального адреса ассоциативной памяти соединен с адресным входом регистра реального адреса, а первый управляющий выход ассоциативной памяти соединен с первым выходом режима поиска устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены мультиплексор, регистр адреса, два дешифратора и шифратор, причем выход индекса блока регистра логического адреса соединен с входом первого дешифратора, выход которого соединен с входом маски ассоциативной памяти, второй управляющий i выход которой соединен с управляющим входом мультиплексора, выход которо(Л го соединен с информационным входом регистра адреса, выход которого соединен с входом второго дешифратора, выход которого соединен с адресным входом ассоциативной памяти, адресный выход которой соединен с входом пмфратора, выход которого соединен с первым информационным входом мультиплексора, второй информационный вход которого соединен с входом загрузки устройства, второй выход режима поиска которого соединен с вторым управляющим выходом ассоциативной памяти.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент QTJA № 4057848, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США 3902164, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Прибор для получения стереоскопических впечатлений от двух изображений различного масштаба | 1917 |

|

SU26A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-11—Подача