хранения страничной таблицы, шестой вход каждого из которых соединен с выходом блока коррекции таблицы, певюй и второй входы которого соедине соответственно с выходом старших разрядов регистра.общего назначения и с вторым выходом;блока управления замещением, второй и первый выходы которого соединены соответственно с первым входом регистра флажков и с третьим входом блока формирования физического адреса, четвертый вход которого соединен с входом Слово состояния программы устройства, первый и второй выходы блока формирования физического адреса соединен соответственно с входами регистра физического адреса и регистра замещаемой страни1цл, второй вход генератора адреса блока хранения соединен с выходом младших разрядов регистра общего назначения, вход Код операции оперативной памяти устройства соединен с седьмыми входами блоков страничной таблицы, выходы блока местного управления с восьмого по двенадцатый соединены с управляющим входом регистра заменяемой страницы и .вторым входом регистра флажков, управляющим .. входс генератра адреса блока хранения, вторим входом блока управления- активностью, восьмыми входами блоков хранения страничной таблицы, третьим входом блока коррекции таблйщл соответственно, выход регистра физического адреса соединен с адресным выходом устройства.

2.Устройство поп.1 отличающееся тем, что блок преобразования адреса содержит Узел элементов И, вычитатель и элемент ИЛИ-НЕ, входы которого подключены

к входам разрядов соответствующей группы второй входной шины блока и к выходной шине блока, к которой подключен выход элемента ЙЛИ-НЕ и выход узла элемента И, второй вход которого соединен с соответствующей группой разрядов, второй входной шины, а первый вход - с вых дом вычйтателя, первый вход которого соединен с выходной шиной и с соответствующей группой разрядов ;первой входной шины, остальные разряды которой подключены к выходной шине блока, а второй вход вычйтателя соединен с соответствующей группой разрядов второй входной дгины.

3.Устройство по П.1, отличающееся тем, ч1о блок хранения страничной таблицы содержит четырнадцать групп элементов памяти пять регистров, два дешифратора, ; элемент сравнения, узел управления занесением, три коммутатора, девять элементов И, причем группы разрядов

ТШрвого входа блока соединены с со ответствующими входами элементов t памяти первой и второй групп, с первым входом элемента сравнения-и с первым прямым входом первого элемента И, второй и третий прямые входы которого соединены с выходами эле- , ментов памяти пятой и шестой групп, выходы группы разрядов второго входа блока соединены с входами соответст-вукяцих элементов памяти третьей, тринадцатой и четырнадцатой групп, с первым и вторым входами первого коммутатора, с адресными входами элементов памяти всех групп и с первым и вторым входами узла управления занесением, выход которого соединен с управляющими входами элементов памяти всех групп, адресные входы элементов памяти первых шести групп соединены с выходом первого коммутатора, третий и четвертый входы которого соединены с выходами элементоЁ памяти тринадцатой и четыр надцатой групп соответственно группы paзpiядoв шестого входа блока соединены с третьим входом узла управления занесением и с входами элементов памяти пятой, шестой, одиннадцатой и двенадцатой групп, входы элегментов памяти девятой и десятой групп соединены соответственно с вы- . ходами первого и второго деилифраторов, входы которых соединены соответственно с выходами первого и второго регистров, разрядные входы первого, из которых соединены с выходами элементов памяти седьмой, девятой и одиннадцатбй групп, а выходы элементов памяти восьмой, десятой и двенадцатой групп соединены с разрядными входами второго

регистра, выходы элементов памяти первой, второй и третьей групп соединены с первым выходом блока, выходы элементов памяти третьей группы соединены с управлягацими входами второго и третьего коммутаторов и с четвертым входом узла управления занесением, пятый, шестой, седьмой и восьмой входы которого соеди- , нены с седьмым входом блока, пятым и третьим входами блока и выходом третьего регистра соответственно, выходы Элементов памяти первой

группы соединены с второй группой входов элемента сравнения, выход которого, выходы элементов памяти второй и шестой групп и второго коммутатора соединены с вторым выходом блока, выходы элементов памяти девятой и десятой групп соединены с первым и вторым входами третьего коммутатора соответственно, выходы элементов памяти одиннадцатой и двенадатой групп соединены соот5ветственно с первым и вторым входами второго коммутатора, четвертый вход блока соединен с входом третьего регистра,выход которого соединен с первьм прямым входом второго элемента И, -выход которого соединен с входами элементов памяти седьмой и восьмой групп, первые и вторые инве)рсные входы третьего элемента И соединены соот.ветственно с выходами первого элемента И и элементов памяти шестой группы, первые, вторые, и третьи инверсные входы четвертого и пятого элементов И соединены с выходами первого элемента И, элемента сравнения и второ,го коммутатора соответственно/ первые /вторые и третьи инверсные входы шестого, седьмого, восьмого и девятого элементов И соединены с выходами первого элемента И, элементов памяти пятой группы и второго KOMMyTHf-.

тора соответственно, четвертые инверсные входы четвертого, шестого и восьмого элементов И и четвертые прямые входы пятого, седьмого и девятого элемейтов И соединены с выходами элементов памяти четвертой группы, пятые пря№де входа шестого и седьмого элементов И и пятые прямые входы восьмого и девятого элементов И соединены с выходами старшего и младшего разрядов третьего коммутатора - соответственно, выходы третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого элементов И соединены с входами четвертого и -пятого регистров, выходы которых соединены с третьим выходом блока, восьмой вход блока соединен с управлякнцими входами де -шфраторов, регистров, узла управления занесением, первого коммутатора, с входом четвертой группы элементов памяти и с вторым прямым входом второго элемента И.

4.Устройство по П.1, о тли чающееся тем, что блок сравт нения содержит элемент сравнения, два элемента И, причем первеай вход элемента сравнения соединен с первым входом блока, второй вход элемента . сравнения соединен с вторым входом блока, первые прямые входы первого и второго элементов И соединены с выходом элемента сравнения, второй и третий прямые входы первого и вто1 го элементов И соединены с вторым рходом блока, четвертый инверсный вход первого элемента И и четвертый (ярямой вход второго элемента И соединены с вторым входом блока, выходы рервогр и-второго элементов И являются первым и вторым выходом блока.

5. Устройство по П.1, отличающееся тем, что генератор алрреса блока хранения содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор, коммутатор, причем входы эле-; ментов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соедиНены с первым входом генератора.

а первый и. второй входы коммутатора .соединены с вторым входом генератор |И выходом элементов ИСКЛЮЧЛЮИЕЕЕ ИЛИ Группы соответственно, вход дешифратора соединен с вторым входом генератора, управляющий вход коммутатор соединен с третьим входом генератора выходы коммутатора, детаифратора, соответствующих разрядов второго входа генератора и выходы группы элементов ИСКЛОЧАЩЕЕ 1ШИ являются выходом генератора.

6.Устройство по П.1, о т л ичающееся тем, что блок управления активностью содержит группу элементов памяти регистр, счетчик, группу элементов И, элемент

И, причем первый вход блрка соединен с адресным -входом элементов памяти группы, выход которых соединен с входом регистра, выход которого соединен с входом счетчика, выход которого соединен с входом элемента И и с первым входом элементов И группы, выходы которых соединены с входами соответствующих элементов памяти группы, выход элемента И является выходом блока управления активностью, второй вход блока соединен с управляющими входами элементов памяти группы и регистра, а также с ВТО1Ж1МИ инверсными входами элементов И группы.

7.Устройство по п.1, с т л ича ю щ е еся тем, что блок управления замещением содержит группу элементов НИИ, дешифратор, группу коммутаторов, узел приоритета, два элемента ИЛИ, причем входаа коммутаторов и входы элементов ИЛИ группы соединены с управл5пощим входом блока, выходы элементов ИЛИ группы соединены с входами дешифратора, первый выход которого соединен с управЛ}Пощими входами коммутаторов, выходил которых соединены с входами узла приоритета, выходы которого соединены с входами первого и второго элементов ИЛИ соответственно, выход узла приоритета и выходы первого и второго элементов ИЛИ. соеди1нены с первым выходом блока, второй

выход дешифратора соединен с вторым выходом блока.

8. Устройство по П.1, о т л и-:;Ч а ю ад е е с я тем, что блок кор;рекции таблшда содержит четыре элемента Ни элемент ИЛИ, причем первые входа первого, второго и третьего элементов И.соединены с первым входом блока, первый вход четверто-го элемента и соединен с вторым входом блока, выходы первого и четвертого элементов И.соединены с входами элемента ИЛИ, выход которого

и выходы второго, третьего, и четвер того :Элементов ,И подключены к выходу блока, третий Bxdh блока соеди нен с вторыми входами первого, второго, третьего и четвертого элег ментов И.

9. Устройство по П.1, о т л ича-ю щ е е с я тем, что блок формирования физического адреса содержит когФ1утаторы, формирователи, элемент И, причем первый вход первого коммутатора соединен с первым входом блока, соответствующие разряды второго входа первого коммутатора соединены с первым и вторым входами блока, выходом второго коммутатора и первого формирователя, вход которого соединен с второй группой входов блока, управляющий вход второго коммутатора соединен с второй группой входов блока, входы второго коммутатора соединены- с первой группой входов блока, первый выход блока соединен с выходом первого коммутатора, управляющий вход которого соединен с четвертым входом блока, третий вход блока соединен с входом второго формирователя и с управляющим входом третьего коммутатора, входа koTOpoi o соединены с первой группой входов блока, второй выход блока соединен с выходами второго формирователя, с выходом элемента И, с выходом третьего коммутатора и вторым входом блока, первый инверсный и второй прямой входы элемента И соединены с третьим входом блока,, соответственно.

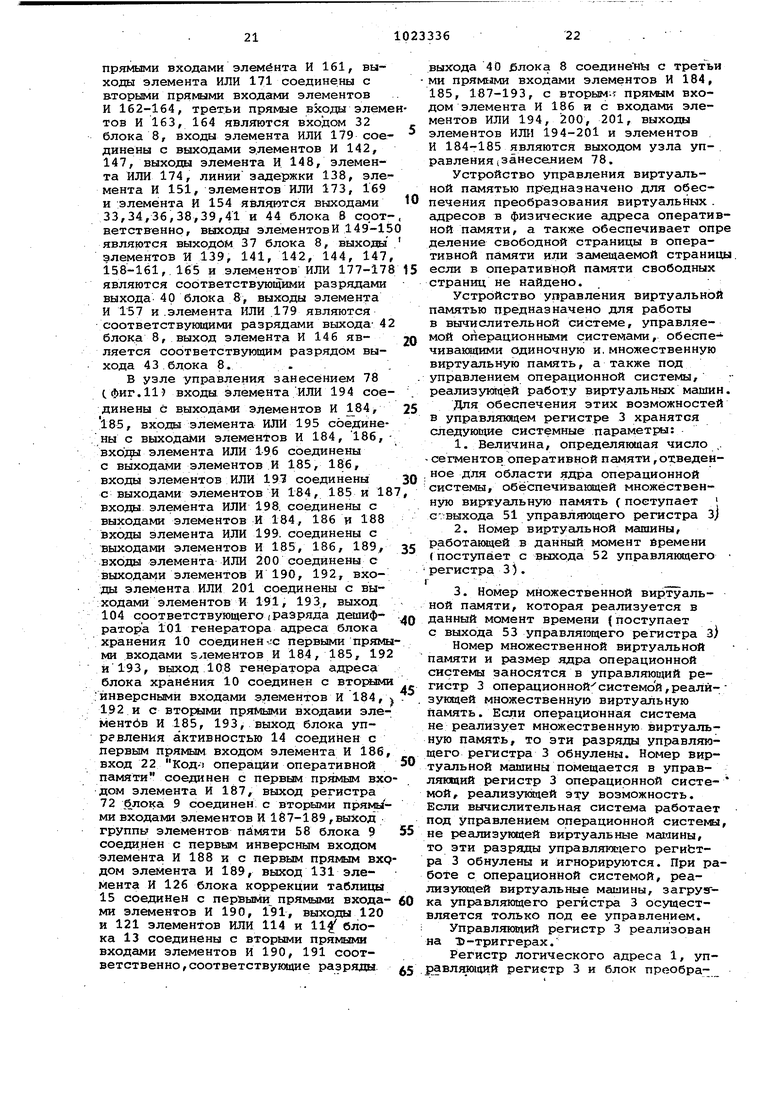

1Q. Устройство по П.1, от личающееся тем, что блок местного управления содержит линию задержки, элементы И, ИЛИ, триггеры, причем первые прямые входы первого, второго, третьего, пятого, шестого, седьмого, восьмого и девятого элементов И, входы первого, второго и третьего элементов ИЛИ и- первый вход первого триггера соединены с вторвам йходом блока местного управления, третьим входом которого являются вторые прямые входы первого, второго, пятого, десятого, одиннадцатого, двенадцатого, тринадцатого, четырнадцатого и пятнадцатого элементов И, входы четвертого, пятого и шестого элементов ИЛИ и второй вход перйого триггера, выход которого соединен с BTOpjjM инверсным входом седьмого элемента И и с вторым прямым входом восьмого элемента И, выход первого элемента И соединен с первыми прямыми входами четвертого, двенадцатого, тринадцатого семнадцатого, восемнадцатого, девятнадцатого и двадцатого элементов И, выход седьмого эле мента И соединен с первыми прямыми : входами двадцать первого, двадцать ; второго,двадцать третьего и двадцать четвертого элементов И, выход вось

мого элемента И соединен с первыми прямыми входами одиннадцатого, шестнадцатого, двадцать пятого, двадцать шестого и двадцать седьмого элементов И, второй прямой вход десятого элемента И соединен с выходом первого элемента ИЛИ, первый прямой вход двадцать восьмого элемента И является первым входом блока местного управления, к четвертому входу которого подключены второй прямой вход первого элемента И и третий инверсный вход второго элемента и, выходы второго, семнадцатого и воаемнадца-; того элементов И соединены с входами i седьмого элемента ИЛИ, вход линии задержки соединен с выходом восьмого элемента ИЛИ, входы которого соединены с выходами второго и семнадцатого элементов И, к пятому входу блока местного управления подключены входы девятого и десятого элементов ИЛИ, выход девятого элемента ИЛИ соединен с четвертым прямым входом семнадцатого элементам и с первЕлм входом второго триггера, выход которого соединен с третьим инверсным входом тринадцатого элемента И и с третьими прямыми .входами четвертого и пятого элементов И, выход которого соединен с первым входом четвертого триггера, выход которого соединен с вторым входом двадцать восьмого элемента И, выход которого соединен с третьими .инверсными вхоп дами семнадцатого и девятнадцатого

элементов И и с третьим прямым входом восемнадцатого элемента И, выход десятого элемента ИЛИ соединен с первым входом третьего триггера, выход которого соединен с третьим прямым входом двенадцатого элемента И, выход Четырнадцатого элемента И соединен с вторыми входами второго

и третьего триггеров и с вторыми прямыми входами семнадцатого, девятнадцатого, двадцатого и двадцать первого элементов И, вторые прямые входал шестнадцатого и двадцать второго элементов И соединены с выходом Пятнадцатого элемента И, выход шестого элемента ИЛИ соединен с вторыми прямыми входами третьего, четвертого, шестого, девятого и двадцать седьмого элементов И, выходы двадцать третьего и двадцать пятого элементов И соединены с входами одиннадцатого элемента ИЛИ, выходы двадцать четвертого и двадцать шестого элементов И соединены с входами двенадцатого элемента ИЛИ, выход второго элемента ИЛИ соединенсвторым вхоло1М четвертого триггера, вахоп четвертого элемента ИЛИ соединен

с вторым прямым входом двадцать тpe

тьего элемента И, выход пятого элемента ИЛИ соединен с вторыми прямыми входами двадцать Четвертого, двадцать пятого и двадцать шестого элементов И, третьи прямые входы двадцать пятого и двадцать шестого элементов И подключены к шестому входу блока, входы тринадцатого элемента ИЛИ соединены с выходами четвертого и девятого элементов И, выходы десятого эле:мента И, восьмого элемента ИЛИ, линии задержки, тринад цатого элемента И, седьмого и третьего элементов ИЛИ и шестнадцатого элемента И соединены с первым, вторым, четвертым, шестым, оедьмьам, девятым, двенадцатым выходами блока соответственно, выходы одиннадцатого и двенадцатого элементов И подключены к пятому выходу блока местного управления, выходы первого, третьего, четвертого, шестого, девятого; двенадцатого, двадцать первого, двадцать второго и двадцать седьмого элементов И и одиннадцатого и двенгивдатого элементов ИЛИ подключены к восьмому выходу блока местного управления, выходы девятнадцатого эле.мента И и тринадцатого элемента ИЛИ подключены к десятому выходу -;. блока местного управления, выход восьмого элемента И подключен к одиннадцатому выходу блока.

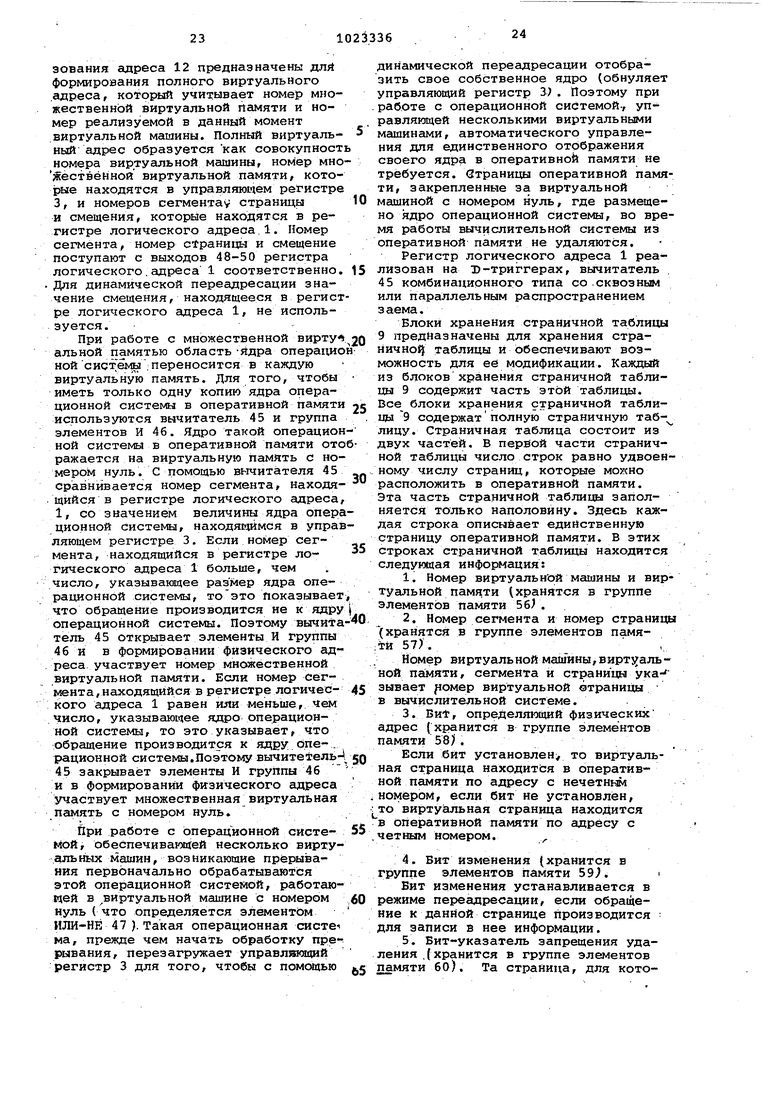

11. Устройство по п.З, отличающееся тем, что узел управления занесением содержит элементы И, ИЛИ, причем первый и втЬрой входы первого элемента ИЛИ соединены с выходами первого и второго элементов И, первый и второй входы второго элемента ИЛИ соединены с выходами первого и третьего элементов И, первый и второй входы третьего элемента или соединены с выходами второго и третьего элементов И, первый, вторбй и третий входы четвертого элемента ИЛИ соединены с выходами первого, второго и четвертого элементов И, первый, .второй и третий входы пятого элемента ИЛИ соединены с выходами первого, третьего и пятого элементов И, первый, второй и третий входы шестого элемента ИЛИ соединены с выходами второго, третьего и шестого элементов И, первый и второй входы седьмого ИЛИ соединешл с выходами седьмого и восьмого элемента И, первый и второй входы восьмого элемента ИЛИ соединены с выходами девятого и десятого элементов И, первый вход узла соединен с первыми прямыми входами первого, второго, восьмого и десятого элементов И второй вход узла соединен с вторыми инверсными входами первого и восьмого элементов И и с вторыми прямыми входами второго и десятого элементов И, седьмой вход узла соединен с первым прямым входом третьего элемента И, пятый вход узла управления соединен с первьич прямым входом четвертого элемента И, восьмой вход узла соединен с вторыми прямыми входами четвертого, пятого и шестого элементов И, четвертый вход узла соединен с первым инверсным входом пятого элемента И и с первым прямым входом шестого элемента- И, третий вход узла соединен с первыми пря1Ф1ми входами седьмого и девятого элементов И, соответствующие разряды шестого входа узла соединены с вторыми прягллми входами седьмого и девятого элементов И соответственно, ,управляющий вход узла соединен с третьими пряшами входс1ми первого, второго, .четвертого, пятого, шестого, седьмого, восьмого, девятого и десятого элементов И, с вторыом прямым:--: входом третьего элемента И и с первым входом первого элемента ИЛИ третьими входами седьмого и вось.мого элементов ИЛИ, выходы элементов ИЛИ и первого и второго элементов И являются выходом узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для трансляции логических адресов в адреса памяти на магнитных дисках | 1981 |

|

SU966695A1 |

| Устройство для управления виртуальной памятью | 1986 |

|

SU1327113A2 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для выбора адреса | 1973 |

|

SU784814A3 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство динамического преобразования адресов | 1978 |

|

SU765805A1 |

| СПОСОБ ФОРМИРОВАНИЯ ВИРТУАЛЬНОЙ ПАМЯТИ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2011 |

|

RU2487398C1 |

1. УСТРОЙСТВО УПРАВЛЕНИЯ ВИРТУАЛЬНОЙ ПАМЯТЬЮ, содержащее регистры логического и физического адреса, управлягощий регистр, регистр общего назначения, буферный регистр, элемент сравнения/ блоки сравнения, блок местного управления, причем вход.регистра логического адреса является входсяч логического адреса устройства, выход регистра логического адреса.соединен с первым входом эл&лента сравнения и с входом буферного регистра, выход которого соединен с вторым входом элемента сравнения, выход которого соединен-. . с первым входом блока местного управления, второй, третий и четвертый входа которого соединены с входом режима синхровходом.и с входом Слово состояния программы устройстЦ ва соответственно, выход блока сравнения соединен с пятым входом блока местного управления, выходы которого с первого до седьмой соединены соответственно. с управляквдим входом регистра логического адреса, управляющим входом буферного регистра, управлякнцим входом управляющего регистра, управляющим входом регистра физич;ес«г кого адреса, с выходом Прерываниа устройства, с первым управлягацим выходом устройства и с вторым управляющим выходом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введены N блоков хранения страничной таблицы (N- положительное, целое число), генератор адреса блока хранения, блок формирования физического адреса, блок преобразования адреса, блок управления замещением, блок управления активностью, блок коррекции таблицы, регистр замещаемой страницы и регистр флажков, причем разрядные выходы регистра логического адреса и управляющего регистра соединены соответственно с первой и второй входными шинами блока преобразования адреса, выходная шина которого соединена с первыми входами блоков хранения страничной таблицы, блоков сравнения,,блока формирования Фиэичес :кого адреса и генератора адреса блоiка хранения, выход которого соединен S с Вторыми входами блоков хранения станичной таблицы и блока формирования физического адреса и с первым входом блока управления активностью, выход которого соединен с третьим входом каждого из блоков хранения страничной таблицы, первые выходы которых соединены с первой группой входов блока фору(ирования физичес; кого адреса, вторая группа входов ког торого соединена с выходами блоков сравнения, вьЕсоды блоков сравнения соединены с четвертыми входами соответствующих блоков хранения страричной таблицы, второй выход каждого из которых соединен с вторым входом соответствующего блока сравнения, третьи выходы блоков хранения страничной таблицы соединены с группой входов блока управления замещением, перВ1& выход которого соединен с шестым входом блока местного управления и с.пятЕлми входами каждого из блоков

Изобретение относится к вычислительной технике, в частности к системам виртуальной памяти, и может быть использовано в вычислительных маши- , нах и системах с виртуальной памятью,

Известно устройство управления виртуальной памятью,содержащее за- поминакадее устройство из дескрипторных регистров, в которые операционная система помещает соответствия между физическими и математическими

номерами страниц. При этом предполагается, что количество дескрипторных регистров равно максимально возможному для одной программы количеству страниц. Математический номер страницы в адресе представляет собой фактически номер дескрипторного регистра, который должен быть использован при формировании исполнительного адреса. Информация, Хранящаяся в дескрипторных регистрах, - это физ1гческие номера страниц Для определения физического адреса производится дешифрирование математического номера страни цы. Выбирается соответствуквдий дескрипторный регистр, содержимое которого определяет соответствующий физический адрес

Однако этот зариант характеризуется большими затратами оборудования для реализации дескрипторных регистров. Поэтому такой вариант реализации аппаратуры преобразования применим только в системах с очень малым количеством математических страниц.

Известно также устройство управления памятью, в котором аппаратура преобразования адресов отличается тем что каждый из дескрипторных регистров закреплен не за математическим номером страницы, а за определенной физической страницей,Информацию,которую ., операционная система засылает в дескрипторные регистры, представляет собой математические адреса страниц: в дескрипторный регистр, соответствующий определенной физической страницё, записывается математический номер, по которому программа будет обращаться к этой странице. Выходная информация из дескрипторных регистров поступает на входы схем совпадения. На другие входы схем совпадения поступает математический номер страницы. При обнаружении соответствия между математическим номером страницы и содержимым своего дескрипторного регистра схемой совпа дения формируется сигнал совпадения. Если сигнал совпадения не выдан ни одной из схем совпадения, то переадресация осуществляется с помощью таблиц переадресации 2.

Недостатками данного варианта являются большие затраты оборудования/: необходимого для реализации дескрипторных регистров и схем совпадения/

а также необходимость таблиц переадресации. В третьем варианте реализации аппаратуры преобразования каждый из дескрипторных регистров состоит из двух частей, где записываются математические номера стрйниц и соответствующие им физические номера. Выход разрядов каждого из дескрипторных регистров с математическим номером страницы соединен с первым входом соответстйукидей схемы совпадения, на второй вход каж.дои из которых поступает математический номер страницы. Нри совпадении математического номера страни-. цы в адресе обращения кпамяти с математическим номером страницы, записанным в дескрипторном регистре, соответствующая схема совпадения . вырабатывает сигнал совпадения.Этот сигнал управляет группой вантилей, соединенных с выходом той части

дескрипторного регистра, где находит ся физический номер страницы. Недостатком этого решения является его низкая скорость работы, обусловленная тем, что при-невозможности переадресации с помощью дескрипторных регистров/ количество которых мало, по сравнению с объемом оперативной памяти вычислительной системы, переадресация осуществляется программными или микропрограммными средствами.

Кроме того, это устройство не решает згшачи размещения страниц в one ративной памяти.

Наиболее близким к изобретению является устройство для динамического преобразования адресов, содержащее регистр логического адреса, управляюютй регистр, регистр физического адреса, ассоциативные регистры, регистр общего назначения, причем соответствугацие выходы регистра логического адреса соединены с входами ассоциативных регистров и регистра физического адреса соответственно, выходы соответствующих разрядов ре-. гистра логического адреса и управляющего регистра соединены с соответствующими входами арифметического устройства процессора, выход которого соединен с входом регистра общего назначения, выход которого соединен, с соответствующими входами регистра физического адреса и ассоциативных регистров, соответствующие входы устройства управления процессора соединены с управляющими входами управляющего регистра, регистра логического и физического адресов, ассоциативных регистров, регистра общего назначения З.

Недостатками известного устройства для динамического преобразования адресов являются его низкая скорость работы обусловленная тем, что при невозможности переадресации с поморДэЮ ассоциативных регистров, количество которых мало по сравнению с объемом оперативной памяти вычислительной системы, переадресация осуществляется программными или микропрограммными средствами, ограниченные функциональные возможности, заключающиеся в том, что это устройств не решает задачи размещения в оперативной памяти новой вводимой страницы, а также не определяет номера страницы в оперативной памяти, которая возможно будет замещаться.

Цель изобретения - повышение быстродействия устройства.

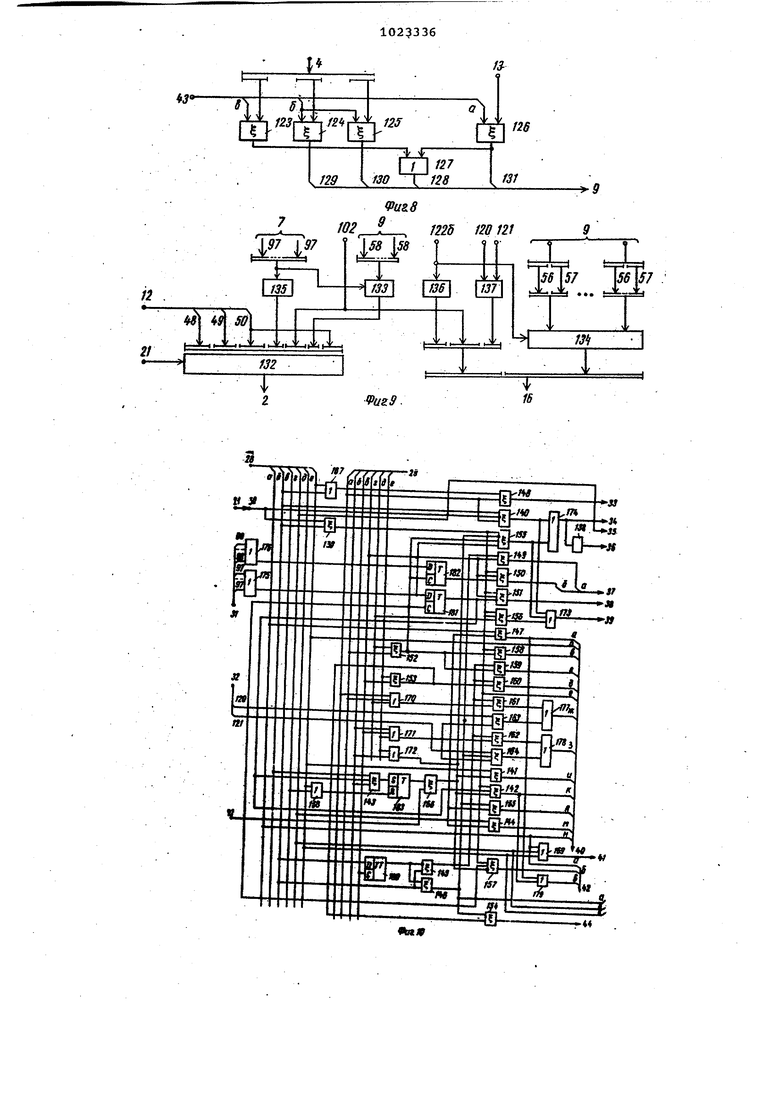

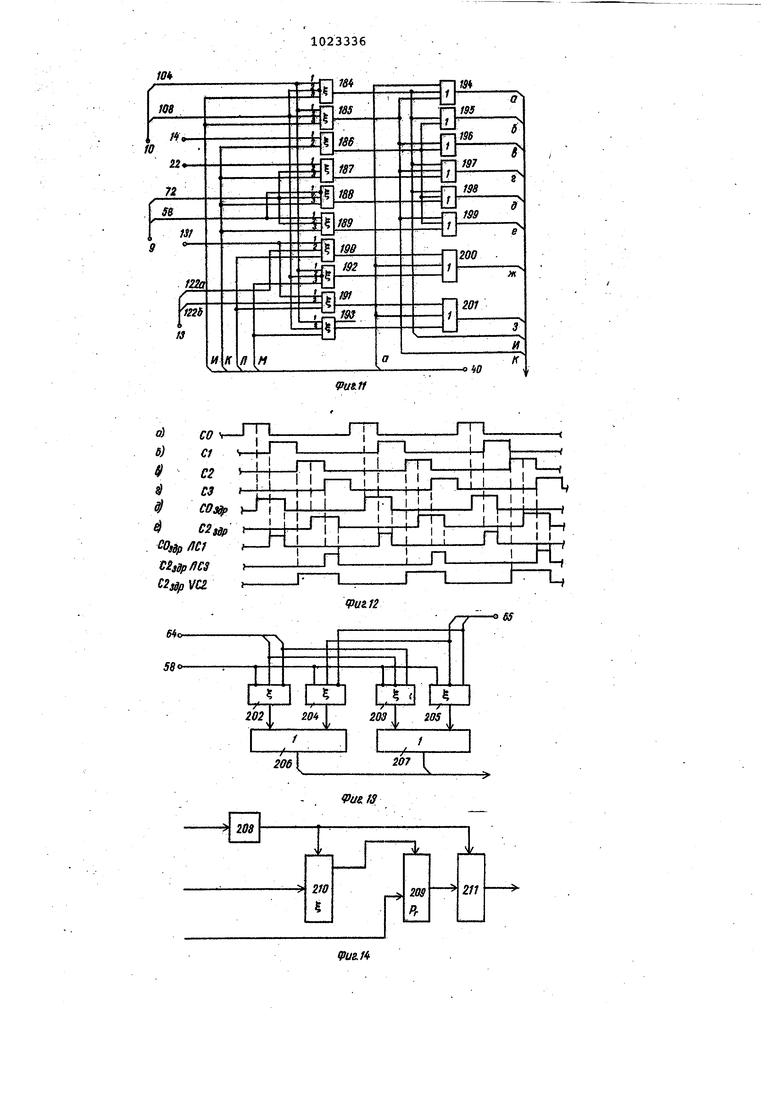

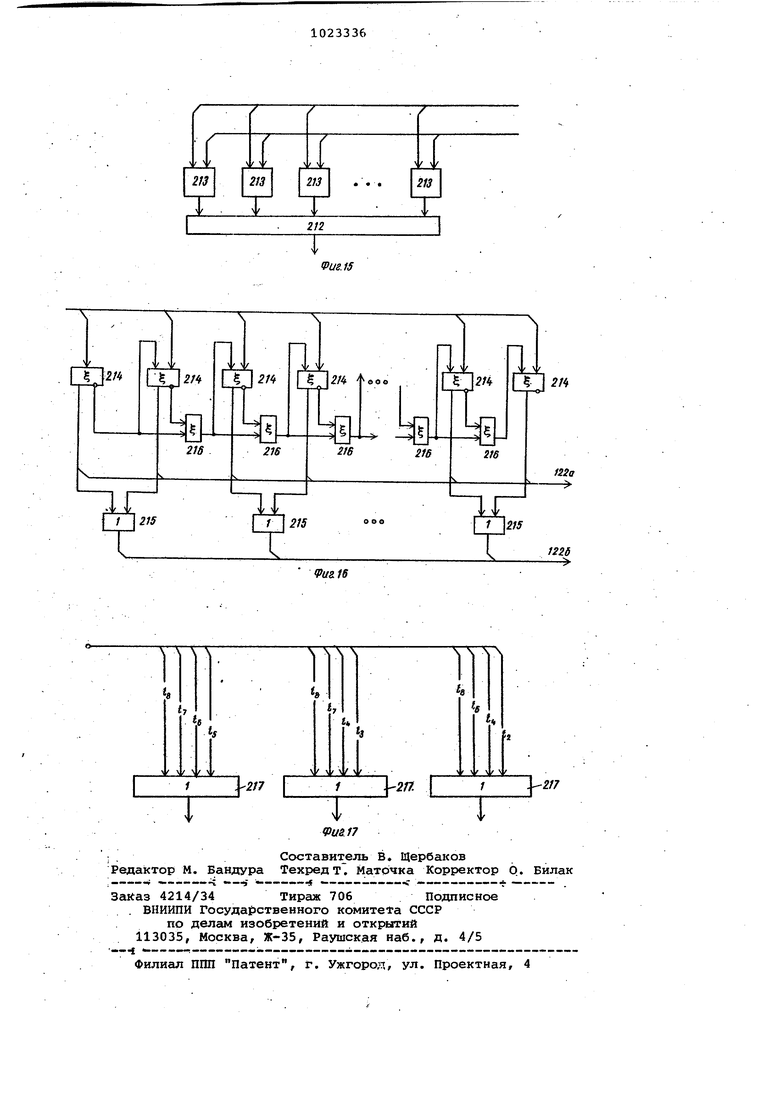

Поставленная цель достигается тем, что в устройство управления виртуальной памятью, содержащее регистры логического и физического адреса/ управляющий регистр/ регистр общего назначения, буферный регистр/ элемент сравнения, блоки Сравнения, блок местного управления, введены блоки хранения страничной таблицыj генератор адреса блока хранения, блок формирования физического адреса, блок преобразования адреса, блок управления замещением, блок управления активностью, блок коррекции таблицы, регистр замещаемой странищ и регистр флажков, причем вход регис ра логического адреса соединен с входом адреса устройства, выход ре гистра логического адреса соединен с первыми входами блока преобразования адреса, элемента сравнения и с.входе буферного регистра, выход которого соединен с вторым входом элемента сравнения, выход которого соединен с первым входом блока местного управления, другие пять входов которого соединены с управляющим входим устройства, с синхровходом устройства, с входом Слово состояния программы, с выходами блоков сравнения и с первым выходом блока управления замещением соответственно , выход управляющего регистра соединен со вторым входом блока преобразования адреса, выход которого соединен с первыми входами блоков хранения страниЧной таблицы, блоков сравнения, блока формирования физического адреса игенератора адреса блока хранения, выход которого соединен со вторыми входами блоков стра ничной таблицы и блока формирования физического адреса и с входом блока управления активностью, выход которого соединен с третьим входом каждо го из блоков страничной таблицы, пер вые выходы каждого из которых соединены с первой гр1уппой входов блока формирования физического адреса, вторая группа входов которого соединена с выходами каждого из блоков сравнения, которые соединены также с четвертыми входами соответствующих блоков хранения страничной таблицы, второй выход каждого из которых соединен со входом соответствующего бяока сравнения, третьи выходы блоков хра1нения страничной таблицы соединены с первым входом блока управления замещением, первый выясщ которого .соединен с шестым входом блока местного управления и с пятыми входами каждого из блоков хранения страничной Таблицы, шестой вход каждого из которых соединен с выходом блока коррекции таблицы, первый и второй входы которого соединены соотв1етствейно с выходом старших разрядов регистра общего назначения и с вторым выходом блока управления замещением, второй и первый выходы которого соединены соответственно с входом регистра флажков и с пятым Входом блока формирования физячееког адреса, четвертый вход которого соединен с вхрдом Слово состояния программы, первый и второй выходы блока формирования физического соединены соответственно с входами регистра физического адаеса и регистра замещаемой страницы, второй вход генератора адреса блока хранения соединен с выходом младших разрядов регистра общего назначения, вход Код операции оперативной памяти устройства соединен с седьмыми вхОдами блоков страничной таблицы, выходы блока местного управления свосьмого пО двенадцатый соединены соответственно с управляющими входами регистров логического и физического адреса, управляющего регистра, буферного ре гистра, блоков хранения страничной таблицы, генератора адреса блока хранения, блока управления активностью, блока коррекции таблицы, регистров замещаемой странш ы и флажков, с выходом Прерывание, с первым управлянкадм выходом устройства и с вторым управлякхцим выходом устройства , адресный выход устройства соединен с выходом регистра физического адреса. При этом блок преобразования адреса содержит вычитатель, группу, элементов И и элолент ИЛИ-НЕ, причем выходы соответствующих разрядов первого и второго входов блока соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход знакового разряда вычитателя соединен с первым входом группы элементов И, второй вход которой соединен с соот-. ветствующими разрядами второго входа блока, оставшиеся (разряды второго входа блока соединены с входами элемента ИЛИ-НЕ, выход которого и оставшиеся разряда второго входа блока, соответствукяцие разряды первого вхо- да блока и выход группы элементов И являются вькодом блока преобразования адреса. -. . Кроме того, блок хранения страничной таблицы содержит четьчрнадцать групп элементов памяти пять регист ров, два детдафратрра, элемент сравнения, узел управления занесение, три кО1« татора, девять элементов И, причем соответствующие разряды первого входа блока соединены с входами первой и второй г руппы элементов памяти с первым входс 1 элемента сравнения и с первым прякнм входом первого элемента И, вторсЛ и третий пря1« е входы которого соединены с выходами пятой и шестой групп элементов памяти, соответствующие выходы группы разрядов второго входа блока соединены с входами третьей, тринадцатой и четырнадцатой групп элементов памяти, с первым и входами пе:рвого коммутатора, с адресными входами всех групп элементов памяти и с первым и вторым ..входами узла управления занесением, выход которого соединен с управляющими входами элементов памяти всех групп) aдpecныe входы элементов памя ти первых шести групп соединены с выходом первого коммутатора, третий и четвертый входы которого соединены с выходами тринадцатой и четырнад цатой групп элементов памяти соответственно, группы разрядов шестого входа блока соединены с третьим входом узла управления занесением и с входами элементов памяти пятой, шестой , одиннадцатой и двенадцатой rpyn входы девятой и десятой групп элемен тов памяти соединены соответственно с выходами первого и второго дешифра торов, входы котоЕих соединены соответственно с выходами первого и второго регистров, вход первого из которых соединен с выходами элементов памяти седьмой, девятой и одиннадцатой групп-а выходы восьмой, десятой и двенадцатой групп элементов памяти соединены с входом второго регистра выходы элементов памяти первой, второй и третьей групп соединены с первым выходом блока, выход третьей группы элементов памяти соединен так же с управляющими входами второго и третьего коммутаторов и с четвертым входом узла управления занесением, пятый, шестой, седьмой, и восьмой входы которого соединены с седьмым входом блока, пятым и третьим входам блока и выходом третьего регистра соответственно, ..выход первой группы элементов памяти соединен с второй группой входов элемента сравнения, выход которого и выходы второй и шес той групп элементов памяти и второго коммутатора соединены с вторым выходом блока, выходы девятой и десято групп элементов памяти соединены с первым и вторым входами третьего коммутатора соответственно, выходы одиннадцатой и двенадцатой групп эле ментов памяти соединеныгс первыми и вторым входами второго коммутатора четвертый вход блока соединен с третьего регистра,.выход которого соединен с первым прямым входом второго элемента И, выход ко торого соединен с входами седьмой и вось-мой групп элементов памяти, первые и вторые инверсные входы третьего :элемента И соединены с выходами первого элемента И и местой группы элементов памяти, первые, вторые и третьи инверсные входаа четвертого и пятого элементов И соединены с выходами первого элемента И, элемен;Та сравне-ния и второго коммутатора соответственно, первые, втор«ле и ,третьи инверсные входы шестого, седьмого, восьмого и девятого элементов И соединены с выходами первого элемента И, пятой группы, элементов памяти и второго коммутатора соответственно, четвертые инверсные входы четвертого, шестого и восьмого элементой И и четвертые прямые входы пятого, седьмого и девятого элементов И соединены с выходами четвертой группы элементов памяти, пятые прямые входы шестого и седьмого элементов И и пятые прямые входы восьмого и девятого элементов И соединены с вадходами старшего и младшего разрядов третьего колмутатора соответственно, выходы третьего, четвертого, пятого, шестого, седьмого, восьмого и девятого элементов- И соединены с входами четвертого и пятого регистров, входи четвертого и пятого регистров, выходы которых соединены с третьим выходом блока, восьмой вход блока соединен с управлякяцими входами дешифраторов, регистров, узла управления занесением, первого коммутатора, с входом четвертой группы элементов памяти и с вторым прямым входом второго элемента И. Причем блок сравнения содержит элемент сравнения, два элемента И, первый вход элемента сравнения соединен с первым входом блока, второй BXqitt элемента сравнения соединен с вторит входом блока:, первые прягуие входы nej)r вого и второго элементов И соединеш с выходом элемента сравнения, второй и третий прямые входы первого иавторого элементов И соединены с втоЕаш входом блока, четвертый инверсный взкед вход первого элемента И и четвертый прямой вход второго элемента И соедц нены с вторым входом блока, выходы первого и второго элементов И .Являются nepBtavj и вторим выходом блока. Кроме того, генератор адреса блохщ хранения содержит группу элементов ИСКЛЮЧАВДЕЕ ИЛИ, дешифратор, коммут«и тор, причем входы группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первым входом генератора, а первый и второ1| входы коммутатора соединены с Ьоот- , ветствуняцими разрядами второго вход гене ратора и выходом группы элемент той ИСКЛЮЧАЮВДБЕ ИЛИ соответствеино, вход дей1иФратора соединен с соответоТву1аци1ии разрядами второго входа гене ратора, управляющий вход коммутатора соединен с третгьим входом генератора« выходы коммутатора, соответствующих разрядов второго входа генератора и выходи дешифратора и группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходом генератора адреса блока хранения. Блок управления.активностью содерит группу элементов памяти, регистр, счетчик, группу элементов И, элемент

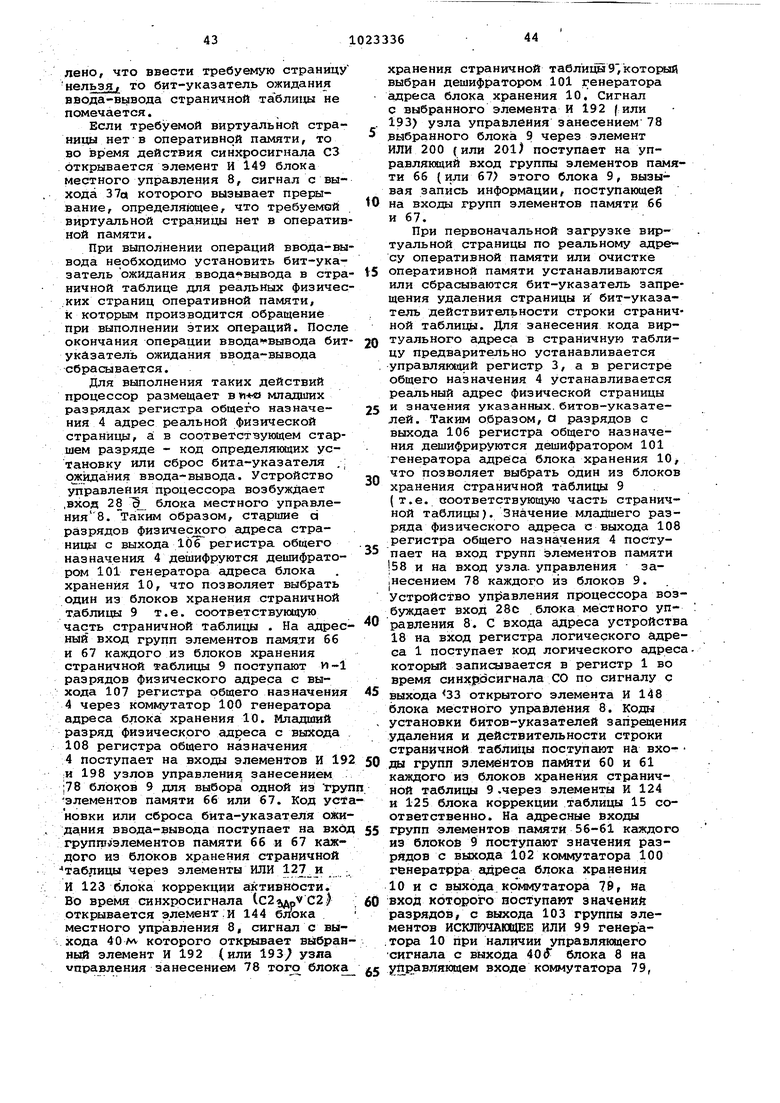

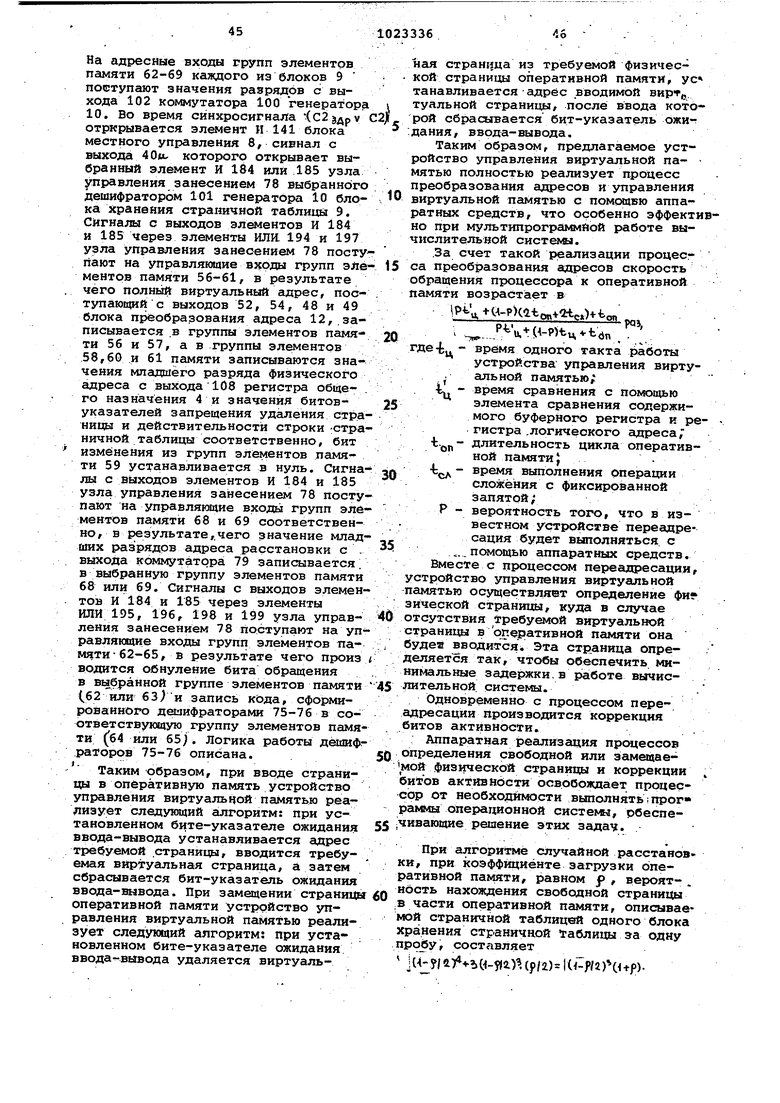

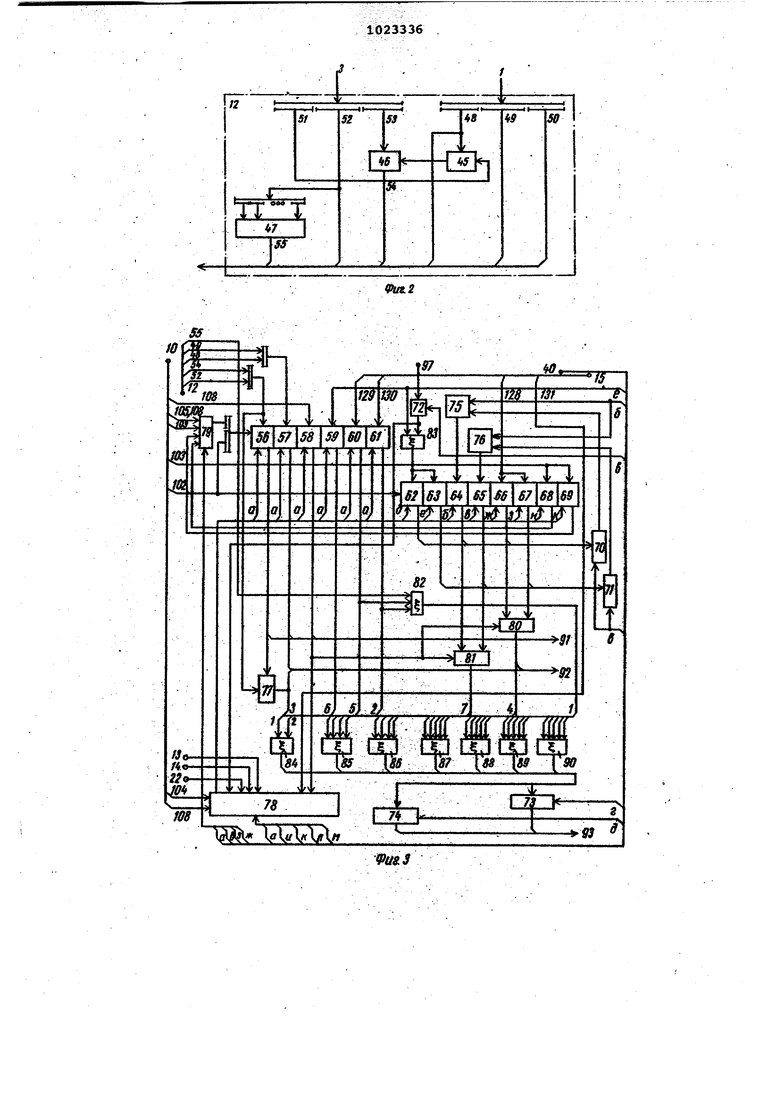

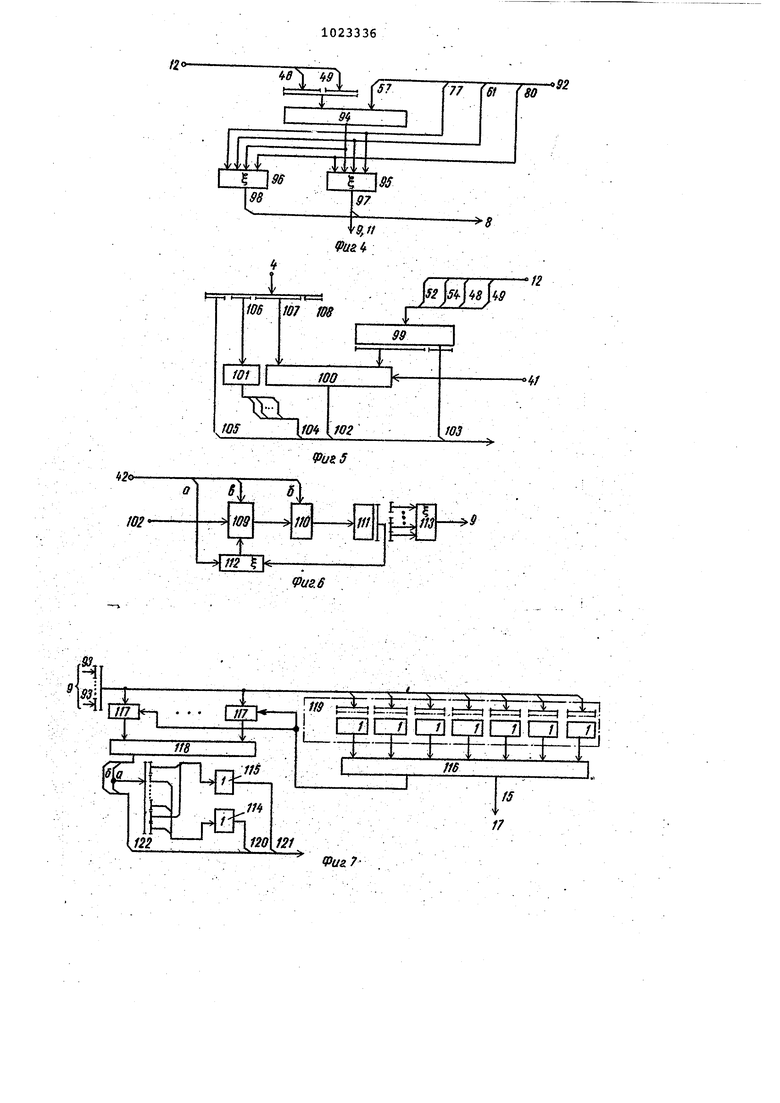

И, причем первый вход-блока соединён с адресным входом груйпы элементов памяти, выход которой соединен с вхо дом регистра, выход которого соедине с входом счетчика, выход которого содинен с входом элемента И и с первым входами группы элементов И, выход которой соединен с входом группы элементов памяти, выход элемента И явля ется выходом блока управления актив- ностью;, второй вход блока соединен с управляющими входами группы элетментов памяти и регистра, а также с вторыми инверсными входами группы элементов И.

При этом блок управления замещени ем содержит группу элементов ИЛИ, дешифратор, группу кс &1утаторов, узел приоритета, два элемента ИЛИ, причем, соответствуннцие разряды входа блока соединены с входами всех коммутаторов и с входс1ми группы элементов ИЛИ, выход которой соединен с входом дешифратора, первый выход ко торого соединен с управляющими входами коммутаторов, гагходы которых ;соединены с входами узла приоритета, соответствукяцие выходы которого соеД11нены с входами первого и второго элёментов ИЛИ соответственно, выход узла приоритета и выходы первого и второго элементов ИЛИ являются первым выходом блока управления замещением, второй выход дешифратора соединен с вторым выходом блока управления замшцения.

Блок коррекции таблицы содержит четыре элемента И и элемент ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с соответствующими разрядами первого входаблока, первый вход четвертого элемента И соединен с вторым входом блока, выходы первого И четвертого элементов И соединены с входами элемента ИЛИ, выход которого и выходы второго, третьего и четвертого элементов, И являются выходом блока, третий вход блока соединен с вторьши входами первого, второго, третьего и четвертого элементов И.

Кроме того, блок формирования Физического адреса содержит коммутаторы, формирователи, элемент И, причем первый вход первого ксйувиутатора соединен с первым входом блоки, соответствуклдие разряды второго входа первого коммутатора соединены с первым и BTpjHaiM входами блок, висход/сйл , второго коммутатора и первого формирователя, вход которого соединён с второй группой входов блока, управлякяцйй вход второго коммутатора соединен с второй группой входов блока фо| 1ирЬвания фиаического адреса, входы втррого коммутатора соединены с первой группой входов блока, пер

вый выход блока соединен с выходом первого коммутатора, управляющий вход которого соединен с четвертым блока, третий вход блока соединен с входом второго формирователя и с управлярзщим входом третьего коммутатора, входы которого соединены с первой группой входов блока формирования физического адреса, второй выход блока соединен с выходами вто рого формирователя, с выходом третьего коммутатора, с втор« м входом блока, с выходсм элемента И, первый инверсный и второй прямой входы элемента И соединены шестш4 и седьмым входом блока соответственно.

Блок местного управления содер- жит линию задержки, элементы И, ИЛИ, триггеры,. причем первые прямые входы первого, второго, третьего, пятого, шестого, седьмого, восьмого И девятого элементов И, входы первого, второго и третьего элементов ИЛИ, первый вход первого триггера и соответствующие разряды третьего восьмого, десятого и одиннадцатоговыхрдов блока местного управления являются соответствующими разрядами второго входа блока местного управления, третьим входом которогоЯВЛЯЮТСЯ вторые прямые входы второго, пятого, десятого, одиннадцатого, двенадаатого, тринадцатого, четырнадцатого и пятнадцатого элементов И входы четвертого, пятого и шестого элементов ИЛИ и второй вход первого триггера, вьвсод которого соединен с вторым инверсгаям входом седыдаго элемента И и с зторам прямым входрм восьмого элемента И, выхрд первого элемента И соединен с первыми прямыми входами четвертого, двенадцатого, тринадцатого, семнадцатого, восемнадцатого, девятнадцатого.и двадцатого элементов И, выход седьмого элемента И соединен с первыми пря-, Мыми входами двадцать первого, двёшцать второгю, двадцать третьего и двадцать четвертрго элементов И, выход восьмого элемента И соединен . с первыми прямыми входс1ми одиннадцатого, шестнадцатого , двадцать пятого двадцать шестого и двадцать седьмого элементов;И j второй прямой вход десятрго элемента И соединен с выходом первого элемента ИЛИ, первый прямой вход двадцать восьмрго элемента И является первшв входом блока местного управления, четвертым входом которог является второй вход первого элемента И и третий инверсный вход второго элемента И, выходы втррого, сё «надцатого и восемнадцатого элементов И соединены с входами седьмого элемента ИЛИ, вход линии задержки соединен с выходом восьмого элемента ИЛИ, входы которого соединены с выходами второго и семнадцатого элементов И | пятым входом блока местног управления являются входы девятого и десятого элементов ИЛИ, выход дев того элемента ИЛИ соединен с четвер тым прямым входом семнадцатого э.лемента И .и с первым входом второго триггера, Выход которого соединен с третьим инверсным входом тринадцатого элемента И и с третьими прямыми входами четвертого и пятого-: элементов И, выход которого соединен с первым входом четвертого триг гера, выход которого соединен с вто рым прямым входом двадцать восьмого элемента И, выход которого соединен с третьими инверсными входами семнадцатого и девятнадцатого элементов И и с третьим прямым входом восемнадцатого элемента И, выход деся того элемента ИЛИ соединен с первым входом третьего триггера, выход которого соединен с третьим прямым входом двенадцатого элемента И, выход, четырнадцатого элемента И соединен с вторыми входами второго и третьего триггеров и с вторыми прямыми входами семнадцатого, девятнадцатого, двадцатого и двадцать первого элементов И, вторые прямые входы шестнадцатого и двадцать второго элементов И соединены с выходом пятнадцатого элемента И, выход шестого элемента ИЛИ соединен с вто рыми прямыми входалш третьего, четвертого, шестого, девятого, двадцать седьмого элементов и, выходы двадцать третьего и двадцать пятого элементов И соединены с входами оди надцатого элемента ИЛИ, выходы двад цать четвертого и двадцать шестого элементов И соединены с входами две надцатого элемента ИЛИ, выход второ го элемента ИЛИ соединен с вторым входом четвертого триггера, выход четвертого элемента ИЛИ соединен с вторым прямым входом двадцать третьего элемента И, выход пятого элемента ИЛИ соединен с вторыми прямыми входами двадцать четвертого, двадцать пятого и двадцать шестого элементов И третьи прямые входа двадцать пятого и двадцать шестого элементов И являются шестым входом блока местного управления, входы тринадцатого элемента ИЛИ соединен с выходами четвертого и девятого элементов и, выходы десятого элемента И, восьмого элемента ИЛИ, линии задержки, тринадцатого элемента И, седьмого и третьего элементов ИЛИ и шеотнадцатого элемента И являются первым, вторым/ четвертвм, шестьФ и седьлалм девятым и двенадцатым выходами, блока местного управления соответственно, выходы одиннад цатого и двенадцатого элементов И являются пятым выходом блока местног управления, выходыпервого, третьего, четвертого, шестого,,девятого, двадцатого, двадцать первого, двадцать второго и двадцать седьмого элементов И и одиннадцатого и две- ; надцатого элементов ИЛИ являются сом ответствующими разрядами восьмого выхода блока местного управления, выходы девятнадцатого элемента И и тринадцатого элемента ИЛИ являются соответствующими разрядами десятого выхода блока местного управления, выход восьмого элемента И является соответствующим разрядом, юдиннадца. того выхода блока управления. При этом узел управления занесением блока страничной таблицы содержит элементы-И и ИЛИ, причем первый и второй входы первого элемента ИЛИ соединены с выходами первого и второго элементов И, первый и второй входда второго элемента ИЛИ соединены с выходами первого и третьего элементов И, первый и второй входал третьего элемента ИЛИ соединены с выходами .второго и третьего элементов И, первый, второй и третий входы четвертого элемента ИЛИ,соединены с выходами первого, второго и четвертого элементов И, первый, второй и третий входы пятого элемента ИЛИ соединены с выходами первого, третьего и пятого элементов И, первый, второй и третий входы шестого элемента ИЛИ соединены с выходами второго, третьего и шестого элементов И, первый и второй . седьмого элемента ИЛИ соединены с вь1ходами седьмого и восьмого элементов И, первый и второй входы восьмого элемента ИЛИ соединены с выходами девятого и десятого элементов И, первый вход узла управления соединен с первыми прямыми входами первого, второго, восьмого и десятого элементов И, второй вход узла соединен с вторыми инверсными входами первого и восьмого элементов И и с ВТО1ЯЛМИ прямыми входами второго и десятого элементов И, седьмой вход узла управления соединен с первым прямым входом третьего элемента И, пятый вход узла управления coe-t динен с первым пряюам входом четвертого элемента И, восьмой вход узла соединен с вторыми прямыми входами четвертого, пятого и шестого элементов И, четвертый вход узла соединен с первым инверсным входом пятого элемента И и с первым прямым входом шестого элемента И, третий вход узла соединен с первыми прямыМи входами седьмого и девятого элементов И, соответствукмщие разряды шестого входа узла соединены с вторыми прямлми входами седьмого и девятого элементов И соответственно, управляющий вход узла соединен с третьими прямыми входами первого, второго, четвертого. пятого, mecTord, седьмого, восьмого девятого и десятого эл ементов И, с .вторым прямым входом третьего эле мента И и с первым входом п-ервого элемента ИЛИ, третьими входа ли седь мого и восьмФго элементов ИЛИ, вы-, ходы элементов ИЛИ и первого, второ элементов И являются выходом узла управления занесением. На фиг.1 приведена структурная схема устройства управления виртуал ной памятью; на фиг.2 - функциональ ная схема блока преобразования адре са/ на фиг.З - то же, блока хранения страничной таблицы; на фиг.4 то же, блока сравнения,- на фиг.З то же, генератора адреса блока хранения; на фиг.6 - то же, блока управления активностью на фиг. 7 - то же, блока управления замещением/ . на фиг.8 - то же, блока коррекции таблицы, на фиг. 9 - то же, блока формирования физического адреса; на фиг. 10 - то же, блока местного управленияi на фиг.11 - то же, узла управления занесением блока хранения страничной таблии -г; на фиг. 12 диаграмма синхросигнайов/ на фиг.13 функциональная схема третьего коммутатора блока хранения страничной таблицы, на фиг.14 - то же, элемент памяти, на фиг. 15 - то же, элемента сравнения, на фиг.16 - Td же, узла приоритета; на фиг.17 - то же формирователя. Устройство управления виртуальной памятью (фиг.1) содержит регист логического адреса 1, регистр.физического адреса 2, управляющий регис 3, регистр общего назначения 4, буферный регистр 5, элемент сравнения б, блоки сравнения 7, блок местного управления 8, блоки хранения страничной таблицы 9, генератор адреса блока хранения 10, блок формирования физического адреса 11, блок преобразования адреса 12, блок управления замещением 13, блок управления активностью 14, блок корре ции таблигда 15, регистр замещаемой ст аницы 16, регистр флажков 17,вход 18 адреса устройства, управляющий , вход 19 устройства, синхровход 20 устройства, вход Слово состояния программы 21, вход 22 Код операци оперативной памяти, выход Прерыва ние 23,.первый управляквдий выход 2 устройства, второй управляющий выхо 25 устройства, адресныйвыход 26 устройства, входы 27-32 и выходы 33 44 блока местного управления. Блок преобразования адреса 12 (фиг.2) содержит вычитатель 45, группу элементов И 46, элемент ИЛИ-НЕ 47, первый вход блока, состо щий из 3-х групп разрядов 48-50, вт рой вход блока, состоящий из 3-х групп разрядов 51-53, --выход 54 груп ,пы элементов И 46, выход 55 элемента ИЛИ-НЕ 47. Блок хранения страничной таблицы 9 (фиг.З содержит группы.элементов памяти 56-69, регистры 70-74, дешифраторы 75 и 76,элемент сравнения 77, узел управления занесением 78, коммутаторы 79-81. элементы И 82-90 выходы 91-93 блока 9. Блок сравнения 7 (фиг.4) содержит элемент сравнения 94, элементы И 95 и 96, выходы 97-98 соответственно. Генератор адреса блока хранения 10 (фиг.5) содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 99, коммутатор 100, дешифратор 101, выходы 102-104 коммутатора 100, разрядов группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 99, дешифратора 101 соответственно, выходы 105-108 младшей группы разрядов регистра общего назначения 4. Блок управления активностью 14 (фиг.6) содержит группу элементов памяти 109, регистр 110, счетчик 111, группу элементов И 112, элемент И 113, Блок управления замещением 13 (фиг.7) содержит элементы ИЛИ 114 и 115, дешифратор 116, коммутаторы 117, узел приоритета 118, группу элементов ИЛИ 119, выходы 120-121 элементов ИЛИ 114 и 115, выход 122 узла приоритета 118. Блок коррекции таблицы 15 (фиг.87 содержит элементы И 123-126, элемент ИЛИ 127, выход 128 элемента ИЛИ 127, выходы 129-131 элементов И 124-126 соответственно. Блок формирования физического адреса 11 (фиг.9р содержит коммутаторы 132-134, формирователи 135-136, элемент И 137. Блок местного управления 8 (фиг.Ю). содержит линИю задержки 138, элементы И 139-166, элементы ИЛИ 167-179, триггеры 180-183. Узел управления занесением 78 (фиг.11) содержит элементы И 184-193, элементы ИЛИ 194-201. Коммутатор 81 (фиг.13) содержит элементы И 202-205, элементы ИЛИ 206. и 207. Элемент памяти (фиг.14) групп элементов памяти 56-59 блоков 9 и группы элементов памяти 109 блока 14 содержит дешифратор адреса 208, информационный регистр 209, группу элементов И 210, коммутатор 211. Элемент сравнения (фиг.15) содержит элемент ИЛИ-НЕ 212 и элементы ИСКЛЮЧАЩЕЕ ИЛИ 213. . Узел приоритета 118 (фиг.16) содержит элементы И 214, элементы ИЛИ 215, элементы И 216. Формирователи 135-136 (фиг.17) содержат элементы ИЛИ 217 (предпола гается, что устройство управления виртуальной памятью содержит восемь блоков страничной таблицы 9 и восем блоков сравнения 1), В устройстве управления виргтуаль ной памятью (фиг.1) вход 18 адреса устройства соединен с входом регист ра логического адреса 1, выход которого соединен с первыми входами блока преобразования адреса 12 и эл мента сравнения бис входом буферного регистра 5, выход которого сое динен с вторым входом элемента срав нения 6, выход которого соединен с входом 27 блока местного управления, входы 28, 29 которого соединены с управляюидим входом 19 устройства, с синхровходом 20 устройства, с входом 21 Слово состояния программы, с выходами блоков срав-нения 7 и с первым выходом блока уп равления замещением 13 соответственно/ выход управляющего регистра соединен с вторым входом блока преобразования адреса 12, выход которого соединен с первыми входами бло ков хранения страничной таблицы 9. блоков сравнения , блока формирования физического адреса 11 и генер тора адреса блока хранения 10, выход которого соединен с вторыми вхо дами блоков хранения страничной таб ли,цы 9 и блока формирования физичес кого адреса 11 и с входом блока управления активностью 14, выход кото рого соединен с третьими входами ка дого из блоков хранения страничной таблицы 9, первые выходы каждого из которых соединены с третьим входом блока формирования физического адреса 11, четвертый вход которого соединен с выходами каждого из блоков сравнения 7, которые соединены также с четвертыми входами соответствующих блоков хранения страничной таблицы 9, второй выход каждого из которых соединен с вторым входом , соответствующего блока сравнения 7, третьи выходы блоков хранения стра ничной таблицы 9 соединены с первым вхбдом блока управления замещением 13,-первый выход которого соединен с пятыми входами кахшого из блоков хранения страничной таблицы 9/ шестой вход каждого из которых соединен с выходом блока коррекции таблицы 15, первый и второй входы которого соединены соответственно с выхрдом старших разрядов регистра общего назначения 4 и с вторым вы-J ходом блока управления замещением 1 второй и первый выходы которого соединены соответственно с входом регистра флажков 17 и с пятым входо блока формирования физического адре 11, шестой вход которого соединен ,с входом 21 Слово состояния програ мы , первый и второй выходы блора . формирования физического адреса 11 соединены соответственно с входами регистра физического адреса 2 и регистра замещаемой страницы 16, второй вход генератора адреса блока хранения 10 соединен с выходами младших разрядов регистра общего назначения 4, вход 22 Код операции оперативной памяти соединен с седьмыми входами блоков хранения страничной таблицы 9, выходы 33-36, 44, 40-43, 37-39 блока местного управления 8 соединены соответственно с управляющими входами регистров 1,2,3/ 5,16,17 блоков хранения страничной таблицы 9, генератора адреса блока хранения 10, блока управления активностью 14, блока коррекции таблищл 15, с выходом 23 Прерывание, с первым управляющим выходом 24 устройства и с вторым управляющим выхОдом 25 устройства, адресный выход 26 устройства соединен с выхрдом регистра физического адреса 2. В блоке преобразования адреса 12 (фиг.2 вход 51 от управляю11его регистра 3 и вход 48 от регистра логического адреса 1 соединены с входами уменьшаемого и вычитаемого вычитателя 45 соответственно, выход знакового разряда вычитателя 45 соединен с вь ходом 53 управляющего регистра 3 выход 52 которого соединен с входами элемента ШШ-НБ 47, выход 55 которого, выход 52 управляющего регистра 3, выход 54 группы элементов Ис46 и выходы 48-50 регистра логического адреса 1 являются выходом блока преобразования адреса 12. В блоке хранения страничной таблицы 9 (фиг.З) входы 52, 54 и входы 48, 49 от блока преобразования, адреса 12 соединены с входами группы элементов памяти 56 и 57 соответственно/ выходы 52,54 и выход 55 блока 12 соединены с входом элемента сравнения 77 и с первым прямым вхой дом элемента И 82 соответственно, второй и третий прямые входы элемента И 82 соединены с выходами групп элементов памяти 60 и -61,- входы 10208 от генератора адреса блока хра.нения 10 соединены с входами групп элементов памяти 58,68 и 69, с первым и вторым входами коммутатора- 79, с адресными входами групп элементов памяти 56-69 и с первым и вторым входами узла управления занесением 7В, выход которого соединен с управляющими входами групп элементов памяти 56-69, адресные входы трупп элементов памяти 56-61 соединены с выходом коммутатора 79, третий и четвертый входы которого соединены с выходами групп элементов -памяти 68 и 69 соответственно, входы 131,129,130 и 128 от блока соррекции таблицы. 15

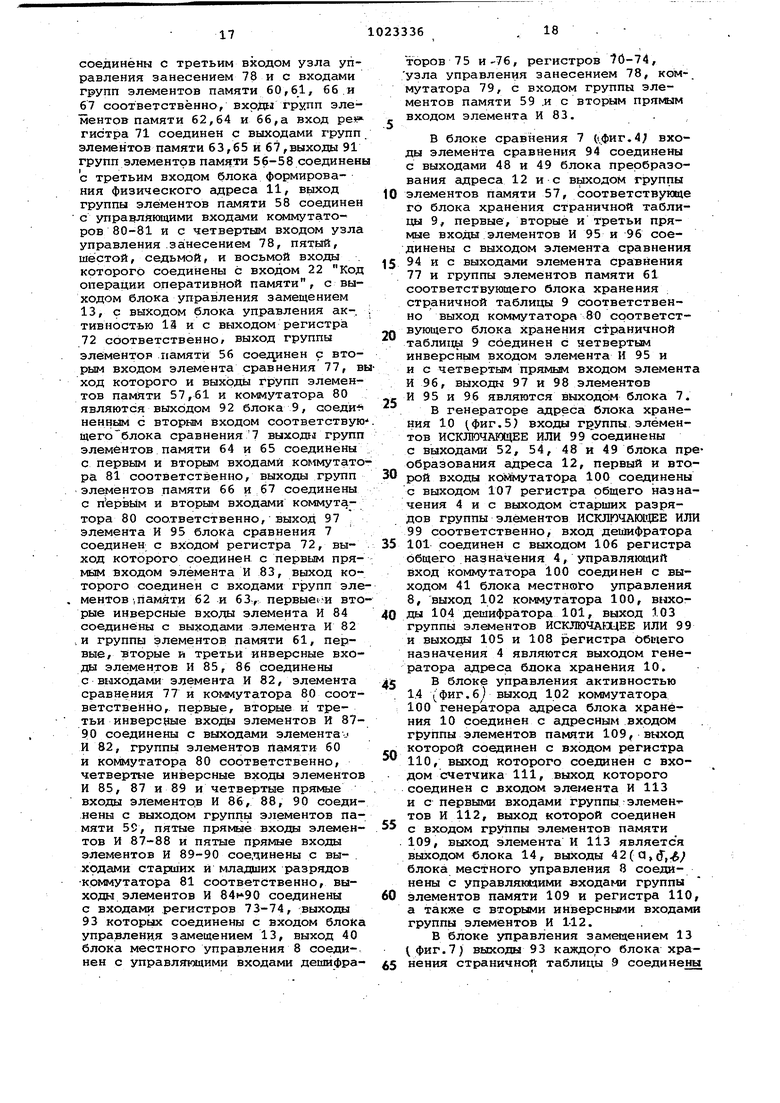

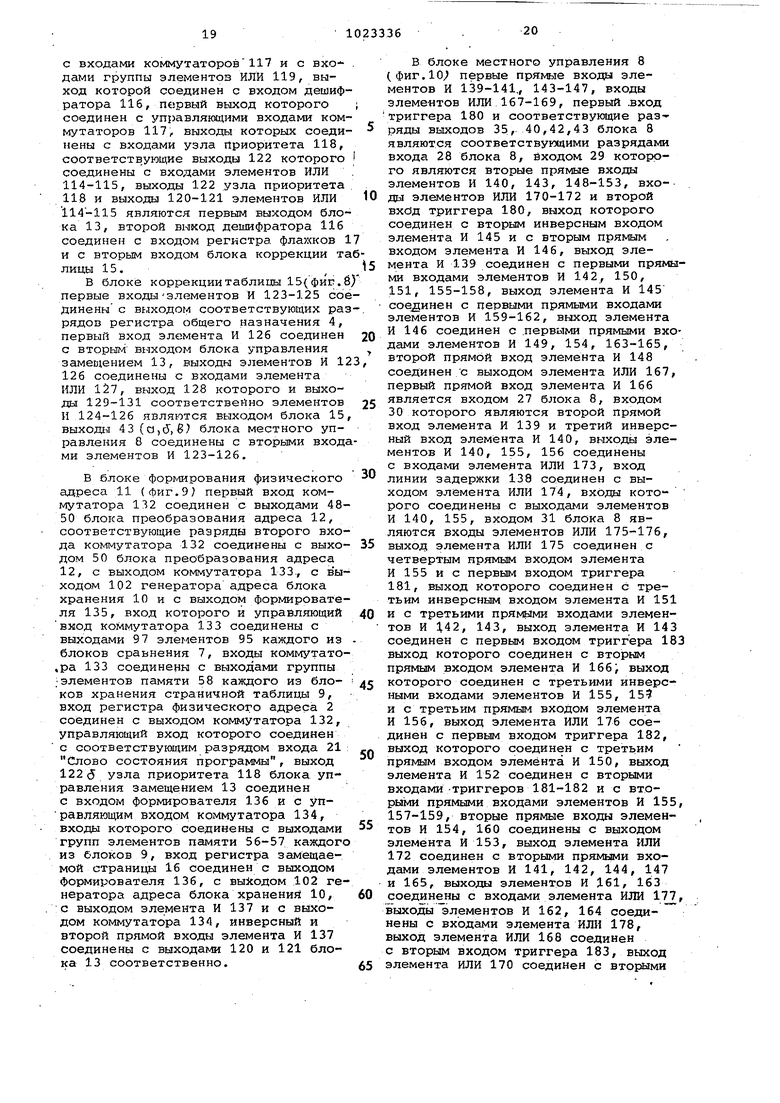

соединены с третьим входом узла управления занесением 78 и с входами групп элементов памяти 60,61, 66.и 67 соответственно, входа групп элементов памяти 62,64 и 66,а вход pes гистра 71 соединен с выходами групп элементов памяти 63,65 и 67 , выходы 91 групп элементов памяти 56-58 соединены с третьим входом блока формирования физического адреса 11, выход группы элементов памяти 58 соединен с управляющими входами ксммутато- ров 80-81 и с четвертым входом узла управления .занесением 78, пятьой, шестой, седьмой, и восьмой входы . которого соединены с входом 22 Код операции оперативной памяти, с выходом блока управления замещением 13, с выходом блока управления ак-. тивностью 13 и с выходом регистра 72 соответственно/ выход группы элементов памяти 56 соеду нен с вторым входом элемента сравнения 77, вход которого и выходы rpiynn элементов памйти 57,61 и коммутатора 80 являются выходом 92 блока 9, соеди- ненным с вторым входом соответствую щегоблока сравнения7 выходы групп элементов памяти 64 и 65 соединены с первым и вторым входами коммутатора 81 соответственно, выходы групп элементов памяти 66 и 67 соединены с nepBbiM и вторым входами коммутатора 80 соо.тветственно, выход 97 элемента И 95 блока сравнения 7 соединен с пходогА регистра 72, выход которого соединен с первым прямым входом элемента И 83, выход которого соединен с входами групп элементов , памяти 62 и 63., первые -и вторые инверсные входы элемента И 84 соединены с выходами элемента И 82 .и группы элементов памяти 61, первые, вторые и третьи инверсные входы элементов И 85, 86 соединены с выходами элемента И 82, элемента сравнения 77 и коммутатора 80 соответственно,, первые, вторые и третьи инверсдаае входы элементов И 8790 соединены с выходами элемента-j И 82, группы элементов 60 и коммутатора 80 соответственно, четвертые инверсные входы элементов И 85, 87 и 89 и четвертые прямые входы элементо.в И 86, 88, 90 соеди.нены с выходом группы элементов памяти 5S, пятые прямые входы элементов И 87-88 и пятые прямые входы элементов И 89-90 соединены с вы- . ходами старших и младших разрядов коммутатора 81 соответственно, выходы элементов И соединены с входами регистров 73-74, выходы 93 которых соединены с входом блока управления замещением 13, выход 40 блока местного управления 8 соединен с управляквдими входами дешифраторов 75 и76, pei iCTpOB 70-74, узла управления занесением 78, коммутатора 79, с входом группы элементов памяти 59 .и с вторым прямым входом элемента И 83.

В блоке сравнения 7 ((фиг. 4; входы элемента сравнения 94 соединены с выходами 48 и 49 блока преобразования адреса 12 и с выходом группы элементов памяти 57, соответствующе го блока хранения страничной таблищл 9, первые, вторые и Третьи прямые входы элементов И 95 и 96 соединены с выходом элемента сравнения 94 и с выходами элемента сравнения 77 и группы элементов памяти 61 соответствующего блока хранения , страничной таблицы 9 соответственно выход коммутатора 80 соответствующего блока хранения страничной табли1 ;ы 9 соединен с четвертым инверсным входом элемента И 95 и и с четвертым прям1 4 входом элемент И 96, выходы 97 и 98 элементов И 95 и 96 являются выходом блока 7.

В генераторе адреса блока хранения 10 фиг.5) входы группы.элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 99 соединены с выходами 52, 54,48 и 49 блока пробразования адреса 12, первый и второй входы ко1 татора 100 соединены с выходом 107 регистра общего назначения 4 и с выходом старших разрядов группы элементов ИСКЛЮЧАЩЕЕ ИЛ

99соответственно, вход дешифратора 101 соединен с выходом 106 регистра общего .назначения 4, управлякадий вход коммутатора 100 соединен с выходом 41 блока местного управления 8, выход 102 коммутатора 100, выходы 104 дешифратора 101, выход 1.03 группы элементов ИСКЛЮЧАЩЕЕ ИЛИ 99 и BbixojiffJ 105 и 108 регистра общего назначения 4 являются выходом генератора адреса блока хранения 10.

В блоке управления активностью 1.4 (фиг.6.) выход 102 коммутатора

100генератора адреса блока хранения 10 соединен с адресным входом г|5уппы элементов памяти 109, выход которой соеддинен с входом регистра 110, выход которого соединен с входом счетчика 111, выход которого соединен с входом элемента И 113

и с первыми входами группы-элемен--тов и 112, выход которой соединен с входом группы элементов памяти 109, выход элемента И 113 является выходом блока 14, выходы 42(a,(J,. блока местного управления 8 соединены с управляющими входами группы элементов памяти 109 и регистра 110 а также с вторыми инверсныг и входам группы элементов И 1-12. .

В блоке управления замещением 13 { фиг.7) выходы 93 каждого блока хранения страничной таблицы 9 соединен

с входами коммутаторов117 и с вхо дами группы элементов ИЛИ 119, выход которой соединен с входом дешифратора 116, первый выход которого соединен с управляющими входами коммутаторов 117, выходы которых соединены с входами узла приоритета 118, соответствующие выходы 122 которого соединены с входами элементов ИЛИ 114-115, выходы 122 узла приоритета 118 и выходы 120-121 элементов ИЛИ 114-115 являются первым выходом блока 13, второй внкод дешифратора 116 соединен с входом регистра флажков 1 и с вторым входом блока коррекции талицы 15.

В блоке коррекции таблицы 15( фиг. 8 первые входыэлементов И 123-125 соединены с выходом соответствующих раз рядов регистра общего назначения 4, первый вход элемента И 126 соединен с вторым выходом блока управления замещением 13, выходы элементов И 12 126 соединены с входами элемента ИЛИ 127, выход 128 которого и выходы 129-131 соответствейно элементов И 124-126 являются выходом блока 15 выходы 43 (о-,6, В) блока местного управления 8 соединены с вторьоми входами элементов И 123-126.

В блоке формирования физического адреса 11 (фиг.9) первый вход коммутатора 132 соед:1инен с выходами 4850 блока преобразования адреса 12, соответствующие разряды второго входа коммутатора 132 соединены с выходом 50 блока преобразования адреса 12, с выходом коммутатора 133., с выходом 102 генератора адреса блока хранения 10 и с выходом формирователя 135, вход которого и управляющий

вход коммутатора 133 соединены с выходами 97 элe 1eнтoв 95 каждого из блоков сравнения 7, входы коммутато,ра 133 соединены с выходами группы

элементов памяти 58 каждого из блоков хранения страничной таблицы 9, вход регистра физического адреса 2 соединен с выходом коммутатора 132, управляющий вход которого соединен с соответствующим разрядом входа 21 : Слово состояния программы, выход 122(5 узла приоритета 118 блока управления замещением 13 соединен с входом формирователя 136 и с управляющим входом коммутатора 134, входы которого соединены с выходами групп элементов памяти 56-57 каждого из блоков 9, вход регистра замещаемой страницы 16 соединен с выходом формирователя 136, с выводом 102 генератора адреса блока хранения 10/

:с выходом элемента И 137 и с BHIXOдом коммутатора 134, инверсный и второй прямой входы элемента И 137 соединены с выходами 120 и 121 блока 13 соответственно.