ff

pesfjoAr

Лмт

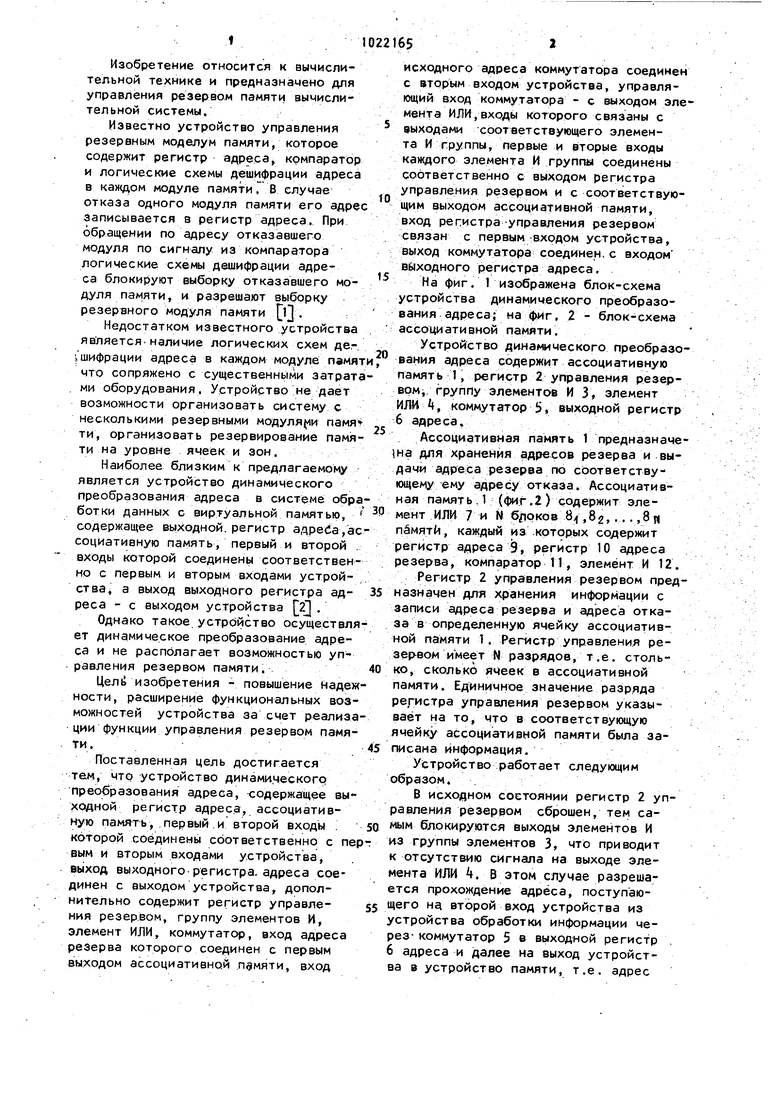

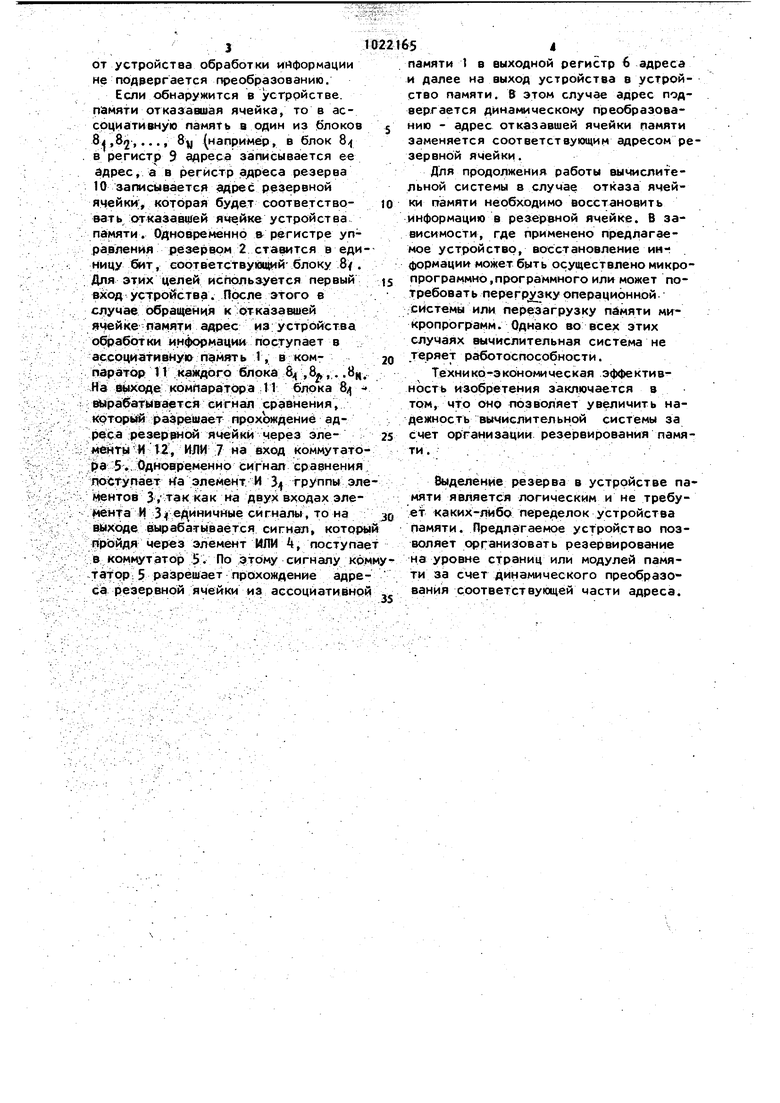

ёГрее ifefoSw Изобретение относится к вычислительной технике и предназначено для управления резервом памяти вычислительной системы. Известно устройство управления резервным моделум памяти, которое содержит регистр адреса, компаратор и логические схемы дешифрации адреса в каждом модуле памяти, В случае отказа одного модуля памяти его адре записывается в регистр адреса. При обращении по адресу отказавшего модуля по сигналу из компаратора логические схемы дешифрации адреса блокируют выборку отказавшего модуля памяти, и разрешают выборку резервного модуля памяти 0 Недостатком известного устройства яв пяетсЯналичие логических схем де,(шифрации адреса в каждом модуле памя что сопряжено с существенными затрат ми оборудования. Устройство не дает возможности организовать систему с несколькими резервными модулями памя ти, организовать резервирование пам;я ти на уровне ячеек и зон. Наиболее близким к предлагаемому является устройство динамического преобразования адреса в системе обр ботки данных с виртуальной памятью, содержащее выходной, регистр аяреба,а социативную память, первый и второй входы которой соединены соответствен но с первым и вторым входами устройства а выход выходного регистра адреса - с выходом устройства , Однако такое устройство осуществл ет динамическое преобразование адреса и не располагает возможностью управления резервом памяти. Цел1 изобретения - повышение Наде ности, расширение функциональных воз можностей устройства за счет реализ ции функции управления резервом памя ти. Поставленная цель достигается тем, что устройство динами.ческогр преобразования адреса, содержащее вы ходной регистр адреса, ассоциативную память,.первый.и второй входы . которой соединены соответственнс с п вым и вторым входами устройства, вь1ход выходного регистра, адреса соединен с выходом устройства, дополниТельно содержит регистр управления резервом, группу элементов И, элемент ИЛИ, коммутатор, вход адреса резерва которого соединен с первым выходом ассоциативной .памяти, вход исходного адреса коммутатора соединен с вторым входом устройства, управляющий вход коммутатора - с выходом элемента ИЛИ,входы которого связаны с выходами соответствующего элемента И группы, первые и вторые входы каждого элемента И группы соединены соответственно с выходом регистра управления резервом и с соответствующим выходом ассоциативной памяти, вход регистра управления резервом связан с первым входом устройства, выход коммутатора соединен,с входом выходного регистра адреса, На фиг. Г изображена блок-схема устройства динамического преобразования адреса; на фиг, 2 - блок-схема ассрциативной памяти, Устройство динамического преобразования адреса содержит ассоциативную память 1, регистр 2 управления резервом, группу элементов И 3, элемент ИЛИ t, коммутатор 5, выходной регистр 6 адреса. Ассоциативная память 1 предназначеа для хранения адресов резерва и выдачи адреса резерва по соответствующему ему адресу отказа. Ассоциативная память,1 (фиг.2) содержит элемент ИЛИ 7 и N б 1оков 8 ,82, ., .,8 и пймятй, каждый из которых содержит регистр адреса 9, регистр 10 адреса резерва, компаратор 11, элемент И 12. Регистр 2 управления резервом предназначен для хранения информации с записи адреса резерва и адреса отказа в определенную ячейку ассоциативной памяти 1. Регистр управления резервом имеет N разрядов, т.е. столько, сколько ячеек в ассоциативной памяти. Единичное значение разряда регистра управления резервом указывает на то, что в соответствующую ячейку ассоциативной памяти была записана информация. Устройство работает следующим образом. В исходном состоянии регистр 2 управления резервом сброшен, тем самым блокируются выходы элементов И из группы элементов 3, что приводит к отсутствию сигнала на выходе элемента ИЛИ 4, В этом случае разрешается прохождение адреса, поступающего нэ второй вход устройства из устройства обработки информации через- коммутатор 5 в выходной регистр . 6 адреса и далее на выход устройства в устройство памяти, т.е. адрес ОТ устройства обработки информации не подвергается преобразованию. Если обнаружится в устройстве, памяти отказавшая ячейка, то в ассоциативную память в один из блоков 84.82,..., (например, в блок 8,( в регистр 9 адреса записывается ее адрес, а в регистр адреса резерва 10 записывается адрес резервной ячейки;, которая будет соответствовать отказавшей ячейке устройства памяти. Однов ременир & регистре управления :рёзе|зврм 2 ставится в еди ницу Опт, соответствующий блоку 8/. Для этих целей используется первый вход устройства. Прсле этого а случае 6бра1цени:я к отказавшей ячейке памяти адрес из;устройства обработки информации поступает в ассрцИчативйу п;эять 1, в компарвтор 11 .«аждбгр блока Д| , 8,,..8ц На выходе компаратора 11 блрка 8 врабатывается сигнал сравнения, крторь й разрешает пррхождениё ад:реса -резерэмой ячейки нерез эле«o fЫ И 12, ИЛИ 7 на вход коммутато . Одновр1€ менно сравнения лоступает rfa элемент И З группы эл i ieHTOB 3i так как на двух входах эле 1ента ИЗ |в иничные сигналы, то на вйхъде вырабатывается сигнал, котор ПрЬйдя через элемент ИЛИ 4, поступа в коммутатор 5. По этому сигналу ко татор- 5 ра;зрёшает прохождение адре са резервной ячейки из ассоциативно 54 памяти 1 в выходной регистр 6 адреса и далее на выход устройства в устройство памяти. В этом случае адрес подвергается динамическому преобразованию - адрес отказавшей ячейки памяти заменяется соответствующим адресом резервной ячейки. Для продо.пжения работы вычислительной системы в случае отказа ячейкм памяти необходимо восстановить Информацию в резервной ячейке. В зависимосТи, где применено предлагаемое у с трои с т вр, восстановление ИНГ формации может быть осуществлено микропрограммно, программного или может потребовать neperpjfSKy операционной. .системы или пере загрузку памяти микропрограмм. Однако во всех этих случаях вычислительная система не теряет работоспособности. Технике-экомомическая эффективность изобретения заключается в том, что оно позволяет увеличить надежность вычислительной системы за счет организации резервирования памяти . Выделение резерва в устррйстве памяти является логическим и не требует каких-либо переделок устройства Памяти. Предлагаемое устройство позволяет организовать резервирование на уровне страниц или модулей памяти за счет динамического преобразования соответствующей части адреса.

f

ф1/г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство динамического преобразования адреса | 1988 |

|

SU1501055A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1163361A1 |

| Устройство для динамического преобразования адреса | 1983 |

|

SU1124300A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Мультиплексный канал с динамическим распределением памяти | 1973 |

|

SU526877A1 |

| Оперативное запоминающее устройство с автономным контролем | 1978 |

|

SU744738A1 |

УСТРОЙСТВО ДИНАМИЧЕСКОГО ПРЕОБРАЗОВАНИЯ АДРЕСА, содержащее выходной регистр адреса, ассоциативную память, первый и второй входы, которой соединены соответственно с первым и вторым входами устройства, а выход выходного регистра адреса соединен с выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и расширевход. ния функциональных возможностей за счет реализации функции управления резервом памяти, в него введены регистр управления резервом, группа элементов И, элемент ИЛИ, .коммутатор, вход адреса резерва которого соединен с первым выходом ассоциативной памяти, вход исходного адреса коммутатора соединен с вторым входом устройства, управляющий вход коммутатора соединен с выходом элемента ИЛИ, входы которого соединены с выходами соответствующего элемента И группы, первые и вторые входы каждог го элемента И группы соединены соответственно с выходом регистра упр,авления резервом и с соответствующим выходом ассоциативной памяти. , вход регистра управления резервом соединен, с первым входом.устройства, выход коммутатора соединен с вхбдом выходного m регистра адреса. О to tsD ОЬ сд

| I | |||

| Патент Франции | |||

| Прибор для определения наклона | 1930 |

|

SU22915A1 |

| G Об F , опублик | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ РАБОЧИМИ ОРГАНАМИ КРУГЛОВЯЗАЛЬНОЙ МАШИНЫ | 0 |

|

SU390216A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| опублик | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1983-06-07—Публикация

1982-03-01—Подача