(5А) ЦИФРОВАЯ ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯЬШ НА ВЫХОДЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1983 |

|

SU1125765A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

| Устройство для преобразования входного двоичного сигнала в телеграфный сигнал | 1984 |

|

SU1233293A1 |

| Преобразователь логических уровней | 1990 |

|

SU1812634A1 |

| НИЗКОВОЛЬТНЫЙ БЫСТРОДЕЙСТВУЮЩИЙ БИПОЛЯРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КОМПЛЕМЕНТАРНЫХ СТРУКТУРАХ | 1999 |

|

RU2173915C2 |

| Транзисторный ключ | 1988 |

|

SU1573535A1 |

| Формирователь импульсов (его варианты) | 1980 |

|

SU974562A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| Интегральная логическая схема | 1977 |

|

SU633395A1 |

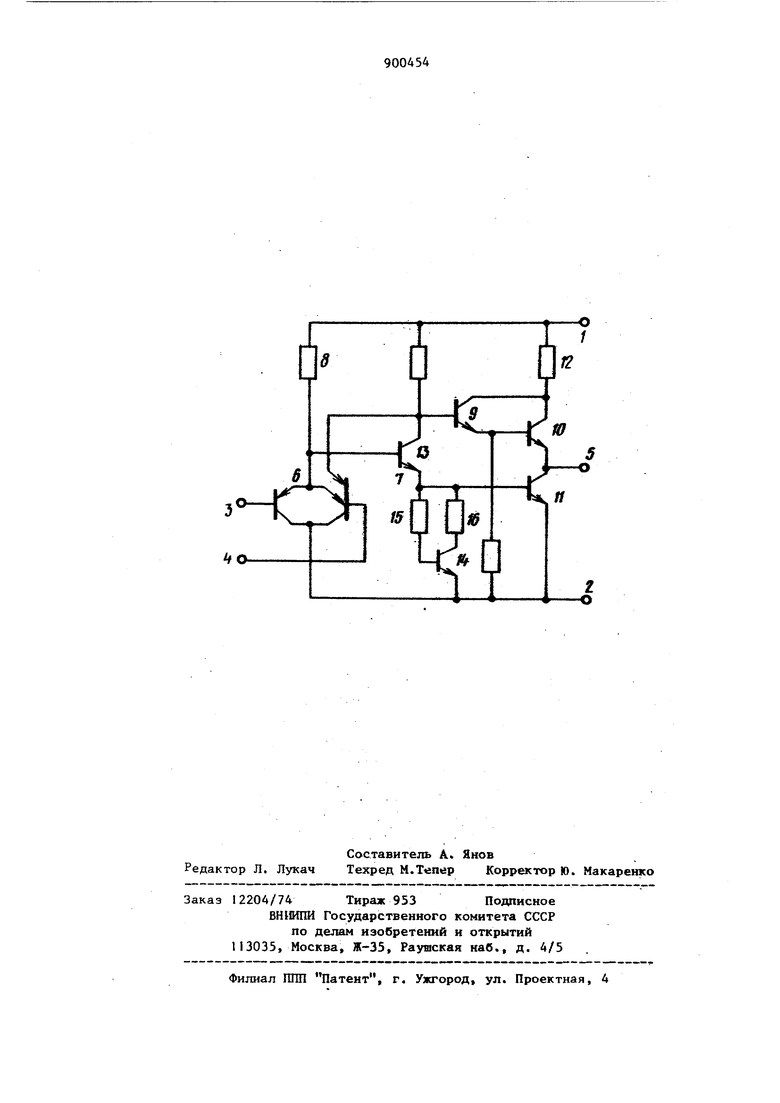

Изобретение относится к электронным логическим устройствам и может найти широкое применение в цифровых системах, особенно в интегральном исполнении. Иэвестш цифровые элементы с тремя состояниями на выходе, содержа vie выходной двухтактный каскад, пр «ежуточный фазоинвертнруювнй каскад и входные управляющие каскады, построен ные на многоймиттерных транзисторах. Перевод элементов в третье состояние производится по коллектора фазоинвертирующего каскада посредством диода, либо жлючевого транзистора, либо специального инвертора tO Недостатком известных устройств является низкое быстродействие вслед ствие использования во входном управляющем каскаде многодатитерного транзистора. Наиболее близким техническим реше йием к изобретению является логический элемент, содержащий двухтактный выходной ипромежуточный фазоинвертирующий каскады, выполненные на транзисторах первого типа проводимости, и входной управляющий каскад, выполненный на транзисторах второго типа проводимости, коллекторы которых подключены к общей шине, эмиттеры ко входу промежуточного фазоинвертируюцего каскада и через резистор к шине питания, а базы - к информациокньм ВХОДФ 2 . Недостатком известного устройства являются узкие функциональные возможности, вследствие невозмодности пepeкJввчeння элемента в третье состояние. Цель изобретения - расширение функциональных возможностей. Для достижения поставленной цели в цифровой полупроводниковой интегральной схеме с тремя состояниями ни выходе, содерж;ащей двухтактный выходной и промежуточный фазоинвертирующий каскады, вьтолненныё на транзисторах первого типа проводимости) и входиой управляющий каскад, вьтолненный на транзисторах второго типа проводимости, коллекторы которых подключены к общей шине,эмиттеры - ко входу промежуточного фазоинвептирующего каскада и через резистор к шике питания, а базы - к информационным входам дополнительный эммитте.р одного из транзисторов входного управляющего каскада подключен к коллектору транзистора промежуточного фазоинвертирующего каскада, а база - к управляющему входу. На чертеже представлена электричес кая схема устройства. Устройство содержит шину 1 питания, общую шину 2, инфо{Мационный вход 3, управляющий вход 4 .выход 5,входной управляющий кас кад на транзисторе 6, двухэмиттерном транзисторе 7 и резисторе 8, выходной двухтактный каскад на транзисторах 9 -Пи резисторе 12, фазоинвертирую1ДИЙ каскад на транзисторах 13 и 14 и резисторах 15 и 16. Цифровая схема с тремя состояниями на выходе работает следующим образом. Если на управляющий вход 4 подать высокий потенциал (Hjj 2,4) ,то тран зистор 7 будет закрыт и схема будет выполнять функцию инвертирующего буфера с информационным входом 3: при подаче на вход 3 высокого напряжения соответствующего логической единице (Hg 2,4в),на выходе возникает низкое напряжение логического нуля . ( 0,3в) и наоборот. Если теперь на управляющий вход 4 подать низкий потенциал, например 0,3в, то на базах транзисторов I3 и 9 будет также низкий потенциал, равный 0,3в + (где 0,8 - напряжение на эмиттерном переходе открытого транзистора 7). В этом случае как транзистор 10, так и траизистор 11 будут закрыты, так как для их открывания необходимо иметь на базах транзисторов 13 и 9 потенциалы, большие или равные 2Hjj . Таким образоМ, выходной импеданс схемы оказывается высоким, т.е. схема отклочается от нагрузки и не реагирует на изменения потенциалов на информационном входе 3. Схема может быть выполнена в составе монолитной БИС по технологии транзисторно-транзисторных схем с диодами Шоттки. В этом случае в качестве транзисторов 13, 14, 9 и II используются транзисторы с коллекторными переходами, зашунтированными диодами Шоттки, а в качестве транзисторов 6 и 7 используются структуры р - п - р типа с общей, р-областью в подложке, так называемые подложечные транзисторы. Предложенная схема обладает улучшенными электрическими характеристиками и занимает малую площадь на кристалле, что способствует снижению стоимости БИС в производстве. Формула изобретения Цифровая полупроводниковая интегральная схема с тремя состояниями йа выходе, содержащая двухтактный выходной и промежуточный фазоинвертирующий каскады, выполненные на транзисторах первого типа проводимости,и входной управляющий каскад, выполненный на транзисторах второго типа проводимости, коллекторы которых подключены к общей шине, эмиттеры - ко входу промежуточного фазоинвертирующего каскада и через резистор к шине питания, а базы - к информационным входам, отли чающая сятем, что, с целью расширения функциональных возможностей, дополнительный эмиттер одного из транзисторов входного управляющего каскада подключен к коллектору транзистора промежуточного фазоинвертирующего каскада, а база к управляющему входу. Источники информации, принятые во внимание при экспертизе 1.Шагурин И.И. Транзисторно-транзисторные логические схемы. М., Сов. радио, 1974, с. 110, рис. 3 и 15 2,Христнансен. Интегральные схемы в действии. - Электроника, т.40, 1967, № 5, с..4, фиг. 2 (прототип).

Авторы

Даты

1982-01-23—Публикация

1980-04-04—Подача