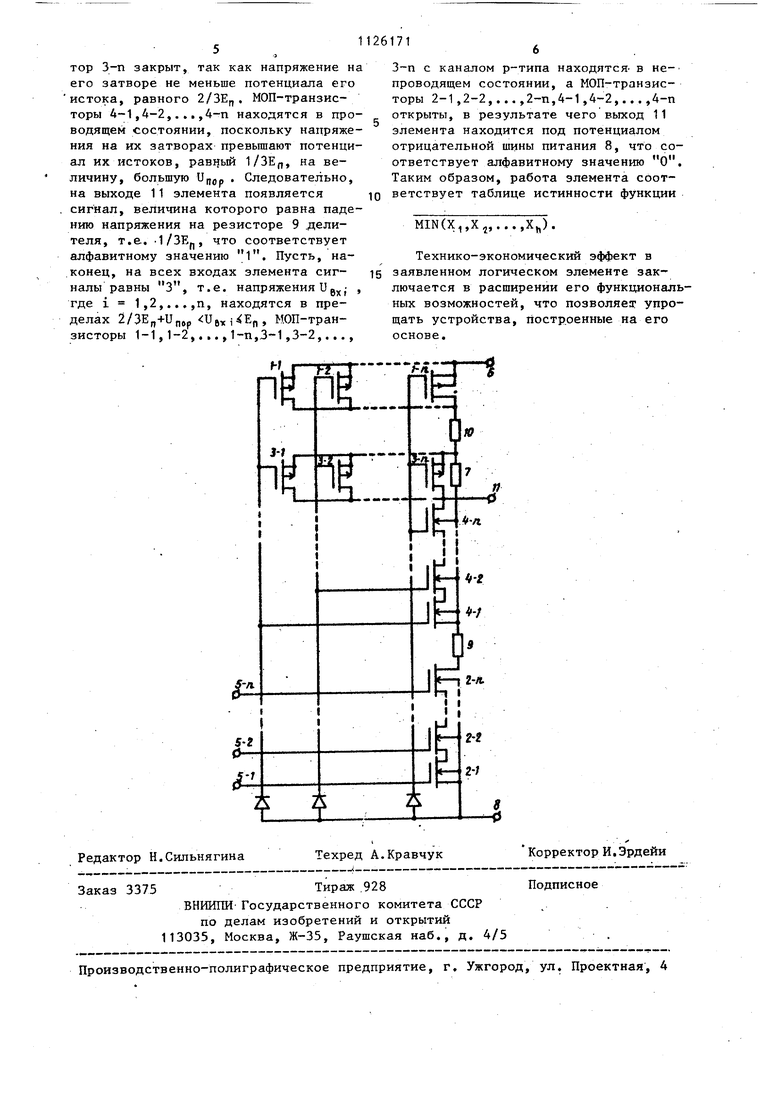

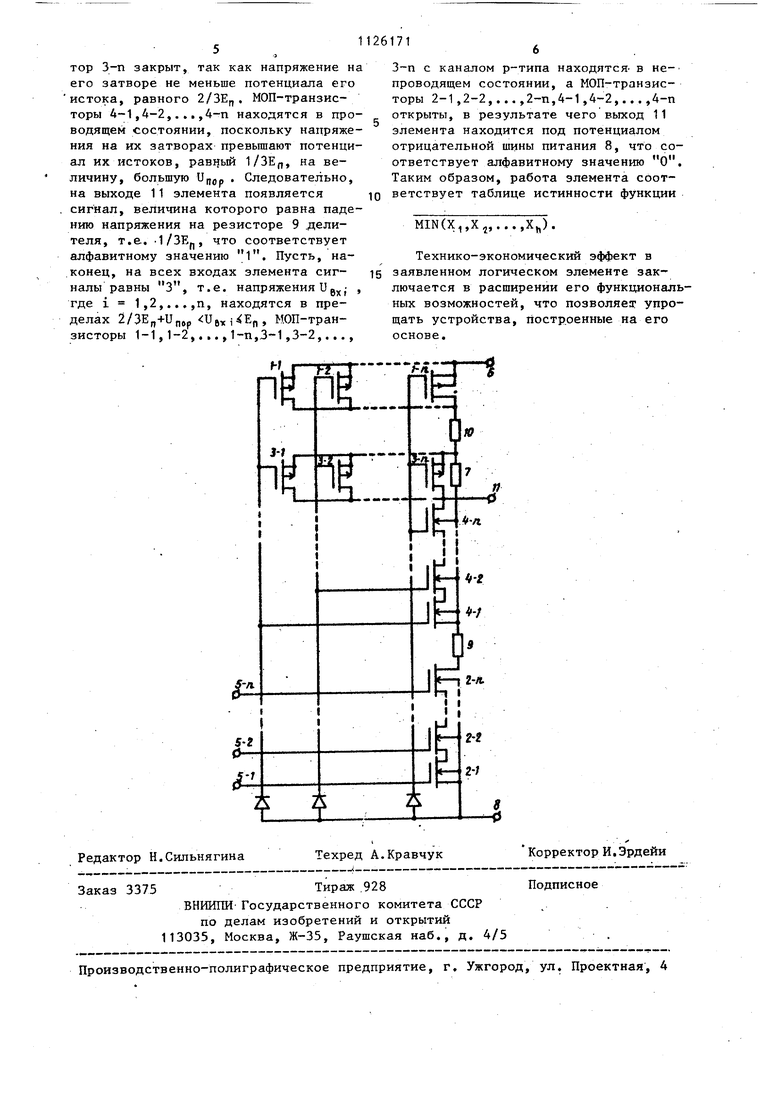

Изобретение относится к импульсно технике, а именно к многозначным эле ментам на МОП-транзисторах, и может быть использовано для построения циф ровых логических устройств. Известны двухвходовые многозначны логические элементы, реализующие функцию MIN (Х, 7) содержащие диоды, пороговые элементы на полевых транзисторах и выходной каскад. Недостаток этих логических элементов заключается в их сложности. Наиболее близким по технической сущности к изобретению является двух |ВХОдовый трехзначный элемент И, реализующий функцию минимум, содержащий .две группы комплементарных пар МОП-транзисторов, затворы i-ой комплементарной пары МОП-транзисторов каждой группы подключены к i-му входу элемента, подложки и истоки МОПтранзисторов с каналом р-типа первой . группы подключены к положительной шине питания, а их стоки объединены, подложки и истоки МОП-транзисторов с каналом р-типа второй группы подключены к шервому вьшоду первого резистора, а их стоки объединены, МОПтранзисторы с каналом п-типа каждой группы включены последовательно, сво бодный исток и подложки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине пита ния, свободный исток и подложки МОПтранзисторов с каналом п-типа первой группы подключены к отрицательной ши не питания, свободньй исток и подлож ки МОП-транзисторов с каналом п-типа второй группы подключены к первому выводу второго резистора, второй вывод которого подключен к отрицательной шине питания, второй вывод, перво го резистора подключен к положительной шине питания. Недостатком известного элемента .являются узкие функциональные возможности, то есть малое количество входов и малая значность элемента. Цель изобретения - расширение функциональных возможностей элемента. Для достижения цели в многовходовый многозначный логический элемент, содержащий две группы комплементарных пар МОП-транзисторов,затворыi-ой комплементарной пары МОП-транзисторов каждой группы подключены к i-му входу элемента, подложки и истоки МОП-транзисторов с каналом р-типа первой группы подключены к положительной гаине питания, а их стоки объединены, подложки и истоки МОПтранзисторов с каналом р-типа второй группы подключены к первому выводу первого резистора, а их стоки объединены, МОП-транзисторы с каналом п-типа каждой группы включены последовательно, свободный исток и подложки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине питания, свободный исток и подложки МОП-транзисторов с каналом п-типа второй группы подключены к первому выводу второго резистора, введен третий резистор, первый и второй выводы которого подключены соответственно к первому выводу первого резистора и к стокам МОП-транзисторов с каналом р-типа первой группы, стоки МОП-транзисторов с каналом р-типа второй группы подключены к свободному стоку МОП-транзистора с каналом п-типа второй группы и выходу элемента, второй вывод первого резистора подключен к первому вьшоду второго резистора, а свободный сток МОП-транзистора с каналом п-типа первой группы подключен к эторому выводу второго резистора. На чертеже представлена принципиальная схема многовходового многозначного логического элемента минимум. Мнрговходовый многозначный логический элемент содержит две группы комплементарных пар МОП-транзисторов 1.1,.,., 1-п,2-1,...,2-п,3-1,...,3-п,4-1,..., 4-п„ Затворы i-ой комплементарной пары МОП-транзисторов 1-i, 2-i, 3-i, 4-i каждой группы подключены к i-му входу 5-i элемента, подложки и истоки МОП-транзисторов 1-1,...,1-п с каналом р-типа первой группы подключены к положительной шине питания 6, а их стоки объединены, подложки и истоки МОП-транзисторов 3-1,,..,3-п с каналом р-типа второй группы подключены к первому вьшоду первого резистора 7, а их йтоки объединены. МОП-транзисторы 2-1,,..,2-п,А-1,..., А-п с каналом п-типа каждой группы включены последовательно, свободный исток и подложки МОП-транзисторов 2-1,...,2-п с каналом п-типа первой группы подключены к отрицательной шине питания 8, свободный исток и подложки МОП-транзисторов 4-1,,.,, 311 4-n e каналом n-типа второй группы подключены к первому выводу второго резистора 9. Первый и второй выводы третьего резистора 10 подключены соответственно к первому выводу первого резистора 7 и к стокам МОП-транзисторов 1-1,...,1-п с каналом р-типа пер вой группы, стоки МОП-транзисторов 3-1,,..,3-п с каналом.р-типа второй группы подключены.к свободному стоку МОП-транзистора 4-п с каналом п-типа второй группы и выходу 11 элемента, вторгой вывод первого резистора 7 под ключен к первому выводу второго резистора 9, а свободный сток МОП-тран зистора 2-п с каналом п-типа первой группы подключен к второму выводу второго резистора 9. Многовходовый многозначный логический элемент минимумj работает сле дующим образом. На входы 5-1,...,5-п элемента поступают сигналы в виде на пряжения постоянного тока в диапазон от нуля вольт до напряжения истЪчника питания Ej,, что в логическом смыс ле, соответствует алфавиту Е 10,Ь2,ЗЬ Пусть величины входных сигналов п-входового четырехзначного логического элемента удовлетворяют следующим условиям: 1) , что соответству логическому нулю, 2)Unop Ugxj Е„, где J, it 1,2,...,п,,, а и пор напряжение порога МОП-транзисторов. Примем для определенности i 2, т.е сигнал, соответствующий первому из указанных условий, приложен к второму входу 5-2 элемента. В этом случае МОП-транзисторы -9-2 и 4-2 с кана лом п-типа закрыты, поскольку напряжение на их затворах не превьшает , и„др , а МОП-транзисторы 1-2 и с каналом р-типа открыты, так как напряжение на их затворах по отношению к потенциалу истоков меньше на величину, превьшающую (уеловне I). В результате на выходе 11 элемента напряжение равно Е, что соответствует логическому сигналу 3, Вышеописанная ситуация сохраняется также и в тех случаях, когда первому условию удовлетворяют величины сигналов на любом числе входов включая п. Это связано с тем, что замкнутому ключу соответствуют МОПтранзисторы 1-1,...,Д-п с такими состояниями при которых проводят любое число от 1 до п параллельно в1слюченные МОП-транзисторы 1-1,...,1-п, 3-1,...,3-п или все п последовательно включенные МОП-транзисторы 2-1, о..,2-п,4-1,...,4-п и наоборот, разомкнутому ключу соответствуют либо все п параллельно включенных,либо один из п последовательно включенных МОП-транзисторов 1-1,...,4-п, находящихся в непроводящем состоянии. В силу вьпцесказанного входовой четырехзначный логический элемент при нескольких различных комбинациях входных сигналов может быть представлен одной и той же эквивалентной схемой, где соответствие исчерпьшается четырьмя эквивалентными схемами для 4 комбинаций входных сигналов. Если в наборе входных сигналов нет сигнала меньше 1 и хотя бы один сигнал из набора равен 1, т.е. если Unop Uexk l/ ЕП + и„вр ; . 1/3En+UnopiUB.En,i,j €tlj2,3,...,n), i j, то МОП-транзисторы 1-1 и 3-1 вследствие того, что напряжение на их затворах по отношению к потенциалам их истоков меньше на величину, большую и 1,9 , открыты. Открыты также МОПтранзисторы 2-1,2т2,..,,2-п поскольку напряжение на их затворах . вьшге Unop , а МОП-транзистор 4-1 закрыт, ибо напряжение на его затворе не превьш1ает потенциала истоков, определяемого падением напряжения на резисторе 9 делителя, образованного резисторами 7, 9, 10, номиналы которых равны, на величину Unop В результате падение напряжения на резисторах 9, 7 делителя, равное 2/ЗЕп (что соответствует логическому значению 2), приложено к выходу 11 логического элемента. Допустим теперь что в наборе входных сигналов нет сигнала меньше 2 и хотя бы один из сигналов равен 2, т.е. на величины входных сигналов накладываются следующие ограничения:1/ЗЕ„+ и„,р ивх; 2/ЗЕ„+ и„р ; Ug., 2/ЗЕ„+и„,, ,i,J6.J1,2,...,ni,, МОП-транзисторы 1-п (щ) ), 2-1,2-2,...,2-п открыты, МОП-транзисг

тор 3-n закрыт, так как напряжение на его затворе не меньше потенциала его истока, равного 2/ЗЕр. МОП-транзисторы 4-1,4-2,...,4-п находятся в проводящем состоянии, поскольку напряжения на их затворах превьшают потенциал их истоков, равный 1/3Ef,, на величину, большую . Следовательно, на выходе 11 элемента появляется сигнал, величина которого равна падению напряжения на резисторе 9 .делителя, т.е. .1/3Ej, что соответствует алфавитному значению 1. Пусть, наконец, на всех входах элемента сигналы равны 3, т.е. напряжения , где i 1,2,...,п, находятся в пределах 2/ЗЕ„+ип,р :UB, , МОП-транзисторы 1-1,1-2,...,1-п,3-1,3-2,...,

с каналом р-типа находятся, в непроводящем состоянии, а МОП-транзисторы 2-1,2-2,...,2-п,4-1,4-2,...,4-п открыты, в результате чего выход 11 элемента находится под потенциалом отрицательной шины питания 8, что соответствует алфавитному значению О. Таким образом, работа элемента соответствует таблице истинности функции

MIN(X,,X,,...,X).

Технико-экономический эффект в заявленном логическом элементе заключается в расширении его функциональных возможностей, что позволяет упрощать устройства, построенные на его основе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовый многозначный логический элемент максимум | 1983 |

|

SU1126172A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| Коммутатор аналоговых сигналов | 1976 |

|

SU544132A2 |

| Интегральная схема | 1989 |

|

SU1755338A1 |

| Кварцевый генератор | 1983 |

|

SU1109855A1 |

| Ключ | 1977 |

|

SU621094A2 |

| Ключ | 1975 |

|

SU531278A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

МНОГОВХОДОВЫЙ МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ МИНИМУМ, содержащий две группы комплементарных пар МОП-транзисторов, затворы i-ой комплементарной пары МОП-транзисторов каждой группы подключены к i-му входу элемента, подложки и истоки МОП-транзисторов с каналом р-типа первой ; группы подключены к положительной шине питания, а их стоки объединены, подложки и истоки МОП-транзисторов с каналом р-типа второй группы подключены к первому выводу первого резис: тора, а их стоки объединены, МОПI транзисторы с каналом п-типа каждой группы включены последовательно, свободньй исток и подлозкки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине питания, свободный исток и подложки МОПтранзисторов с каналом п-типа второй группы подключены к первому выводу второго резистора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введен третий резистор, первый и второй выводы которого подключены соответственно к первому выводу пер(Л вого резистора и к стокам МОП-транзисторов с каналом р-типа первой группы, стоки МОП-транзисторов с каналом р-типа второй группы подключены к свободному стоку МОП-транзистора с каналом п-типа второй группы и выходу элемента, второй вывод первого .резистора подключен к первому выводу втоtsD рого резистора, а свободный сток МОПО) транзистора с кайалом п-типа первой группы подключен к второму выводу второго резистора.

| Tront I.G., Givone D.D.Multiplevalued Logic Cater usinp, MEgFST s Proceedings of the 9-th International SimEOsium of Multiple-valued Logic, Bath 1979, №4, p | |||

| Ручной прибор для загибания кромок листового металла | 1921 |

|

SU175A1 |

| Huertal I.L | |||

| Carmone I.M | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Способ прикрепления барашков к рогулькам мокрых ватеров | 1922 |

|

SU174A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1988-04-23—Публикация

1983-01-12—Подача