Изобретение относится к области вычислительной техники и микроэлектроники и может быть использовано для построения многозначных устройств на МОП-транзисторах.

Известны многозначные инверторы на КМОП-транзисторах, содержащие базовые декодеры, двузначные инверторы и кодер соответствующей значности, например трехзначный инвертор, состоящий из двух базовых декодеров, двух двузначных инверторов и трехзначного кодера.

Недостатком известных устройств является их сложность.

Известен также трехзначный инвертор, содержащий два резистора и два .КМОП-транзистора, -затворы которых подключены к входу устройства, истоки и подложки - к соответствующим шинам питания,, а стоки соответственно подключены у МОП-транзистора с каналом р-типа к первому выводу первого резистора и у МОП-транзистора с каналом п-типа к первому выводу второго резистора, а вторые выводы резисторов подключены к выходу устройства.

Недйстатком этого инвертора являются узкие функциональные возможноети, обусловленные его низкой значностью, ограничивающей эффект от его применения.

Целью, изобретения является расширение функциональных возможностей устройства.

Указанная цель достигается тем, что в т-значный инвертор на КМОП-транзисторах, содержащий два резистора и два КМОП-транзистора, затворы которых подключены к входу устройства, истоки и подложки - к соответствующим шинам питания, а стоки подключены соответственно у КМОП-транзистора с каналом р-типа к первому выводу первого резистора и у КМОП-транзистора с каналом п-типа к первому выводу второго резистора, введены два дополнительных КМОП-транзистора, затворы которых подключены к входу устройства, и третий резистор, первый вывод которого подключен к второму вьшоду первого резистора, к истоку и подложке дополнительного КМОПтранзистора с каналом р-типа, а второй вывод подключен к второму выводу второго резистора, истоку и подложке дополнительного КМОП-транзистора с каналом п-типа,. стоки дополнительных КМОП-транзисторов подключены к выходу устройства.

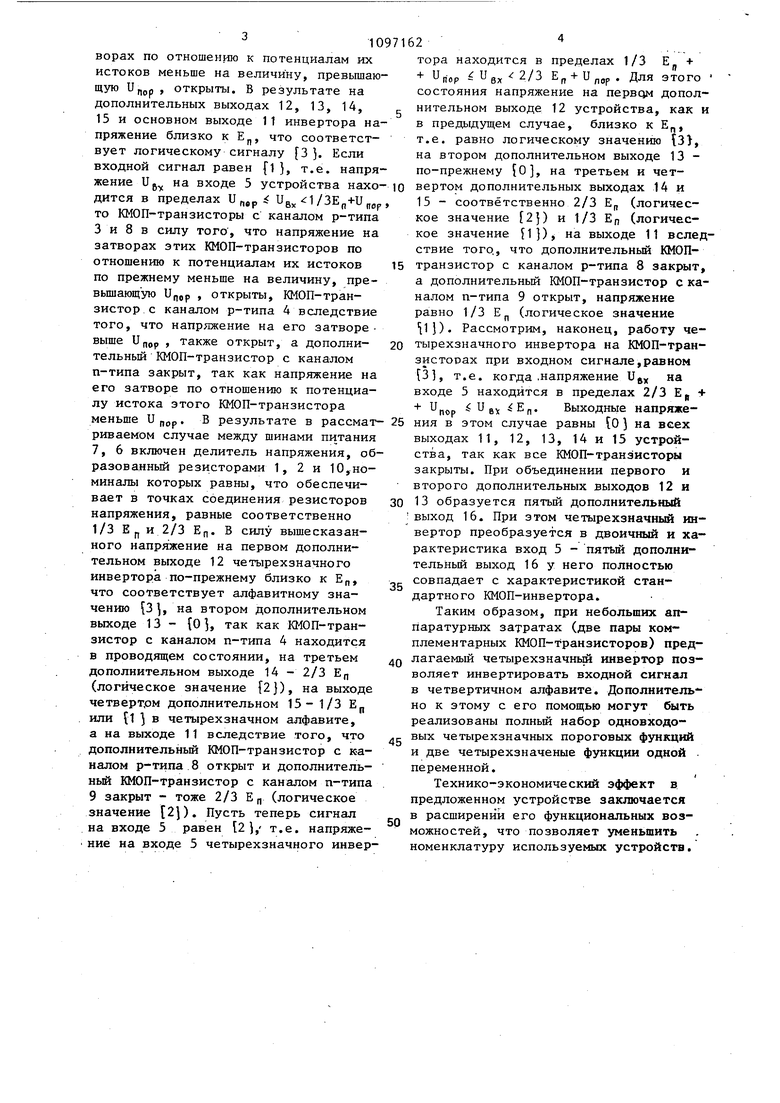

На чертеже приведена принципиальная схема предложенного т-значного инвертора на КМОП-транзисторах.

т-значньш инвертор на КМОП-транзисторах содержит два резистора 1,2 и два КМОП-транзистора 3, 4, затворы которых подключены к входу 5 устройства, истоки и подложки - к соответствующим шинам 6, 7 питания, а стоки соответственно подключены у КМОП-транзистора 3 с каналом р-типа к первому выводу первого резистора 1 и у КМОПтранзистора 4 с каналом п-типа к первому выводу второго резистора 2, два дополнительных КМОП-транзистора 8,9j затворы которых подключены к входу 5 устройства, и третий резистор 10, первый вывод которого подключен к второму выводу первого резистора 1, истоку и подложке дополнительного КМОП-транзистора 8 с каналом р-типа, а второй вывод - к второму выводу второго резистора 2, истоку и подложке дополнительного КМОП-транзистора 9 с каналом п-типа, стоки дополнительных КМОП-транзисторов 8, 9 подключены к выходу 11 устройства, стоки КМОП-транзисторов 3, 4 подключены соответственно к первому и второму дополнительным выходам 12, 13, а истоки дополнительных КМОП-транзисторов 8,9 - соответственно к третьему и четвертому дополнительным выходам 14, 15, пятый дополнительньш выход 16 может быть получен путем объединения первого и второго дополнительных выходов 12, 13.

т-значный инвертор на КМОП-транзисторах работает следующим образом. На вход 5 устройства поступают сигналы в виде напряжения постоянного тока в диапазоне от О вольт до напряжения источника питания Е, что в логическом плане соответствует алфавиту Е 0,1,2,3). Предположим,что входной сигнал четырехзначного инвертора на КМОП-транзисторах равен О, т.е. напряжение Uj на входе 5 находится в пределах О U вх U пор где и J, - напряжение порога КМОП-транзисторов, В этом случае КМОП-транзисторы. с каналами п-типа 4 и 9 закрыты, поскольку напряжение на их затворах не превьш1ает U пор а КМОПтранзисторы с каналами р-типа 3 и 8 в силу того, что напряжение на ворах по отношению к потенциалам их истоков меньше на величину, превышаю щую и„др , открыты. В результате на дополнительных выходах 12, 13, 14, 15 и основном выходе 11 инвертора на пряжение близко к Ер, что соответствует логическому сигналу 3). Если входной сигнал равен fl ), т.е. напря жение Ug на входе 5 устройства нахо дится в пределах то КМОП-транзисторы с каналом р-типа 3 и 8 в силу того, что напряжение на затворах этих КМОП-транзисторов по отношению к потенциалам их истоков по прежнему меньше на величину, превьш1ающую и„др , открыты, КМОП-транзистор с каналом р-типа 4 вследствие того, что напряжение на его затворевыше и пор , также открыт, а дополнительньй КМОП-транзистор с каналом п-типа закрыт, так как напряжение на его затворе по отношению к потенциалу истока этого КМОП-транзистора меньше U В результате в рассмат риваемом случае между шинами питания 7, 6 включен делитель напряжения, об разованный резисторами 1, 2 и 10,номиналы которых равны, что обеспечивает в точках соединения резисторов напряжения, равные соответственно 1/3 Е, и 2/3 ЕП. В силу вышесказанного напряжение на первом дополнительном выходе 12 четырехзначного инвертора по-прежнему близко к Е, что соответствует алфавитному значению 3, на втором дополнительном выходе 13 - {0, так как КМОП-транзистор с каналом п-типа 4 находится в проводящем состоянии, на третьем дополнительном выходе 14 - 2/3 Е (логическое значение 2), на выходе четвертрм дополнительном 15- 1/3 „ или 1 в четырехзначном алфавите, а на выходе 11 вследствие того, что дополнительный КМОП-транзистор с каналом р-типа 8 открыт и дополнительньй КМОП-транзистор с каналом п-типа 9 закрыт - тоже 2/3 Е (логическое значение 2J). Пусть теперь сигнал на входе 5 равен 2),- т.е. напряжение на входе 5 четырехзначного инвер „д 2 тора находится в пределах 1/3 Е и,, 2/3 Е.+ Улар Для этого состояния напряжение на первом дополнительном выходе 12 устройства, как и в предьщущем случае, близко к Е„, т.е. равно логическому значению {З}, на втором дополнительном выходе 13 по-прежнему 0, на третьем и четвертом дополнительных выходах 14 и 15 - соответственно 2/3 Е„ (логическое значение 2) и 1/3 Ер (логическое значение {1) на выходе 11 вследствие того,, что дополнительный КМОПтранзистор с каналом р-типа 8 закрыт, а дополнительный КМОП-транзистор с каналом п-типа 9 открыт, напряжение равно 1/3 Е (логическое значение ilj). Рассмотрим, наконец, работу четырехзначного инвертора на КМОП-транзисторах при входном сигнале,равном 31, т.е. когда .напряжение U на входе 3 находится в пределах 2/3 Е, + + Uj,jj и вк Ef,. Выходные напряжения в этом случае равны О на всех выходах 11, 12, 13, 14 и 15 устройства, так как все КМОП-транэисторы закрыты. При объединении первого и второго дополнительных выходов 12 и 13 образуется пятый дополнительный выход 16. При этом четырехзначный инвертор преобразуется в двоичный и характеристика вход 5 - пятый дополнительный выход 16 у него полностью совпадает с характеристикой стандартного КМОП-инвертора. Таким образом, при небольших аппаратурных затратах (две пары комплементарных КМОП-транзисторов) предлагаемый четырехзначньм инвертор позволяет инвертировать входной сигнал в четвертичном алфавите. Дополнительно к этому с его помощью могут быть реализованы полный набор одновходовых четырехзначных пороговых функций и две четырехзначеные функции одной переменной. Технико-экономический эффект в предложенном устройстве заключается в расширении его функциональных возможностей, что позволяет уменьшить номенклатуру используемых устройств.

1

h.

-i

иг

-0;v

75

п )t

/ /

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовый многозначный логический элемент минимум | 1983 |

|

SU1126171A1 |

| Многовходовый многозначный логический элемент максимум | 1983 |

|

SU1126172A1 |

| Циклический инвертор на КМОП-транзисторах | 1985 |

|

SU1352642A1 |

| Циклический инвертор @ ( @ ) на КМОП-транзисторах | 1985 |

|

SU1287280A1 |

| М-ЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1994 |

|

RU2079970C1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| Контролируемый логический элемент | 1987 |

|

SU1429312A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| Трехзначный универсальный элемент | 1987 |

|

SU1499482A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

т-ЗНАЧНЫЙ ИНВЕРТОР, содержащий два резистора и два КМОП-транзистора, затворы которых подключены к входу инвертора истоки и подложки к соответствующим шинам питания, а стоки соответственно подключены у КМОП-транзистора с каналом р-типа к первому выводу первого резистора и у КМОП-транзистора с каналом п-типа к первому вьтоду второго резистора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены два до. полнительных КМОП-транзистора, затворы которых подключены к входу инвертора, и третий резистор, первый вывод которого подключен к второму вьгооду первого резистора, к истоку S и подложке дополнительного КМОПтранзистора с каналом р-типа, а вто рой вывод - к второму вьшоду второго резистора, истоку и подложке дополнительного КМОП-транзистора с каналом п-типа, стоки дополнительных КМОП-транзисторов подключены к выходу инвертора. О) с

| Huetras I.L., Carmona I.M | |||

| Lowpower ternary C-MOS circuits | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для передачи фотографических изображений на расстояние | 1920 |

|

SU170A1 |

| Makoto Hatta, Itsuo Takanami and Katsushi Inoue | |||

| A realization of ternary logic functions by using cellular arrays | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1988-04-23—Публикация

1982-12-20—Подача