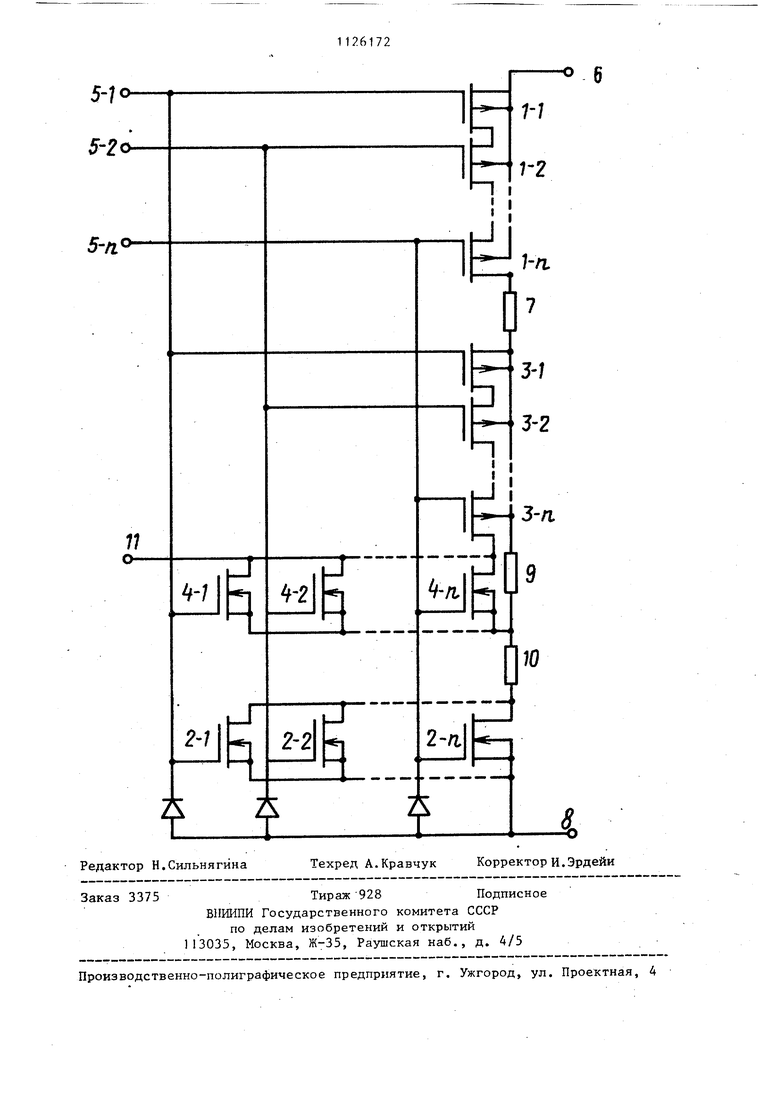

Изобретение относится к импульсной технике, а именно к многозначным элементам на МОП-транзисторах, и может быть использовано для построения цифровых логических устройств. Известны двухвходовые многозначные логические элементы, содержащие переключатели тока на полевых транзисторах и выходной каскад Недостатком известных устройств является их. сложность, Наиболее близким по технической сущности к изобретению является двух входовой трехзначный элемент ИЛИ, реализующий функцию максимум, содер.жащий. две группы комплементарных пар -МОП-транзисторов5 затворы i-ой комплементарной пары МОП-транзисторо каждой группы подключены к i-му входу элемента, МОП-транзисторы с каналом р-типа каждой группы включены последовательно, подложки и свободны исток МОП-транзисторов с каналом р-типа первой группы подключены к положительной шине питания, свободный исток и подложки МОП-транзисторов с йаналом р-типа подключены к первому выводу первого резистора, второй вьюод которого подключен к по ложительной шине питания, истоки и подложки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине питания, а их сто ки объединены, подложки и истоки МОП-транзисторов с каналом п-типа второй группы подключены к первому вьшоду второго резистора, второй вывод которого подключен к положительной шине питания, свободные стоки МОП-тракзисторов с каналом р-типа первой и второй групп подключены соответственно к стокам МОП-транзисторов с каналом п-типа второй и первой групп. Недостатком известного элемента являются узкие функциональные возможности, то есть малое количество входов и малая значность элемента. Цель изобретения - расширение функциональных возможностей элемент Для достижения поставленной цели в элемент, содержащий две группы комплементарных пар МОП-транзисторов затворы i-ой комплементарной пары транзисторов каждой группы подключе ны к 1-му входу элемента, МОП-транзисторы с каналом р-типа каждой гру пы включены последовательно, подлож ки и свободный исток МОП-транзисторов с каналом р-типа первой группы подключены к положительной шине питания, свободный исток и подложки МОПтранзисторов с каналом р-типа второй группы подключены к первому выводу первого резистора, истоки и подложки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине питания, а их стоки объединены, подложки и истоки МОП-транзисторов с каналом п-типа второй группы подключены к первому вьтоду второго резистора, а их стоки объединены, введен третий резистор, включенный между стоками МОП-транзисторов с каналом п-типа первой группы и первым выводом второго резистора, второй вьшод которого подключен к первому выводу первого резистора, а стоки МОП-транзисторов с каналом п-типа второй группы подключены к выходу элемента и свободному стоку МОП-транзистора с каналом р-типа второй группы, а свободньт сток МОП-транзистора с каналом р-типа первой группы подключен к второму выводу первого резистора. На чертеже представлена принципиальная схема многовходового многозначного логического элемента максимум. Элемент содержит две группы комплементарных пар МОП-транзисторов 1-11 п, 2-1,,.,,2-п, 3-1,...,3-п 441,...,4-п. Затворы i-ой комплементарной пары МОП-транзисторов 1-i, 2-i, 3-i, 4-i подключены к i-му входу 5-i элемента, МОП-транзисторы 1-1,...,1-п, 3-1,...,3-п с каналом р-типа каждой группы включены после- . довательно, подложки и свободный исток МОП-транзисторов И-1,...,1-п первой группы подключены к положительной шине питания 6, свободный исток и подложки МОП-транзисторов 3-15...,3-п с каналом р-типа второй группы подключены к первому выводу первого резистора 7. Истоки и подложки МОП-транзисторов 2-1,...,2-п с каналом п-типа первой группы подключены к отрицательной шине питания 8, а их стоки объединены, подложки и истоки МОП-транзисторов 4-1,...,4-п с каналом п-типа второй группы подключены к первому вьшоду второго резистора 9. Третий резистор 10 включен между стоками МОП-транзисторов 4-1,...,4-n с каналом n-типа первой группы с первьм выводом второго резистора 9, второй вывод которого под ключен к первому выводу первого резистора 7, а стоки транзисторов 4-1,.,.,4-п с каналом п-типа второй группы подключены к выходу 11 элемента и свободному стоку МОП-транзистора 3-п с каналом р-типа второй группы, а свободный сток МОП-транзисто 1-п с каналом р-типа первой группы подключен к второму выводу первого резистора 7. Многовходовый многозначный логический элемент максимум работает сле дующим образом. На входы 5-1,...,5-п элемента поступают сигналы в виде напряжения постоянного тока в диапазоне от нуля вольт до напряжения источника питания Е„, что в логическом смысле соответствует алфавиту ЕП 0,1,2,3). Пусть величины входных сигналов п-входового четырехзначного логического элемента равны 0 т.е. напряжения Ug, где 1 1,2,....,п, находятся в пределах , где и пор .- пороговое напряжение МОПтранзисторов. В этом случае все МОП-транзисторы 2-1,...,2-п,4-1,..., 4-п с каналом п-типа закрыты, пос кольку напряжение на их затворах не превьшаег Unop а все МОП-транзисторы 1-1...,1-п,3-1,...,3-п с каналом р-типа открыты,так как напряжение на и : затворах по отношению к потенциалу истоков меньше на величину, превьппающую и пер В результате на выходе 11 элемента напряжение равно Ej,, что соответствует логическому сигналу З. Если в наборе, входных сигналов хотя бы один равен 1, а все остальные меньше 1, т.е. если U пер Uexv 1/3En + Unop , а Uexi :Unop , . где i,j е t1,2,...,nj, j , то все МОП-транзисторы 1-1,...,1-n,3-1,..., 3-n с каналом р-типа вследствие того, что напряжение на затворах указанных МОП-транзисторов по отношению к потенциалам их истоков по прежнему меньше на величину, большую открыты. Открыт также МОП-тран зистор 2-1, поскольку, напряжение на его-затворе вьш1е, а МОП-транзис торы 4-1,,..,4-п закрыты, ибо напряжение на их затворах не превьшает на величину и„ор потенциала rfcTOKOB, определяемого падением напряжения на резисторе 10 делителя, образованного резисторами 7, 9, 10, номиналы которых равны. В результате падение напряжения на резисторах 10 и 9 делителя, равное./З Е (что соответствует логическому значению 2) приложено к выходу 11 логического элемента. Допустим теперь, что в наборе входных сигналов хотя бы один равен, 2, а остальные меньше 2, т.е. 1/3Ef, + Unop Ujxi 2/3Efl пор , , Uexi 1/3En и„ор , и пор i,j «ll,2,...nj. г j. МОП-транзисторы 1-1,.,.,1-п открыты, открыт по крайней мере один МОП-транзистор 2-1, МОП-транзистор меняет свое состояние по сравнению с предьщущим случаем на противоположное, т,е, станет непроводящим, так как напряжение на его затворе не меньше на величину Unop потенциала-кстока, равного 2/ЗЕп. МОП-транзистор 4-п находится в проводящем состоянии, поскольку напряжение на его затворе превьшгает потенциал истока, равный 1/ЗЕп, на величину, большую и лор , Следовательно, на выходе 11 элемента появляется сигнал, величина которого равна падению напряжения на резисторе 10 делителя, т.е. 1/ЗЕп, что соответст1вует алфавитному значению 1, Пусть наконец, хотя бы на одном входе элемента сигнал равен 3, т,е, напряжение где i е 1,2,... nl, находится 8 пределах 2/ЗЕп + Unop 4U , В этом выход 11 элемента находится под потенциалом отрицательного полюса 8 источника питания, что соответствует алфавитному значению О, Следовательно, работа элемента, как вытекает из вьш1енаписанного, соответствует таблице истинности функции lAX(x |,х Технико-экономический эффект в предложенном элементе заключается в расширении его функциональных врзможностей, что позволяет упростить устройства, построенные на его основе,

| название | год | авторы | номер документа |

|---|---|---|---|

| Многовходовый многозначный логический элемент минимум | 1983 |

|

SU1126171A1 |

| @ -Значный инвертор | 1982 |

|

SU1097162A1 |

| Циклический инвертор @ ( @ ) на КМОП-транзисторах | 1985 |

|

SU1287280A1 |

| Циклический инвертор на КМОП-транзисторах | 1985 |

|

SU1352642A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Интегральная схема | 1989 |

|

SU1755338A1 |

| Пьезополупроводниковый стабилизатор постоянного напряжения | 1980 |

|

SU926636A1 |

| Многоканальный коммутатор | 1989 |

|

SU1644373A1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ РАЗРЯДОВ СТАТИЧЕСКОГО ЭЛЕКТРИЧЕСТВА ВЫВОДОВ ПИТАНИЯ КОМПЛЕМЕНТАРНЫХ МОП (МЕТАЛЛ-ОКИСЕЛ-ПОЛУПРОВОДНИК) ИНТЕГРАЛЬНЫХ СХЕМ НА КРЕМНИЕВЫХ ПЛАСТИНАХ С ПРОВОДИМОСТЬЮ N-ТИПА | 2013 |

|

RU2585882C2 |

МНОГОВХОДОВЬЙ МНОГОЗНАЧНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ МАКСИМУМ, содержащий две группы комплементарных Пар МОП-транзисторов, затворы i-той комплементарной пары МОП-транзисторов каждой группы подключены к i-му входу элемента, МОП-транзисторы с каналом р-типа каждой группы включены последовательно, подложки и свободный исток мод-транзисторов с каналом р-типа первой группы подключены к положительной шине питания, свободный исток и подложки МОП-транзисторов с каналом р-типа второй группы подключены к первому выводу первого резистора, истоки и подложки МОП-транзисторов с каналом п-типа первой группы подключены к отрицательной шине питания, а их стоки объединены, подложки и истоки МОП-транзисторов с каналом п-типа второй группы подключены к первому выводу второго резистора, а их стоки объединены, отличающийся тем что, с целью расширения функциональных возможностей, в него введен третий резистор, включенный мезкду стоками МОП-транзисто(Л ров с каналом п-типа первой группы и первым выводом второго резистора, второй вывод которого подключен к первому вьшоду первого резистора, а стоки МОП-транзисторовс каналом п-типа второй группы подключены к выходу элемента и свободному стоку МОПтранзистора с каналом р-типа второй ю группы, а свободный сток МОП-транзис& тора с каналом р-типа первой группы . подключен к второму вьшоду первого to резистора.

| Front I.G., Givone D.D | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Ручной прибор для загибания кромок листового металла | 1921 |

|

SU175A1 |

| Huertas I.L.,Carmona I.M | |||

| Lowpower Ternaly G-MOS- Circuits | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Способ получения борнеола из пихтового или т.п. масел | 1921 |

|

SU114A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1988-04-23—Публикация

1983-01-12—Подача