группы входов блока Формирования максимального кода соединен с первмм входом элемента И, выход второго элемента И каждого узла выделения приоритетного разряда и выход элемента И являются группой выходов устройства, выход второго элемента И в каждом узле выделения приоритетного разряда через элемент НЕ своего узла выделения приоритетного разряда соединен с вторым входом элемейта ИЛИ своего узла выделения приоритетного разряда, выход элемента ИЛИ каждого узла выделения приоритетного разряда соединен в вторым входом-первого элемента И своего узла выделения приоритетного разряда, выход первого элемента И последнего узла выделения приоритетного разряда соединен с вторым входом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения абонентов с общей магистралью | 1984 |

|

SU1223237A1 |

| Многоканальное устройство для приоритетного подключения источников информации к общей магистрали | 1987 |

|

SU1425670A2 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1984 |

|

SU1239717A1 |

| Устройство для подключения источников информации с изменяемыми приоритетами к магистрали | 1983 |

|

SU1166111A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1275459A1 |

| Устройство для формирования видимых сегментов изображений | 1990 |

|

SU1785033A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

МГОЕОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПРИОРИТЕТНОГО ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ, содержащее в каждом канале элемент задержки, три элемента НЕ, два элемента И, два элемента ИЛИ и триггер, причем в каждом канале выход элемента задержки соединен, с первым входом первого элемента И, выход которого является сигнальным выходом устройства, выход запрета устройства через первый элемент НЕ соединен с -первым входом второго элемента И., .о т л и чающееся тем, что, с целью.расширения области применения устройства за счет обслуживания запросов с учетом приоритета источника и информации от негр, в устройство введены сумматор, два регистра, два блока элементов И, схема сравнения и блок формирования максимального кода, содержащий элемент и и группу узлов выделения приоритетного разряда, каждый из которых содержит элемент ИЛИ, элемент НЕ и два элемента И, причем в каждом канале п«рвая группа кодовых входов устройства соединена с группой входов .сумматора, группа выходов которого соединена с первой группой входов первого блока элементов И и с входами первого элемента ИЛИ, выход которого соединен с управляющим входом второго блока элементов.И, группа входов и выходов которого соединены соответственно с группой выходов первого регистра и с второй группой входов первого блока элементов И, управляющий вход и группа выходов которого соединены соответственно с выходом второго элемента НЕ и с груп .пой входов второго регистра,-группа выходов которого соединена с первой 1руппой входов схемы сравнения, выход схемы сравнения, соединен с вторым вх,одом первого элемента .И, выход которого соединен с единичным входом триггера, выход которого соединен с выходом запрета устройства, группа входов второго элемента ИЛИ и вторая группа входов схемы сравне ния соединены с группой выходов устi ройства, выход второго элемента ИЛИ соединен с входом второго элемента СЛ НЕ и с входом элемента задержки, выход которого через третий элемент С НЕ соединен с вторым входом ВТОРОГО элемента И, входы сброса второго регистра, триггера и сумматора соединены с входом конца обслуживания устройства, группа входов первого регистра соединена с второй группой кодовых входов устройства, причем to выход второго элемента И в блоке 00 формирования максимального кода соединен с первыми входами первого и to ел второго элементов И первого узла выделения приоритетного разряда, . выход первого элемента И каждого узла выделения приоритетного разряда соединен с первыми входами первого и второго элементов и следующего узла выделения приоритетного разряда, группа выходов регистра соединена с- группой входов блока формирования максимального кода, каждый вход, начиная с второго, группы входов блока формирования максимального кода соединен с вторым входом второго элемента И ,и с первым входом элемента ИЛИ соответствующего узла выде.лёни.я приоритетного разряда, начи1ная с первого узла, первый вход

Изобретение относится к области вычислительной техники и может быть применено в многомашинных и многопроцессорных вычислительных систе-мах, исп ользующих-для обмена данны ми общую магистраль.. Известно устройство для приоритетного подключения источников информации к магистрали, содержащее в каждом канале узел синхронизации триггер, узел анализа приоритета, элемент задержки, диодные элементы согласования электрическихсигнало линии запрета и опроса Ll3. Недостатком данного устройства является низкая надежность, Наиболее-близким к предлагаемом (по технической сущности является устройство для приоритетного подключения источников информации к ма гистрали, содержащее М блоков обслу живания запросов, каждый из которых включает входной элемент И, соеди ненньай первым входом через первый элемент НЕ с шиной запрета устройст ва, а выходом - с первым входом три гера, первый выход которого подключен к nepBiJM входам выходного элемента И, первого элемента ИЛИ и через элемент задержки к второму входу выходного элемента И, выход которого является соответствующим: выходом сигнала разрешения обмена, выход первого элемента ИЛИ каждого блока обслуживания запросов соединен через линию опроса с вторым вхо дом следующего блока обслуживания запросов, второй выход триггера под ключен через второй элемент НЕ к ши не запрета, устройства, а второй вход - к выходу второго элемента .ИЛИ, первый вход которого соединен через третий элемент НЕ с вторым входом выходного элемента И и соот ветствующим входом сигнала запрета устройства, а второй вход - с вторым входом элемента ИЛИ Сз. Однако известное устройство не обеспечивает учет важности переда. ваемой информации при предоставлении магистрали источникам. Целью изобретения является расширение области применения устройства за счет обслуживания запросов с учетом приоритета источника и информации от. него. Поставленная цель достигается тем, что в многоканальное устройство для приоритетного подключения источников информации к общей магистрали, содержащее в каждом канале элемент задержки, три элемента НЕ, два элемента И, два элемента ИЛИ и триггер, причем в каждом канале выход элемента задержки соединен с первым входом первого элемента И, выход которого является сигнальным выходом устройства, выход запрета устройства через первый элемент НЕ соединен с первым входом второго элемента И, введены сумматор, два регистра, два блока элементов И, схема сравнения и блок формирования максимального кода, содержащий элемент И и группу узлов выделения приоритетного разряда, каждый из которых содержит элемент ИЛИ, элемент НЕ и два элемента И, причем в каждом канале первая группа кодовых входов устройства соединена с группой входов сумматора, группа выходов которого соединена с первой группой входов первого блока элементов И и с входами первого элемента ИЛИ, выход которого соединен с управляющим входом второго блока элементов И, группа входов и выходов которого соединены соответственно- с группой выходов первого регистра и с второй группой входов первого бЛока элементов И, управляющий вход и группа выходов которого соединены соответс5твенно с выходом второго элемента НЕ и с группой входов второго регистра, группа выходов которого соединена с первой группой входов схемы сравнения, выход которой соединен с вторым входом первого ьлемента И, выход которого соединен с единичным входом триггера, выход которого соединен с выходом- запрета устройства, группа входов второго

элемента ИЛИ и вторая группа входов cxeiHH сравнения соединены с группой выходов устройства, выход второго элемента ИЛИ соедине с входом второго элемента НЕ и с входом элемента задержки, .выход которого через третий элемент НЕ соединен с вторым входом второго элемента И, входы сброса второго регистра, триггера и сумматора соединены с входом конца обслуживания устройства,- группа входов первого регистра соединена с второй группой кодовых входов устройства, причем выход второго элемента И в блоке формирования максимального кода соединен с первыми входами первого и второго элементов И первого узла выделения приоритетного разряда, выход первого элемента И каждого узла выщелёния приоритетного разряда; соединен с первыми входами первого и второго элементов И следующего -узла выделе ния приоритетного разряда, группа выходов регистра соединена с группой входов блока формирования максимального кода, каждый вход, начиная с . второго, группы входов блока формирования максимального кода соединен с вторым входом второго элемента И и с первым вводом элемента ИЛИ соответствующего узла выделения приоритетного разряда, начиная с первого узла, первый вход.группы входов блока формирования максимального кода, первый вход группы входов блока формирования .максимального кода сое.динен с первым входом элемента И, выход второго элемента И каждого. узла выделения приоритет.ного разряда и выход элемента И являются группой выходов устройства, выход второго элемента И в каждом узле выделения приоритетного разряда через элемент НЕ своего узла выделения . приоритетного разряда соединен с вторым входом элемента ИЛИ своего узла выделения приоритетного разряда, выход элемента ИЛИ каждого узла выделения приоритетного разряда соединен с вторым входом первого элемента И |своего узла выделения приоритетного разряда, выход первого элемента И последнего узла выделения приоритетного разряда соединен с вторым входом элемента И.

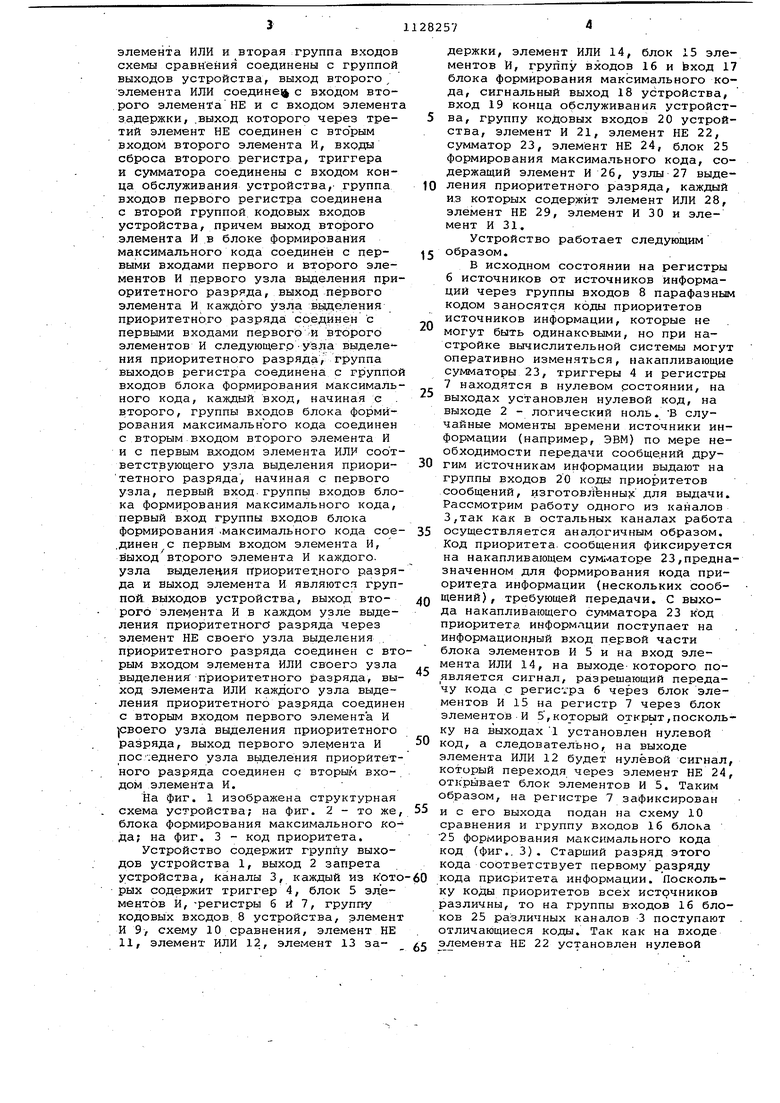

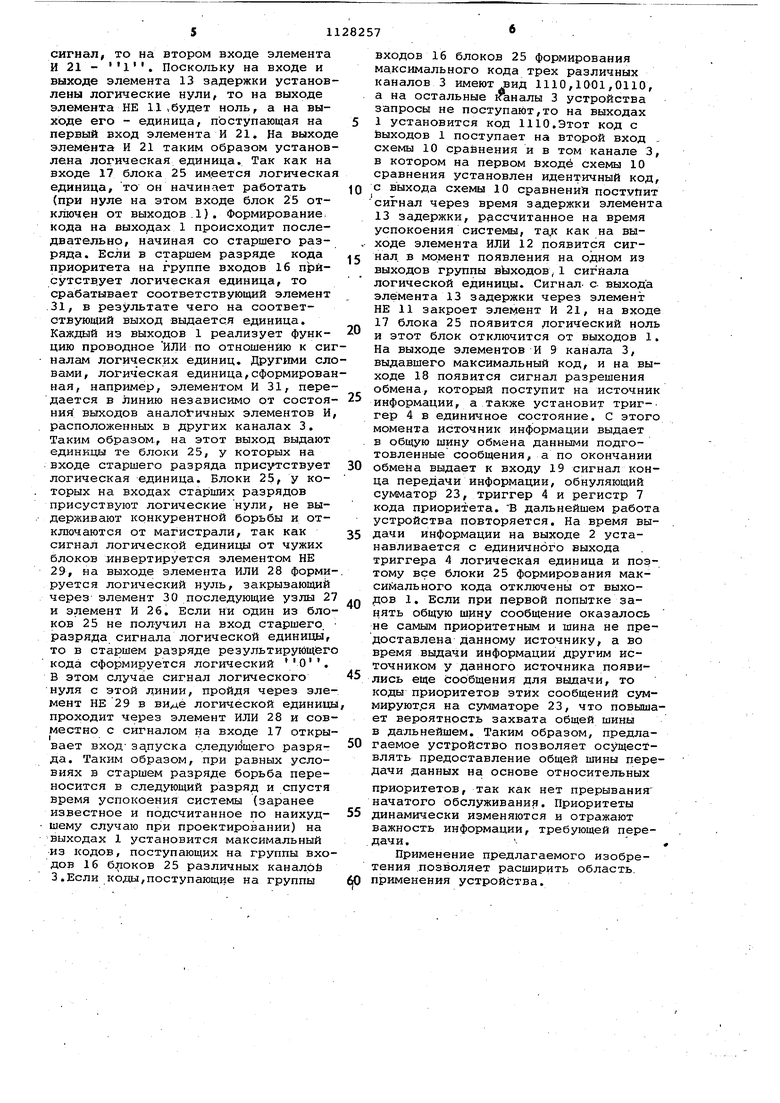

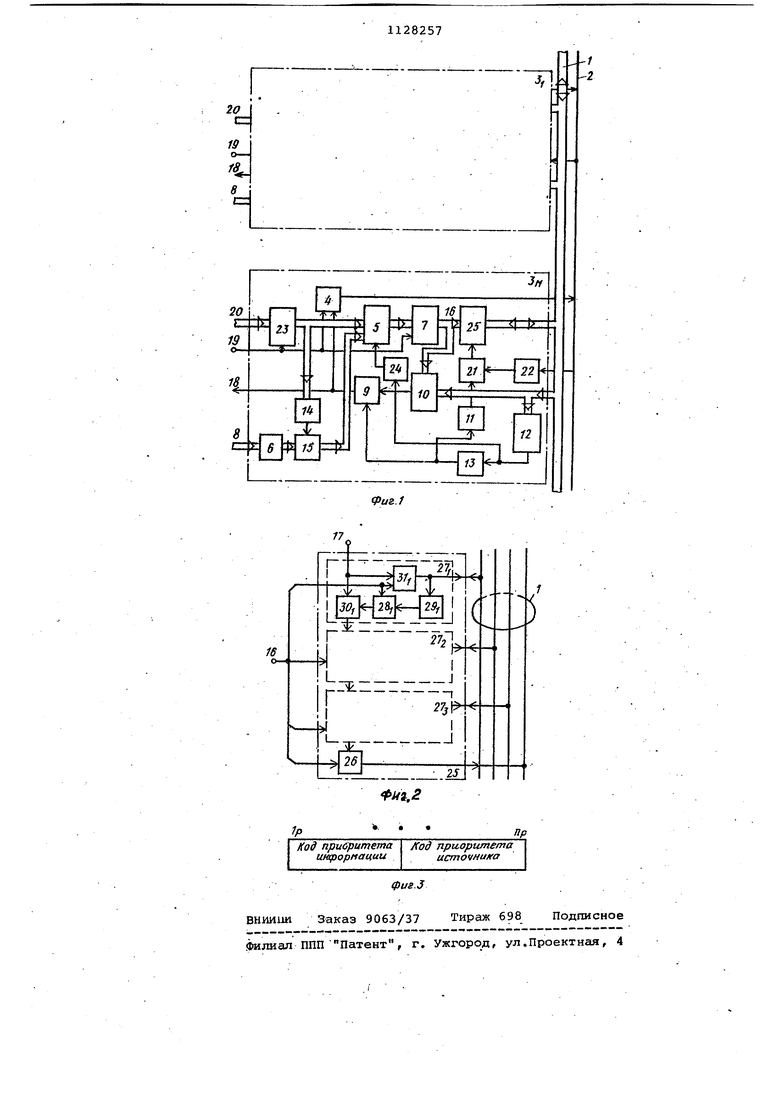

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - то же, блока формирования максимального кода; на фиг. 3 - код приоритета.

Устройство содержит группу выходов устройства 1, выход 2 запрета устройства. Каналы 3, каждый из которых содержит триггер 4, блок 5 элементов И, -регистры б и 7, группу кодовых входов. 8 устройства, элемент И 9, схему 10 сравнения, элемент НЕ 11, элемент ИЛИ 12, элемент 13 задержки, элемент ИЛИ 14, блок 15 элементов И, группу входов 16 и Ьход 17 блока формирования максимального кода, сигнальный выход 18 устройства, вход 19 конца обслуживания устройст5 ва, группу кодовых входов 20 устройства, элемент И 21, элемент НЕ 22, сумматор 23, элемент НЕ 24, блок 25 формирования максимального кода, содержащий элемент И 26, узлы 27 выде10 ления приоритетного разряда, каждый из которых содержит элемент ИЛИ 28, элемент НЕ 29, элемент И 30 и элемент И 31.

Устройство работает следующим 5 образом.

В исходном состоянии на регистры

6источников от источников информации через группы входов 8 парафазным кодом заносятся коды приоритетов

. источников информации, которые не могут быть одинаковыми, но при настройке вычислительной системы могут оперативно изменяться, накапливающие сумматоры 23, триггеры 4 и регистры

7находятся в нулевом состоянии, на выходах установлен нулевой код, на выходе 2 - логический ноль. В случайные моменты времени источники информации (например, ЭВМ) по мере необходимости передачи сообще.ний дру0 гим источникам информации выдают на группы входов 20 коды приоритетов сообщений, изготов 1Ънных для выдачи. Рассмотрим работу одного из каналов 3,так как в остальных каналах работа

5 осуществляется аналогичным образом. Код приоритета сообщения фиксируется на накапливающем сум;иаторе 23,предназначенном для формирования кода приорите.та информации (нескольких сообQ щений) , требующей передачи. С выхода накапливающего сумматора 23 кЪд приоритета информации поступает на информационный вход первой части блока элементов И 5 и на вход элемента ИЛИ 14, на выходе-которого появляется сигнал, разрешающий передачу кода с регистра 6 через блок элементов И 15 на регистр 7 через блок элементов И 5,который открыт,поскольку на выходах 1 установлен нулевой

0 код, а следовательно, на выходе

элемента ИЛИ 12 будет нулевой сигнал, который переходя через элемент НЕ 24, отк.рывает блок элементов И 5. Таким образом, на регистре 7 зафиксирован

5 и с его выхода подан на схему 10 сравнения и группу входов 16 блока 25 формирования макс1 мального кода код (фиг.. 3). Старший разряд этого кода соответствует первому разряду

0 кода приоритета информации. Поскольку коды приоритетов всех источников различны, то на группы входов 16 блоков 25 различных каналов 3 поступают отличающиеся коды. Так как на входе

5 элемента НЕ 22 установлен нулевой

сигнал, то на втором входе элемента И 21 - Ч. Поскольку на входе и выходе элемента 13 задержки установлены логические нули, то на выходе элемента НЕ Избудет ноль, а на выходе его - единица, поступающая на первый вход элемента И 21. На выходе элемента И 21 таким образом установлена логическая единица. Так как на входе 17 блока 25 имеется логическая единица, то он начинает работать (при нуле на этом входе блок 25 отключен от выходов. 1), Формирование кода на выходах 1 происходит последвательно, начиная со старшего разряда. Если в старшем разряде кода приоритета на группе входов 16 присутствует логическая единица, то срабатывает соответствующий элемент .31, в результате чего на соответствующий выход выдается единица. Каждый из выходов 1 реализует функцию проводное ИЛИ по отношению к сигналам логических единиц. Другими словами, логическая единица,сформированная, например, элементом И 31, передается в линию независимо от состояния выходов аналогичных элементов И, расположенных в других каналах 3. Таким образом, на этот выход выдают единицы те блоки 25, у которых на входе старшего разряда присутствует логическая единица. Блоки 25, у которых на входах старших разрядов присуствуют логические нули, не выдерживают конкурентной борьбы и отключаются от магистрали, так как сигнал логической единицы от чужих блоков .инвертируется элементом НЕ 29, на выходе элемента ИЛИ 28 формируется логический нуль, закрывающий через элемент 30 последующие узлы 27 и элемент И 26. Если ни один из блоков 25 не получил на вход старшего разряда сигнала логической единицыf то в старшем разряде результирующего кода сформируется логический 0. В этом случае сигнал логического нуля с этой линии, пройдя через элемент НЕ 29 в логической единицы проходит через элемент ИЛИ 28 и совместно с сигналом на входе 17 открыIi

вает ВХОД за.пуска следующего разряда. Таким образом, при равных условиях в старшем разряде борьба переносится в следующий разряд и спустя время успокоения системы (заранее известное и подсчитанное по наихудшему случаю при проектировании) на выходах 1 установится максимальный из кодов, поступающих на группы входов 16 блоков 25 различных каналоё 3.Если коды,поступающие на группы

входов 16 блоков 25 формирования максимального кода трех различных каналов 3 имеют вид 1110,1001,0110, а на остальные каналы 3 устройства запросы не поступак)т,то на выходах 1 установится код ШО.Этот код с йыходов 1 поступает на второй вход схемы 10 сравнения и в том канале 3, в котором на первом йходё схемы 10 сравнения установлен идентичный код, с выхода схемы 10 сравнений ПОСТУПИТ сигнал через время задержки элемента 13 задержки, рассчитанное на время успокоения системы, iaj как на выходе элемента ИЛИ 12 появится сигнал, в момент появления на одном из выходов группы вУходов,1 сигнала логической единицы. Сигнал- с- выхода элемента 13 задержки через элемент НЕ 11 закроет элемент И 21, на входе 17 блока 25 появится ;1огический ноль и этот блок отключится от выходов 1. На выходе элементов И 9 канала 3, выдавшего максимальный код, и на выходе 18 появится сигнал разрешения обмена, который поступит на источник информации, а также установит триг-гер 4 в единичное состояние, С этого момента источник информации выдает в общую шину обмена данными подготовленные сообщения, а по окончании обмена выдает к входу 19 сигнал конца передачи информации, обнуляющий сумматор 23, триггер 4 и регистр 7 кода приоритета. В дальнейшем работа устройства повторяется. На время выдачи информации на выходе 2 устанавливается с единичного выхода триггера 4 логическая единица и поэтому все блоки 25 формирования максимального кода отключены от выходов 1. Если при первой попытке занять общую шину сообщение оказалось не самым приоритетным и шина не предоставлена данному источнику, а во время выдачи информации другим источником у данного источника появились еще сообщения для выдачи, то коды приоритетов этих сообщений суммируютря на сумматоре 23, что повышает вероятность захвата общей шины в дальнейшем. Таким образом, предлагаемое устройство позволяет осуществлять предоставление общей шины передачи данных на основе относительных приоритетов, так как нет прерывания начатого обслуживания. Приоритеты динамически изменяются и отражают важность информации, требующей передачи,

Применение предлагаемого изобретения позволяет расширить область, применения устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-07—Публикация

1983-08-26—Подача