«1

Изобретение относится к вычислительной технике и может быть применено в многомапшнных и многопроцессор - ных вычислительных системах, использующих для обмена данными общую ма- ГНСтраль.

Цель изобретения - расширение функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала.

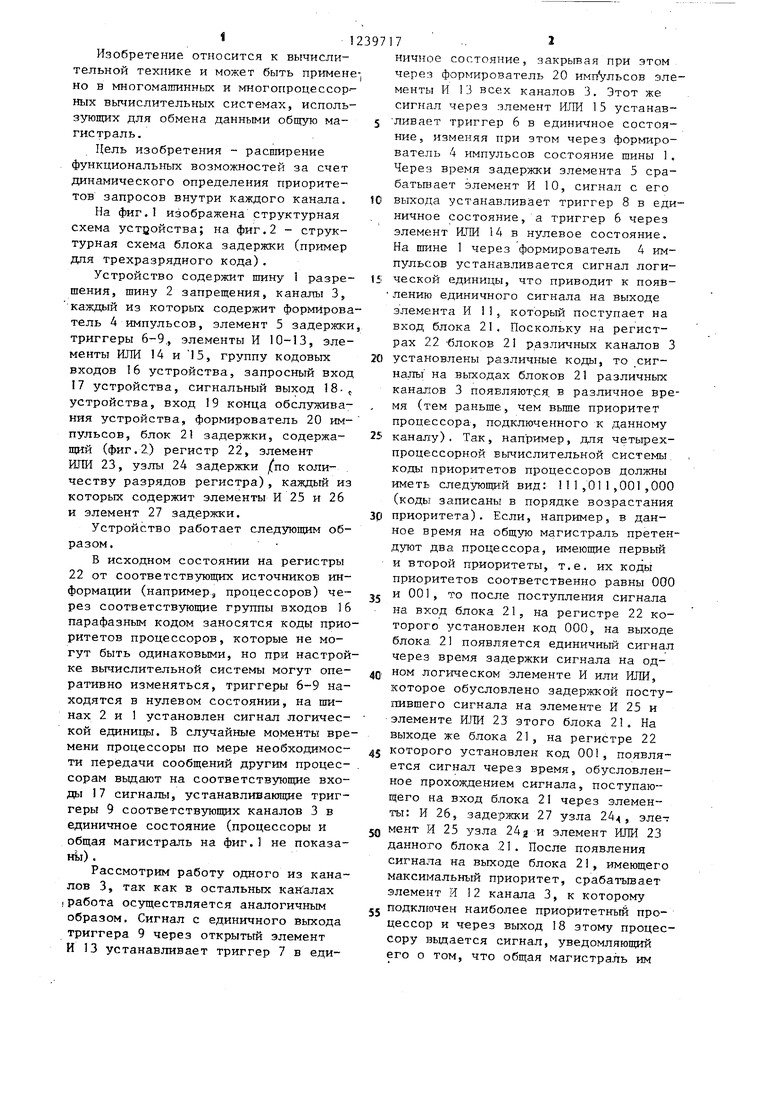

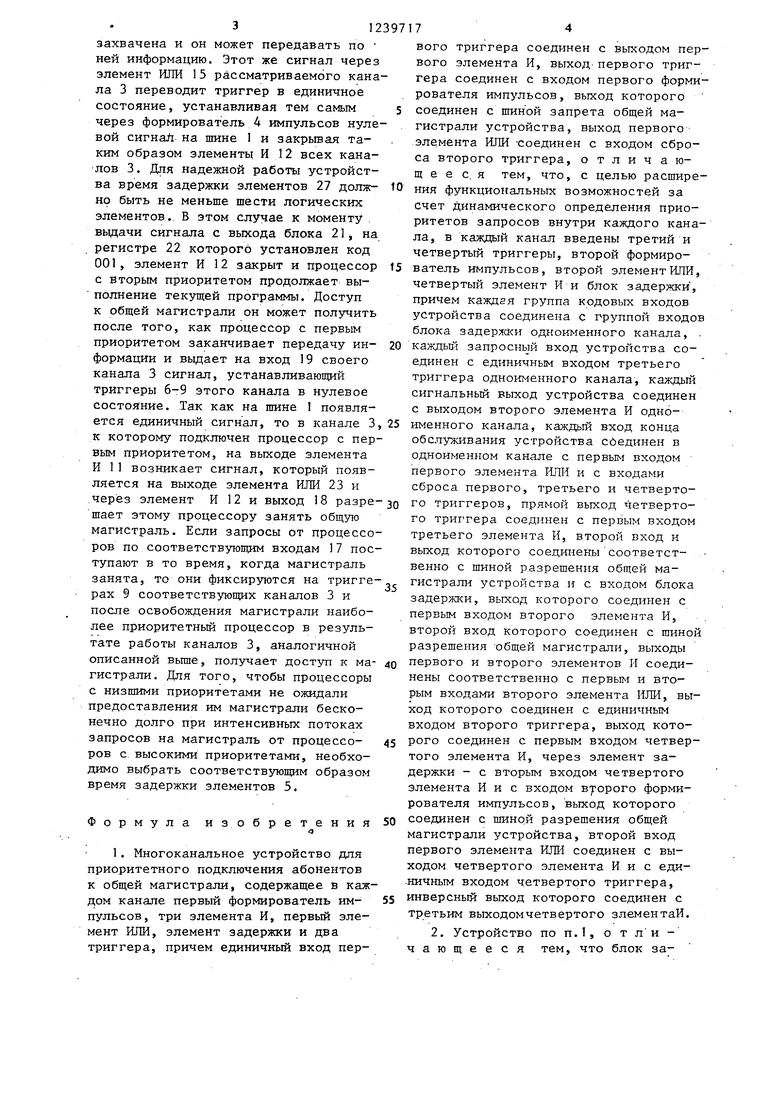

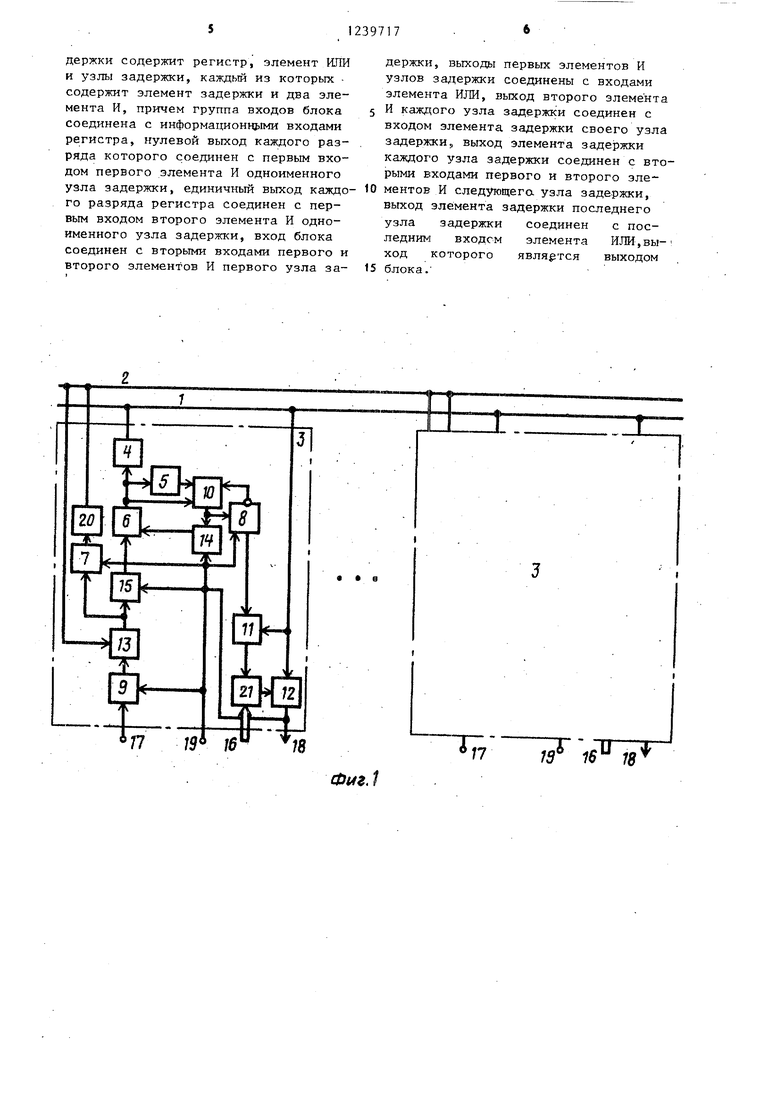

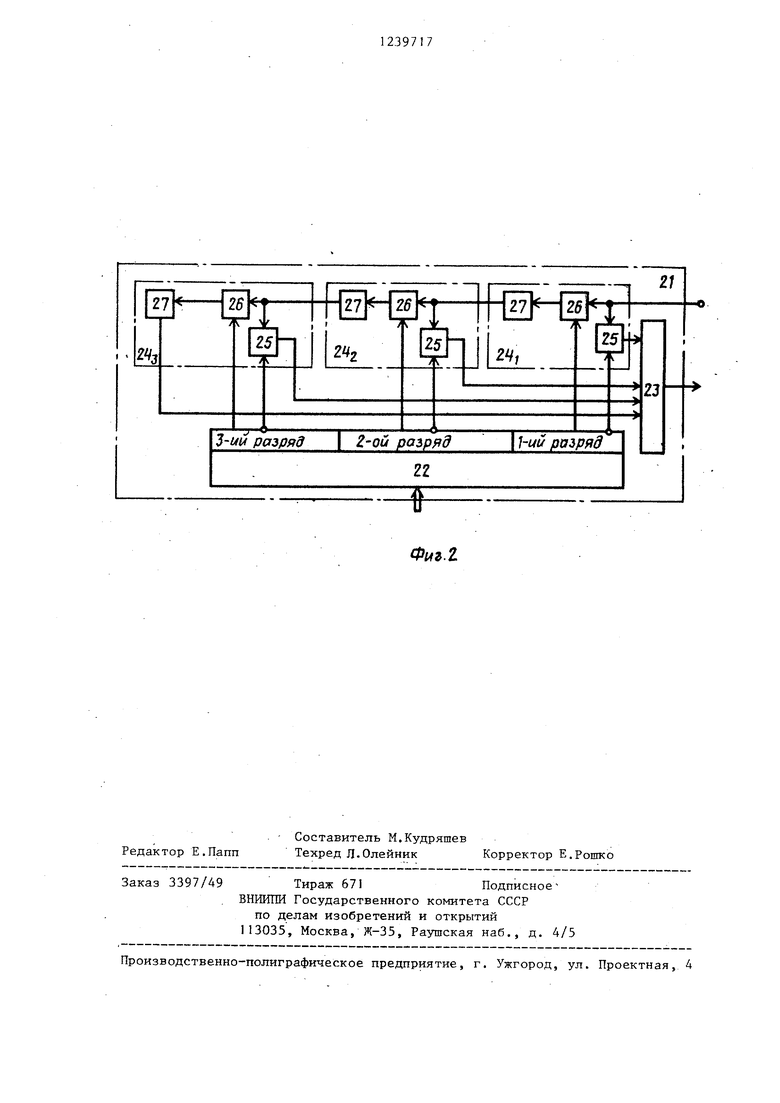

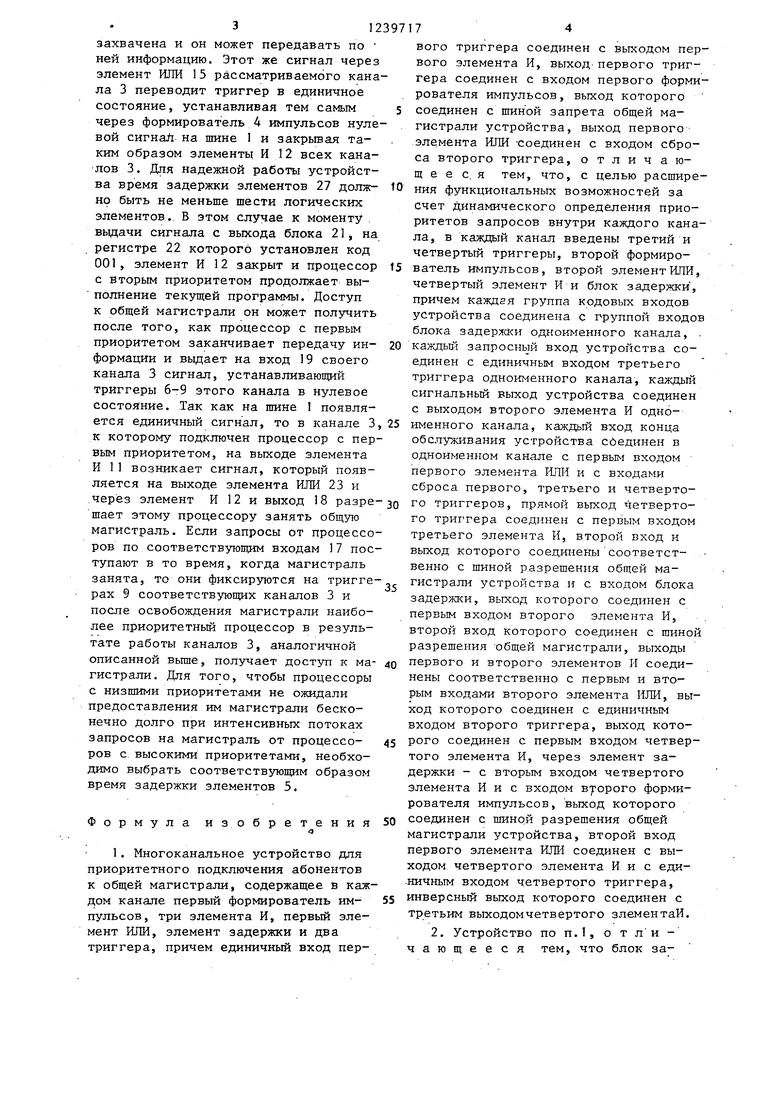

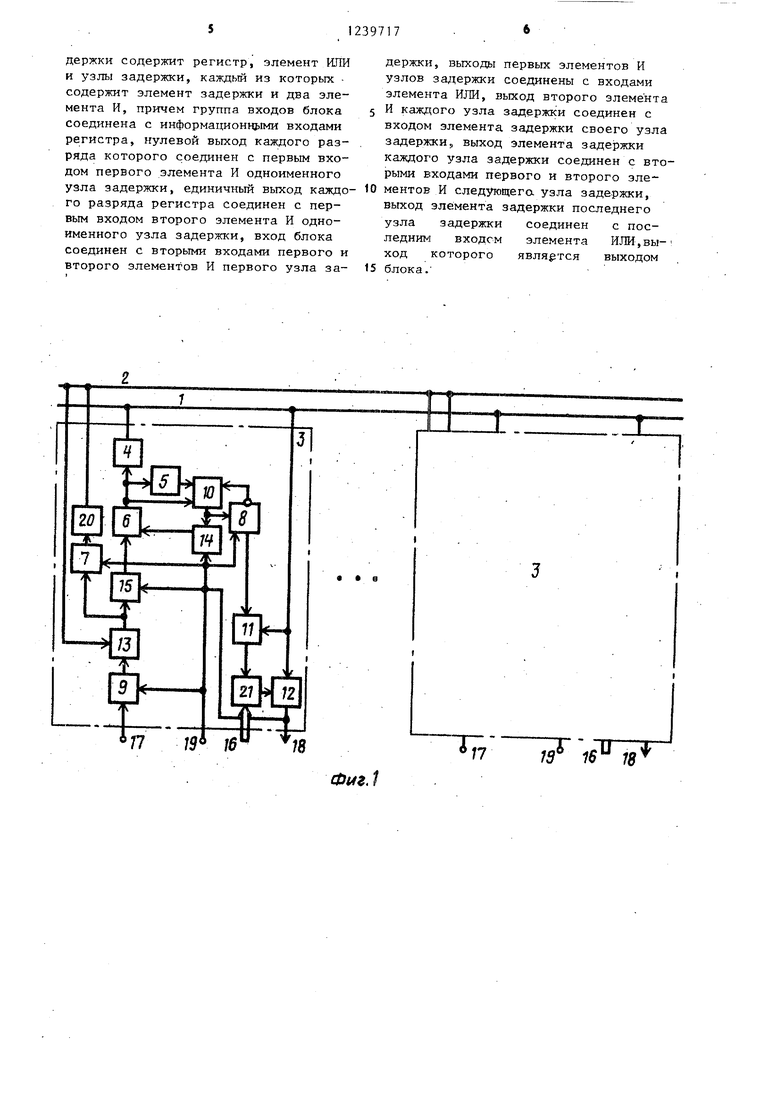

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока задержки (пример для трехразрядного кода).

Устройство содержит шину 1 разре- шения, шину 2 запрещения, каналы 3, каждый из которых содержит формирователь 4 импульсов, элемент 5 задержки триггеры 6-9., элементы И 10-13, элементы ИЛИ 4 и 15, группу кодовых входов 16 устройства, запросный вход 17 устройства, сигнальный выход 18- устройства, вход 19 конца обслуживания устройства, формирователь 20 им- пульсов, блок 21 задержки, содержа- щий (фиг.2) регистр 22, элемент ИЛИ 23, узлы 24 задержки /по коли- . честву разрядов регистра), каждый из которых содержит элементы И 25 и 26 и элемент 27 задержки.

Устройство работает следующим образом,

В исходном состоянии на регистры 22 от соответствующих источников информации (например, процессоров) че- рез соответствующие группы входов 16 парафазным кодом заносятся коды приоритетов процессоров, которые не могут быть одинаковыми, но при настройке вычислительной системы могут one- ративно изменяться, триггеры 6-9 находятся в нулевом состоянии, на шинах 2 и 1 установлен сигнал логичес- кой единицы. В случайные моменты времени процессоры по мере необходимое- ти передачи сообщений другим процес- сорам выдают на соответствующие входы 17 сигналы, устанавливающие триггеры 9 соответствзпощих каналов 3 в единичное состояние (процессоры и общая магистраль на фиг.1 не показаHbl) .

Рассмотрим работу одного из каналов 3, так как в остальных каналах I работа осуществляется аналогичньгм образом. Сигнал с единичного выхода триггера 9 через открытый элемент И 13 устанавливает триггер 7 в еди

.

5

7 .. 2 ничное состояние, закрывая при этом через формирователь 20 импVльcoв элементы И 13 всех каналов 3. Этот же сигнал через элемент ИЛИ 15 устанавливает триггер 6 в единичное состояние, изменяя при этом через формирователь 4 импульсов состояние шины 1. Через время задержки элемента 5 сра- батьшает элемент И 10, сигнал с его выхода устанавливает триггер 8 в единичное состояние, а триггер 6 через элемент ИЛИ 14 в нулевое состояние. На шине 1 через формирователь 4 импульсов устанавливается сигнал логической единицы, что приводит к появлению единичного сигнала на выходе элемента И 11,, который поступает на вход блока 21, Поскольку на регистрах 22 -блоков 21 различных каналов 3 установлены различные коды, то сиг- налы на выходах блоков 21 различных KaHajioB 3 появляются, в различное время (тем раньше, чем вьшхе приоритет процессора, подключенного к данному каналу). Так, например, для четьфех- процессорной вычислительной системы, коды приоритетов процессоров должны иметь следующи:й вид: 111,011,001,000 (кодьг записаны в порядке возрастания приоритета). Если, например, в данное время на общую магистраль претендуют два процессора, имеющие первый и второй приоритеты, т.е. их коды приоритетов соответственно равны 000 и 001, то после поступления сигнала на вход блока 21, на регистре 22 которого установлен код 000, на выходе блока 21 появляется единичный сигнал через время задержки сигнала на одном лог -гческом элементе И или ИЛИ, которое обусловлено задержкой поступившего сигнала на элементе И 25 и элементе ИЛИ 23 этого блока 21. На выходе ж:е блока 21, на регистре 22 которого установлен код 001, появляется сигнал через время, обусловленное прохождением сигнала, поступающего на вход блока 2I через элементы: И 26, задержки 27 узла 24, эле-г мент И 25 узла 242 и элемент ИЛИ 23 данного блока 2I. После появления сигнала на выходе блока 21, имеющего максимальный приоритет, срабатьгеает элемент И 12 канала 3, к которому ггадклЕочен наиболее приоритетный процессор и через выход 18 этому процессору выдается сигнал, уведомляющий его о том, что общая магистраль им

312

захвачена и он может передавать по ней информацию. Этот же сигнал через элемент ИЛИ 15 рассматриваемого канала 3 переводит триггер в единичное состояние, устанавливая тем самым через формирователь 4 импульсов нулевой сигнал на шине 1 и закрьшая таким образом злементы И 12 всех кана- лов 3. Для надежной работы устройства время задержки элементов 27 долж- но быть не меньше шести логических элементов. В этом случае к моменту . вьщачи сигнала с выхода блока 21, на регистре 22 которого установлен код 001, элемент И 12 закрыт и процессор с вторым приоритетом продолжает выполнение текущей программы. Доступ к общей магистрали он может попучг тъ после того, как процессор с первым приоритетом заканчивает передачу ин- формации и вьщает на вход 19 своего канала 3 сигнал, устанавливающий триггеры 6-9 этого канала в нулевое состояние. Так как на шине 1 появляется единичный сигнал, то в канале 3 к которому подключен процессор с первым приоритетом, на выходе элемента И 11 возникает сигнал, который появляется на выходе элемента ИЛИ 23 и через элемент И 12 и выход 18 разре шает этому процессору занять общую магистраль. Если запросы от процессоров по соответствующим входам 17 поступают в то время, когда магистраль занята, то они фиксируются на триггерах 9 соответствующих каналов 3 и после освобождения магистрали наиболее приоритетный процессор в результате работы каналов 3, аналогичной описанной выше, получает доступ ic ма- гистрали. Для того, чтобы процессоры с низшими приоритетами не ожидали предоставления им магистрали бесконечно долго при интенсивных потоках запросов на магистраль от процессо- ров с высокими приоритетами, необходимо выбрать соответствуюшдм образом время задержки элементов 5.

Формула изобретения

4

1. Многоканальное устройство для приоритетного подключения абонентов к общей магистрали, содержащее в каждом канале первый формирователь им- пульсов, три элемента И, первый элемент РШИ, элемент задержки и два триггера, причем единичный вход пер174

вого триггера соединен с выходом первого элемента И, выход- первого триггера соединен с входом первого формирователя импульсов, выход которого соединен с шиной запрета общей магистрали устройства, выход первого элемента ИЛИ -соединен с входом сброса второго триггера, отличаю- щ е е с. я тем, что, с целью расширения функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала, в каждый канал введены третий и четвертый триггеры, второй формирователь импульсов, второй элемент ИЛИ, четвертый элемент И и блок задержки , причем каждгя группа кодовых входов устройства соединена с группой входо блока задержки одноименного канала, каждьй запросный вход устройства соединен с единичным входом третьего триггера одноименного канала, каждый сигнапьньй выход устройства соединен с выходом второго элемента И одноименного канала, каждый вход конца обслуживания устройства сбединен в одноименном канале с первым входом первого элемента ИЛИ и с входами сброса первого, третьего и четвертого триггеров, прямой выход четвертого триггера соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответст- венно с шиной разрешения общей магистрали устройства и с входом блока задержки, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с шиной разрешения -общей магистрали, выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера, выход которого соединен с первым входом четвертого элемента И, через элемент задержки - с вторым входом четвертого элемента И и с входом в орого формирователя импульсов, выход которого соединен с шиной разрешения общез магистрали устройства, второй вход первого элемента ИШ соединен с выходом четвертого элемента И и с еди- .ничным входом четвертого триггера, инверсный выход которого соединен с третьим выходомчетвертого злементаИ.

2. Устройство по п.1, о т л и - чающееся тем, что блок задержки содержит регистр, элемент ИЛИ и узлы задержки, каждый из которых содержит элемент задержки и два элемента И, причем группа входов блока соединена с информационн1 1ми входами регистра, нулевой выход каждого разряда которого соединен с первым входом первого элемента И одноименного узла задержки, единичный выход каждого разряда регистра соединен с первым входом второго элемента И одноименного узла задержки, вход блока соединен с вторыми входами первого и второго элементов И первого узла задержки, выходы первых элементов И узлов задержки соединены с входами элемента ИЛИ, выход второго элемента

5 И каждого узла задержки соединен с входом элемента задержки своего узла задержки,, выход элемента задержки каждого узла задержки соединен с вторыми входами первого и второго эле10 ментов И следздащега узла задержки, выход элемента задержки последнего узла задержки соединен с последним входом элемента ИЛИ,вы- ход которого является выходом

15 блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1986 |

|

SU1397914A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1709312A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1987 |

|

SU1462311A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1987 |

|

SU1458873A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Многоканальное устройство для приоритетного подключения источников информации к мультишинной магистрали | 1989 |

|

SU1647564A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Многоканальное устройство для приоритетного подключения абонентов к общей магистрали | 1989 |

|

SU1589277A2 |

| Мультиплексный канал | 1980 |

|

SU957199A1 |

| Многоканальное устройство для сопряжения абонентов с общей магистралью | 1984 |

|

SU1223237A1 |

Изобретение относится к области вычислительной техники и может быть применено в многонашинных и многопроцессорных вычислительных системах, использзпощих для обмена данными общую магистраль . Целью изобретения является расширение функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала. Цель достигается путем изменения схемы каналов- введением в каждый канал дополннтель- но двух триггеров, формирователя импульсов, элемента 1-ШИ, элемента И и блока задержки, соединенных соответственно с другими узлами и элементами устройства. Кроме того, блок задержки имеет характерное для данного устройства схемное вьшолнение. 1 з.п.- ф-лы, 2 ил. I СО 1О со

77 19

I

17

13

Фиг. 1

Z-w разряд 2 Ой разряд

Редактор Е.Папп

Составитель М.Кудряшев

Техред Л.Олейник Корректор Е.Рошко

Заказ 3397/49 Тираж 671ПодписноеВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фмъ.1

| Устройство для приоритетного подключения источников информации к магистрали | 1979 |

|

SU860073A2 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Многоканальное устройство приоритета | 1978 |

|

SU798839A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-09-15—Подача