Изобретение относится к вычислительной технике и может быть использовано для построения устройств цифровой обработки и формирования изображений на экранах растровых систем отображения при создании комбинированных кадров, в устройствах сжатия видеоинформации, а также в устройствах сортировки элементов по группам.

Цель изобретения - повышение быстродействия и упрощение устройства за счет сокращения памяти путем обработки и хранения сегментированных описаний приоритетных плоскостей изображения.

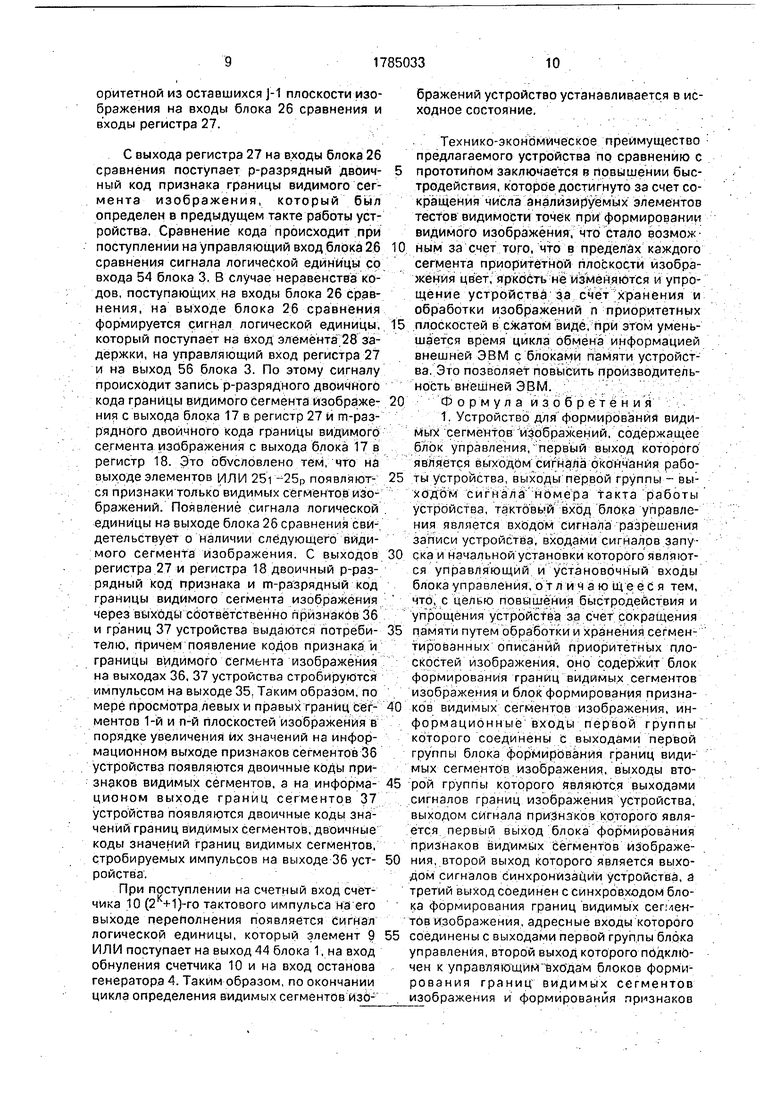

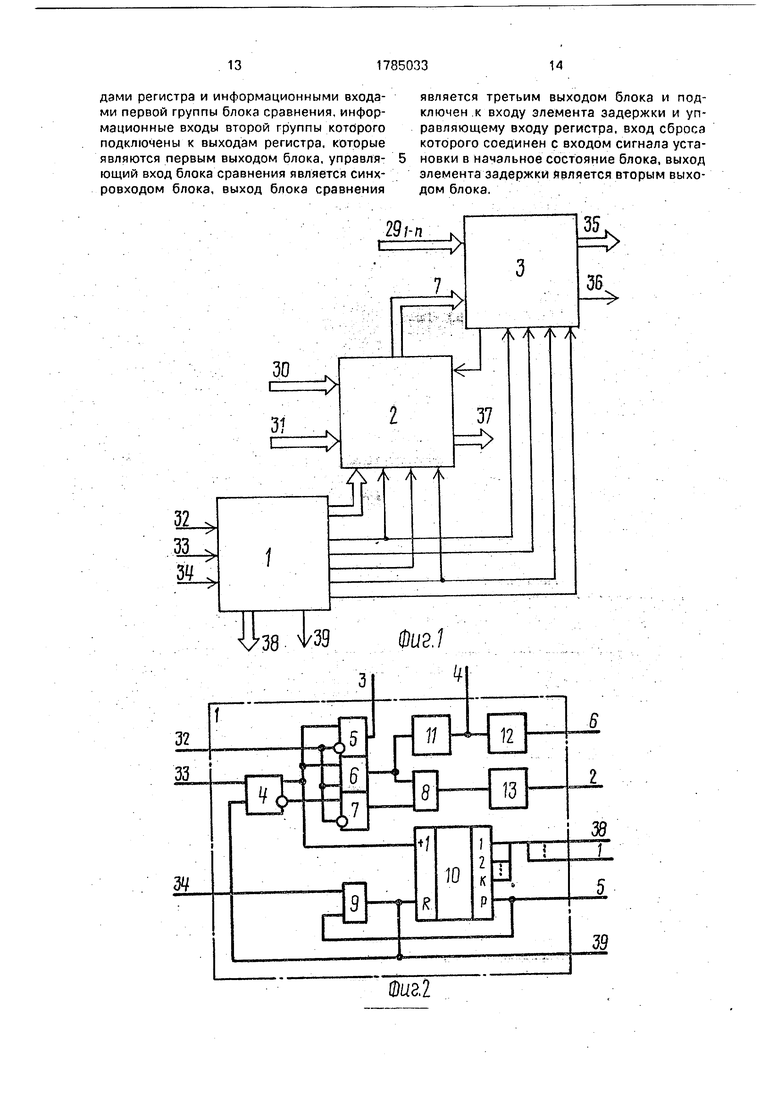

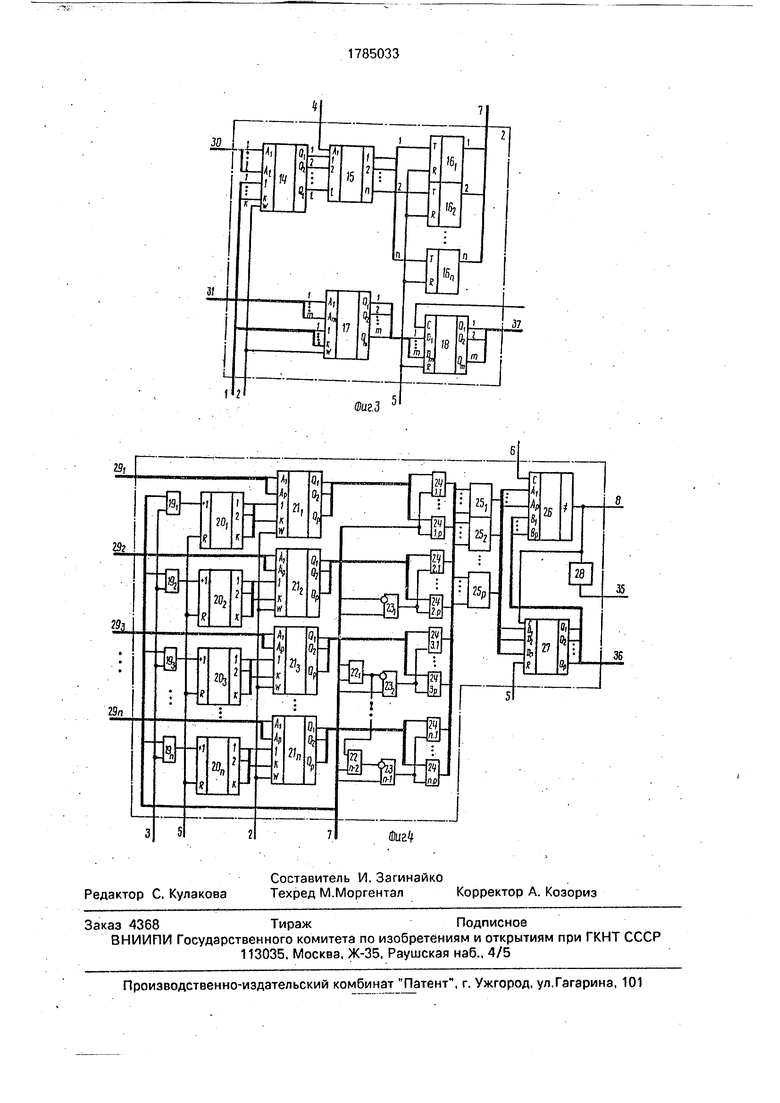

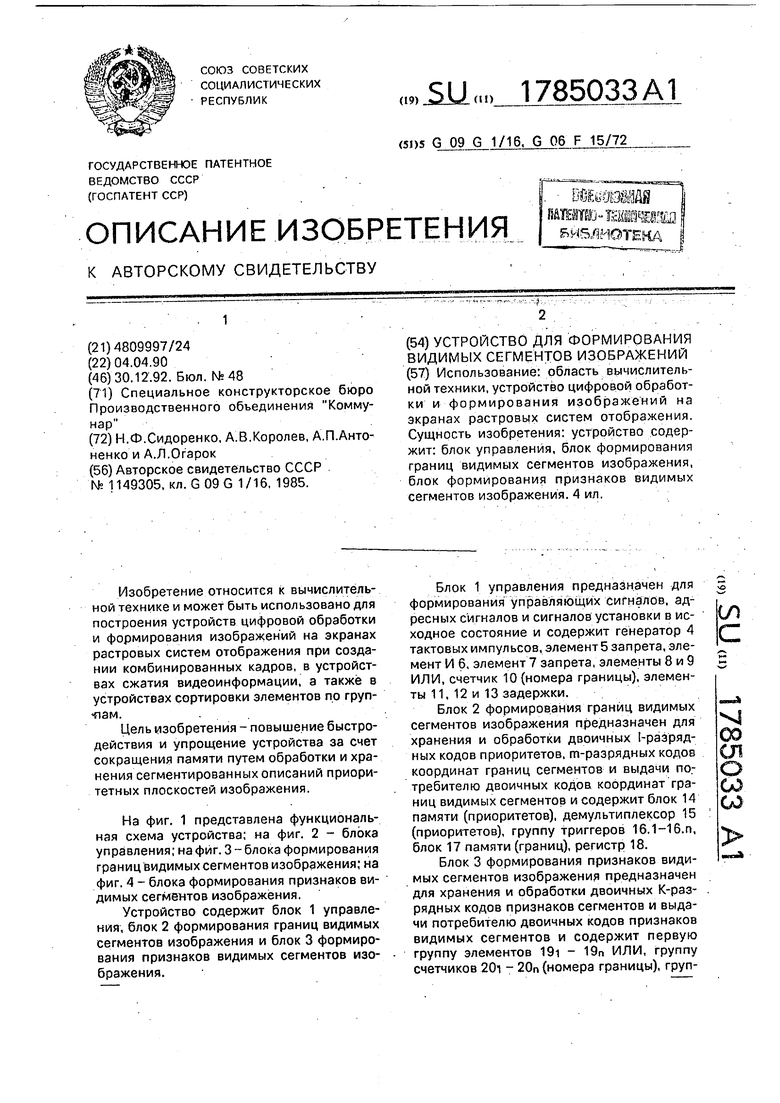

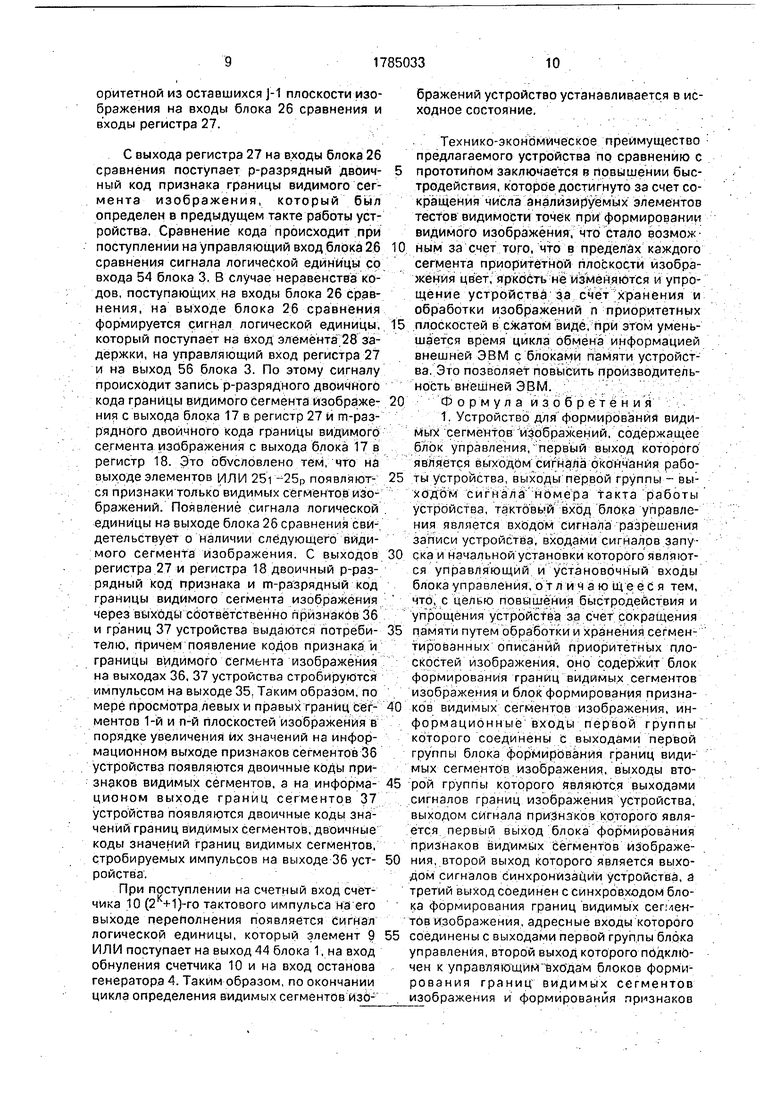

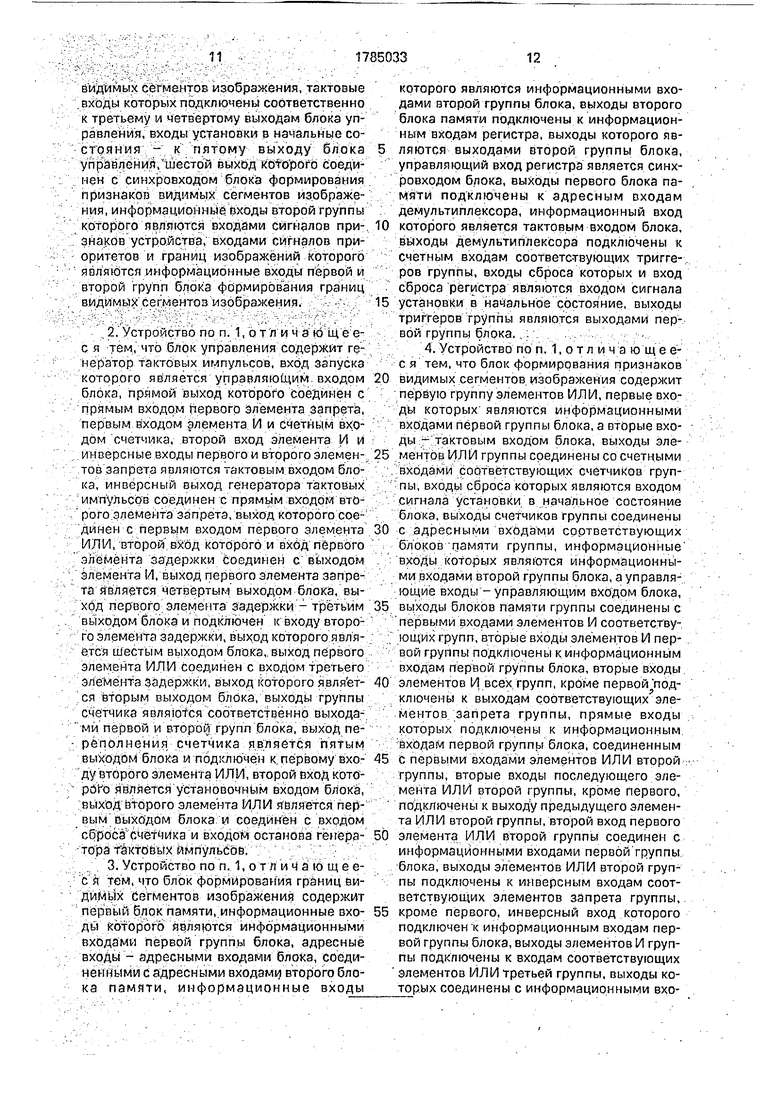

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - блока управления; на фиг. 3 - блока формирования границ видимых сегментов изображения; на фиг. 4 - блока формирования признаков видимых сегментов изображения.

Устройство содержит блок 1 управления, блок 2 формирования границ видимых сегментов изображения и блок 3 формирования признаков видимых сегментов изображения.

Блок 1 управления предназначен для формирования управляющих сигналов, адресных сигналов и сигналов установки в исходное состояние и содержит генератор 4 тактовых импульсов, элемент 5 запрета, элемент И 6, элемент 7 запрета, элементы 8 и 9 ИЛИ, счетчик 10 (номера границы), элементы 11, 12и 13 задержки.

Блок 2 формирования границ видимых сегментов изображения предназначен для хранения и обработки двоичных 1-разрядных кодов приоритетов, m-разрядных кодов координат границ сегментов и выдачи по.- требителю двоичных кодов координат границ видимых сегментов и содержит блок 14 памяти (приоритетов), демультиплексор 15 (приоритетов), группу триггеров 16.1-16.П, блок 17 памяти (границ), регистр 18.

Блок 3 формирования признаков видимых сегментов изображения предназначен для хранения и обработки двоичных К-раз- рядных кодов признаков сегментов и выдачи потребителю двоичных кодов признаков видимых сегментов и содержит первую группу элементов 19i - 19П ИЛИ, группу счетчиков 20т - 20п (номера границы), трупсл С

х 00 СП

со со

пу блоков 211 - 21П памяти, вторую группу элементов 22i - 22П ИЛИ, группу элементов 23i - 23П запрета, группу элементов 241 - 24Р, третью группу элементов 25i - 25Р ИЛИ, блок 26 сравнения, регистр 27 (признаков) и элемент 28 задержки.

Позициями 29i - 29П обозначены входы сигналов признаков устройства, 30 - вход сигналов приоритетов, 31 - вход сигналов границ, 32, 33 и 34 - входы сигналов разрешения записи, запуска и начальной установки устройства, 35, 36 - второй и первый выходы блока, 3,37 - выходы второй группы блока 2, 38 и 39 - выход сигнала окончания работы и выход сигнала номера такта работы устройства соответственно.

Позициями 40-45 соответствующие выходы блока 1 управления, 46-50 - соответствующие входы блока 2, 51-55 - соответствующие входы блока 3, а 56 - его третий выход, 57 - выход блока 2.

Устройство работает следующим образом. Комбинированное изображение создается путем приоритетного наложения сегментированных описаний п числа разнесенных по глубине плоскостей изображений таким образом, что каждая точка видимого изображения, формируемого на экранной плоскости, соответствует одной точке изображений 1-й приоритетной плоскости Более близкая к наблюдателю плоскость изображения имеет больший приоритет. Сегментированное изображение в каждой плоскости определено множеством значений левых и правых границ сегментов, приоритетом границ сегментов данной плоскости изображения и признаками сегментов изображения (цвет, яркость отображаемых объектов). Комбинированное изображение определяется мн ожест- вом значений левых границ видимых сегментов, а также множеством признаков видимых сегментов изображения множеством комбинаций яркостей и цветов отображаемых объектов соответствующих плоскостей изображений.

Устройство работает по тактам. Длительность такта определяется периодом следования тактовых импульсов, формируемых генератором 4 тактовых импульсов. В каждом такте устройство обрабатывает очередное ближайшее (большее) значение левой или правой границы сегмента 1- п-й плоскостей изображения и определяет его видимость. Определение видимых сегментов основано на сравнении приоритетов границ сегментов 1-й - n-й плоскостей изображения в процессе развертки.

Устройство работает в режиме записи сегментов 1-й - n-й приоритетных плоскостей изображений в блоки памяти и в режиме определения видимых сегментов изображений.

В исходном состоянии группа счетчиков

(номера границы) 20i - 20п, регистр 27, группа триггеров 16i - 16n, регистр 18, счетчик (номера границы) 10 обнулены сигналом логической единицьтоступрющим со входа 34 начальной установки устройства через эле0 мент 9 ИЛИ и выход 44 блока 1 управления на входы сброса элементов.

Для записи двоичных кодов признаков, приоритетов, границ сегментов 1-й - п-пло- скостей изображения в группу блоков памя5 ти 211 - 21 п в блок 14 памяти (приоритетов) и в блок 17 памяти (границ) соответственно, на вход 32 разрешения записи устройства подается потенциал логического нуля, который поступает на инверсные входы элемен0 тов 5, 7 запрета и первый вход элемента 6 И. Элементы 5, 7 запрета открываются и разрешают прохождение последовательности 2 тактовых импульсов с прямого и инверсного выходов генератора 4 на выходы

5 43 и 41 блока 1 соответственно. Элемент 6 И закрывается и запрещает прохождение тактовых импульсов с. прямого выхода генератора 4 на выходы 41, 42 и 45 блока 1. На вход запуска 33 устройства подается сигнал

0 логической единицы, который запускает генератор 4. С прямого выхода генератора 4 последовательности - 1 тактовых импульсов поступает на выход 43 блока 1 через элемент 5 запрета и на счетный вход счетчи5 ка- 10. С инверсного выхода генератора 4 последовательность 2+1 тактовых импульсов поступает через элемент 7 запрета, элемент 8 ИЛИ, элемент 13 задержки на выход 41 блока 1. С выхода 43 блока 1 через вход

0 52 блока 3, через группу элементов ИЛИ 19i - 19П последовательность 2К+ 1 импульсов поступает на счетные входы счетчиков 20i - 20П. Группа счетчиков 20i - 20n, счетчик 10 формируют возрастающую последо5 вательность адресных кодов, которая поступает соответственно на адресные входы группы блоков памяти 21 - 21П, блока памяти 14 и блока 17 памяти. Адресные коды с выходов счетчиков 191 - 19п и счетчика

0 10 поступают на адресные входы блока 14 и блока 17, а также на выход 36 блока 1. На управляющие входы блока 14, блока 17 и группы блоков памяти 211 - 21П поступает последовательность 2к сигналов логическо5 го нуля, разрешающая запись соответственно приоритетов, границ и признаков сегментов изображений. Синхронно со сменой адресных кодов на входы 29i - 29П устройства, на входы 30 и 31 признаков, 1-разрядные коды приоритетов устройства

поступают двоичные Р-разрядные коды и m-разрядные коды границ сегментов 1-й - n-й плоскостей изображения, которые последовательно записываются в группу блоков памяти 211 - 21п, в блок 14 и в блок 17 соответственно, Двоичные коды границ сегментов в блоке 17 упорядочены по возрастанию их значений, В случае, если значения координат границ сегментов изображений, принадлежащих различным плоскостям, равны, по меньшему адресу записывается информация о сегменте с большим приоритетом, т.е. принадлежащему плоскости с меньшим номером.

Изменение кодов признаков, приоритетов и границ на входах 291 - 29n, 30 и 31 происходит в соответствии со значением двоичного кода, поступающего с выхода счетчика 10 на выход 38 блока 1. Запись кодов признаков, приоритетов и границ сегментов в блоки памяти происходит в момент поступления низкого потенциала с инверсного выхода генератора 4 через элемент 7 запрета, элемент 8 ИЛИ. элемент 13 задержки, выход 41 блока, входы 47 и 51 блоков 2, 3 на управляющие входы соответствующих блоков памяти синхронно с информационными и адресными кодами. При поступлении (2К + 1)-го тактового импульса с прямого выхода генератора 4 на счетный вход счетчика 10 с его выхода переполнения через элемент 9 ИЛИ, выход 44 блока 1t выход 39 блока 1 поступает потенциал логической единицы. Генератор 4 прекращает выдачу тактовых импульсов, а счетчик 10, регистр границ 18, группа тригге-1 ров 16i - 1бп, регистр 27 при этом обнуляются. Схема возвращается в исходное состояние, а в блоках памяти 211 - 21П, в блоке 14 и блоке 17 остаются записанными соответственно коды признаков, приоритетов и границ сегментов 1-й - n-й плоскостей изображения. На этом заканчивается цикл записи кодов в блоки памяти устройства.

Для установки режима выборки видимых сегментов на вход 32 разрешения запи- си устройства подается потенциал логической единицы, который закрывает элемент 5, 7 запрета и разрешает прохождение последовательности 2к тактовых импульсов через элемент 6И.

На вход 33 запуска устройства подается сигнал логической единицы, который запускает генератор тактовых импульсов 4. С прямого выхода генератора. 4 последовательность 2К - 1 импульсов поступает на счетный вход счетчика 10 и через элементы Иб, ИЛИ 8 и элемент 13 задержки на выход 41 блока 1. Последовательность 2К импульсов с выхода элемента 6 И поступает На

выход 42 блока 1 через элемент 11 задержки, на выход 45 блока 1 - через элементы 11 и 12 и на выход 41 блока 1 - через элемент 8 ИЛИ и элемент 13 задержки. 5Последовательность 2К тактовых импульсов с выходов 41,42 и 45 блока 1 поступает на входы 47, 48, 51, 54 блоков 2, 3 соответственно. При поступлении кода адреса с выхода 40 блока 1 и синхроимпульса

0 с выхода 41 блока 1 на адресные и управляющие входы блоков памяти 14 и 17 с их выходов на входы, регистра 18 и демультип- лексора 15 поступают двоичные коды соответственно границ и приоритета

5 обрабатываемого сегмента изображения, Двоичный 1-разрядный код приоритета, поступающий на адресный вход демультип- лексора 15, коммутирует сигнал логической единицы, поступающий со входа 48 блока 2

0 на 1-й информационный выход демультип- лексора, где 1 - значение двоичного кода приоритета сегмента изображения. Унитарный код с выходов дёмультиплексора 15 поступает на счетные входы соответствующих

5 триггеров 16i 16n и изменяет их состояние. Двоичный n-разрядный код с выходов триггеров 16i - 1бп поступает на выход 7 блока 2. Учитывая замкнутость контуров изображения в 1-й - n-й плоскости, двоичный код

0 приоритета границ сегментов 1-й плоскости изображения появляется на выходе блока памяти 14 четное количество раз пр и последовательной обработке в каждой строке развертки границ сегментов всех плоско5 стей изображений. Это обусловлено тем, что каждый сегмент изображения имеет левую и правую границу, причем приоритеты левой и правой границы сегмента изображения будут одинаковыми, так как каждый сег0 мент принадлежит только одной определенной плоскости изображения. Значение левой границы сегмента не пре- выша ет значения его правой границы, т.е. в блоке памяти 17 записано по меньшему ад5 ресу. Следователь но, триггер 1б| переключается в единичное состояние при обработке значений левых границ сегментов 1-й плоскости изображения и в нулевое состояние при обработке значений правых

0 границ.

Двоичный m-разрядный код границы сегмента поступает с выхода блока памяти 17 на вход регистра 18 и записывается в него при поступлении с выхода блока 26

5 сравнения через выход 56 блока 3, вход 50 блока 2 на управляющий вход регистра 18 сигнала логической единицы. Двоичный т- разрядный код с выхода регистра 18 поступает на выход 37 блока 2. являющийся выходом границ видимых сегментов.

Двоичный m-разрядный код с выхода 57 блока 2 поступает через вход блока 3, элементы 19i - 19П ИЛИ, на счетные входы; счетчиков 20i - 20П. При обработке левой границы сегмента 1-й плоскости изображе- ния сигнал логической единицы с выхода триггера 16i через 1-й разряд выхода 57, блока 2, входа 55 блока 3, через элемент ИЛИ 19| поступает на счетный вход счетчика 20i. По переднему фронту сигнала логиче- ской единицы увеличивает на единицу значение двоичного кода счетчика номера границы 20|. Таким образом, на выходе счетчика 20 формируется значение адресного кода номера обрабатываемого сегмента в 1-й плоскости изображения. С выхода счетчика 20i код номера обрабатываемого сегмента 1-й плоскости изображения поступает на адресные входы блока памяти 21|. При поступлении выхода 51 блока 3 сигнала ло- гической единицы на управляющие входы блоков памяти 21| - 21П на выходе блока памяти 21 появляется двоичный р-разряд- ный код признака обрабатываемого сегмента 1-й плоскости изображения. С выхода блока памяти 21| двоичный р-разрядный код признака обрабатываемого сегмента 1-й плоскости изображения поступает на первые входы элементов И 24-24.р группы. При обработке значений правых границ сегмен- тов 1-й плоскости изображения триггер 16 переключается в нулевое состояние сигналом логической единицы, поступающим с 1-го выхода демультиплексора 15. Потенциал логического нуля с выхода триггера 16 поступает на счетный вход счетчика 20 аналогично рассмотренному ранее случаю обработки левой границы сегмента. Потенциал логического нуля не изменяет состояния счетчика 20i. Двоичный К-раЗряд- ный адресный код номера обрабатываемого сегмента 1-й плоскости изображения поступает на адресные входы блока памяти 21i до обработки левой границы последующего сегмента 1-й плоскости изображения. Таким образом, в любой момент времени работы устройства на первых входах элементов И24|.1-24|.р группы находится р-разрядный двоичный код признака обрабатываемого сегмента 1-й плоскости изображения.

Группы элементов запрета 23i - 23п-1, ИЛИ 221 - 22п-2 образуют приоритетную цепочку элементов, обеспечивающую выдачу единственного сигнала с выхода триггера 16i на вторые входы элементов И 24и - 24j.p наиболее приоритетной 1-й плоскости изображения, в которой существует сегмент в точке развертки с координатами обрабатываемой границы. При обработке значения левой границы левой границы сегмента 1-й

плоскости изображения триггер 161 устанавливается в единичное состояние. Потенциал логической единицы с прямого выхода триггера 161 поступает на прямой вход элемента запрета 23i-i, где I 2, п и через элементы ИЛИ 22м - 22п-2 поступает на инверсные входы элементов запрета 23i - 23п-1 Таким образом, появление потенциала логической единицы на выходе триггера 16i обуславливает наличие сигнала запрета на инверсных входах элементов запрета 23| - 23п-1. Этим обеспечивается запрет прохождения двоичных кодов признаков сегментов менее при- оритетных (+1)-й - п-1 плоскостей изображений через группы элементов И24|н,1--24п р. ИЛИ 25i-25p на входы блока 26 сравнения и входы регистра 27. Если при обработке значения левой границы сегмента i-й плоскости изображения не существует сегментов более приоритетных плоскостей, то с выходов триггеров 16i- 161-1 потенциал логического нуля поступает через элементы запрета 23i - 23м на вторые входы элементов И 24i,i - 24ы,р и через элементы ИЛИ 22i - 22i-2 на инверсный вход элемента запрета 23ы. Потенциал логической единицы с выхода элемента запрета 23ы поступает на вторые входы элементов 24ij - 24i p, обеспечивая выдачу через элементы ИЛИ 25i -25P двоичного кода признака сегмента наиболее приоритетной плоскости изображения на входы блока 26 сравнения и на входы регистра 27.

При обработке значения правой границы сегмента 1-й плоскости изображения триггер 16i устанавливается в нулевое состояние. Потенциал логического нуля с прямого выхода триггера 16i поступает на прямой вход элемента запрета 23i-i, где i 2,п, и через элементы ИЛИ 22i-i - 22n-2 поступает на инверсные входы элементов запрета 23i - 23п-1. Таким образом, появление сигнала логического нуля на выходе триггера 16i обуславливает появление разрешающего сигнала логического нуля на инверсном входе элемента запрета 23, при отсутствии сегментов изображений более приоритетных плоскостей. Следовательно, потенциал логической единицы на вторые входы элементов И 24j i - 24jp поступит с выхода триггера 16j. где j - наиболее приоритетная из оставшихся плоскость изображения, в которой существует сегмент в точке развертки с координатами обрабатываемой границы, причем j i. Потенциал логической единицы с выхода элемента запрета 23i-i поступает из вторые входы группы элементов И 24j i - 24j p, обеспечивая выдачу через элементы И Л И 25i - 25Р двоичного кода признака сегмента наиболее приоритетной из оставшихся J-1 плоскости изображения на входы блока 26 сравнения и входы регистра 27.

С выхода регистра 27 на входы блока 26 сравнения поступает р-разрядный двоичный код признака границы видимого сегмента изображения, который был определен в предыдущем такте работы устройства, Сравнение кода происходит при поступлении на управляющий вход блока 26 сравнения сигнала логической единицы со входа 54 блока 3, В случае неравенства кодов, поступающих на входы блока 26 сравнения, на выходе блока 26 сравнения формируется сигнал логической единицы, который поступает на вход элемента 28 задержки, на управляющий вход регистра 27 и на выход 56 блока 3. По этому сигналу происходит запись р-разрядного двоичного кода границы видимого сегмента изображения с выхода блока 17 в регистр 27 и т-раз- рядного двоичного кода границы видимого сегмента изображения с выхода блока 17 s регистр 18. Это обусловлено тем, что на выходе элементов ИЛИ 25i -25P появляются признаки только видимых сегментов изображений. Появление сигнала логической единицы на выходе блока 26 сравнения свидетельствует о наличии следующего видимого сегмента изображения. С выходов регистра 27 и регистра 18 двоичный р-разрядный код признака и m-рззрядный код границы видимого сегмента изображения через выходы соответственно признаков 36 и границ 37 устройства выдаются потребителю, причем появление кодов признака и границы видимого сегмента изображения на выходах 36, 37 устройства стробируются импульсом на выходе 35 Таким образом, по мере просмотра левых и правых границ сегментов 1-й и n-й плоскостей изображения в порядке увеличения их значений на информационном выходе признаков сегментов 36 устройства появляются двоичные коды признаков видимых сегментов, а на информа- ционом выходе границ сегментов 37 устройства появляются двоичные коды значений границ видимых сегментов, двоичные коды значений границ видимых сегментов, стробируемых импульсов на выходе 36 устройства.

При поступлении на счетный вход счетчика 10 (2к+1)-го тактового импульса на его выходе переполнения появляется сигнал логической единицы, который элемент 9 ИЛИ поступает на выход 44 блока 1, на вход обнуления счетчика 10 и на вход останова генератора 4. Таким образом, по окончании цикла определения видимых сегментов изображений устройство устанавливается в исходное состояние.

Технико-экономическое преимущество предлагаемого устройства по сравнению с 5 прототипом заключается в повышении быстродействия, которое достигнуто за счет сокращения числа анализируемых элементов тестов видимости точек при формировании видимого изображения, что стало возмож

0 ным за счет того, что в пределах каждого сегмента приоритетной плоскости изображения цвет, яркость не изменяются и упрощение устройства за счет хранения и обработки изображений л приоритетных

5 плоскостей в сжатом виде, при этом уменьшается время цикла обмена информацией внешней ЭВМ с блоками памяти устройства, Это позволяет повысить производительность внешней ЭВМ.

0 Формула изобретения

1. Устройство для формирования видимых сегментов изображений, содержащее блок управления, первый выход которого является выходом сигнала окончания рабо5 ты устройства, выходы первой группы - выходом сигнала номера такта работы устройства, тактовый вход блока управления является входом сигнала разрешения записи устройства, входами сигналов запу0 ска и начальной установки которого являются управляющий и установочный входы блока управления, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства за счет сокращения

5 памяти путем обработки и хранения сегментированных описаний приоритетных плоскостей изображения, оно содержит блок формирования границ видимых сегментов изображения и блок формирования призна0 ков видимых сегментов изображения, информационные входы первой группы которого соединены с выходами первой группы блока формирования границ видимых сегментов изображения, выходы вто5 рой группы которого являются выходами сигналов границ изображения устройства, выходом сигнала признаков которого является первый выход блока формирования признаков видимых сегментов изображе0 ния, второй выход которого является выходом сигналов синхронизации устройства, а третий выход соединен с синхровходом блока формирования границ видимых сег чен- тов изображения, адресные входы которого

5 соединены с выходами первой группы блока управления, второй выход которого подключен к управляющим входам блоков формирования границ видимых сегментов изображения и формирования признаков

видимых сегментов изображения, тактовые входы которых подключены соответственно к третьему и четвертому выходам блока управления, входы установки в начальные состояния - к пятому выходу блока управлений, шестой выход которого соединен с синхровходом блока формирования признаков видимых сегментов изображения, информационные входы второй группы которого являются входами сигналов признаков устройства, входами сигналов приоритетов и границ изображений которого являются информационные входы первой и второй групп блока формирования границ видимых сегментоз изображения.

2.Устройство по п. 1,отличзющее- с я тем, что блок управления содержит генератор тактовых импульсов, вход запуска которого является управляющим входом блока, прямой выход которого соединен с прямым входом первого элемента запрета, первым входом элемента И и счетным входом счетчика, второй вход элемента И и инверсные входы первого и второго элементов запрета являются тактовым входом блока, инверсный выход генератора тактовых импульсов соединен с прямым входом второго злемеита запрета, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого и вход первого .элемента задержки соединен с выходом злемента И, выход первого элемента запрета является четвертым выходом блока, выход первого элемента задержки - третьим выходом блока и подключен к входу второго элемента задержки, выход которого является шестым выходом блока, выход первого элемента ИЛИ соединен с входом третьего элемента задержки, выход которого является вторым выходом блока, выходы группы счетчика являются соответственно выходами первой и второй групп блока, выход переполнения счетчика является пятим выходом блока И подключен к первому входу второго элемента ИЛИ, второй вход которого является установочным входом блока, выход второго злемента ИЛИ является первым выходом блока и соединен с входом сброса счетчика и входом останова генератора тактовых импульсов.

3.Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что блок формирования границ видимых сегментов изображения содержит первый блок памяти, информационные входы которого являются информационными входами первой группы блока, адресные входы - адресными входами блока, соединенными с адресными входами второго блока памяти, информационные входы

которого являются информационными входами второй группы блока, выходы второго блока памяти подключены к информационным входам регистра, выходы которого являются выходами второй группы блока, управлякж ий вход регистра является синхровходом блока, выходы первого блока памяти подключены к адресным входам демультиплексора, информационный вход

0 которого является тактовым входом блока, выходы демультиплексора подключены к счетным входам соответствующих триггеров группы, входы сброса которых и вход сброса регистра являются входом сигнала

5 установки в начальное состояние, выходы триггеров группы являются выходами первой группы блока.

4. Устройство поп. 1,отличающее- с я тем, что блок формирования признаков

0 видимых сегментов изображения содержит первую группу элементов ИЛИ, первые входы которых являются информационными входами первой группы блока, а вторые входы - тактовым входом блока, выходы оле5 ментов ИЛИ группы соединены со счетными входами соответствующих счетчиков группы, входы сброса которых являются входом сигнала установки в начальное состояние блока, выходы счетчиков группы соединены

0 с адресными входами соответствующих блоков памяти группы, информационные входы которых явпяются информационными входами второй группы блока, а управляющие входы - управляющим входом блока,

5 выходы блоков памяти группы соединены с первыми входами элементов И соответствующих групп, вторые входы элементов И первой группы подключены к информационным входам первой группы блока, вторые входы

0 элементов И всех групп, кроме первой подключены к выходам соответствующих элементов запрета группы, прямые входы которых подключены к информационным входам первой группы блока, соединенным

5 с первыми входами элементов ИЛИ второй группы, вторые входы последующего элемента ИЛИ второй фуппы, кроме первого, подключены к выходу предыдущего элемента ИЛИ второй группы, второй вход первого

0 элемента ИЛИ второй группы соединен с информационными входами первой группы блока, выходы элементов ИЛИ второй группы подключены к инверсным входам соот- ветствукж1их элементов запрета группы,

5 кроме первого, инверсный вход которого подключен к информационным входам первой группы блока, выходы элементов И группы подключены к входам соответствующих элементов ИЛИ третьей группы, выходы которых соединены с информационными входзми регистра и информационными входами первой группы блока сравнения, информационные входы второй группы которого подключены к выходам регистра, которые являются первым выходом блока, управляющий вход блока сравнения является синх- ровходом блока, выход блока сравнения

является третьим выходом блока и подключен к входу элемента задержки и управляющему входу регистра, вход сброса которого соединен с входом сигнала установки в начальное состояние блока, выход элемента задержки является вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1429148A2 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1988 |

|

SU1575231A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для формирования сигналов алфавитно-цифровых и графических изображений | 1982 |

|

SU1083406A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| Устройство для отображения информации на экране цветного телевизионного индикатора | 1985 |

|

SU1354243A1 |

| Устройство для реализации логических функций | 1989 |

|

SU1619247A1 |

| Устройство для последовательного программного управления | 1983 |

|

SU1126928A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

Использование: область вычислительной техники, устройство цифровой обработки и формирования изображений на экранах растровых систем отображения. Сущность изобретения: устройство содержит: блок управления, блок формирования границ видимых сегментов изображения, блок формирования признаков видимых сегментов изображения. 4 ил.

30

31

v

39

32

ZJF

33

29i-n

3

А 4

г

2

37 t

ч Л

Фиг./

Фиг

| Устройство для отображения информации на экране телевизионного индикатора | 1983 |

|

SU1149305A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1992-12-30—Публикация

1990-04-04—Подача