2.Устройство по II. 1 , о т л ич а ю 1U е е с я тем, что приорите ный блок содержит группу из П элементов ИЛИ, группу из элементов запрета, шифратор и регистр приоритета, выход которого соединен

с выходом блока, упр-авлягаций. и информационный входы регистра приоритета подключены соответственно к управляющему входу блока и выходу шифратора, первый которого соединен с выходом первого элемента ИЛИ группы, а второй, третий,. (П+1)-й входы шифратора подключены к выходам соот.ветствукщих элементов запрета группы, каждый информационный вход блока соединен с первым входом соответствуквдего элемента ИЛИ группы и прямым входом соответствующего элемента запрета группы, вход запрета которого подключен к выходу последуыцего элемента ИЛИ и к второму входу соответствукхиего элемента ИЛИ группы.

3.Устройство для поворота вектора, содержащее два регистра, два сдвигателя, четыре сумматора, генератор импульсов, блок памяти, блок вычитания, группу пороговых элементов, приоритетный блок, регистр инкрементных прира1-1ений, накапливающий суг-лматор и цифроаналоговый преобразователь, вход и выход которого соединены соответственно с выходом накапливающего сумматора и вычитаюгцим входом блока вычитания, суммиругаций вход, знаковый и информационный выходы которого подключены соответственно к аналоговому входу устройства,- входу приращения накапливагацего сумматора и входам пороговых элементов группы, информационный вход

г. выход накапливающего сумматора соединены соответственно с вьтгкодом per-HCTi-a инкрементных приращений и информационным выходом устройства, f.jax;;.;:,bj пороговых элементов грут -- 1тодключены к соответствуго:цим информационным входам приоритетного блока, выход которого соединен с информационным входом ре1истра инкрементных приращений, первые информационные входы первого и второго регистров подключены соответственно к первому и второму информационным входам устройства, вторые информационные входы первого и второго регистров соединены с выходами соответственно первого и второго сумматоров, выход первого регистра подключен к первым информационным входам первого и третьего сумматоров и первому Еьжоду кода координат устройства, а выход второго регистра к первьлм информационным входам второго и четвертого сумматоров и второму выходу кода координат устройства, вторые информационные входы третьего и четвертого сумматоров соединены с выходами соответственно первого и второго сумматоров, информационные входы и выходы первого и второго сдвигателей подключены соответственно к выходам третьего и четвертого сумматоров и вторым информационным входам второго и первого сумматоров, отличающее ся тем, что, с целью повьиения его быстродействия, введены счетчик, два шифратора, триггер, два элемента И, элемент запрета, сумматор по модулю два и дешифратор нуля, выход которого соединен с информационным входом триггера, установочный вход и выход которого подключены соответственно к запускающему входу устройства и первьвд входам первого и второго элементов И, запускающий вход устройства соединен с входом установки о накапливающего сумматора, прямым входом элемента запрета, первыми управляющими входами первого и второго регисров и входом генератора импульсов, первый, второй и третий выходы которого подключены соответственно к второму входу второго элемента И, тактируквдему входу триггера и инверсному входу элемента, выход которого соединен с вторыми управляющими входами первого и второго регстров, выход второго элемента И подключен к тактируквдим входам блока вычитания, регистра инкременных приращений и г«акапливан1дего сумматора, второй вход и выход первого элемента И соединены соответственно с вторым выхрдом генератора импульсов и синхровходом счетчика, выход регистра инкрементных приращений подключен к входам первго и второго шифраторов, синхровхо информационный вход и выход счетчика соединены соответственно с третим выходом генератора импульсов, выходом второго шифратора и входом дешифратора нуля, первый и второй адресные входы и первый и второй иформационные выходы блока памяти подключены соответственно к выходу счетчика, выходу nepgoro шифратора управляющим входам первого и второго сдвигателей и первому входу сумматора по модулю два, второй вход и выход которого соединены соответственно с знаковым выходом блока вычитания и управлякщими входами первого и второго сумматоров.

Изобретение относится к вычислительной технике и может быть использовано в управлягацих и моделируидих устройс гвах как общего, так и специального назначения.

Поворот векторов и координат используется во многих задачах управления и моделирования с применением реальной аппаратуры. При этом угол поворота часто снимается с датчиков в аналоговой форме, в то время как координаты объекта представлены в ЦВМ в цифровой форме.

Известно аналого-цифровое устройство для поворота вектора, которое содержит два сумматора, элемент ИЛИ, четыре группы элементов И, реверсивный счетчик, два регистра, схему сравнения и другие вспомогательные элементы, причем аргумент, -представленный в аналоговой форме, посредством схемы сравнения и реверсивного счетчика отспеживается с Ломированием элементарных приращений, используемых для поворота вектора по методу решения на цифровых дифференциальных анализаторах (ЦДА) определяющих систем дифференциальных уравнений ij .

Недостатки данного устройства низкие точность и быстродействие, присущие методам вычисления посредством ЦДА.

Известно цифровое устройство для поворота вектора, содержащее три регистра, два блока сдвига, семь сумматоров, блок памяти и блок управления, причем соединения между блоками выполнены по схеме, реализугадей алгоритм Волдера с коррекцией результата. Если аргумент представлен в аналоговой форме то последовательно с входом третьего регистра необходимо подключить аналго-цифровой преобразователь 2 . i Недостатки указанного устройства состоят в больших аппаратурных затртах и малом быстродействии, обусловленном необходимостью выполнения большого количества итераций для каждого изменяющегося значения аргумента.

Наиболее близким к предлагаемому является устройство, содержащее последовательно включенные стандартный аналого-цифровой преобразователь следящего типа, цифровое устройство для поворота вектора, три регистра, пять сумматоров, два блока сдвига, блок памяти, блок анализа состояния, набор пороговых элементов, логический блок, цифроаналоговый преобразователь и накапливающий сумматор, причем аналого-цифровой преобразователь преобразовывает аналоговый аргумент

в цифровой код, после чего ocyinecвляется поворот вектора каждый ра из начального состоя ния на заданн величину аргумента .

Недостатком известного устройства является низкое быстродействие, обусловленное наличием многошагового итерационного процесса .при повороте вектора из исходного состояния в заданное.

Цель изобретения - повычение бродействия .

Поставленная цель достигается тем, что по первому варианту в усройстве, содержащем два регистра, два сдвигателя, четыре сумматора, генератор импульсов, блок памяти, блок вычитания, группу пороговых элементов, приоритетный блок, накапливакщий сумматор и цифроаналоговый преобразователь, вход и выход которого соединены соответств но с выходом накапливающего сумматора и вычитакхдим входом блока вычитания, суммирующий вход, тактирующий вход, знаковый и информационный выходы которого подключены соответственно к аналоговому входу устройства, выходу генератора импульсов, входу приращения накапливакадего сумматора и входам пороговых элементов группы, тактирукщий вход и выход накапливающ€-го сумматора соединены соответственно с выходом генератора импульсов и информационным выходом устройства, выходы пороговых элементов группь- подключены к соответствующим инфор-, мационным входам приоритетного блока, управляющий вход которого соединен с выходом генератора импульсов, первые информационные входы первого и второго регистров подключены соответственно к первому и второму информационным вхсдам устройства, вторые информационные входы первого и второго регистров соединены с выходами соответственно первого и второго сумматоров, выход первого регистра подключен к первым информационным входам первого и третьего сумматоров и первому выходу кода координат устройства, а выход второго регистра - к первым информационным входам второго и четвертого сумматоров и второму выходу кода координат устройства, вторые информационные входы третьего и четвертого сумматоров соединены с выходами соответственно первого и второго сумматоров, информационные входы и выходы первого и второго сдвигателей подключены соответственно к выходам

третьего и четвертого сумматоров и вторым информационным входам втрого и первого сумматоров, запускщий вход устройства соединен с вхдом генератора импульсов, входом установки о накапливакиего сумматора и первьлми управлякичими входами первого и второго регистров, вторые управля1шдие входы которых подключены к выходу генератора импульсов, выход приоритетного блка соединен с управляющими входами первого и второго сдвигателей и адресным входом блока памяти, вход которого подключен к ин(ормационному входу накапливагацего сумматора, а управляющие входы первого и второго сумматоров соединены со знаковым выходом блока вычитания.

Кроме того, приоритетный блок ссдержит группу из п элементов ИЛИ, группу из Я элементов запрета, шифратор и регистр приоритета, выход которого соединен с выходом блока, управлягаций и информционный входы регистра приоритета подключены соответственно к управляющему входу блока и выходу шифратора, первый вход которого соединен о выходом первого элемента ИЛИ группы, а второй, третий, ... (п+1)-й входы шифратора подключены к выходам соответствующих элементов запрета группы, каждый информационный вход блока . соединен с первым входом соответствукщего элемента группы и прямым входом соответствующего элемента запрета группы, вход запрета которого подключен к выходу : лследук1цего элемента ИЛИ и второму входу соответствующего элемента ИЛИ группы.

По второму варианту в устройство содержащее два регистра, два сдвигателя, четыре сумматора, генератор импульсов, блок памяти, блок вычитания, группу пороговых алиментов, приоритетный блок, регистр инкрементных прира1,ений , накапг;:-1ваю:яий сумматор и цифроаналоговый преобразователь, вход и выход которого соединены соответственно с выходом накапливаюгцего сумматора и вычитающим входом блока вычитания, суммирующий вход, знаковый и информационный выходы которого подключены соответственно к аналоговому входу устройства, входу приращения накапливающего cyi-vCvsaTOpa и вхо-.. дам пороговых элементов группы, информационный вход и выход на-., капливающего cy tмaтopa соединены соответственно с выходом регистра инкрементных приращений и информационным выходом устройства, выходы пороговых элементов группы подключены к соответствуганим информационным входам приоритетного блока, выход которого соединен с информационным входом регистра инкрементных приращений первые информационные входы первого и второго регистров подключены соответственно к первому и второму информационным входам устройства, вторые информационны входы первого и второго регистров соединены с выходами соответственно первого и второго сумматоров, выход первого регистра подключен к первым информационным входам первого и третьего сумматоров и первому выходу кода координат устройства, а выход второго регистра - к первь1М информационным входам второго и четвертого сумматоров и второму выходу кода координат устройства вторые информационные входы третего и четвертого сумматоров соединены с выходами соответственно первого и второго сумматоров, информационные входы и выходы первого и второго сдвигателей подключены соответственно к выходам третьего и четвертого сумматоров и вторым информационным входам второго и первого сумматоров, дополнительно введены счетчик, два шифратора, триггер, два элемента И, элемент запрета, сумматор по модулю два и дешифратор нуля, выход которого соединен с информационным входом триггера, устанвочный вход и выход которого подключены соответственно к запускащему входу устройства и первым входам первого и второго элементов И, запускающий вход устройства соединен с входом установки накапливающего сумматора, прямым входом элемента запрета, первыми управляющими входами первого и второго регистров и входом генератора импульсов, первый, второй и третий выходы которого подключены соответственно к второму входу второго элемента И, тактирующему входу триггера и инверсному входу элемента запрета, выход которого соединен с вторыми управляющими входами первого и второго регистров, вьбсод второго элемента И подключен к тактирующим входам блока вычитания, регистра инкрементных приращений и накапливающего сумматора, второй вход и выход первого элемента И соединены соответственно с вторым выходом генератора импульсов и синхровходом счетчика, выход регистра инкрементных приращний подключен к входам первого и второго шифраторов, синхровход, информациейHbrii вход и выход счетчика соединены соответственно с третьим выходом генератора импульсов, выходом второго шифратора и входом дешифратора нуля, первый и второй адресные входы и первый и второй информационные выходы блока памяти подключены соответственно к выходу счетчика, выходу первого и ифратора, управляющим входам первого и второго сдвигателей и первому входу сумматора по модулю два, второй вход и врзгход которого соединены соответственно со знаковым выходом блока вычитания и управлякадими входами первого и второго сумматоров.

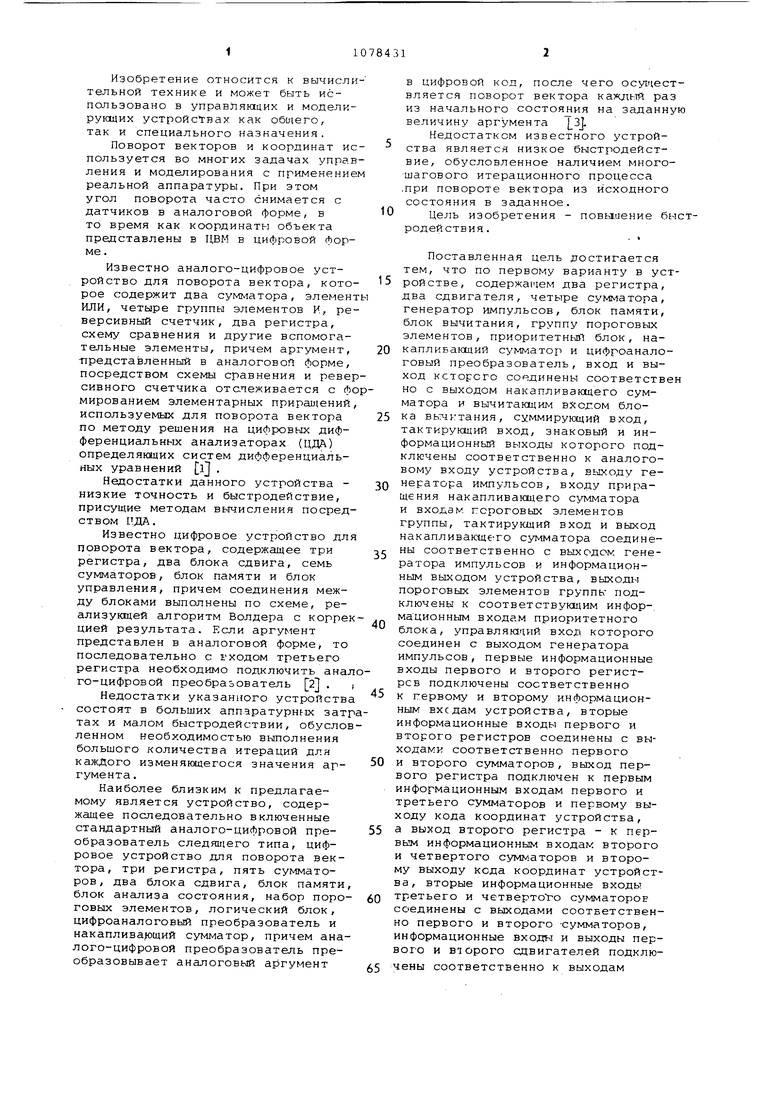

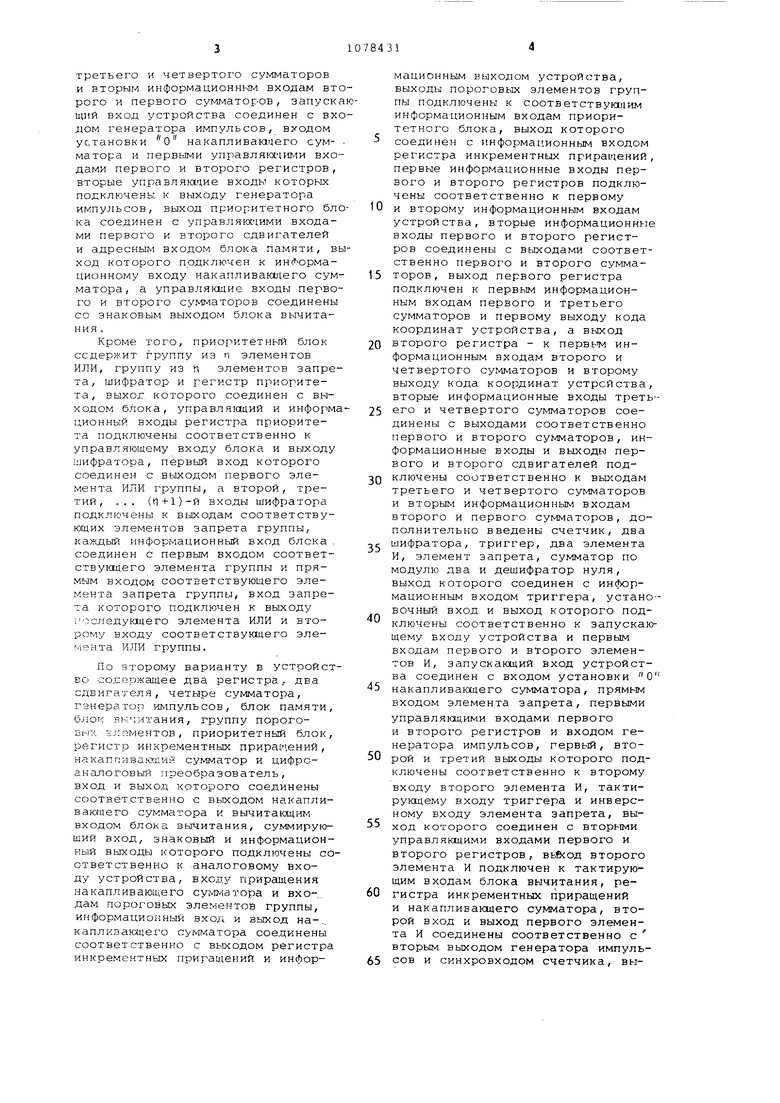

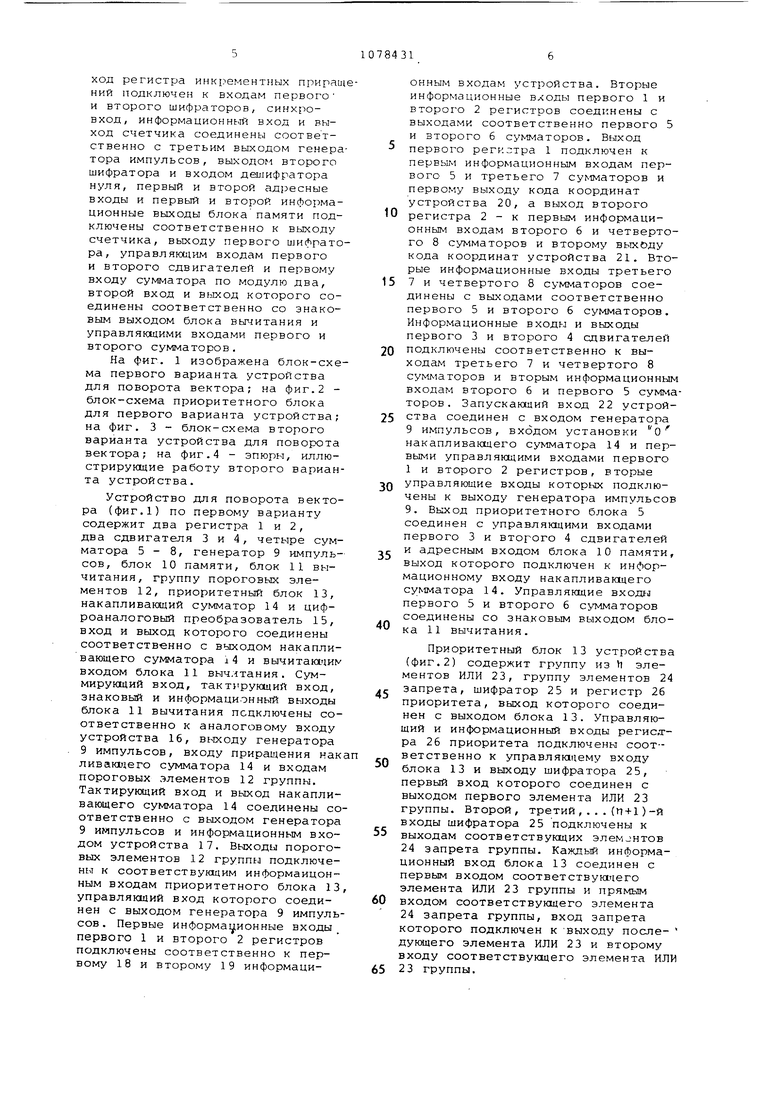

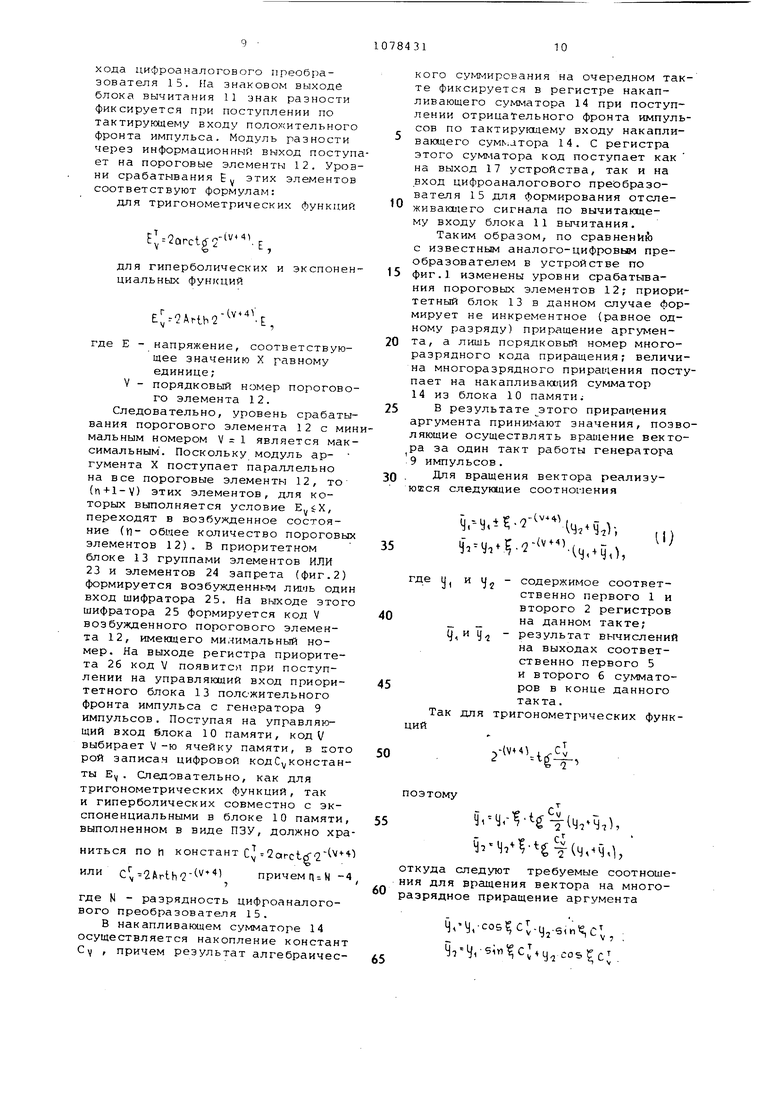

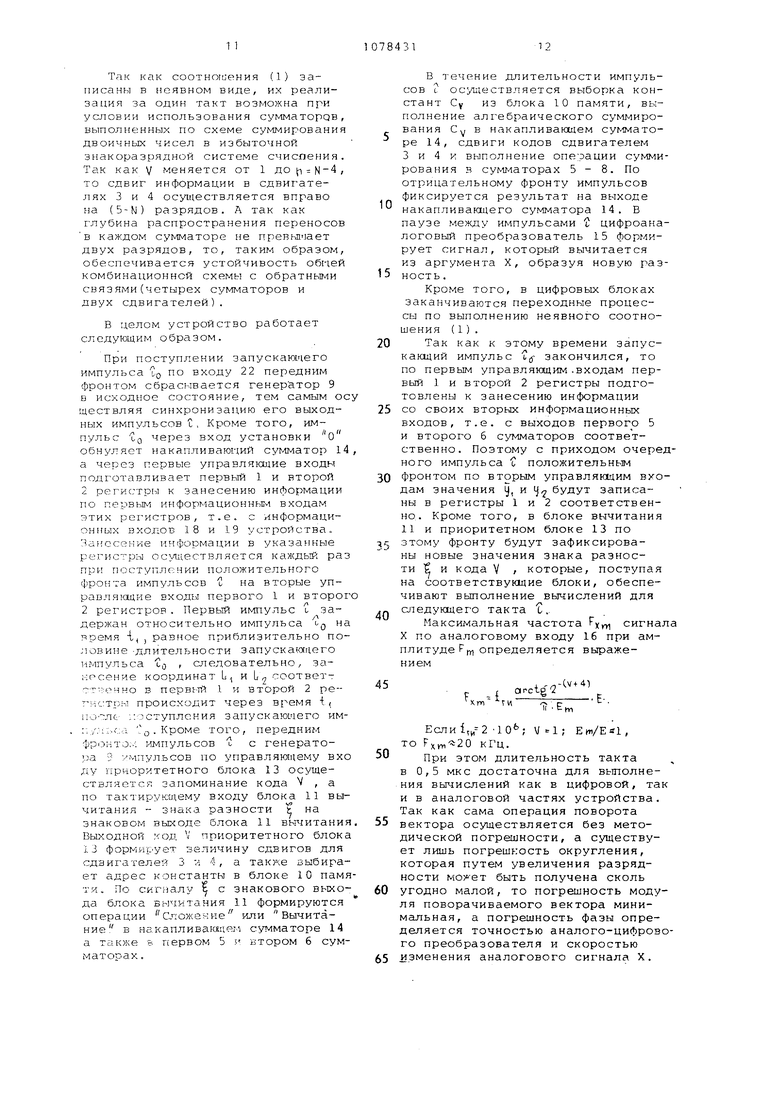

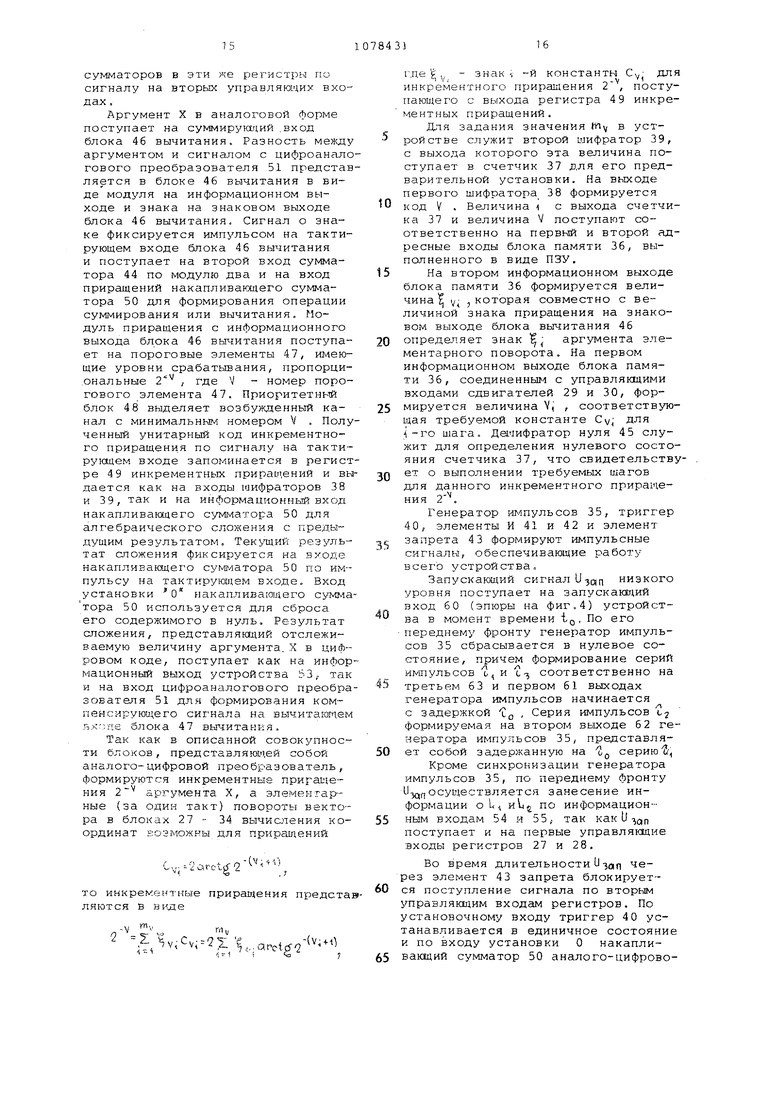

На фиг. 1 изображена блок-схема первого варианта устройства для поворота вектора; на фиг.2 блок-схема приоритетного блока для первого варианта устройства; на фиг. 3 - блок-схема второго варианта устройства для поворота вектора; на фиг.4 - эпюры, иллюстриругацие работу второго варианта устройства.

Устройство для поворота вектора (фиг.1) по первому варианту содержит два регистра 1 и 2, два сдвигателя 3 и 4, четыре сумматора 5-8, генератор 9 импульсов, блок 10 памяти, блок 11 вычитания, группу пороговых элементов 12, приоритетный блок 13, накапливающий сумматор 14 и цифроаналоговый преобразователь 15, вход и выход которого соединены соответственно с выходом накапливающего сумматора а4 и вычитагатшу входом блока 11 вычлтания. Суммируюций вход, тактирующий вход, знаковый и информационный выходы блока 11 вычитания подключены соответственно к аналоговому входу устройства 16, выходу генератора 9 импульсов, входу приращения нак ливаюидего сумматора 14 и входам пороговых элементов 12 группы. Тактирующий вход и выход накапливающего сумматора 14 соединены соответственно с выходом генератора 9 импульсов и информационным входом устройства 17. Выходы пороговых элементов 12 группьл подключены к соответствугещим информаицонным входам приоритетного блока 13 управлякший вход которого соединен с выходом генератора 9 импульсов. Первые информа1 ионные входы первого 1 и второго 2 регистров подключены соответственно к первому 18 и второму 19 информационным входам устройства. Вторые информационные входы первого 1 и второго 2 регистров соединены с выходами соответственно первого 5 и второго б сумматоров. Выход первого регк.гтра 1 подключен к первыг 1 информационным входам первого 5 и третьего 7 сумматоров и первому выходу кода координат устройства 20, а выход второго регистра 2 - к первЕлм информациOHHfcJM входам второго 6 и четвертого 8 сумматоров и второму выходу кода координат устройства 21. Вторые информационные входы третьего 7 и четвертого 8 сумматоров соединены с выходами соответственно первого 5 и второго 6 сумматоров. Информационные входы и выходы первого 3 и второго 4 сдвигателей подключены соответственно к выходам третьего 7 и четвертого 8 сумматоров и вторым информационным входам второго б и первого 5 сумматоров. Запускакхций вход 22 устройства соединен с входом генератора 9 импульсов, входом установки Q накапливаквдего cyNiMaTOpa 14 и первыми управляющими входами первого 1 и второго 2 регистров, вторые управляющие входы которых подключены к выходу генератора импульсов 9. Вьжод приоритетного блока 5 соединен с управлягацими входами первого 3 и второго 4 сдвигателей и адресным входом блока 10 памяти выход которого подключен к информационному входу накапливакадего сумматора 14. Управлякщие входьл первого 5 и второго б су-мматоров соединены со знаковым выходом блока 11 вычитания.

Приоритетный блок 13 устройства (фиг. 2) содержит группу из Vi элементов ИЛИ 23, группу элементов 24 запрета, шифратор 25 и регистр 26 приоритета, выход которого соединен с выходом блока 13. Управляющий и информационный входы регислгра 26 приоритета подключены соот-ветственно к управляющему входу блока 13 и выходу шифратора 25, первый вход которого соединен с выходом первого элемента ИЛИ 23 группы. Второй, третий ,... (n-t-l)-и входы шифратора 25 подключены к выходам соответствующих элементов 24 запрета группы. Каждьзй информационный вход блока 13 соединен с первым входом соответствунхцего элемента ИЛИ 23 группы и прямым входом соответствующего элемента 24 запрета группы, вход запрета которого подключен к выходу последующего элемента ИЛИ 23 и второму входу соответствукщего элемента ИЛ 23 группы.

Пред.утагаемое устройство для поворота вектора по второму варианту (фиг.З) содержит два регистра 27 и 28, два сдвигателя 29 и 30, четыре cyNiMBTOpa 31 - 34, генератор 35 импульсов, блок 36 памяти, счегчик 37, два и ифратора 38 и 39, три гер 40, два элемента И 41 и 42, элемент 43 запрета, сумматор 44 по модулю два, дешифратор 45 нуля, блок 46 вычитания, группу пороговых элементов 47, приоритетный блок 48, регистр- 49 инкрементных приращений, накапливакишй сумматор 50 и цифроаналоговый преобразователь 51, вход и выход которого соединены соответственно с виходом накапливающего cy 1мaтopa 50 и вычитающим входом блока 46 вычитания. Суммирующий вход, знаковьгй и информационный выходы блока 46 вычитания подключены соответственно к аналоговому входу 52 устройства, входу приращения накапливающего сумматора 50 и входам пороговьк элементов 47 группы. Информационный вход и выход накапливаю1цего сумматора 50 соединены соответствено с выходом, регистра 49 инкрементных приращений и информационным выходом 53 устройства. Выходы пороговых элементов 47 группы подключены к соответствующим информационным входам приоритетного блока 48, выход которого соединен с информационным входом регистра 49 инкрементных приращений. Первые информационные входы первого 27 и второго 28 регистров подключены соответственно к первому 5 и iiTOpOMy 55 информационны -/ входам устройства. Вторые информацион: ые входы первого 27 и второго 28 /регистров соединены с выходами соответственно первого 31 и второго 32 сумматоров. Выход первого регистра 27 подключен к первым инфОрМиЗ-уионным входам первого 31 и третьего 33 сумматоров и первому 56 кода координат устройства, а выход второго регистра 28 к- первым информационным входам втоpoio 32 и четвертого 34 су маторов

и второму выходу 57 кода координат устройства. Вторые информационные входы третьего 33 и четвертого 34 сумматоров соединены с в ходами соответственно первого 31 и второго 32 сумматоров. Информационные входы и вьгходы первого 29 и второго 30 сдЕигате/гей подключены соответственно к выходам третье

го 33 и четвертого 34 сумматоров и вторым информационным входам второго 32 и парвого 31 сумматоров Выход 58 дешифратора куля 45 соединен с информационным входом триггера 40, установочный вход и выход 59 которого подключены соответственно к запускающему входу 60 устройства и первым входам первого 41 5 и второго 42 элементов И. Запускающий вход 60 устройства соединен с входом установки о накапливающего сумматора 50, прямым входом элемента 43 запрета, первьлми уп0 равлякщими входами первого 27 и

второго 28 регистров и входом генератора 35 импульсов, первый 61, второй 62 и третий 63 выходы которого подключены соответственно

5 к второму входу второго элемента И 42, тактирующему входу триггера 40 и инверсному входу элемента запрета 43, выход которого соединен с вторыми управлякцими входами

0 первого 27 и второго .28 регистров. Выход 64 второго элемента И 42 подключен к тактиругацим входам блока 46 вычитания, регистра 49 инкрементных приращений и накапливаквдего

5 сумматора 50. Второй вход и выход 65 первого элемента И 41 соединены соответственно с вторым выходом 62 генератора 35 импульсов и синхровходом счетчика 37. Выход регистQ ра инкрементных прираьпений подключен к входам первого 38 и второго 39 шифраторов. Счетный вход, информационный вход и выход счетчика 37 соединены соответственно с

третьим выходом 63 генератора импульсов 35, выходом второго шифратора 39 и входом деижфратора 45 нуля. Первый и второй адресные входы и первый и второй информационные выходы блока 36 памяти подключены соответственно к выходу счетчика 37, выходу первого шифратора 38, управлякщим входам перво-: го 29 и второго 30 сдвигателей и первому входу сумматора 44 по модулю два, второй вход и выход которого соединены соответственно со знаковым выходом блока 46 вычитания и управля1Ш1ими входами первого 31 и второго 32 сумматоров.

Устройство по первому варианту

работает следующим образом.

Задают в цифровой форме координаты L и 1,2 исходного вектора на информационных входах 18 и 19 устройства (фиг.1), аргумент X на аналоговом входе 16 и запускакишй сигнал tg на запускагачем входе 22 и после времени отслеживания результаты на выходе 17 и выходах 20 и 21 кода координат устройства в каждом такте работы генератора 9 импульсов.

В блоке вычитания 11 определяется разность между аналоговым значением , аргумента X и напряжением с выхода цифроаналогового преобразователя 15. На знаковом выходе блока, вычитания 11 знак разности фиксируется при поступлении по тактирующему входу положительного фронта импульса. Модуль разности через информационный выход поступает на пороговые элементы 12. Уровни срабатывания Е этих элементов соответствуют формулам:

для тригонометрических функций

-(и 41

«о

для гиперболических и экспоненциальнЕзК функций

E Artb2- 4,

где Е - напряжение, соответствующее значению X равному единице;

V - порядковый номер порогового элемента 12.

Следовательно, уровень срабатывания порогового элемента 12с минмальным номером V 1 является максимальным. Поскольку модуль ар- гумента X поступает параллельно на все пороговые элементы 12, то (n+1-V) этих элементов, для которых выполняется условие E,i-X, переходят в возбужденное состояние (ц- общее количество пороговых элементов 12), В приоритетном блоке 13 группами элементов ИЛИ 23 и элементов 24 запрета (фиг.2) формируется возбужденньм ли1чь один вход шифратора 25. На выходе этого шифратора 25 формируется код V возбужденного порогового элемента 12, имеющего минимальный номер. На выходе регистра приоритета 26 код V появится при поступлении на управляющий вход приоритетного блока 13 положительного фронта импульса с генератора 9 импульсов. Поступая на управляющий вход блока 10 памяти, код V выбирает V-ю ячейку памяти, в кото рой записан цифровой кодС константы Еу. Следовательно, как для тригонометрических функций, так и гиперболических совместно с экспоненциальными в блоке 10 памяти, выполненном в виде ПЗУ, должно храниться по h констант С 2arctd2 или C -2Arth2 причем п-И -4

где N - разрядность цифроаналогового преобразователя 15.

В накапливающем сумматоре 14 осуществляется накопление констант Су , причем результат алгебраического суммирования на очередном такте фиксируется в регистре накапливающего сумматора 14 при поступлении отрицательного фронта импульсов по тактирующему входу накапливающего cyMN.aTopa 14. С регистра этого сумматора код поступает как на выход 17 устройства, так и на вход цифроаналогового преобразователя 15 для формирования отслеживакщего сигнала по вычитающему входу блока 11 вычитания.

Таким образом, по сравнению с известным аналого-цифровым преобразователем в устройстве по

фиг.1 изменены уровни срабатывания пороговых элементов 12; приоритетный блок 13 в данном случае формирует не инкрементное (равное одному разряду) приращение аргумента, а лишь порядковый номер многоразрядного кода приращени.я; величина многоразрядного приращения поступает на накапливаюсций сумматор 14 из блока 10 памяти;

В результате этого приращения

аргумента принимают значения, позволяющие осуществлять вращение вектора за один такт работы генератора 9 импульсов.

. Для вращения вектора реализуюшся следующие соотно1- ения

-Cv-t4

г-у,.д.)-,

УVУ..,.ЧO,

у, и у

содержимое соответственно первого 1 и второго 2 регистров на данном такте; (и у - результат вычислений на выходах соответственно первого 5 и второго 6 сумматоров в конце данного такта. ак для тригонометрических функ2- U %-,

поэтому

y..,),

.4.4T(,b откуда следуют требуемые соотношения для вращения вектора на многоразрядное приращение аргумента

Ч,у,,.у.в,, .

47,. .

Так как соотноп;ения (1) записаны в неявном виде, их реализация за один такт возможна при условии использования сумматоров, выполненных по схеме суммирования двоичных чисел в избыточной знакоразрядной системе счисления. Так как V меняется от 1 до fj-4 , то сдвиг информации в сдвигателях 3 и 4 осуществляется вправо на (5-М) разрядов. А так как глубина распространения переносов в каждом сумматоре не превы1 ает двух разрядов, то, таким образом, обеспечивается устойчивость обпей комбинационной схемы с обратными связями (четырех сут 1маторов и двух сдвигателей).

В целом устройство работает следующим образом.

При поступлении запускакхчего импульса I-Q по входу 22 передним фронтом сбрасывается генератор 9 в исходное состояние, тем самым ос ществляя синхронизацию его выходных импульсов I. Кроме того, импульс IQ через вход установки о обнуляет накапливающий cy -lмaтop 14 а через первые управляющие входы подготавливает первый 1 и второй 2 регистры к занесению информации по первым информационньы входам этих регистров, т.е. с информационных входов 18 и 19 устройства. Занесение информации в указанные регистры осуи1ествляется каждый; раз при поступлении положительного фронта импульсов L на вторые управлягацие входы первого 1 и второг 2 регистров . Первый импульс L задержан относительно импульса ьд на время : J равное приблизительно половине -длительности запуска ощего импульса LQ , следовательно, закосение координат Ь, и L, соответгт-;рчно в первьпЧ 1 и втЪрой 2 ре--ис:тры происходит через время i 110-:л& :: затупления запускающего имг,/;:v.f:-;; , .Кроме того, передним Фр|Энто:.-. импульсов 1 с генерато;.за 9 умпульсов по управляющему вхо ду приоритетного блока 13 осуществляется запоминание кода V , а по тактирующему входу блока 11 вычитания - знака разности на знаковом выходе блока 11 вычитания Выходной код V приоритетного блока 13 формиг-ует Гзеличину сдвигов для сдвигателея 3 л 4 , а такке выбирает адрес константы в блоке 10 памятя. По сигналу с знакового выхода блока вычитания 11 формируются операции Сложение или Вычитание в накапливанвдем сумматоре 14 а также в первом 5 и втором 6 сумматооах.

в течение длительности импульсов с осуществляется выборка констант Су из блока 10 памяти, выполнение алгебраического суммирования Су в накапливающем сумматоре 14, сдвиги кодов сдвигателем 3 и 4 и выполнение операции суммирования в cyMj-iaторах 5 - В. По отрицательному фронту импульсов фиксируется результат на выходе накапливагоцего сумматора 14. В паузе между импульсами 1) цифроаналоговый преобразователь 15 формирует сигнал, который вычитается из аргумента X, образуя новую разность .

Кроме того, в цифровых блоках заканчиваются переходные процессы по выполнению неявного соотношения (1) .

Так как к этому времени запускающий импульс if закончился, то по первым управляющим.входам первьлй 1 и второй 2 регистры подготовлены к занесению информации со своих вторых информационных входов, т.е. с выходов первого 5 и второго 6 сумматоров соответственно. Поэтому с приходом очереного импульса С положительным фронтом по вторым управлягадим входам значения у, и у будут записаны в регистры 1 и 2 соответственно. Кроме того, в блоке вычитания 11 и приоритетном блоке 13 по этому фронту будут зафиксированы новые значения знака разности и кода V ; которые, поступая на соответствуидие блоки, обеспечивают выполнение вычислений для следугадего такта С.,

Максимальная частота сигна X по аналоговому входу 16 при амплитуде Ffy| определяется выражением

-CVi41

tg2

arc

;и

1 Ek

Если 15,2 Еж/Е, то кГц.

При этом длительность такта в 0,5 МКС достаточна для выполнения вЕлчислений как в цифровой, так и в аналоговой частях устройства. Так как сама операция поворота вектора осуществляется без методической погрешности, а существует лишь погрешкость округления, которая путем увеличения разрядности может быть получена сколь угодно малой, то погрешность модуля поворачиваемого вектора минимальная, а погрешность фазы определяется точностью аналого-цифрового преобразователя и скоростью 5 изменения аналогового сигнала X.

Таким образом zyin обработки одного значения угла поворота XJ с аналого-цифрового преобразователя в предлагаемом устройстве требуется один такт работы устройств а в прототипе от 1 до W тактов, т.е. в среднем BNt(2 раз болыое (где N разрядность цифроаналогового преобразователя), а следовательно, и частотный диапазон сигнлов по аналоговому входу X для прлагаемого устройства будет во столько же раз шире, чем для прототипа .

Запаздывание информации в предлагаемом устройстве составляет 2 такта (1 такт в блоках аналогоцифрового преобразования и 1 такт в блоках для цифрового поворота вектора), а в прототипе это запаздывание является переменной величинорЧ и изменяется в пределах от (-|+1) до (Jj+N) тактов { - тактов для аналого-цифрового преобразования и (1 -N ) тактов для поворота вектора), следовательно, оперативность предлагаемого устройства для поворота вектора примерно в (4 Т f Bbiuje, чем пртотипа .

Аппаратурные затраты в предлагаемом устройстве значительно меньше, так как в нем по сравнению с прототипом исключены регист сумматор, блок управления и блок анализа, что составляет от общего объема оборудования.

В качестве базового устроПства принимают устройство для поворота вектора, построенное на цифровых дифференциальных анализаторах типа Метеор-4 с аналого-цифровым преобразователем следящего типа. Цифровые дифференциальные анализаторы интегрируют по простейшей формуле прямоугольников, поэтому в таком устройстве имеются большие противоречия между точностью и быстродействием, так как для повышения точности требуется уменьшение шага интегрирования, что приводит к значительному увеличению времени поворота вектора и снижению частотного диапазона устройства.

В предлагаемом устройстве, операция поворота вектора осугчествляется без методической погрешности и шаг интегрирования без увеличения погрешности может быть в сотни раз больше, чем в базовом устройстве, что и обеспечивает предлагаемому устройству значительно более высокую точность поврота вектора и быстродействие

при соизмеримых с базовым устройством аппаратурных затратах.

Последовательность работы устройства по второму варианту (фиг.З) состоит в задании в цифровой форме координат Lj и ( ксу опного вектора на информационнь входах 54 и 55 устройства, задании аргумента X .на аналоговом входе 52, задании запускающего сигнала на запускаютем входе 60 и снятии после времени отслеживания результатов на выходах 53, 56 и 57 устройства.

В блоках 27 - 34 вычисляются координаты вектора в соответствии 5 с соотношениями

,,r4, 4-2100, и.., У.,Лу,,,„,

гдеи .ии,, - содержимое соответствен но первого 27 и второго

28регистров на теку5 щем 4-м такте;

U-,. иу г значения на выходах соч) ответственно первого 31 и второго 32 суммаTcjpOB ;у-4И конце i - го такта; 2 - коэффициенты, формируемые блоками сдвига

29и 30;

;- величина знака (41 или -1), поступающая на управляю ше сумматоров 31 и 32, Все сумматоры 31 - 34 вьтолнены по схеме суммирования чисел в избыточной двоичной знакоразрядной системе счисления, поэтому соот0 ношения (1) вычисляются за один такт, поскольку ограниченная глубина распространения переносов второго разряда обеспечивает устойчивость вычислений при V, 4 . 5 Представив коэффициенты 2-CV,+) в виде

,

50 где Су- - некоторая константа, на выходах первого 31 и второго 32 сумматоров в конце такта будет получено

Ju.),t,py,,Cvi -,

1 7 ,,) j,-5i,.co5,

ЧТО соответствует повороту вектор

на угол 5, С V, .

Исходная информация о координатах L, и Lj заносится в регистры 27 и 28 по сигналу на первых управлякхдих входах этих регистров , а результаты вычислений заносятся с

сумматоров в эти же регистры по сигналу на вторых управляющих входах .

Аргумент X в аналоговой форме поступает на суммируквшй .вход блока 46 вычитания. Разность меищу аргументом и сигналом с цифроансшогового преобразователя 51 представляется в блоке 46 вычитания в виде модуля на информационном выходе и знака на знаковом выходе блока 46 вычитания. Сигнал о знаке фиксируется импульсом на тактирующем входе блока 46 вычитания и поступает на второй вход сумматора 44 по модулю два и на вход приращений накапливающего сумматора 50 для формирования операции суммирования или вычитания. Модуль приращения с информационного выхода блока 46 вычитания поступает на пороговые элементы 47, имеющие уровни срабатывания, пропорци.ональные 2 , где V - номер порогового элемента 47. Приоритетный блок 48 выделяет возбужденный канал с минимальным номером V . Полученный унитарный код инкрементного приращения по сигналу на тактирующем входе запоминается в регистре 49 инкрементных приращений и выдается как на входы шифраторов 38 и 39, так и на информационный вход накапливающего cyм 1aтopa 50 для алгебраического сложения с предыдущим результатом, результат сложения фиксируется на входе накапливающего су№латора 50 по импульсу на тактируюашм входе. Вход установки о накапливастдего сумматора 50 используется для сброса его содержимого в нуль. Результат сложения, представлявший отслеживаемую величину аргумента. X в цифровом коде, поступает как на информационный выход устройства 53,, так и на вход цифроаналогового преобразователя 51 для формирования компенсирующего сигнала на вычитающем . блока 47 вычитания.

Так как в описанной совокупности блоков, представляюи.ей собой аналого-цифровой преобразователь, формируются инкрементные пригак ения аргумента X, а элементарные (за один такт) повороты векто-ра в блоках 27 - 34 вычисления координат Еозможкы для приращений

C,,.2a.,

то инкрементные прирап1ения предсталяются в в иле

,,Cvi 2Z . nn.(

- V;.Cii ctd-2

n - 1 t S3

где ,, - знак -, -и константы для инкрементного приращения 2 , поступающего с врыхода регистра 49 инкрементных приращений.

Для задания значения гл в уст5 ройстве служит второй шифратор 39, с выхода которого эта величина поступает в счетчик 37 для его предварительной установки. На выходе первого шифратора 38 формируется

0 код V . Величина i с выхода счетчика 37 и величина V поступают соответственно на первый и второй адресные входы блока памяти 36, выполненного в виде ПЗУ,

5 На втором информационном выходе блока памяти 36 формируется величина V, , которая совместно с величиной знака приращения на знаковом выходе блока вычитания 46

0 определяет знак аргумента элементарного поворота. На первом информационном выходе блока памяти 36, соединенным с управлягацими входами сдвигателей 29 и 30, фор5 мируется величина Vj , соответствующая требуемой константе Су; для i-го шага. Де1чифратор нуля 45 служит для определения нулевого состояния счетчика 37, что свидетельствуQ ет о выполнении требуемых шагов

для данного инкрементного прира1чения 2,

Генератор шшульсов 35, триггер 40, элементы И 41 и 42 и элемент

е: запрета 43 формируют импульсные сигналы, обеспечивающие работу всего устройства,.

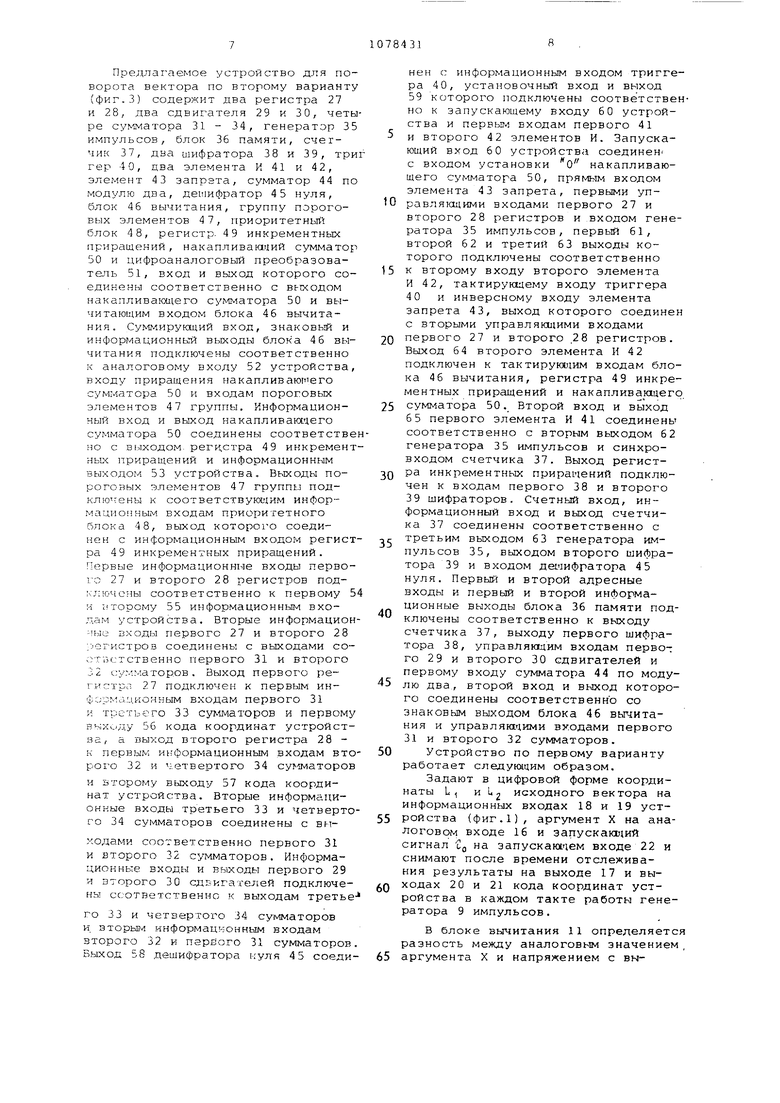

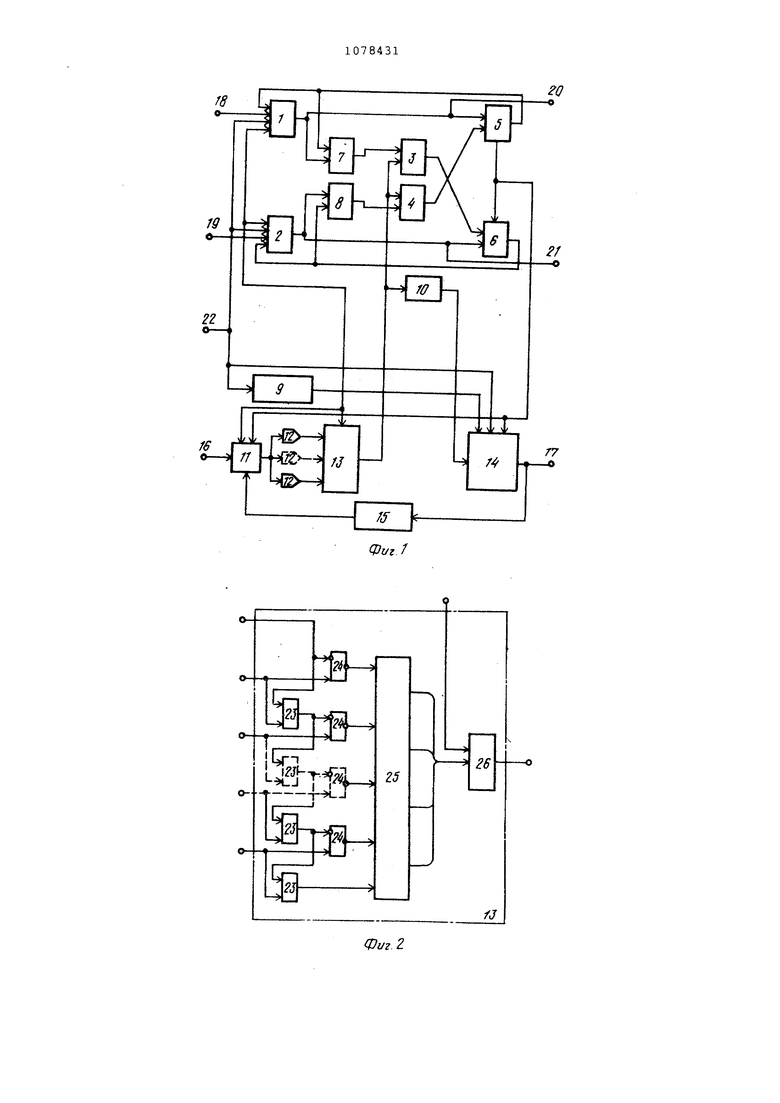

Запускающий сигнал низкого уровня поступает на запускагаций вход 60 (эпюры на фиг.4) устройст ва в момент времени tg, По его

переднему фронту генератор импульсов 35 сбрасывается в нулевое состояние, причем формирование серий импульсов ll, и cj соответственно на

5 третьем 63 и первом 61 выходах генератора импульсов начинается с задержкой С , Серия импульсов с формируемая на втором выходе 62 генератора импульсов 35, представля0 ет собой задержанную на IQ сериюIJ-,

Кроме синхронизации генератора импульсов 35, по переднему фронту U i осуществляется занесение информации oL и1| по информацион5 ным входам 54 и 55, так как поступает и на первые управлякзцие входы регистров 27 и 28,

Во время длительностиUзал через элемент 43 запрета блокирует0 ся поступление сигнала по вторым управлякщим входам регистров. По установочному входу триггер 40 устанавливается в единичное состояние и по входу установки О накапли5 ваюций сумматор 50 аналого-цифрового преобразователя сбрасывается в нулевое состояние. Так как триггер 40 установлен в единичное состояние то с приходом серии на первом выходе 61 генератора 35 импульсов и на вьоходе 64 второго элемента И

42формируется положительнрлй импульс 2 дц . По переднему фронтуСд 1,п н выходе регистра инкрементных приращений 49 и на знаковом выходе блока 46 вычитания фиксируются соответственно значения инкремента и знак приращения. Код инкремента 1 ифрируется в значения i и V поэтому с приходом переднего фронта серии

на выходе первого элемента И 41 формируется строб, разреишюидий занесение значениям в счетчик 37.

Отсчет длительностей серий , и 1,-5 осуществляется от заднего фронта запускающего импульсаО-j n Длительность импульсов серии t меньше, че серии и,..По окончании импульса сери о 3 оканчивается и импульс дцп своим задним фронтом фиксируя результат на информационном выходе 53 устройства, так как поступает на тактирующий вход накапливагачего сумматора. 50. При окончании импульса серии bi с третьего выхода 63 генератора 35 импульсов на выходе схемн

43запрета формируется сигнал занесения, по которому информация с выходов первого 31 и второго 32 сумматоров переписывается в соответствующие регистры 27 и 28. Кроме того, задним фронтом импульс серии

1ц поступающий на счетный вход сче чика 37, изменяет его состояние на единицу (счетчик 37 работает на вычитание). Это состояние дешифрируется дешифратором 45 нуля, и если оно окажется нулевьил, то на информационный вход триггера 40 поступит единичный сигнал 58, которьой передастся на выход 59 триггера 40 в момент окончания импульса t со второго выхода генератора импульсов. Если счетчик 37 находится не в нулевом состоянии, то триггер 40 имеет нулевое состояние, в результате чего блокированы сигналы с дцп на тактирующих входах соответствующих блоков 46, 49 и 50 аналого-цифрового преобразователя, а блокирован строб занесения на синхровходе счетчика 37. В этом случае информация о V сохраняется, а счетчик 37 работает только в режиме вычитания. При этом блоками 27 34 осуществляется последовате-пьность гПу элементарных поворотов для инкрементного приращения 2 .

Если счетчик 37 находится в нулевом состоянии, то задним фронтом импульса , триггер 40 переводится в единичное состояние, поэтому по .импульсу t-J формируется импульс

Г (цп управлякщий работой блоков аналого-цифрового преобразователя, а по импульсу i-j формируется стро на счетчик 37, передним фронтом устанавливая значение глу для нового значения V. Количество значений Wy зависит от величины приращения и разрядности блока вычисления координат. Для установившегося режима слежения в блоках аналогоцифрового преобразователя значение

V обычно близко к максимальному, пэтому п1 V чаще всего принимает значения равные единице. В этом случае блоки 27 - 34 вычисления координат работают вместе с аналого-цифровым преобразователем в конвейерном режиме, т.е. параллельно, без потерь времени. В отдельных случаях, когда крутизна сигнала достаточно влика, может принимать значения порядка 5 - 10, что несколько увеличивает переходный процесс отслеживания аргумента X.

Отработка одного значения приращения входного сигнала X с аналогоцифрового преобразователя устройства по второму варианту осуществляется в основном за 1 - 3 такта по сравнению с (1 -) тактов прототипа, т.е. в предлагаемом устройстве быстродействие в N|3 раз выие, чем в известном. Сокращены аппаратурные затраты на 10 - 15% по сравнению с прототипом за счет исключения из устройства регистра, сумматора, блока памяти и блока анализа состояния в блоке формирования остатка аргумента.

В отличие от первого варианта предложенного устройства, второй вариант практически при тех же за тратах оборудования имеет на 30% меньшее быстродействие, однако в связи с тем, что для аргумента используются инкрементные приращения, значительно легче может быть осуществлено согласование с иными устройствами инкрементного типа.

Г8

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Аналого-цифровой инкрементный дифференциатор | 1985 |

|

SU1343410A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Устройство для вычисления квадратного корня | 1984 |

|

SU1264167A1 |

| Инкроментный умножитель аналоговых сигналов | 1982 |

|

SU1057970A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Аналого-цифровой инкрементный вычислитель экспоненциальной функции | 1985 |

|

SU1254511A1 |

1. Устройство для поворота вектора, содержащее два регистра, два сдвигателя, четыре сумматора, генератор импульсов, блок памчти, блок вычитания, группу пороговых элементов, приоритетный блок, накапливаютий сумматор и цифроаналоговый преобразователь, вход и выход которого соединены соответственно с выходом накапливагацего сумматора и вычитаквдим входом вычитания, суммиругаций вход, тактирующий вход, знаковый и информационный -выходы которого подключены соответственно к аналоговому входу устройства, выходу генератора импульсов, входу приращения накапливающего сумматора и входам пороговых элементов группы, тактирующий вход и выход накапливакяцего сумматора соединены соответственно с выходом генератора импульсов и информационным выходом устройства, выходы пороговых элементов группы подключенн к соответствующим информационным входам приоритетного блока, управляющий вход которого соединен с выходом генератора импульсов, первые информационные зходы первого и второго регистров подключены соответственно к первому и второму информационньлм входам устройства, вторые информационные входы первого и второго регистров соединены с выходами соответственно первого и второго., сумматоров, выход первого регистра подключен к первым информационным входам первого и третьего сумматоров и первому выходу кода координат устройства, а выход второго регистра к первым информационным входам второго и четвертого сумматоров и.второму выходу кода координат устройства, вторые информационные (О входы третьего и четвертого сумматоров соединены с выходами соответственно первого и второго сумматоров , информационные входы и выходы первого и второго сдвигателей подключены соответственно к выходам третьего и четвертого сумматоров и вторым информационным входам второго и первого сумматоров , отличающееся X) тем, что, с целью новы1иения его 4;ib быстродействия, запускакхпий вход устройства соединен с входом гене: ратора импульсов, входом установки о накаплива1Ш1его сумматора и первыми управляющими входами первого и второго регистров, вторые управлякиие входы которых подключены к ввЕходу генератора импульсов, выход приоритетного блока соединен с управляюсчими входами первого и второго сдвига)телей и адресным входом блока памяти Твыход которого подключен к информационному входу накапливающего сумма,тора,а управляющие входы первого и второго сумматоров соединены со знаковым входом блока вычитания.

t,lft|;g J

26

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Н | |||

| и др.Введение в кибернетическую технику .Киев ,наукова думка,1979,с.172, рис | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-07—Публикация

1982-04-19—Подача