(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределителя | 1980 |

|

SU942026A1 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для разбраковки полупроводниковых диодов | 1983 |

|

SU1164636A1 |

| Пересчетное устройство с контролем | 1982 |

|

SU1019452A1 |

| Устройство для контроля параметров срабатывания электромагнита | 1985 |

|

SU1302245A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для управления шаговым двигателем с дроблением шага | 1983 |

|

SU1149367A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАСПРЕДЕЛИТЕЛЯ по авт. св. 942026Л о.тличающееся тем, что, с целью расширения его функциональных возможностей путем обеспечения воз- можности контроля распределителей, реализованных на базе регистров . , сдвига, выход нулейого -разряда блока формирования остаточного кода по модулю три подключён к информационному входу контролируемого распределителя .4

ГС

00 tsP

да

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для контроля электронных блоков дискретной автоматики и ЭВМ.

По авт. св. 942026 известно устройство для контроля распределителя, содержащее три триггера, два элемента ИтНЁ, элемент И, элемент НЕ, элемент 2И-ИЛИ-НЕ, элемент задержки и блок формирования остаточного кода по модулю три, причем выход первого элемента И-НЕ соединен с установочным входом первого триггера, выход второго триггера соединен с первым входом второго элемента И-НЕ, входы блока формирования остаточного кода по модулю три соединены соответственно с выходами контролируемого распределителя выход нулевого разряда которого соединен с установочным входом второго триггера и с входом элемента НЕ, выход i OTOporo соединен с входо сброса третьего триггера, прямой выход которого соединен с первым входом элемента 2И-ИЛЙ-НЕ, выход которого соединен с вторым входом второго элемента, И-НЕ, выход второго элемента И-НЕ соединен с первым входом второго элемента И-НЕ, второй вход которого соединен с выходом элемента задержки, вход которог соединенс выходом элемента И, с синхровходом контролируемого.распределителя и со счетным входом третьего триггера, инверсный выход которого соединен с вторым входом элемета 2И-ИЛИ-НЕ, третий вход которого соединен с выходом первого разряда блока формирования остаточного кода по модулю три, выход второго разряда которого соединен с четвертым входом элемента 2И-ИЛИ-НЕ, инверсный выход первого триггера соединен с первым входом элемента И, второй вход которого является синхровходом устройства,-выход устройства соединей с прямым выходом первого триггера 13.

Цель изобретения - расширение функциональных возможностей устройства Путем обеспечения возможности контроля распределителей, реализованных на базе регистров сдвига.

Поставленная цель достигается тем, что в устройстве для контроля распределителя выход нулевого разряда блока формирования, остаточного кода по модулю три подк,лючен к информационному входу контролируемого распределителя.

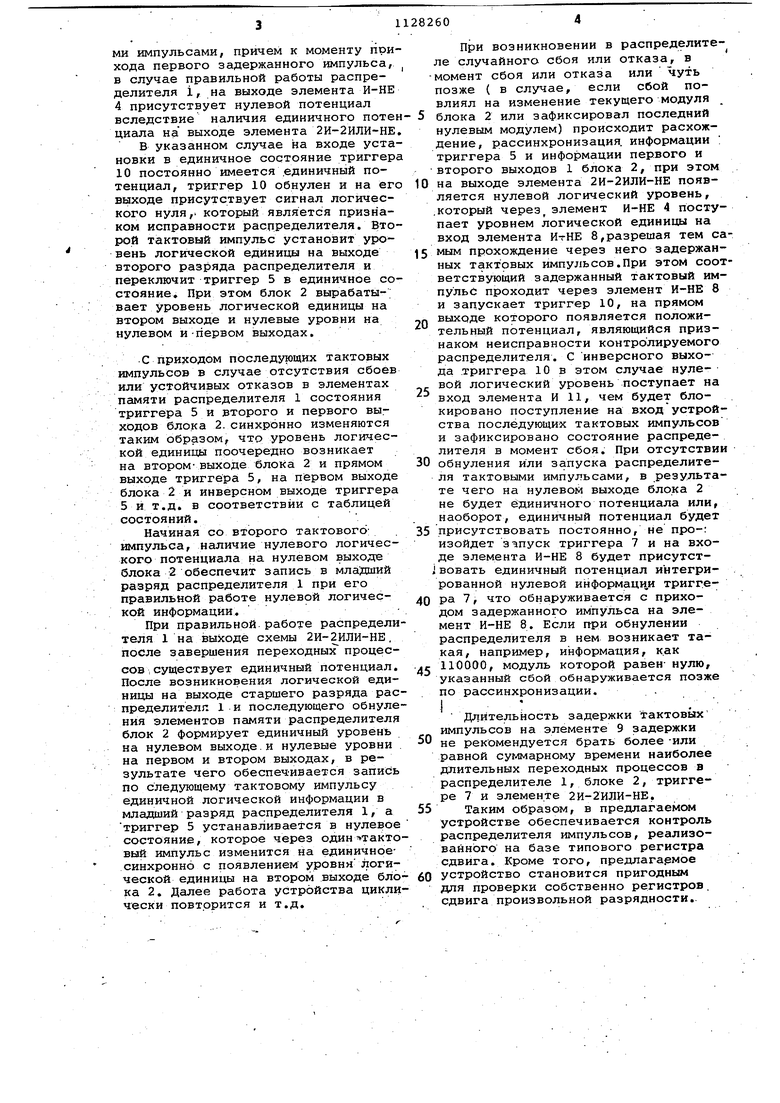

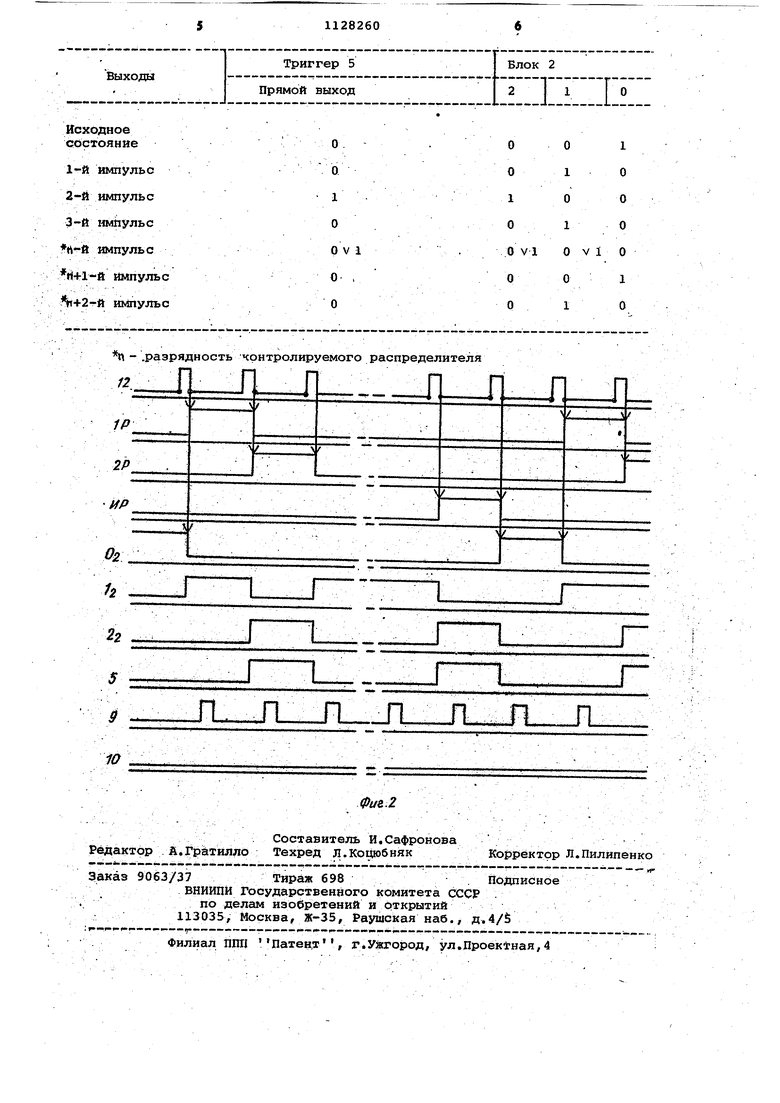

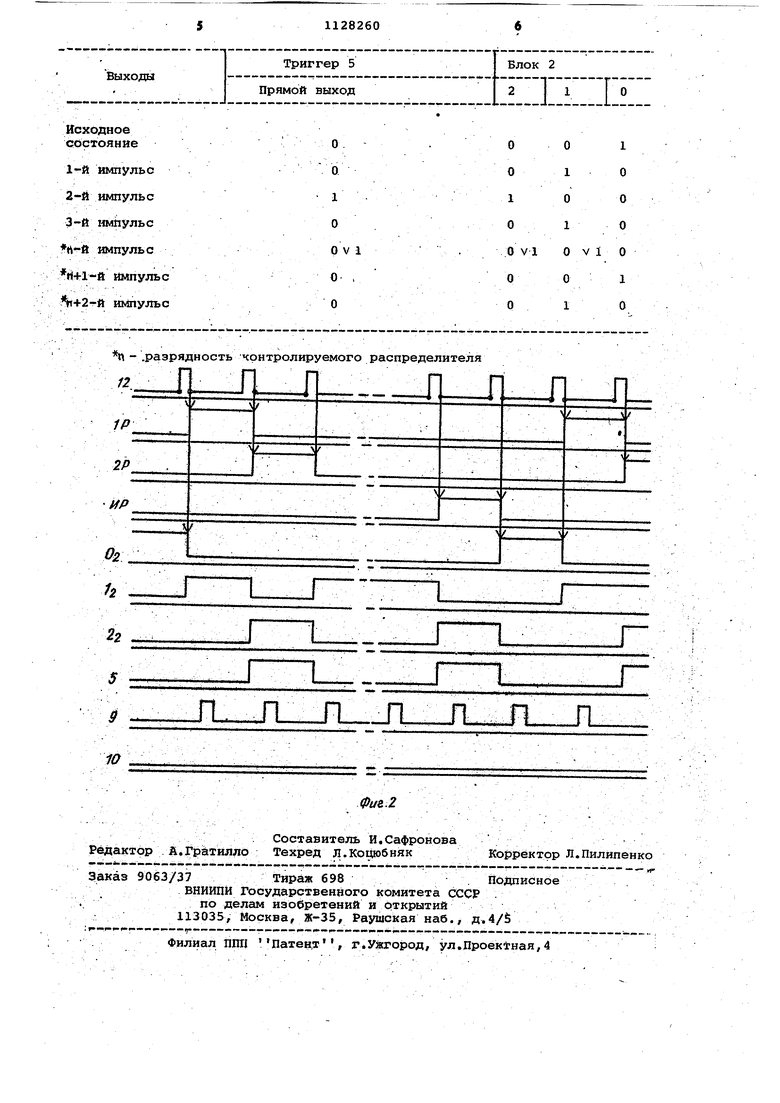

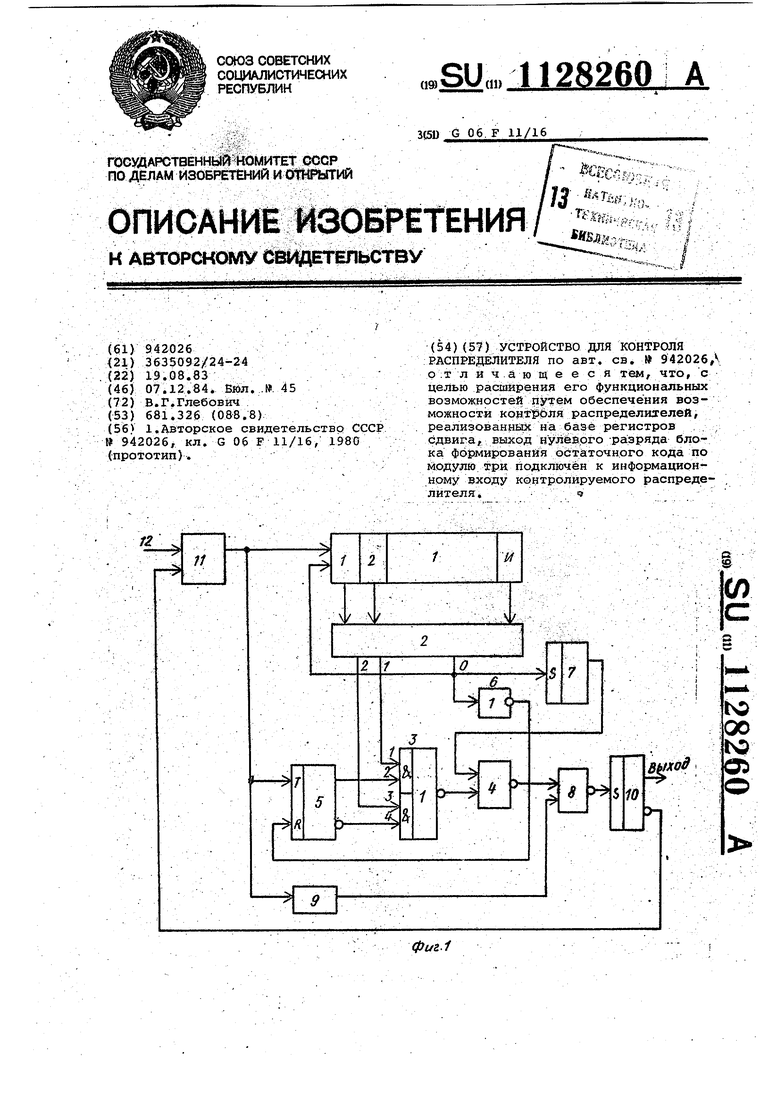

На фиг.1приведена функциональная схема устройства; на фиг. 2 - временные диаграммы.

Устройство содержит контролируемый распределитель 1, блок 2 формирования остаточного кода по модулю

три, элемент 2И-ИЛИ-НЕ 3, элемент И-НЕ 4, первый триггер- 5, элемент НЕ 6, второй триггер 7, элемент И-НЕ 8, элемент 9 задержки, третий триггер 10, элемент И 11, синхровход 12 устройства.

Устройство работает следующим образом..

Перед началом проверки распределтель 1, триггеры 5, 7 и 10 устанавливаются в нулевбе состояние сигналом Сброс (цепи сброса не показны) .

При- этом на нулевом выходе блока 2 формирования остаточного кода по модулю три и, следовательно, на информационном входе распределителя 1 устанавливается уровень логической единицы, на первом и втором чщыходах данного же блока устанавливаются логические потенциалы (блок 2 сигнализирует о фактическом или мнимом обнулении элементов памяти распределителя 1), на прямом выходе триггера 10 присутствует нулевой логический потенциал, являющийся признаком исправности контролируемого распределителя, одновременно уровень логической единицы с инверсного выхода данного же триггера поступает на вход элемента И 11, тем самым разрешая поступление в устройство RO второму входу указанной схемы тактовых импульсов.

С приходом первого тактового импульса по его заднему фронту (все триггеры устройства и распределител п еключаются при подаче на их импульсные входы перепада Логическая единица - логический нуль) срабатывает распределитель 1, на выходе младшего разряда которого при этом появляется уровень логичекой единицы.

При этом на нулевом выходе блока 2 возникает нулевойлогический потенциал, на первом выходе - единичный логический потенциал, а на втором выходе сохраняется нулевой логический поте1нциал, причем триггер 5 остается в исходном состоянии, так как разрешающий переключение триггера единичный потенциал поступает на его вход обнуления с выхода элемента НЕ 6 после завершения первого тактового импульса.

При изменении потенциала на нулевом выходе 6jjOKa 2 с единичного уровня на уровень логического нуля происходит запуск триггера 7, который подает положительный потенциал на вход элемента И-НЕ 4, разрешая тем самым прохождение информации с элемента 2И-2ИЛИ-НЕ на выход устрой ства.

элемент И-НЕ 8 осуществляет опрос состояния элемента И-НЕ 4 задержанными на элементе 9 задержки тактовыми импульсами, причем к моменту прихода первого задержанного квмпульса, в случае правильной работы распределителя 1, на выходе элемента И-НЕ

4присутствует нулевой потенциал вследствие наличия единичного потен циала на выходе элемента 2И-2ИЛИ-НЕ

В указанном случае на входе установки в единичное состояние триггера 10 постоянно имеется .единичный потенциал, триггер 10 обнулен и на его выходе присутствует сигнал логического нуля , который является признаком исправности распределителя. Второй тактовый импульс установит уровень логической единицы на выходе второго разряда распределителя и переключит триггер 5 в единичное состояние. При этом блок 2 вырабатывает уровень логической единицы на втором выходе и нулевые уровни на нулевом и-первом выходах,

С приходом последующих тактовых импульсов в случае отсутствия сбоев или устойчивых отказов в элементах памяти распределителя 1 состояния триггера 5 и второго и первого выходов блока 2. синхронно изменяются таким образом, чтр уровень логической единицы поочередно возникает на втором-выходе блока 2 и прямом выходе триггера 5, на первом выходе блока 2 и инверсном выходе триггера

5и т.д. в соответствии с таблицей состояний.

Начиная со второго тактового; импульса, наличие нулевого логического потенциала на нулевом выходе блока 2 обеспечит запись в младший разряд распределителя 1 при его правильной работе нулевой логической информации, При правильной работе распределителя 1 на выходе схемы 2И-2 ИЛИ-НЕ, после завершения переходнызГ процессов , существует единичный потенциал. После возникновения логической единицы на выходе старшего разряда распределителл 1 и последующего обнуления элементов памяти распределителя блок 2 формирует единичный уровень на нулевом выходе.и нулевые уровни . на первом и втором выходах, в результате чего обеспеч-ивается запись по следующему тактовому импульсу единичной логической информации в младший разряд распределителя 1, а триггер 5 устанавливается в нулевое состояние, которое через один«тактовый импульс изменится на единичноесинхронно с появлением уровня логической единицы на втором выходе блока 2. Далее работа устройства циклически повт.орится и т.д.

При возникновении в распределителе случайного сбоя или отказа, в -момент сбоя или отказа или чуть позже ( в случае, если сбой повлиял на изменение текущего модуля

5 блока 2 или зафиксировал последний нулевым модулем) происходит расхождение, рассинхронизация. информации ; триггера 5 и информации первого и -второго выходов 1 блока 2, при этом

0 на выходе элемента 2И-2ИЛИ-НЕ появляется нулевой логический уровень, .который через, элемент И-НЕ 4 поступает уровнем логической единицы на вход элемента ИтНЕ 8,разрешая тем са5 мым прохождение через него задержанных тактовых импульсов.При этом соответствующий задержанный тактовый импульС проходит через элемент И-НЕ 8 и запускает триггер 10, на прямом

,. выходе которого появляется положительный потенциал, являющийся признаком неисправности контролируемого распределителя. С инверсного выхода .триггера 10 в этом случае нулевой логический уровень поступает на

5 вход элемента И 11, чем будет бло- . кировано поступление на входустройства послёдующи-х тактовых импульсов и зафиксировано состояние распределителя в момент сбоя. При отсутствии

0 обнуления или запуска распределителя тактовыми импульсами, в результате чего на нулевом выходе блока 2 не будет единичного потенциала или, наоборот, единичный потенциал будет

г llOQiOO, модуль которой равен- нулю, указанный сбой обнаруживается позже по рассинхронизации. .

Дд1йтельность задержки тактовых импульсов на элементе 9 задержки

50 не рекомендуется брать более -или

равной суммарному времени наиболее длительных переходных процессов в распределителе 1, блоке 2, триггере 7 и элементе 2И-2ИЛИ-НЕ.

55 Таким образом, в предлагаемом устройстве обеспечивается контроль распределителя импульсов, реализовайного на базе типового регистра сдвига. Кроме того, предлагаэмое

60 устройство становится пригодным для проверки собственно регистров. сдвига произвольной разрядности..

разрядность контролируемого распределителя

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля распределителя | 1980 |

|

SU942026A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| (прототип). | |||

Авторы

Даты

1984-12-07—Публикация

1983-08-19—Подача