001...100. После одного сбоя синхро низации регистр имеет состояние в конце такта 01...1000, т.е. эта информация по отношению к пришедшей на вход будет искаженной, а схема контроля по первому и последнему триггеру регистра это искажение не обнаружит. Цель изобретения - повышение эффективности контроля сдвигающего ре гистра за счет фиксирования неиспра ностей, вызванных пропаданием одного или нескольких импульсов синхронизации. Поставленная цель достигается тем, что в устройство для контроля регистра сдвига,содержащее блок кон роля по четности, первый и второй сумматоры по модулю два, первый триггер, первый элемент 2ИИЛИ, первый и второй элементы И, причем информационные входы контролиру емого регистра соединены с входами блока контроля по четности, выход которого соединен с первым входом первого сумматора по модулю два, вы ход которого соединен с первым вход второго сумматора по модулю два, т товый вход устройства соединен с пе выми входами первого и второго элементов И, с тактовым входом контрол руемого регистра, с первым входом первого элемента 2И-ИЛИ, выход кото рого является выходом устройства, ВЫХОД первого триггера соединен с вторым входом первого сумматора по дулю два, прямой И инверсный входы принимаемой информации устройства соединены соответственно с вторыми входами первого и второго элементов И, выходы которых соединены соответственно с единичным и нулевым входами первого разряда Контролируемого регистра, введены трети и четвертый сумматоры по модулю два второй и третий триггеры, формирова тель начальной установки, ждущий мультивибратор, первый и второй элементы НЕ, второй, .третий и четве тый элементы 2И-ИЛИ, причем вход начальной установки устройства,соединен с входом ждущего мультивибрз тора, с синхровходом второго тригге ра, с первым входом формирователя начальной установки и с входом первого элемента НЕ, единичный выход второго триггера соединен с вторым входом формирователя начальной уста новки, с первым входом второго элемента 2И-ИЛИ, выход которого соединен с синхровходом первого триггера, выход первого элементами соединен с вторым входом второго элемента 2И-ИЛИ, нулевой выход второго триггера соединен с третьим входом второго элемента 2И-ИЛИ и с первым входом третьего сумматора по модулю два; выход которого соединен с вторым входом второго сумматора по модулю два, выход третьего триггера соединен с вторым входом третьего сумматора по модулю два и с первым входом четвертого сумматора по модулю два, выходы второго и четвертого сумматоров по модулю два соединены соответственно с вторым и третьим входами первого элемента 2И-ИЛИ, выход ждущего мультивибратора соединен с четвертым входом первогб элемента 2И-ИЛИ, единичный второго триггера соединен с вторым входом четвертого сумматора по модулю два, выход второго элемента И соединен с четвертым входом второго элемента И, первый выход формирователя начальной установки соединен с входом установки в ноль первого разряда контролируемого регистра, с входом установки в единицу всех остальных разрядов, с первым единичным входом третьего триггера и с первым входом третьего элемента 2И-ИЛИ, выход которого соединен с нулевым входом первЪго триггера, второй выход формирователя начальной установки соединен с первым нулевым входом третьего триггера, с входом установки Ъ единицу первого разряда контролируемого регистра и с входом установки в ноль всех остальных разрядов и с первым входом четвертого элемента 2И-ИЛИ, выход которого соединен с единичным входом первого триггера, управляющий вход устройства соединен с вторыми входами третьего и четвертого элементов 2И-ИЛИ и через второй элемент НЕ с третьими входами третьего и четвертого элементов 2И-ИЛИ, выход первого элемента НЕ соединен с четвертым входом четвертого элемента 2И-ИЛИ, четвертый вход третьего элемента 2И-ИЛИ соединен с входом задания логической единицы, третий и второй контрольные выходы контролируемого регистра соединены соответственно с вторыми единичным и нулевым входами третьего триггера. Формирователь начальной установки содержит первый и второй элементы И-НЕ, причем первый вход формирователя соединен с первыми входами первого и второго элементов И-НЕ, выходы которых являются соответствен но первым и вторым выходами формирователя, второй вход формирователя со- «О

единен с вторым входом первого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ.

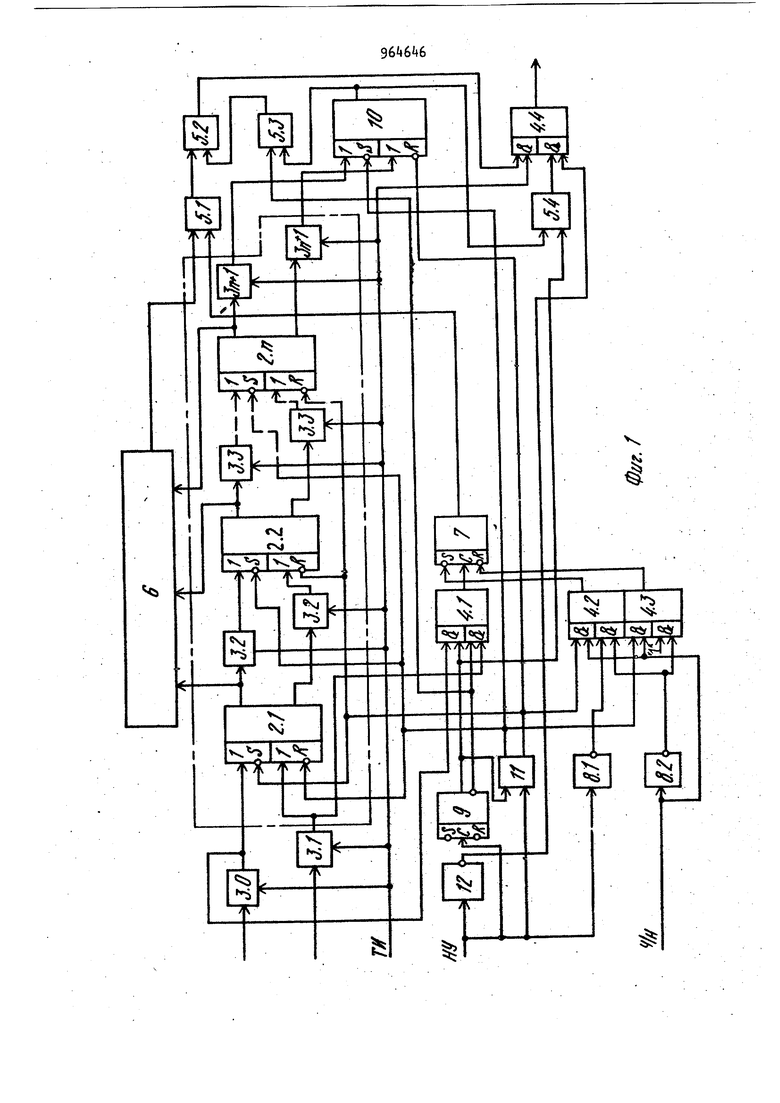

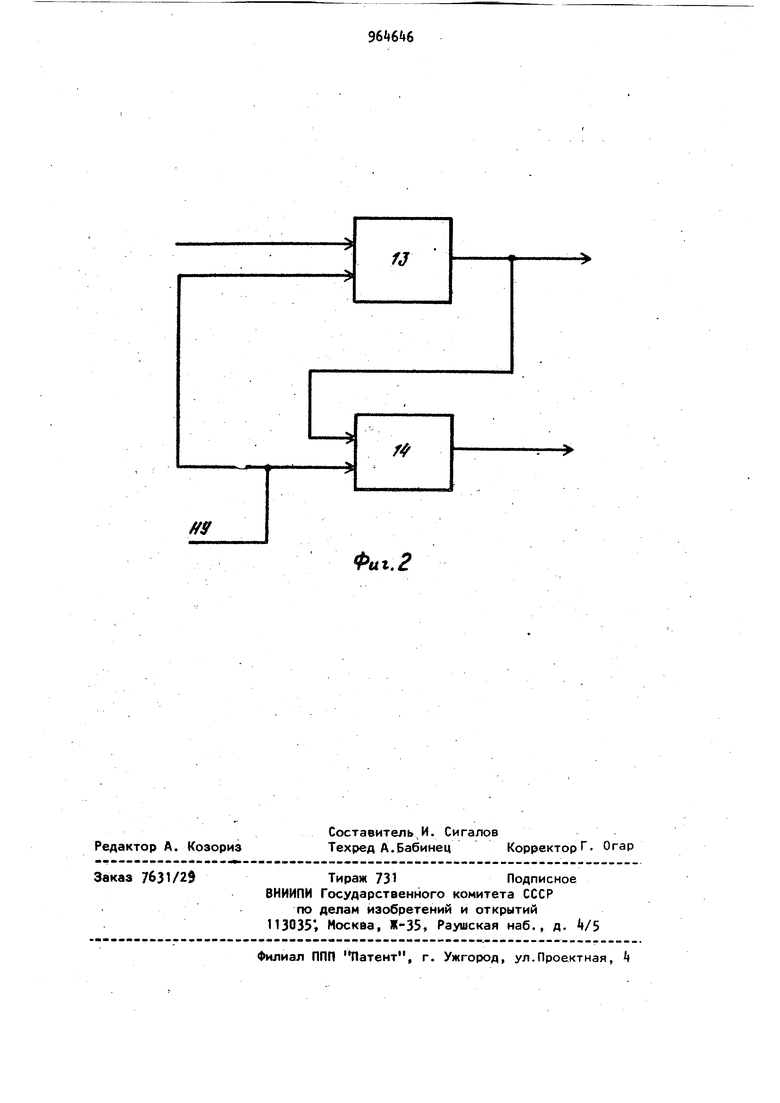

На фиг.1 представлена структурная схема устройства для контроля регистра сдвига; на фиг, 2 - структурная схема формирователя начальной установки,

В качестве контролируемого регистра сдвига (фиг, 1) представлен импульсно-потенциальный регистр 1, На статических триггерах 2.1-2,п прямой и инверсный информационные входы устройства соединены соответственно через первый 3-0 и второй 3.1 элементы И единичным и нулевым входами контролируемого регистра 1, В состав регистра входят элементы И 3.2-3(п+1), Кроме того, в состав устройства входят первый Ц.Ц, второй 4.1, третий ,3 и четвертый .2 элементы 2И-ИЛИ, первый 5-1, второй 5,2, третий 5,3 и четвертый Б, сумматоры по модулю д%а, блок 6 контроля tio четности, первый триггер 7, первый 8,1 и второй 8.2 элементы НЕ, второй 9 и третий 10 триггеры, формирователь 11 начальной установки и ждущий мультивибратор 12, В формирователь 11 начальной vcтановки входит первый 13 и второй-. 1 элементы И-НЕ, выходы которых являются выходами формирователя.

Начальная установка (НУ) триггеров регистра сдвига и контролирующих элементов производится перед каждым сдвигаемым словом до начала пачки тактовых импульсов, равных по количеству числу статических триггеров в регистре. Устройство контроля услов но можно разделить на схему контроля информации, производящую контроль сдвигаемой информации на каждом такте сдвига и схему контроля сбоя синхронизации, производящую контроль по сбою синхронизации после каждого сдвигаемого слова.

ГО выхода КС запирает по четвертому входу первый двухвходовый элемент 2И-ИЛИ ., предназначенный для выхода сигнала ошибки при сбое синхро5низации, причем длительность запрета выбирается равной длительности прохождения пачки импульсов (в данном случае - трех). Импульс начальной установки, попадая на счетный вход второго триггера 9, устанавливает

0 его в одно из состояний (О или 1), изменяемых с каждым словом информации. Для примера предположим, что он . установится в состояние 1. В соот5ветствии с этим, а также по импульсу (на управляющем входе), формирователь П начальной установки (фиг.- 2) вырабатывает на выходе первого элемента И-НЕ 13 нулевой потенциал, а на выходе Bfpporo элемента И-НЕ 1 0единичный потенциал. Высокий потенциал с первого выхода формирователя 11 поступает на вход установки в О первого разряда регистра и на вход установки в О всех остальных. Нуле5вой потенциал с второго выхода формирователя 11 установит триггер перjBoro разряда регистра в единицу, а. все остальные разряды в НОЛБ. Кроме того, третий триггер 10 также устано0вится в нулевое состояние. После окончания сигнала на управляющем входе устройства, на выходах формирователя 11 будут единичные потенциалы, которые не изменяют состояния регистра и третьего триггера. Таким образом, нулевой сигнал с выхода триггера 10 и сигнал 1 с прямого выхода второго триггера 9 устанавливают на выходе 46 4 .Контроль работы сдвигающего регистра рассмотрим на конкретном примере регистра, состоящего из трех статических триггеров. На управляющий вход в данном случае подается логическая юдиница. С приходом импульса в начальной установке, следующим перед каждой пачкой тактовых импульсов с постоянным временем. мультивибратор 12 со своего инверсночетвертого сумматора 5 сигнал ошибки, который пройдет на выход первого двухвходового элемента 2И-ИЛИ по окончании пачки из трех импульсов в случае пропадания хотя бы одного импульса синхронизации, в результате. записанная чего контрольная единица, в первый разряд регистра 1, не заносится в триггер 10 и ликвидирует ошибку на выходе сумматора 5, В тригге.7 pax 2 регистра, кроме первого, запис на именно ошибочная информация (в данном случае нули), и только точное количество пачки . импульса приведет к перезаписи в контрольный триггер 10 без.ошибочной контрольной информации записанной в первый разряд регистра 1, а следовательно, к отсутствию ошибки в конце слова по сбс синхронизации, . Аналогичный контроль по сбою синх ронизации осуществляется с приходом нового управляющего сигнала (т.е. с новым словом информации),но с записью, в соответствии с измененным состоянием триггера 9 из Ч в О, в первый разряд триггера 2 - нуля, а в остальные триггеры 2 регистра и третий триггер 10 единиц. Контроль работоспособности регистра сдвига с каждым тактом поступ ющей информации по четности происходит следующим образом. Согласно примеру, когда на выходе второго триггера 9 находится единица, и в соответствии с этим в первом разряде регистра 1 также 1, в первом - триггере 7 ,в триггерах 2.2, 2.3 и третьем триггере 10-нули,Вэтом случае на входе блока 6 имеется информация 100, а результате на его выходе - ед ница, которая поступает на первый вход сумматора 5.1) на втором входе которого - единица с выхода первого триггера 7- Сигнал ошибки.перед приходом информации на вход регистра иа сумматоре 5-1 отсутствует. Предположим, на вход регистра пос тупает вместе с первым тактом единичная информация, тогда на входе блока 6 информация изменится на 110, следовательно, с выхода блока 6 на первый вход первого сумматора 5.1 поступит нулевой сигнал, ,что должно привести к ошибке на выходе сумматора 5.1, но, в связи с тем, что поступающая вместе с тактом на вход регистра единица совпадает с единицей прямого выхода второго триггера 9, по первому входу двухвходового элемента 2И-ИЛИ будет k.. Эта единица поступит на счетный вход первого триггера 7, устанавливая его

снимая ошибку суммаа состояние

тора 5.1 и не давая ей проходить через первый вход элемента запрета ., что говорит о правильной записи данной единицу информации в регистр.

с выхода блока

оста.пьные - единицы, 6 будет единица.

гГредлагаемое устройство позволяет обнаружить любые ошибки в регист 6Предположим, что на вход вместе с вторым тактом поступает нулевая информация, тогда на входе блока 6 она будет после сдвига Oti, следовательно, выход блока 6 не изменится (О) , в то же время присутствие сигнала с нулевого входа с элемента 3, с наличием второго такта, через . четвертый вход второго двухвходового элемента 2И-ИЛИ - k. пройдет, так как он закрыт нулевым потенциалом триггера 9, следовательно на счетный вход триггера 7 единичная информация не поступит и он останется в нулевом положении, т.е. ошибка на выходе сумматора 5-1 отсутствует, что говорит о .правильной записи информации (в данном случае нулевой). Пусть с третьим тактом поступает единичная информация, тогда на входе блока 6 она будет после сдвига 101, контрольная единица запишется в триггер 10, на выходе блока 6 - О, а на В1з1ходе триггера 7 - 1, так как поступившая единица информации изменит его состояние „а с выхода сумматора 5.1 единица поступит на первый вход сумматора 52, на втором входе которого тоже единица, и, следовательно; сигнал ошибки на выходе устройства отсутствует. Аналогично осуществляется контроль работы работоспособности регистра сдвига по четности при приходе следующего импульса НУ, только в этом случае, в связи с установкой триггера 9 в нулевое состояние, информация в триггере 7, в триггере 10 и в триггерах регистра записывается инверсной и контрольный разряд, про двигающийся по регистру, равен не М, а ТТ. Контроль работоспособности сдвигающёго регистра при четном количестве триггеров 2 отличается тем, что на уп(эавляющий вход подается логический .нуль и с каждым импульсом НУ триггер 7 устанавливается только в единичное состояние во избежание появления ошибки на сумматоре 5.1,так как при записи единицы в первый триггер 2, а остальные - нулй, атакже (с новым импульсом НУ) при записи нуля в первый триггер 2 регистра, а в ре сдвига с неограниченным1числом разрядов как при четном их количестве, так и при нечетном. Формула изобретения 1. Устройство для контроля регист ра сдвига, содержащее блок контроля по четности, первый и второй сумматоры по модулю два, первый триггер, первый элемент 2И-ИЛИ| первый и второй элементы И, причем информационны выходы контролируемого регистра соединены с входами блока контроля по четности, выход которого соединен с первым входом первого сумматора по модулю два, выход которого соединен с первым входом второго сумматора по модулю два, тактовый вход устройства соединен с первыми входами первого и второго элементов И, с тактовым входом контролируемого регистра, с первым входом первого элемента 2И-ИЛИ; выход которого является выходом устройства, выход первого триггера соединен с вторым входом первого сумматора по модулю два, прямой и инверсный входы |;1ринимаемой информации устройства соединены соответственно с вторыми входами пер вого и второго элементов И, выходы которых соединены соответственно с единичным и нулевым входами первого разряда контролируемого регистра, отличающееся тем, что,с целью повышения эффективности контро ля, в устройство введены третий и четвертый сумматоры по модулю два, второй и третий триггеры, формирователь начальной установки, ждущий мультивибратор, первый и второй элементы НЕ, второй, третий и четвертый элементы 2И-ИЛИ, причем вход начальной установки устройства соединен с входом ждущего мультивибратора, с синхровходом второго триггера, с пер вым входом формирователя начальной установки и с входом первого элемента НЕ, единичный выход второго три1- гера соединен с вторым входом формирователя начальной установки, с первым входом второго элемента 2И-ИЛИ, аыход которого соединен с синхровходом первого триггера, выход перво го элемента И соединен с вторым входом второго элемента 2И-ЙЛИ, нулевой выход второго триггера соединен с третьим входом второго элемента 2И-ИЛИ и с первым входом третьего сумматоратпо модулю два, выход которого соединен с вторым входом второг го сумматора по модулю два, выход третьего триггера соединен с вторым входом третьего сумматора по модулю два и с первым входом четвертого сумматора по модулю два, выходы второго и четвертого сумматоров по модулю два соединены соответственно с вторым и третьим входами первого элемента 2И-ИЛИ, выход ждущего мультивибратора соединен с четвертым вхо- . дом riepBoro, элемента 2И-ИЛИ, единичный выход второго триггера соединен с вторым входом четвертого сумматора по модулю два, выход второго элемента И соединен с четвертым входом второго элемента И, первый выход формирователя начальной установки соедин нен с входом установки в ноль пе рвого разряда контролируемого регистра, с входом установки в единицу всех остальных разрядов, с первым единичным входом третьего триггера и с первым входом третьего элемента 2И-ИЛИ, выход которого соединен с нулевым входом первого триггера, второй выход формирователя начальной установки соединен с первым нулевым входом третьего триггера, с входом установки в единицу первого разряда контролируемого регистра и. с входом установки в ноль всех остальных разрядов и с первым входом четвертого элемента 2И-ИЛИ, выход которого соединен с единичным входом первого триггера, управляющий вход устройства соединен с вторыми входами третьего и четвертогЬ элементов 2И-ИЛИ и через второй элемент НЕ с третьими входами третьего и четвертого элементов 2И-ИЛИ, выход первого элемента НЕ соединен с четвертым входом четвертого элемента 2И-ИЛИ, четвертый вход третьего элемента 2И-ИЛИ соединен с входом задания логической единицы, третий и второй контрольные выходы контролируемого регистра соединены соответственно с вторы-ми единичным и нулевым входами третьего триггера. 2. Устройство по п. 1, отличающееся, тем, что формирователь начальной установки содержит первый и второй элементы И-НЕ, причем первый вход формирователя соединен с первыми входами первого и второго

11 96i«64612

элементов И-НЕ, выходы которых яв-Источники информации,

ляются соответственно первым и вто-принятые во внимание при экспертизе

рым выходами формирователя, вторбй1. Авторское свидетельство СССР

вход формирователя соединен с вторымIf 399862, кл. G, ОЕ F , 197.

входом первого элемента И-НЕ, вы.ход5 2, Авторское свидетельство СССР

которого соединен с вторым входомN , кл. G 06 F 11/08, 1378

второго элемента И-НЕ. .(прототип).

Фаг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1982 |

|

SU1056199A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Запоминающее устройство с исправлением многократных ошибок | 1985 |

|

SU1300568A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

Авторы

Даты

1982-10-07—Публикация

1981-03-17—Подача