Изобретение относится к айтоматике и вычислительноГ1 технике и может быть использовано для контроля распре делителей. Известно устройство для проверки логических схем, содержащее устройство для генерирования контрольных сигналов, подаваемых на входные контакты проверяемой схемы, которое включает логическую схему, полностью идентич ную проверяемой, и функционируют заве домо правильным образом; коммутационное устройство, которое предназначено для того Чтобы подавать проверочные сигналы, вырабатываемые устройством . контрольных сигналов, одновременно на входные контакты проверяемого устройства и устройства эталонного, устройство логического сравнения, подключенное к выходным контактам проверяемое логической схемы и эталон ной логической схемы, которое осуществляет проверку того, совпадают или не совпадают их выходные сигна™ Недостаток этого устройства - необходимость использования эталонной логической схемз полностью аналогичной проверяемой схеме, причем, при возникновении одновременных идентичных сбоев в эталонной и контролируемой схемах указанные сбои не обнаруживаются. Наиболее близким по технической сущности является устройство, содержащее входной регистр, сдвиговый регистр, узел индикации, формирователь импульсов, f3fBa триггера и две схемы запрета U1), которое обеспечивает локализацию неисправностей элементов памяти распределителя в режиме обработки инчюрмации как при наличии в нем устойчивого отказа, так и при наличии сбоя . Однако в известном устройстве недрстаточная достоверность контроля.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля распределителя, содержащее два триггера, два элемента И-НЕ, причем выход первого элемента И-НЕ соединен: с установочным входом первого триггера, выход второго триггера соединен с первым входом второго элемента И-НЕ, введен элемент НЕ, элемент И, элемент 2-2И-ИЛИ-НЕ, элемент задержки, третий триггер и блок формирования остаточного кода по модулю три, входы которого соединены соответственно с выходами контролируемого распределителя, выход нулевого разряда которого соединен с установочным входом второго триггера и входом элемента НЕ, выход которого соединен с входом сброса третьего триггера, прямой выход которого соединен с первым входом элемента 2-2И-ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом элемента задержки, вход которого соединен с выходом элемента И, с синхровходом контрол|1руемого распределителя и с счетным входом третьего триггера, инверсный выход которого соединен с вторым входом элемента 2-2И-ИЛИ-НЕ, третий вход которого соединен с выходом первого разряда блока формирования остаточного кода по модулю три, выход второго разряда которого соединен с четвертым входом элемента 2-2И-ИЛИ-НЕ, инверсный выход первого триггера соединен с первым входом элемента И, второй вход которого является синхровходом устройства, выход которого соединен с прямым выходом первого

триггера. I

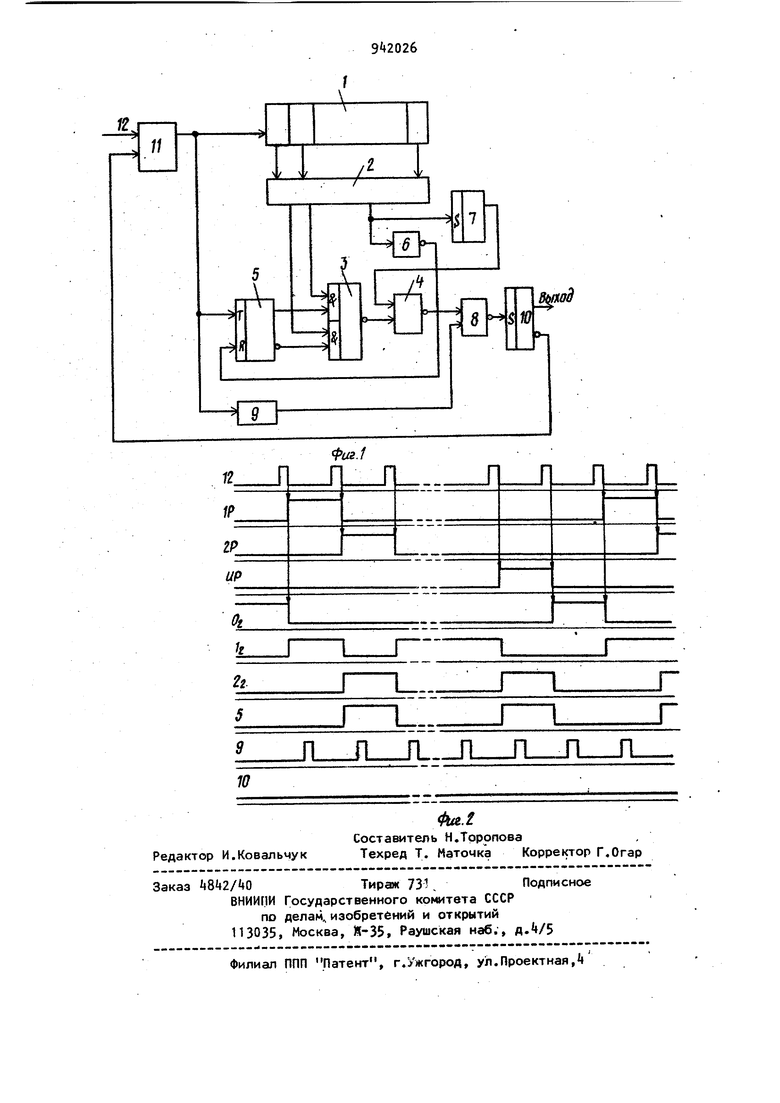

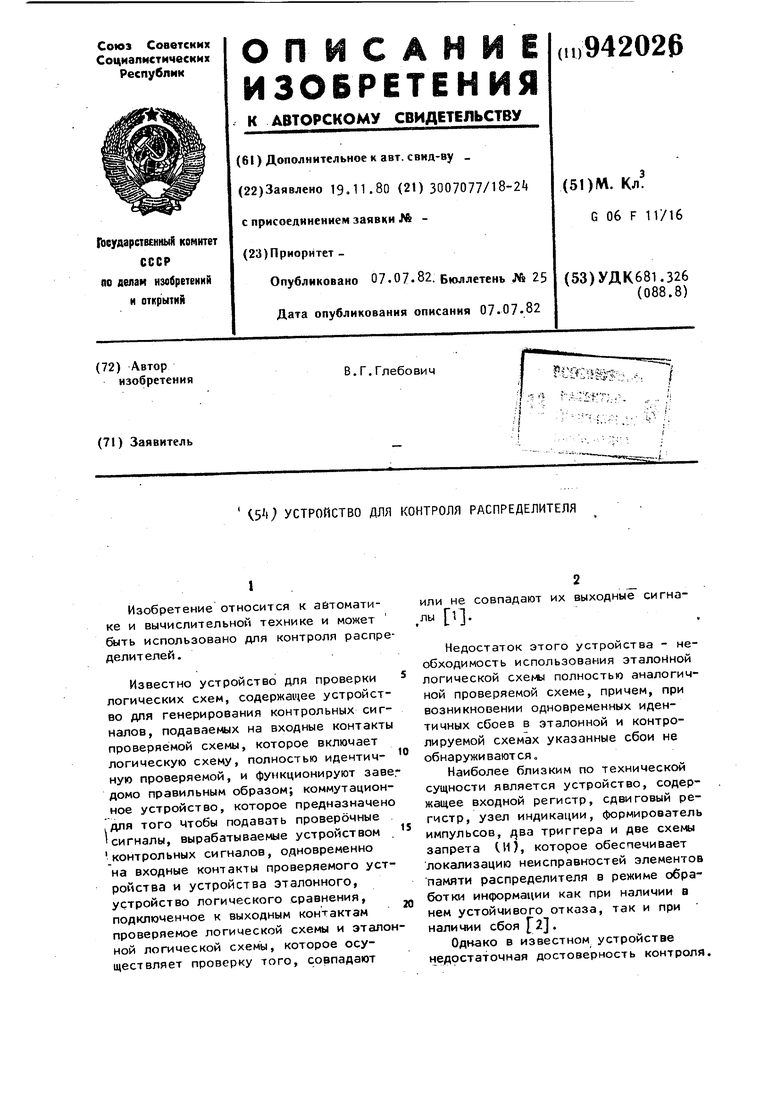

. На фиг.1 приведена схема устройства; на фиг.2 - временная диаграмма.

Устройство содержит контролируемый распределитель 1, блок 2 формирования остаточного кода по модулю три, элемент 2-2И-ИЛИ-НЕ-3, элемент И-НЕ , триггер 5, элемент НЕ 6, триггер 7, элемент И-НЕ 8, элемент 9 задержки, триггер 10, элемент И 11 , синхровход 12 устройства.

Устройство работает следующим образом.

Перед началом проверки распределитель 1, триггеры 5, 7 и 10 устанавливаются в нулевое состояние, (цепи сброса на схеме не показаны.

При этом на нулевом выходе блока 2 формирования остаточного кода по модулю три устанавливается уровень логической единицы, на первом и втором выходах данного блока устанавливаются нулевые логические потенциалы (блок 2 сигнализирует о фактическом или мнимом обнулении элементов памяти распределителя 1), на прямом выходе триггера 10 присутствует нулевой логический потенциал, являющийся признаком исправности конролируемого распределителя, одновременно уровень логической единицы с инверсного выхода данного триггера поступает на вход элемента И 11, тем самым разрешая поступление в устройствопо второмуВХОДУ указанного элемента тактовых импульсов.

С приходом первого тактового импульса по его заднему фронту (все триггеры устройства и распределител пе} еключаются при подаче на их импульсные входы перепада Логическая единица - логический нуль) срабатывает распределитель 1, на выходе младшего разряда которого при этом появляется уровень логической единицы .

При этом на нулевом выходе блока 2 возникает нулевой логический потенциал, на первом выходе - единичный логический потенциал и на втором выходе сохраняется нулевой логический потенциал, причем триггер 5 остается в исходном состоянии так как разрешающий переключение триггера единичный потенциал поступает на его вход сброса с выхода элемента НЕ 6 после завершения первого тактрвого импульса.

При изменении потенциала на нулевом выходе блока 2 с единичного уровня на уровень логического нуля происходит запуск триггера 7, который подает положительный потенциал на вход элемента И-НЕ , разрешая те самым прохождение информации элементу 2-2И-ИЛИ-НЕ 3 на выход устройства

На элементе И-НЕ 8 осуществляется опрос состояния элемента И-НЕ k задержанными на элементе задержки 9 татовыми импульсами, причем к моменту прихода первого задержанного импульса в случае правильной работы распределителя 1 на выходе элемента И-НЕ присутствует нулевой потенциал, вследствие наличия единичного потенциала на выходе элемента 2-2ИИЛИ-НЕ.З.

В указанном случае на входе установки в единичное состояние триггера 10 постоянно имеется единичный потенциал, триггер 10 обнулен и на его выходе присутствует сигнал логического нуля, который является признаком исправности распределителя Второй тактовый импульс устанавливае уровень логической единицы на выходе второго разряда распределителя и переключает триггер 5 в единичное состояние. При этом блок 2 вырабатывает уровень логической единицы на втором выходе и нулевые уровни на нулевом и первом выходах.

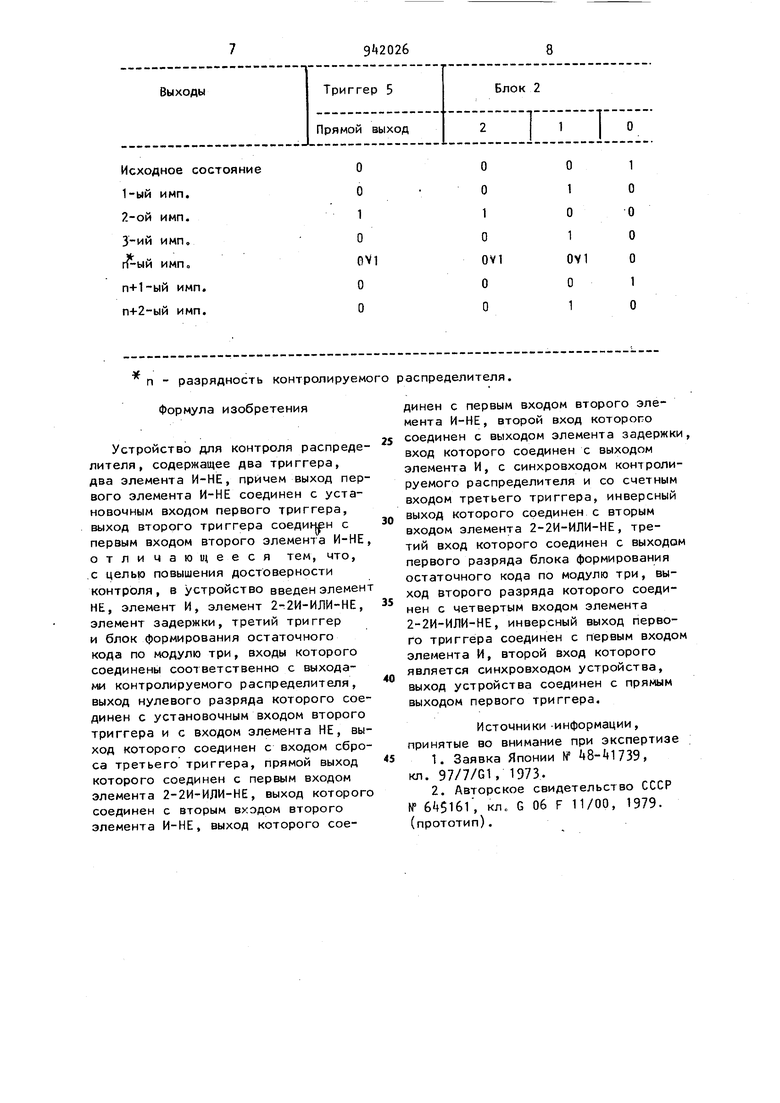

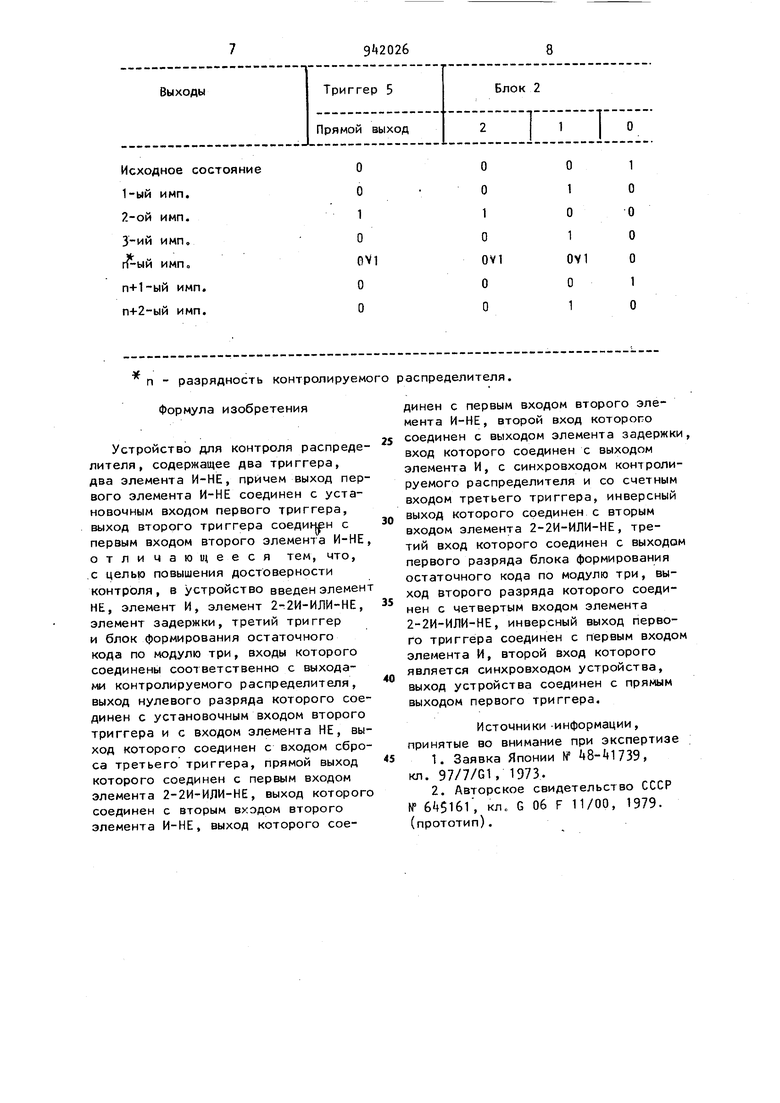

С приходом последующих тактовых импульсов в случае отсутствия сбоев или устойчивых отказов в элементах памяти распределителя 1 состояние триггера 5 Второго и первого выходов разрядов блока 2 синхронно изменяются таким образом, что уровень логической единицы поочередно возникает на выходе второго разряда бло ка 2 на прямом выходе триггера 5, на выходе первого разряда блока 2 и инверсном выходе триггера 5 и т.д. в соответствии с таблицей состояния.

При правильной работе распределителя 1, на выходе элемента 2-2И-2ИЛИНЕ 3 после завершения переходных процессов возникает единичный потенциал. После возникновения логической единицы на выходе старшего разряда распределителя 1 и последующего обнуления элементов памяти распределителя блок 2 формирует единичный уровень на нулевом выходе и нулевые уровни на 1-ом и 2-ом выходах, в результате чего триггер 5 устанавливается в нулевое состояние, которое через один тактовый импульс изменяется на единичное синхронно с появлением уровня логической единицы на втором выходе блока 2. Далее работа устройства продолжается, как описано выше, т.е. циклически повторится и т.д.

При возникновении в распределителе случайного сбоя или отказа в момент сбоя, или чуть позже (в случае если сбой не повлиял на изменение текущего модуля блока 2) . происходит расхождение, рассинхронизация информации триггера 5 и выходов бло ка 2, при этом на выходе элемента 2-2И-ИЛИ-НЕ 3 появляется нулевой логический уровень, который через элемент И-НЕ и поступает уровнем логической единицы на вход элемента И-НЕ 8, разрешая тем самым прохождение через нее задержанных тактовых импульсоВо При этом соответствующий задержанный тактовый импульс проходит элемент И-НЕ, 8 и запускает триггер 10, на прямом выходе которого появляется положительный потенциал, являюи;ийся признаком неисправности контролируемого распределителя. С инверсного выхода триггера 10 в этом случае нулевой логический уровень поступает на вход элемента И 11, что блокирует поступление на вход устройства последующих тактовых импульсов и зафиксирует состояние распределителя 1 в момент сбоя. При отсутствии обнуления или запуска распределителя 1 тактовыми импульсами на нулевом выходе блока 2 не будет единичного потенциала или наоборот, единичный потенциал будет присутствовать постоянно, запуск триггера 7 не произойдет и на входе элемента И-НЕ 8 будет присутствовать единичный потенциал инверсной информации триггера 7 что обнаруживается с приходом задержанного импульса на элемент И-НЕ 8, Еслм при обнулении распределителя 1 в нем возникает текая., например, информация как 110000, модуль которой равен нулю, указанный сбой обнаруживается позже по рассинхрони 39ЦИИ, как отмечего ранее.

Длительность задержки тактовых импульсов на элементе 3 задержки рекомендуется брать большей или равной суммарному времени наиболее длительных переходных процессов в оаспределителе 1. блоке 2, триггере 7 и схеме 2-2И-ИЛИ-НЕ 3.

Таким образом, предлагаемое устройство по сравнению с известными обеспечивает большую достоверность контроля, упрощение устройства,

Формула изобретения

Устройство для контроля распределителя, содержащее два триггера, два элемента И-НЕ, причем выход первого элемента И-НЕ соединен с установочным входом первого триггера, выход второго триггера соединен с первым входом второго элемента И-НЕ отли чающееся тем, что, .с целью повышения достоверности контроля, в устройство введен элемент НЕ, элемент И, элемент 2-2И-ИЛИ-НЕ, элемент задержки, третий триггер и блок формирования остаточного кода по модулю три, входы которого соединены соответственно с выходами контролируемого распределителя, выход нулевого разряда которого соединен с установочным входом второго триггера и с входом элемента НЕ, выход которого соединен с входом сброса третьего триггера, прямой выход которого соединен с первым входом элемента 2-2И-ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, второй вход которого 5 соединен с выходом элемента задержки, вход которого соединен с выходом элемента И, с синхровходом контролируемого распределителя и со счетным входом третьего триггера, инверсный выход которого соединен с вторым входом элемента 2-2И-ИЛИ-НЕ, третий вход которого соединен с выходом первого разряда блока формирования остаточного кода по модулю три, выход второго разряда которого соединен с четвертым входом элемента 2-2И-ИЛИ-НЕ, инверсный выход первого триггера соединен с первым входом элемента И, второй вход которого является синхровходом устройства, выход устройства соединен с прямым выходом первого триггера.

Источники-информации, принятые во внимание при экспертизе 1. Заявка Японии № ,

кл. 97/7/G1, 1973.

2. Авторское свидетельство СССР

№ 6 5161, кл„ G Об F 11/00, 1979. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля распределителя | 1983 |

|

SU1128260A2 |

| Устройство для контроля регистра сдвига | 1981 |

|

SU964646A1 |

| Устройство для отладки вычислительной системы | 1986 |

|

SU1336015A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Устройство для синхронизации с контролем | 1983 |

|

SU1161933A1 |

| Устройство для ввода информации (его варианты) | 1985 |

|

SU1290286A1 |

| Устройство для контроля электромагнита | 1986 |

|

SU1388832A1 |

| Устройство для синхронизации вычислительной системы | 1982 |

|

SU1068921A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для распределения импульсов | 1986 |

|

SU1381467A1 |

Авторы

Даты

1982-07-07—Публикация

1980-11-19—Подача