(54) ЦИФРОВОЕ УСТРОЙСТВО для СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство слежения за задержкой | 1975 |

|

SU555553A2 |

| Цифровое устройство слежения за задержкой | 1975 |

|

SU543184A2 |

| Устройство слежения за задержкой шумоподобных сигналов | 1978 |

|

SU966926A1 |

| Цифровое устройство слежения за задержкой | 1973 |

|

SU467489A1 |

| Цифровое устройство слежения за задержкой псевдослучайной последовательности | 1983 |

|

SU1088146A1 |

| Устройство синхронизации корреляционного приемника псевдослучайных сигналов | 1982 |

|

SU1069182A1 |

| Устройство слежения за задержкой | 1978 |

|

SU849520A1 |

| Цифровое устройство слежения за задержкой псевдослучайных последовательностей | 1975 |

|

SU554630A1 |

| Цифровой некогерентный дискриминатор задержки псевдослучайного радиосигнала | 1983 |

|

SU1131034A2 |

| Цифровое устройство слежения за задержкой | 1977 |

|

SU711696A2 |

1

Изобретение относится к технике ев зи и может быть применено в системах связи и управления, использующих сигналы в виде псевдослучайных последовательностей.

Известно цифровое устройство для слежения за задержкой псевдослучайной последовательности, которое содержит опорный генератор псевдослучайной последовательности, выполненной на регистре сдвн- 10 га с обратной связью, два разряда которого подключены к первым входам двух, перемножителей, вторые входь которых соединены с входной шиной, a выходы подключены к управляющим входам, ре- 15 версивного счетчика и сумматора по мо-. дулю два, выход которого соединен с nejpвым входом элемента И, второй вход которого подключен к выходу кварцевого генератора, a выход соединен со входом реверсивного счетчика, выходы сложения и вычитания которого соединены со входами управляющего элемента, третий вход которого подключен к выходу кварцевого генератора, a выход через делитель соединен со входом опорного генератора || 13 .

Известное устройство при формирова-5нии сигнала рассогласования между входным и опорным сигналами использует отрезоквремени, длительность которого меньше периода псевдослучайной последовательности, что приводит к его недостаточной помехоустойчивости.

Целью изобретения является повышение помехоустойчивости.

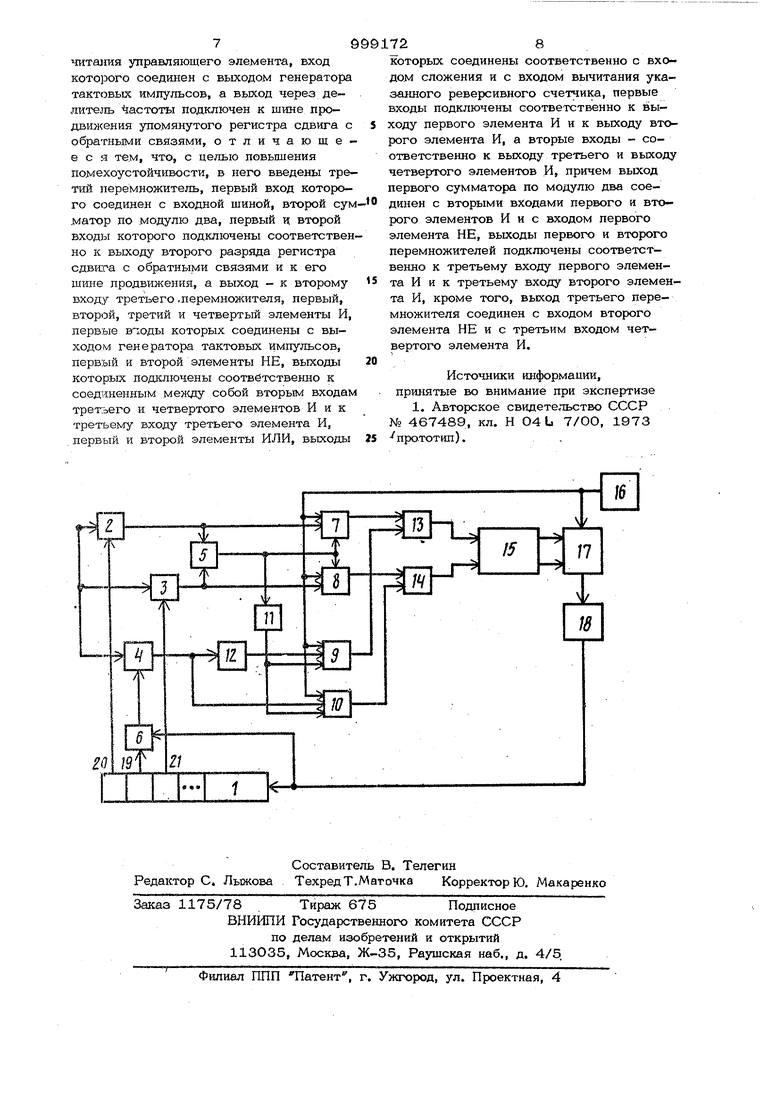

Цель достигается тем, что в цифровое устройство для слежения за задержкой псевдослучайной последовательности, содержащее первый и второй перемножители, первые входы которых соединены с входной шиной, a выходы подключены соответственно к первому н второму входам первого сумматора по модулю два, регистр сдвига с обратными связями, выход первого и выход третьего разрядов кото1Х)ГО соединены соответственно с вторым входом первого перемножителя и с вторым входом второго перемножителя, реверсивный счетчик, выходы сигналов сложения и вычитания которого подключены соответственно к входу сигнало сложения и к входу сигналов вычитания управляющего элемента, вхоа соединен с вьзходом генератора тактовых импульсов, а выход через делитель частоты подключен к щине продвижения упомянутого регистра сдвига с об затными связями, введены третий перемножитель, первый вход которого соединен с входной шиной, второй сумматор по модулю два, первый и второй входы которого подключены соответственн(3 к выходу второго разряда регистр сдвига с обратными связями и к его шине продвижения, а выход - к второму вкокг третьего перемножителя, первый, второй, третий и четвертый элементы И, первые входы которых соединены с выхо дом генератора тактовых импульсов, nep вый и второй элементы НЕ, вькоды кото рых подключены соответственно к соединенным мелоду собой вторым входам третьего и четвертого элементов И и к входу третьего элемента И, первый и второй элементы ИЛИ, выходы которых соединены соответственно с вхо дом сложения и с входом вычитания указанного реверсивного счетчика, первые входы подключены соответственно к выходу первого элемента И и к выходу второго элемента И, а вторые входы - соответственно к выходу третьего и выходу четвертого элементов И, причем выход первого сумматора по модулю лва соединен с вторыми входами первого и второго элемен тов И и с входом первого элемента НЕ, выходы первого и второго перемножителей подключены: соответственно к третьему входу первого элемента И и к третьему входу второго элемента И, кроме того, выход третьего перемножителя соединен с входом второго элемента НЕ и с третьим входом четвертого элемента И. На чертеже представлена функциональ ная схема цифрового устройства для еле жения за задержкой псевдослучайной последовательности. Цифровое устройство для слежения за задержкой псевдослучайной последователь кости содержит опорный генератор 1, вы лолненный в виде регистра сдвига с обратными связями, первый, второй и греги перемножители 2-4, первые входы кот 9 724 рых соединены со входной шиной, первый и второй сумматоры 5 и 6 по модулю два, первый, второй, третий и четвертый элементы И 7 - 10, первый и второй элементы НЕ 11 и 12, первый и второй элементы ИЛИ 13 и 14, реверсивный счетчик 15, входы сложения и вычитания которого соединены соответственно с выходом первого элемента ИЛИ 13 и выходом второго элемента ИЛИ 14, генератор 16 тактовых импульсов, управляющий элемент 17, входы сложения и вычитания которого подключены к выходам сложения и вычитания реверсивного счетчика 15, делитель 18 частоты, вход которого соединен с выходом управляющего элемента 17, а выход подключен к входу продвижения опорного генератора 1 и к второму входу сумматора 6 по модулю два, первый вход которого подключен к выходу 19 второго разряда опорного генератора 1. При этом выход 20 первого и выход 21 третьего разрядов опорного генератора 1 соединены соответственно с вторым входом первого перемножителя 2 и вторым входом второго перемножителя 3, выход первого перемножителя 2 подключен к первому входу первого сумматора 5 по модулю два и к третьему входу перврго элемента И 7, а выход второго перемножителя 3 - к второму входу первого сумматора Б по модулю два и к третьему входу второго элемента И 8. Далее , выход первого сумматора 5 по модулю двасоединен со вторыми входами первого и второго элементов И 7 и 8 непосредственно и через первый элемент НЕ 11 - с вторыми входами третьего и четвертого элементов И 9 и 10, выход третьего перемножителя 4 подключен к третьему входу четвертого элемента И 10 непосредст венно, а к. третьему входу третьего .элемента И через второй элеме нт НЕ 12, выход генератора 16 тактовых импульсов соединен со входом управ; яюйего элемента 17 и с первыми входамипе эвого, второго, тр0теёго и.четвертого элементов И 7 - 10. Кроме того, выход первого элемента PI 7 и выход третьего элемента И 9 подйлючены соответственно к первому и второму входам первого элемента ИЛИ 13, выходы второго элемента И 8 и выход четвертого элемента И 10 соединены соответственно с пер вым и вторым входами второго элемента ИЛИ 14, и выход второго -сумматора 6 по модулю два подюпочен к второму входу третьего перемножителя 4. Цифровое устройство для слежения за задержкой псевдослучайной последователь ности работает следующим образом. Входной сигнал, поступающий на первы входы перемножителей 2--1, перемножаетс в перемножителях 2 и 3 на два смещенных во време ни на 2 такта опорных сигн ла, поступающих соответственно с выходов 20 и 21 первого и третьего разрядов опорного генератора 1 и прецставляю щих собой копии входного сигнала. Кроме того, в перемножителе 4 входной сигнал перемножается на опорный сигнал, поступающий с выхода второго сумматора 6 по модулю два и представляющий собой результат сложения по модулю два копии входного сигнала, поступающей с выхода 19 второго разряда опорного генератора 1, с меандром сигналов продвижения, поступающим с выхода делителя 18 частоты. Сигналы с выходов первого и второго перемножителей 2 и 3 поступают на третьи входы Соответственно первого и второго элементов. И 7 и 8, а с выхо- да третьего перемножителя 4 - на третий вход четвертого элемента И 10 и через элемент НЕ 12 - на третий вход третьего элемента И 9. На первые входы всех четырех элементов И 7 - 10 подаются тактовые импульсы с генератора 16 ргактовых импульсов, С выходов первого и второго перемножителей 2 и 3 сигналы поступают также на входы перво го сумматора 5 ло модулю два. При не- совпадении знаков выходных первого и второго перемложителей 2 и 3 на выходе cyMS-iaTopa 5 по модулю два формируется сигяал, который поступает на вторые входь первого и второго элементов И 7 и 8, также на вход первого элемента НЕ 11; Выходные сигналы первого и второго элементов И 7 и 8 через элементы ИЛИ 13 и 14 поступают соответственно на вход сложения и вход вычитания реверсивного счетчика 15, который, интегрируя разность выходных сигналов первргр и второго перемножи- телей 2 и 3, формирует дискриминационную характеристику. Разрешающий сигнал на вторые -входы третьего и четвертого элементов И 9 и 10 с выхода элемента НЕ 11 подается только тогда, когда не подается разрешающий сигнал на вторые входы первого и второго элементов И 7 и 8. При этом выходные сигналы третьего леремножителя 4 поступают с его выхода на третий вход четвертого элемен- та и 1О непосредственно и на третий вход третьего элемента И 9 через элемент НЕ 12. Выходные сигналы третьего и четвертного элементов И 9 и 1О через элементы ИЛИ 13 и 14 подаются соответственно на вход сложенияи вход вычитания реверсивного счетчика 15. Таким образом, первый и второй перемножители 2 и 3, первый сумматор 5 по модулю два, первый и второй элементы И 7 и 8 и реверсивный счетчик 15 образуют основной дискриминатор, а сумматор 6 по модулю два, третий перемножитель 4, элемент НЕ 12, элементы И 9 и 10 совместно с реверсивньгм счетчиком 15 образуют дополнительный дискриминатор. Основной и дополнительный дискриминаторы, работая поочередно, обеспечивает формирование дискриминационной характеристики. В зависимости от обнаруженного знака рассогласования в управляющем элементе 17 осуществляется добавление или исключение импульсов из последовательности, формируемой генератором 16 тактовых импульсов. Из выходных нмпульсов управляющего элемента 17 делитель 18 частоты формирует сигналы продвижения, поступающие на вход опорнснго генератора 1. Выход 19 второго разряда . опорного генератора 1 является одновременно выходом полезного сигнала. Предлагаемое изобретение позволяет увеличить число выборок входного псевдослучайного сигнала, используемых при его обработке, и тем самым повысить помехоустойчивость цифрового устройства для слежения за задержкой псевдослучайной последовательности. Формула изобретения Цифровое устройство для слежения за задержкой псевдослучайной последовательности, содержащее первый и второй перемножители, первые Kx.oiua которых соединены с входной щиной, а выходы подключены соответственно к первому и второму входам первого сумматора по модулю дьа, регистр сдвига с обратщ 1ми связями, выход первого и выход третьегю разр$здов которого соединены соответственно с вторым входом первого перемножителя и с вторым входом второго пере- множителя, реверсивный счетчик, выходы сигналов сложения и вычитания которого подключены соответственно к входу сигналов сложения и к входу сигналов вычихания управляющего элемента, вход )Го соединен с выходом генератора тактовых импульсов, а выход через делитель lacTOTbi подключен к шине продвижения упомянутого регистра сдвига с обратными связями, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены третий перемножитель, первый вход которого соединен с входной шиной, второй сум матор по модулю два, первый и второй входы которого подключены соответствен но к выходу второго разряда регистра сдБкга с обратными связями и к его шине продвиже} ия, а выход - к второму входу третьего .перемножителя, первый, второй, третий и четвертый элементы И, первые В1ОДЫ которых соединены с выходом генератора тактовых импульсов, первый и второй элементы НЕ, выходы которых подключены соответственно к соединенным мелоду собой вторым входам третьего и четвертого элементов И и к третьему входу третьего элемента И, первый и второй элементы ИЛИ, выходы 9 728 которых соединены соответственно с входом сложения и с входом вычитания указанного реверсивного счетчика, первые входы подключены соответственно к выходу первого элемента И и к выходу второго элемента И, а вторые входы - соответственно к выходу третьего и выходу четвертого элементов И, причем выход первого сумматора по модулю два соединен с вторыми входами первого и второго элементов И и с входом первого элемента НЕ, выходы первого и второго перемножителей подключены соответственно к третьему входу первого элемента И и к третьему входу второго элемента И, кроме того, выход третьего перемножителя соединен с входом второго элемента НЕ и с третьим входом четвертого элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 467489, кл. И О4 L 7/ОО, 1973 про.тотип).

Авторы

Даты

1983-02-23—Публикация

1978-11-01—Подача