Изобретение относится к вычислительной технике и может быть использовано в системах передачи и преобразования цифровых данных для получения по выбору одного или нескольких объединенных последовательно цифровых сигналов в последовательном коде на L выходах от M цифровых источников с параллельным кодом на входе, с возможностью свободного перераспределения числа названных входных сигналов между выходами либо исключения любого из них (или любой их группы) из цифровой последовательности на соответствующем выходе при адекватном изменении скорости передачи в нeм.

Известен преобразователь параллельного кода в последовательный (см. авторское свидетельство СССР N(12) A2(II)1603529, 1988), который формирует один цифровой поток на своем выходе из M сигналов на своих входах. При этом названный преобразователь кода содержит регистр сдвига, первый и второй дешифраторы нуля, первый дешифратор, коммутатор (мультиплексор), первый и второй генераторы импульсов, триггер и элемент ИЛИ, информационные и установочный (управляющий) входы, информационный, первый управляющий и второй управляющий выходы преобразователя, второй дешифратор, счетчик, одновибратор, элемент задержки, выходы формата кода преобразователя.

Однако этот преобразователь имеет недостатки, заключающиеся в том, что его использование ограничивается одним исходящим направлением передачи и при этом скорость передачи в нем фиксирована. Названные недостатки существенно сужают область использования преобразователя. Так, при применении преобразователя в цифровых средствах многоканальной радиосвязи возможна одновременная его работа только в одном направлении, естественно, при выполнении требований к энергетике линии и к качеству передачи. Тем самым значительно ограничиваются возможности по созданию коммутируемой коммуникационной сети. Кроме того, число входов в данном устройстве тоже фиксировано, что также ограничивает его область применения.

Наиболее близким по технической сущности аналогом к предлагаемому устройству является преобразователь параллельного кода в последовательный (см. авторское свидетельство СССР N 1425848, (51) МКИ H 03 M 9/00, 1987), содержащий регистр сдвига, счетчик, генератор импульсов, информационные входы и приоритетный шифратор. Выход генератора импульсов соединен с тактовым входом счетчика и тактовым входом регистра сдвига, информационные входы которого соединены с информационными входами преобразователя. Информационный выход преобразователя соединен с выходом регистра сдвига, а выход начала формата преобразователя соединен с управляющим входом генератора импульсов и выходом заема счетчика. С целью повышения быстродействия введен приоритетный шифратор, информационные входы которого соединены с информационными входами преобразователя, а выходы приоритетного шифратора соединены с информационными входами счетчика и выходами формата преобразуемого кода преобразователя.

Данный преобразователь имеет высокое быстродействие и позволяет получить на выходе один последовательный цифровой сигнал преобразовывая n-разрядный информационный сигнал в параллельном коде на входе.

Недостаток описанного устройства-прототипа заключается в том, что оно имеет узкую область применения. Обусловлено это тем, что оно имеет одно исходящее направление (с последовательным цифровым сигналом) и фиксированную скорость передачи. Кроме того, его внутренняя структура жестко фиксирована, что не позволяет осуществлять функциональную адаптацию данного устройства к прозрачным каналам, предоставляемым первичной сетью связи при переменном их числе и изменяющейся величине пропускной способности. Под прозрачными каналами понимаются разнородные широкопoлосные асинхронные каналы, способные обеспечивать передачу информации в широком диапазоне скоростей от "0" до "Cmax", где "Cmax" - максимально допустимая скорость передачи по широкополосному каналу, определяемая теоремой Шеннона [4].

Целью изобретения является расширение возможной области применения преобразователя параллельного кода в последовательный путем реализации функциональной возможности оперативно перераспределять исходящие информационные потоки между несколькими прозрачными каналами, предоставляемыми первичной сетью связи при переменном их числе и изменяющейся величине максимальной пропускной способности.

Поставленная цель достигается тем, что в известном преобразователе параллельного кода в последовательный, содержащем генератор импульсов, 1-й регистр сдвига, информационный вход которого является информационным входом преобразователя и первый счетчик, дополнительно введены первый, второй, третий, четвертый коммутаторы, M-1 регистров сдвига, L-1 счетчик и L D-триггеров, где M ≥ L и M=2,3,..., а L=2,3,..., k стробирующих выходов генератора импульсов подключены к соответствующим k стробирующим входам второго коммутатора. k тактовых выходов генератора импульсов подключены к соответствующим k тактовым входам первой группы тактовых входов первого коммутатора. i-й тактовый вход второй группы тактовых входов первого коммутатора, i=1,2,. . . , M, подключен к тактовому выходу i-1-го регистра сдвига. Информационный выход i-го регистра сдвига подключен к i-му информационному входу четвертого коммутатора. j-й выход четвертого коммутатора, j=1,2,...,L, подключен к D-входу j-го D-триггера. К C-входу j-го D-триггера подключен j-й выход второго коммутатора, он же подключен к входу j-го счетчика. Адресный выход j-го счетчика подключен к j-му адресному входу третьего коммутатора. i-й адресный выход третьего коммутатора подключен к адресному входу i-го регистра сдвига. Тактовый вход i-го регистра сдвига подключен к i-му тактовому выходу первого коммутатора. Причем информационные входы M регистров сдвига являются M информационными входами преобразователя, а выходы D-триггеров являются L информационными выходами преобразователя.

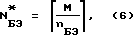

Важной особенностью заявляемого преобразователя параллельного кода в последовательный является то, что в нем каждый регистр сдвига состоит из тактируемого параллельного регистра и мультиплексора. Информационный выход i-го тактируемого параллельного регистра подключен к информационному входу i-го мультиплексора. Управляющий выход i-го мультиплексора подключен к управляющему входу i-го тактируемого параллельного регистра. В свою очередь управляющий выход тактируемого параллельного регистра подключен к управляющему входу мультиплексора. Информационный вход тактируемого параллельного регистра является информационным входом регистра сдвига, а тактовый вход тактируемого параллельного регистра является тактовым входом регистра сдвига. Тактовый выход тактируемого параллельного регистра является тактовым выходом регистра сдвига, а адресный вход мультиплексора является адресным входом регистра сдвига. Информационный выход мультиплексора является информационным выходом регистра сдвига.

Благодаря новой совокупности существенных признаков, заключающихся во введении новых информационных и управляющих связей между элементами преобразователя, появляется возможность получить несколько (L) последовательностей цифровых сигналов на его выходах, с произвольным их числом и произвольной переадресацией между ними входных сигналов.

Естественно, что предельная скорость передачи информации, реализуемая на отдельном выходе конкретной функциональной структуры преобразователя будет определяться известными ограничениями теоремы Шенона [4], а также конкретными возможностями каналообразующих средств, наличием и характером помех на линиях связи.

Преобразователь параллельного кода в последовательный позволяет оперативно распределять исходящие информационные потоки между несколькими прозрачными каналами, предоставляемыми первичной сетью связи при переменном их числе и изменяющейся величине максимальной пропускной способности.

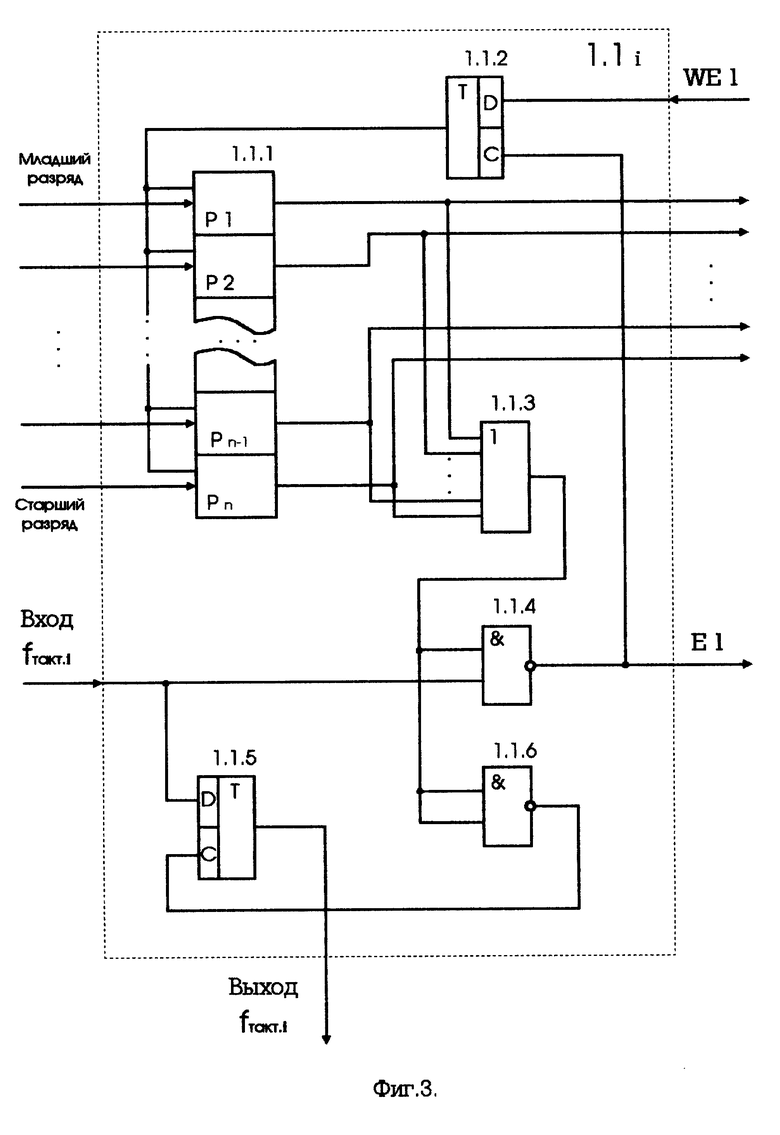

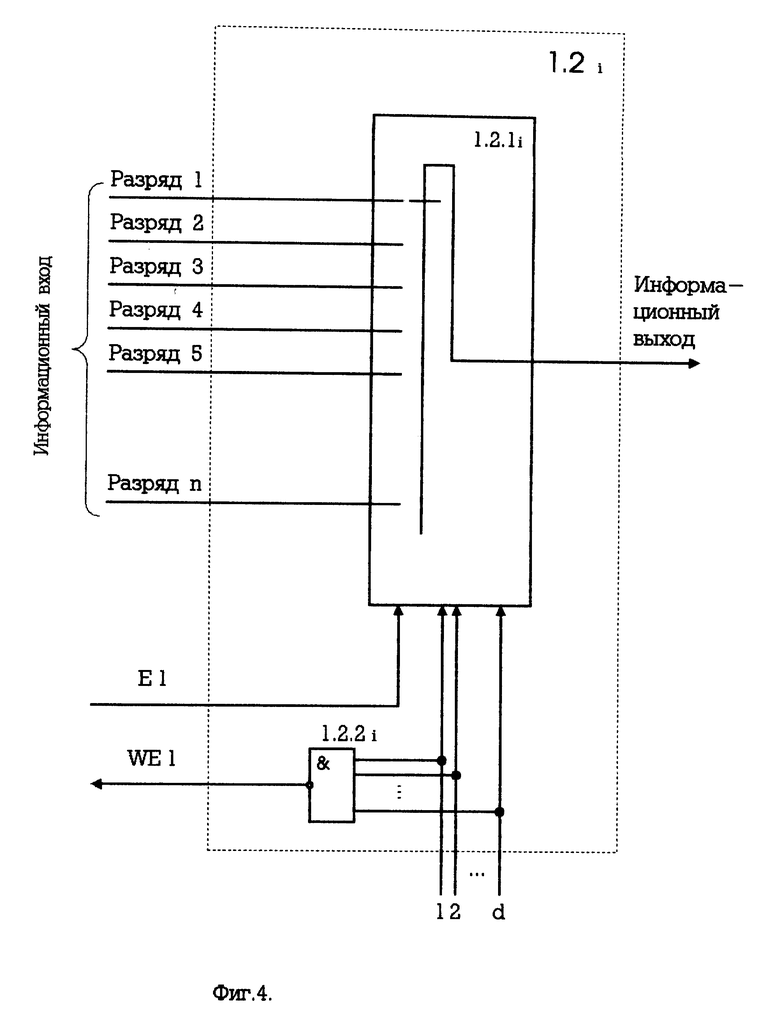

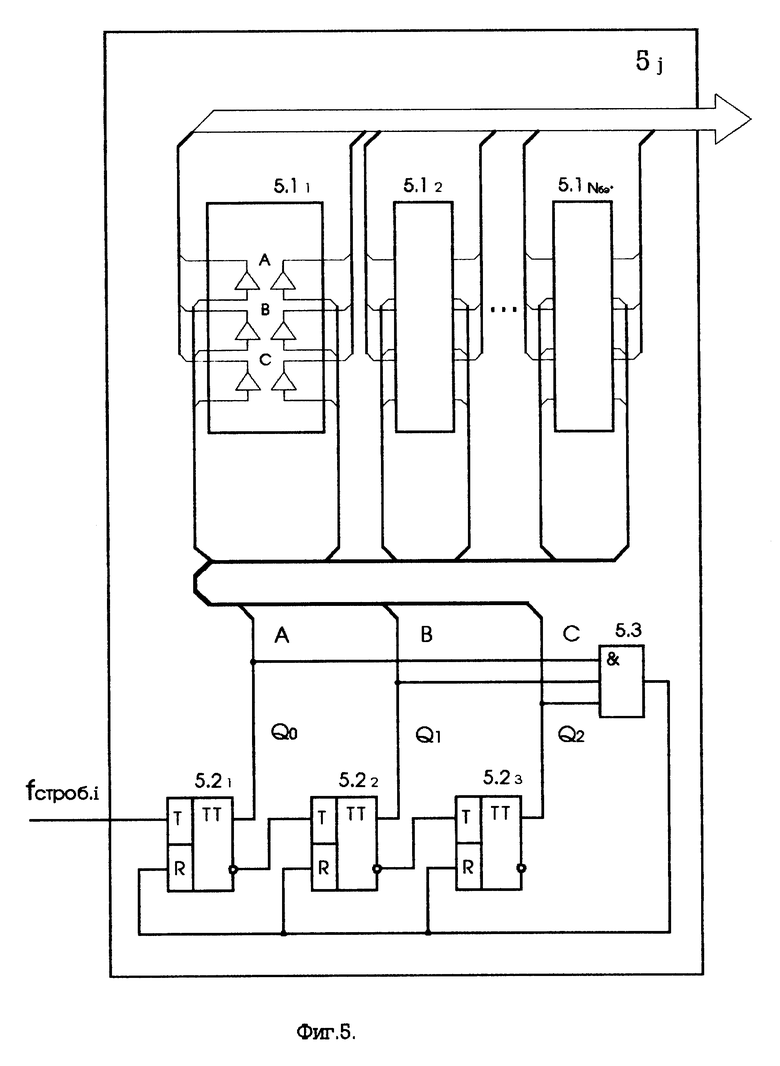

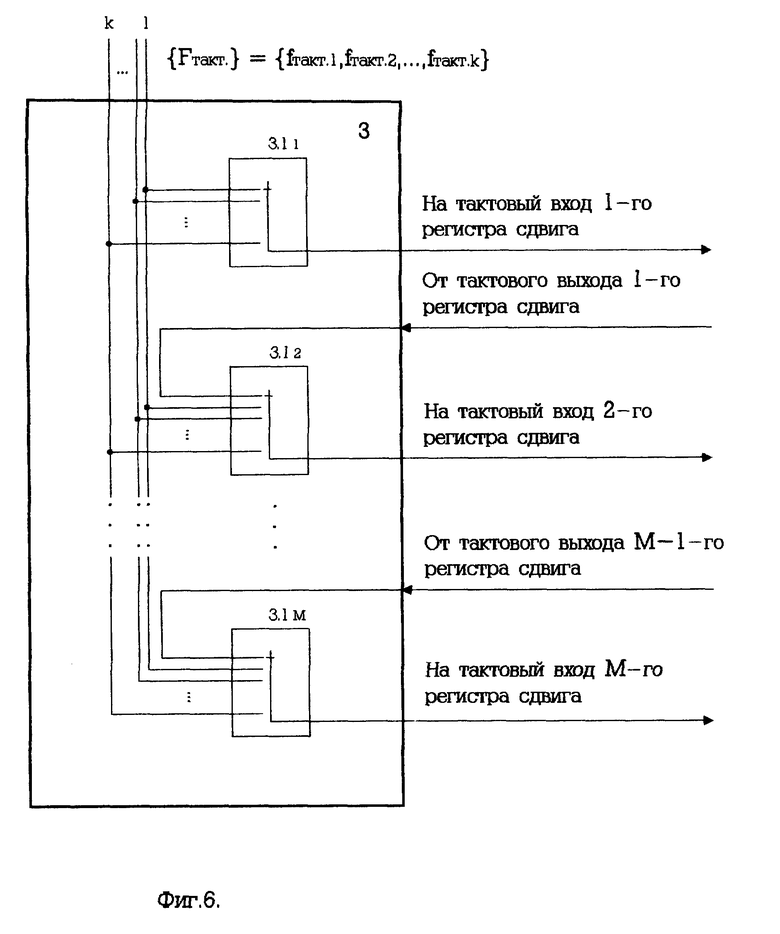

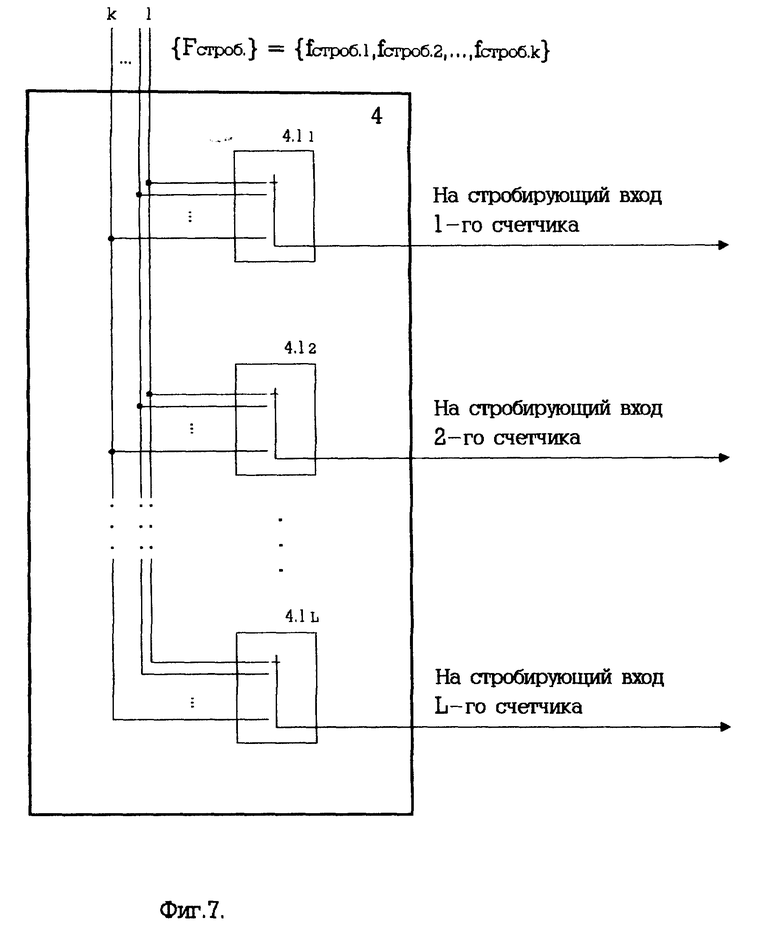

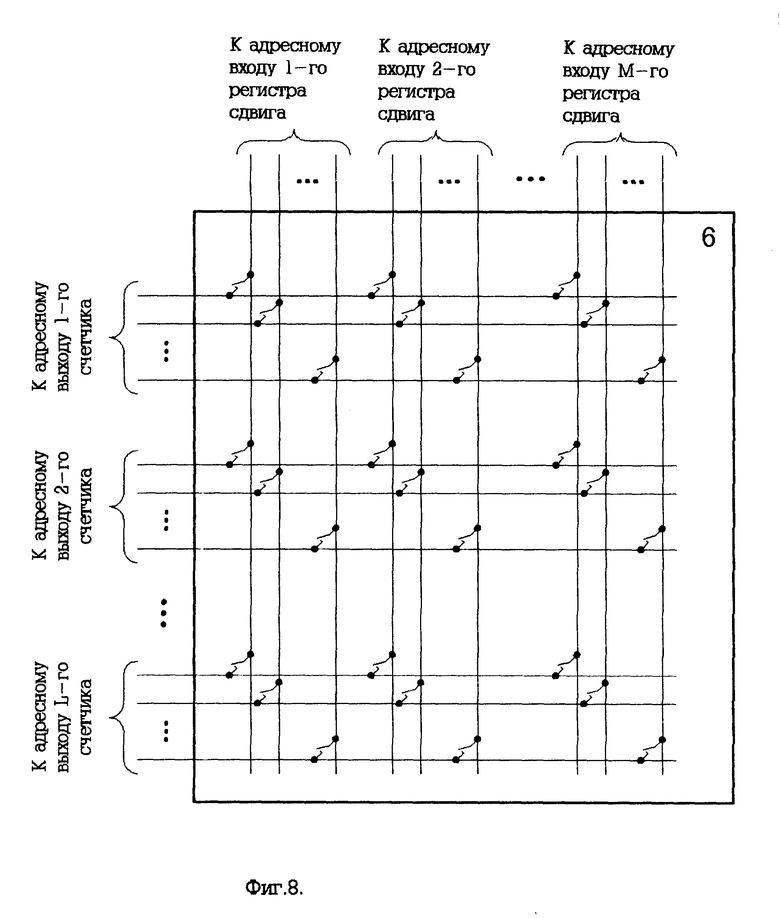

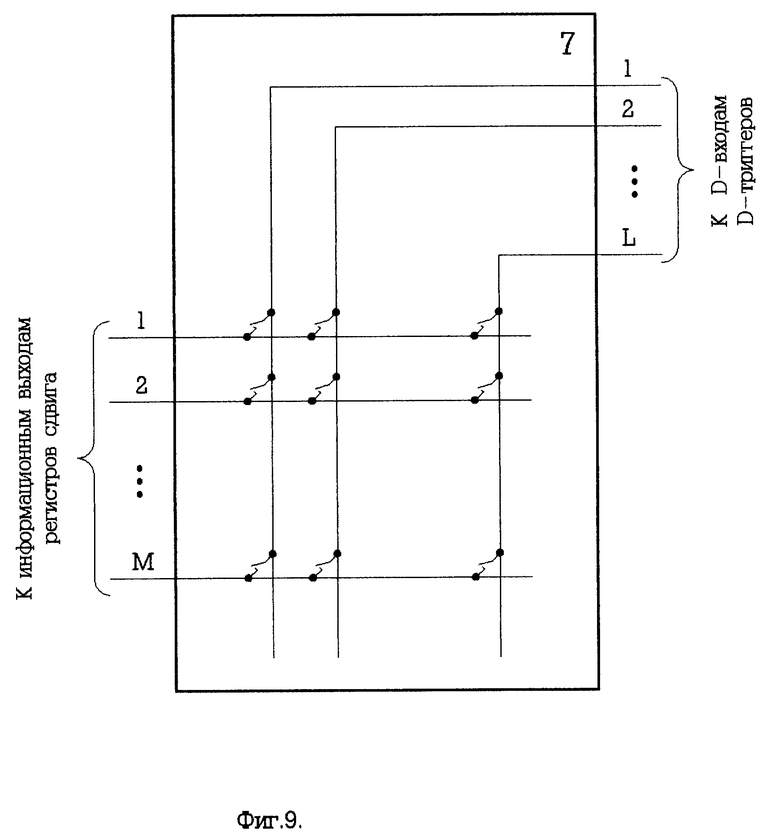

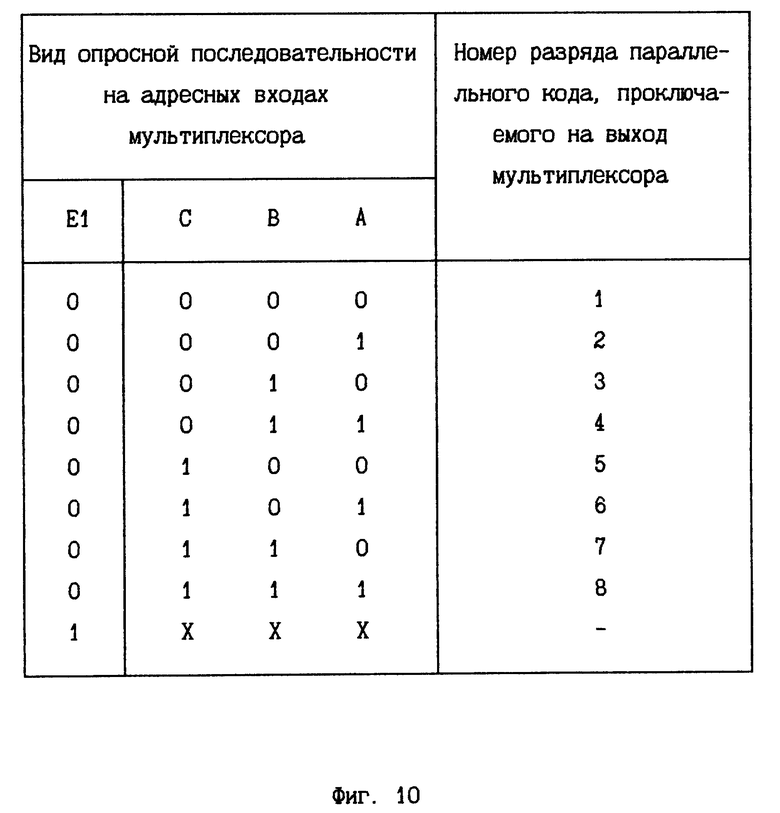

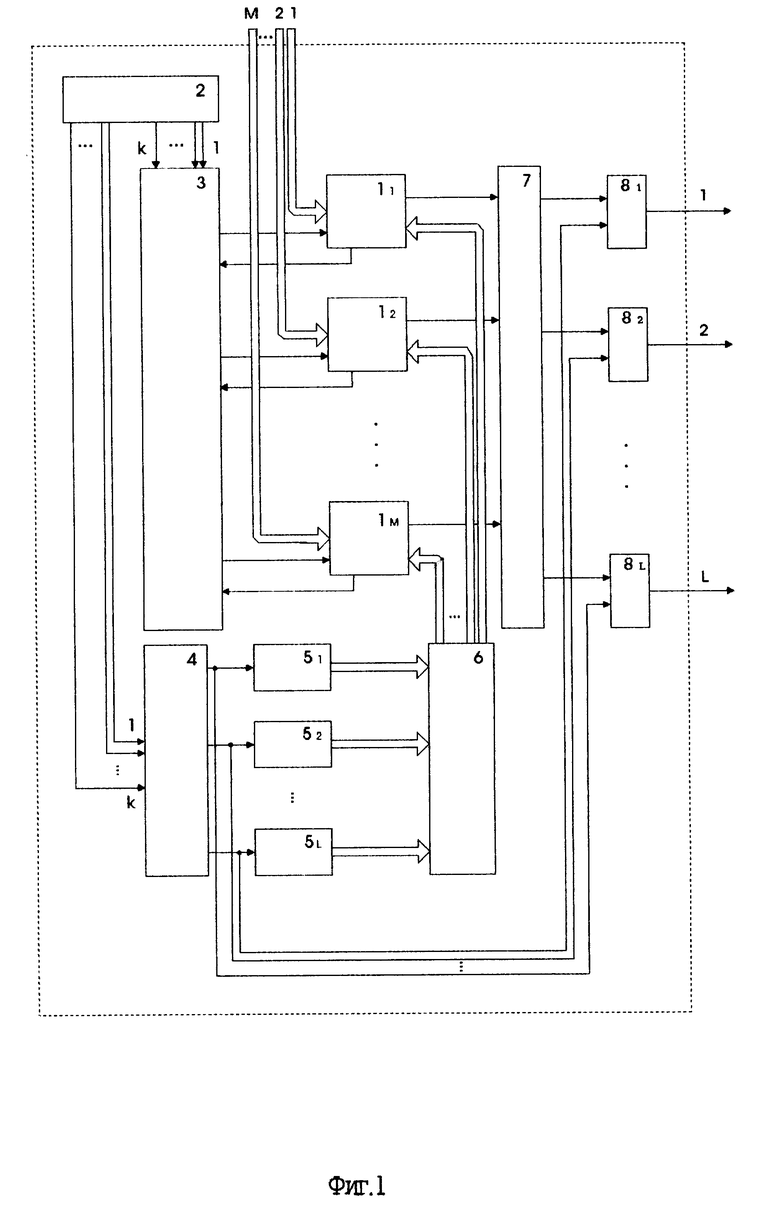

Заявленное устройство поясняется чертежами, где на фиг. 1 дана общая функциональная схема преобразователя параллельного кода в последовательный; на фиг. 2 - функциональная схема регистра сдвига; на фиг. 3 - функциональная схема параллельного (буферного) регистра; на фиг. 4 - функциональная схема мультиплексора; на фиг. 5 - функциональная схема счетчика; на фиг. 6 - функциональная схема первого коммутатора; на фиг. 7 - функциональная схема второго коммутатора; на фиг. 8 - функциональная схема третьего коммутатора; на фиг. 9 - функциональная схема четвертого коммутатора; на фиг. 10 - таблица соответствия кода адресных входов мультиплексора порядковому номеру прoключаемого на выход разряда преобразуемого параллельного кода.

Заявленное устройство, показанное на фиг. 1, состоит из M регистров сдвига 1 (1i - 1m), генератора импульсов 2, первого 3, второго 4, третьего 6 и четвертого 7 коммутаторов, L счетчиков 5 (51 - 5L), L D-триггеров 8 (81 - 8L).

При этом k стробирующих выходов генератора импульсов 2 подключены к соответствующим k стробирующим входам второго коммутатора 4, а k тактовых выходов генератора импульсов 2 подключены к первой группе соответствующих k тактовых входов первого коммутатора 3, i-й тактовый выход первого коммутатора 3, i=1,2,...,M, подключен к тактовому входу i-го регистра сдвига 1, тактовый выход которого подключен к соответствующему i-му тактовому входу второй группы тактовых входов первого коммутатора 3. Информационный выход i-го регистра сдвига 1 подключен к i-му информационному входу четвертого коммутатора 7, j-й выход четвертого коммутатора 7, j=1,2,...,L, подключен к D-входу j-го D-триггера 8. К C-входу D-триггера 8 подключен j-й выход второго коммутатора 4, который в параллель подключен к входу j-го счетчика 5. Адресный выход j-го счетчика 5 подключен к j-му адресному входу третьего коммутатора 6, i-й адресный выход третьего коммутатора 6 подключен к адресному входу i-го регистра сдвига 1. Информационные входы M регистров сдвига 1 являются M информационными входами преобразователя параллельного кода в последовательный, а выходы D-триггеров 8 являются информационными выходами преобразователя.

M регистров сдвига 1 выполнены идентично, структурная схема регистра сдвига 1 представлена на фиг. 2. Регистр сдвига 1 предназначен для преобразования параллельного кода одного отдельного входного сигнала в последовательный код. Он состоит из тактируемого параллельного регистра 1.1. и мультиплексора 1.2. Информационный вход тактируемого параллельного регистра является информационным входом регистра сдвига 1. Тактовый вход тактируемого параллельного регистра 1.1 является тактовым выходом регистра сдвига 1. Информационный выход тактируемого параллельного регистра соединен с информационным входом мультиплексора 1.2. Управляющий выход E1 тактируемого параллельного регистра 1.1 соединен с управляющим входом мультиплексора 1.2. Управляющий выход WE1 мультиплексора 1.2 соединен с управляющим входом WE1 тактируемого параллельного регистра 1.1. Адресный вход мультиплексора 1.2 является адресным входом регистра сдвига 1, а информационный выход мультиплексора 1.2 является информационным выходом регистра сдвига 1.

Тактируемый параллельный регистр 1.1, схема которого показана на фиг. 3, предназначен для выполнения предварительных операций перед преобразованием параллельного кода отдельных цифровых каналов в объединенную во времени цифровую последовательность и обеспечивает асинхронный характер информационных входов заявляемого преобразователя параллельного кода в последовательный.

Тактируемый параллельный регистр 1.1 имеет в своем составе: n-разрядный параллельный регистр 1.1.1, устройство управления сбросом информации из параллельного регистра после ее прочтения 1.1.2, устройство анализа 1.1.3, устройство формирования команды запрета чтения из параллельного регистра 1.1.4, устройство задержки проключения (УЗП) управляющего импульса 1.1.5, устройство управления задержкой проключения 1.1.6.

Информационный вход тактируемого параллельного регистра 1.1, является n информационными входами n-разрядного параллельного регистра 1.1.1, а n выходов n-разрядного параллельного регистра 1.1.1 являются информационным выходом тактируемого параллельного регистра 1.1 и подсоединены в параллель к входам устройства анализа 1.1.3.

Выход устройства анализа 1.1.3 соединен в параллель со входом устройства формирования команды запрета чтения 1.1.4 из параллельного регистра и устройства управления задержкой проключения 1.1.6. Второй вход устройства формирования команды запрета чтения 1.1.4 из параллельного регистра является тактовым входом тактируемого параллельного регистра 1.1. Выход устройства формирования команды запрета чтения 1.1.4 из параллельного регистра соединен с C-входом устройства управления сбросом информации 1.1.2 из параллельного регистра после ее прочтения и является управляющим выходом E1 тактируемого параллельного регистра 1.1. Выход устройства управления задержкой проключения 1.1.6 соединен с C-входом УЗП 1.1.5. Выход УЗП является тактовым выходом тактируемого параллельного регистра 1.1.

Устройство управления сбросом информации из параллельного регистра 1.1.2 также представляет собой D-триггер. Его D-вход является управляющим входом WE1 тактируемого параллельного регистра 1.1, а выход соединен с асинхронными входами сброса параллельного регистра 1.1.1.

Тактируемый параллельный регистр 1.1, имеющий порядковый номер M, элементов 1.1.5 и 1.1.6 в своем составе не содержит, так как дальнейшее проключение управляющего импульса за пределы рассматриваемого устройства смысла не имеет.

Мультиплексор 1.2, схема которого показана на фиг. 4, предназначен для преобразования параллельного кода из параллельного регистра в последовательный код. Схема мультиплексора состоит из собственно мультиплексора 1.2.1 и элемента И-НЕ 1.2.2. Элемент И-НЕ 1.2.2 в состав мультиплексора 1.2 включен для формирования команды сброса WE-1 параллельного регистра после окончания опросного цикла. Информационный вход стандартного мультиплексора 1.2.1 имеет n разрядов [1, стр. 222] и является информационным входом мультиплексора 1.2. Адресные входы стандартного мультиплексора 1.2.1 соединены в параллель с входами элемента И-НЕ 1.2.2, являются адресными входами мультиплексора 1.2, и имеют разрядность d = ┌log2n┐ (где ┌ ┐ - оператор округления до ближайшего целого числа вверх по числовой оси).

Информационный выход стандартного мультиплексора 1.2.1 является информационным выходом мультиплексора 1.2. Вход разрешения E1 стандартного мультиплексора 1.2.1 является управляющим входом мультиплексора 1.2.

Первый коммутатор 3, схема которого представлена на фиг. 6, предназначен для обеспечения проключения выбранных тактовых импульсов fтакт.1 на первый из выделенных в общую функциональную группу регистров сдвига 1. Кроме того, он выполняет функцию взаимного сочленения соседних, в рамках выделенной функциональной группы, регистров сдвига 1 в интересах формирования объединенного последовательного цифрового кадра от названной группы.

Первый коммутатор 3 реализуется на основе M мультиплексоров 3.1 [1, стр. 222], k входов каждого из которых соединены с параллельной шиной, на которую через первую группу тактовых входов первого коммутатора 3 подана первая группа тактовых импульсов от генератора импульсов 2. Тактовые выходы регистров сдвига 1 соединены с второй группой тактовых входов первого коммутатора 3, являющихся k+1-ми входами 2-го, 3-го, ..., M-1-го и M-го его мультиплексоров 3.1. Соединение соседних по выделенной группе регистров сдвига 1 в единую функциональную группу осуществляется за счет проключения i+1-ми мультиплексорами тактовых выходов i-х регистров сдвига 1 на тактовые входы i+1-х регистров сдвига 1.

Второй коммутатор 4, схема которого представлена на фиг.7, предназначен для обеспечения проключения стробирующих импульсов fстроб.1 на j-й счетчик 5, выбранный для работы в единой функциональной группе с соответствующими регистрами сдвига 1. Он имеет только одну группу входов и L мультиплексоров 4.1 в своем составе. Его мультиплексоры 4.1 имеют k входов, соединенных с параллельной шиной, на которую через соответствующие стробирующие входы (1,2, . . .,k) второго коммутатора 4 подается полная группа стробирующих импульсов от генератора импульсов 2. Выходы мультиплексоров 4.1 являются выходами второго коммутатора 4.

Счетчик 5 предназначен для работы с n-битными цифровыми сигналами. На фиг. 5 представлен вариант его возможной реализации, предназначенный для работы с 8-битными информационными сигналами. Он представляет собой суммирующий последовательный (асинхронный) счетчик, выполняющий прямой счет [3, стр.216] и выполнен с использованием T-триггеров.

Счетчик 5 состоит из следующих элементов: 5.1 - буферные усилители тока без инверсии, 5.2 - T-триггеры, 5.3 - формирователь сигнала сброса счетчика. T-вход первого T-триггера 5.21 является стробирующим входом счетчика 5, инверсный выход первого T-триггера 5.21 соединен с T-входом второго T-триггера 5.22, инверсный выход которого в свою очередь соединен с T-входом третьего T-триггера 5.23. R-входы T-триггеров 5.2 соединены между собой и с выходом формирователя сигнала сброса счетчика 5.3. Формирователь сигнала сброса счетчика 5.3 представляет собой логический элемент ИЛИ, входы которого соединены с неинверсными выходами T-триггеров 5.2 и в параллель с входами буферных усилителей тока без инверсии 5.1. Выходы буферных усилителей тока без инверсии 5.1 являются адресными выходами счетчика 5.

Третий коммутатор 6, схема которого представлена на фиг.8, предназначен для соединения адресных выходов j-х счетчиков 5 с соответствующими адресными входами объединенных с ними в j-ю функциональную группу регистров сдвига 1. Он представляет собой коммутационную матрицу емкостью L•M•d, где d = ┌log2n┐ - требуемая разрядность адресного кода на выходе счетчика (округление получившегося значения до ближайшего целого числа производится в большую сторону). Третий коммутатор 6 также может быть реализован с использованием рассмотренныx выше мультиплексоров [1, стр.222]. Их контактные группы в коммутационной матрице располагаются таким образом, чтобы обеспечивать возможность подразрядного проключения адресного кода с адресных выходов счетчиков 5 на адресные входы регистров сдвига 1. Т.е. контактные группы, соответствующие каждой из вертикальных шин, соответствуют контактным группам отдельного мультиплексора, при этом его входы соединяются с горизонтальными шинами, а выход - с одной из вертикальных, и представляет собой один из разрядов адресного выхода третьего коммутатора 6. Горизонтальные шины соединены с его соответствующими адресными входами, а вертикальные - с его соответствующими адресными выходами.

Четвертый коммутатор 7, схема которого представлена на фиг.9, предназначен для обеспечения проключения на D-входы любого из D-триггеров 8 от 1-го до M информационных выходов регистров сдвига 1. Контактные группы в его коммутационной матрице располагаются таким образом, чтобы обеспечивать возможность параллельного соединения информационных выходов регистров сдвига 1, выделенных для объединения в единую функциональную группу. Т.е. контактные группы, соответствующие каждой из горизонтальных шин, соответствуют контактным группам отдельного мультиплексора, при этом его входы соединяются с вертикальными шинами, а выход - с одной из горизонтальных. Т.e. здесь мультиплексоры используются в качестве демультиплексоров, что вполне допустимо в силу того, что они являются обратимыми многополюсниками [1, стр.222]. Горизонтальные шины соединены с соответствующими входами четвертого коммутатора 7, а вертикальные - с его соответствующими выходами.

D-триггеры 8 [1, стр. 74] обеспечивают синхронную с подаваемыми на их C-выходы (тактовые входы) стробирующими импульсами fстроб.1 работу информационных выходов заявляемого преобразователя параллельного кода в последовательный. Это позволяет нормализовать взаимное расположение отдельных n-разрядных цифровых пакетов на временной оси на выходах преобразователя за счет передачи сигнала от D-входов D-триггеров 8 на их выходы по положительным перепадам стробирующих импульсов.

Входящие в общую схему остальные элементы известны. Так, входящий в состав преобразователя генератор импульсов 2 состоит из k однотипных генераторов [5, стр.415] и k делителей частоты [1, стр.230-234] с переменным коэффициентом деления n.

Элементы предлагаемого устройства являются типовыми [1, 2, 3] и могут быть технически реализованы при использовании современной элементной базы. При этом конкретные значения граничных возможностей реализуемого устройства выбираются исходя из показателей обслуживаемых информационных потоков, характера их направленности и прогнозируемого неблагоприятного воздействия на реализуемую систему связи.

Заявляемый преобразователь работает следующим образом.

Пусть на i-й информационный вход преобразователя подается n-разрядный параллельный цифровой сигнал. Попав на тактируемый параллельный регистр 1.1i i-го регистра сдвига, он записывается в соответствующие ячейки параллельного регистра 1.1.1i.

Наличие (на момент считывания) записанной в параллельные регистры 1.1.1 информации упрощает в дальнейшем взаимную синхронизацию индивидуальных канальных пакетов на временной оси, а также позволяет достаточно просто реализовать необходимую группу команд для управления параллельно-последовательным преобразованием.

Устройство анализа 1.1.3, выполненное на основе элемента ИЛИ и имеющее число входов n - равное разрядности используемого параллельного канального кода, формирует на своем выходе сигнал логической единицы, когда в параллельном регистре имеется хотя бы один значимый разряд (есть записанная информация). Отсутствию записи в параллельном регистре соответствует наличие логического нуля на выходе устройства анализа.

Тактовый импульс, определяющий длину последовательного информационного пакета на последовательном информационном выходе преобразователя, поступив на один из входов элемента И-НЕ 1.1.4, в сочетании с логической единицей с выхода устройства анализа 1.1.3 на его другом входе, приведет к появлению логического нуля на управляющем выходе E1 параллельного регистра. Этим сигналом будет разрешено считывание из i-го тактируемого параллельного регистра соответствующему мультиплексору. Одновременно низкий логический уровень с выхода элемента 1.1.6 (И-НЕ) не позволит осуществить прохождение тактового импульса на выход устройства УЗП 1.1.5. УЗП представляет собой D-триггер [1].

Появление логической единицы на выходе WE1 соответствующего мультиплексора соответствует считыванию последнего разряда из параллельного регистра 1.1.1. Этим сигналом параллельный регистр сбрасывается и до окончания импульса WE1 имеет низкие логические уровни на всех своих выходах. В результате этого на выходе элемента 1.1.3 (устройства анализа) формирует сигнал логического нуля, что в свою очередь приводит к формированию на выходе E1 высокого логического уровня, запрещающего дальнейшее считывание соответствующему мультиплексору, а на входе C УЗП 1.1.5 - разрешающего сигнала на проключение управляющего импульса на следующий (i+1-й) трактируемый параллельный регистр.

Теперь рассмотрим ситуацию, когда в i-ом параллельном регистре 1.1.1 на момент прихода тактового импульса информация отсутствует. Соответственно на выходе устройства анализа 1.1.3 получим низкий логический уровень, что соответствует запрету считывания по линии E1 и ждущему режиму УЗП 1.1.5. Таким образом, тактовый импульс сразу же после прихода на i-е УЗП будет подключен на следующий импульс (i+1-й) параллельный регистр.

Мультиплексор 1.2 осуществляет непосредственное преобразование i-го сигнала, записанного в ячейки i-го параллельного регистра 1.1.1i, считывая находящуюся в них информацию. Порядок считывания определяется j-м счетчиком 5, который генерирует адресные коды опроса, управляющие состоянием мультиплексора 1.2.

К примеру, восьмиканальный вариант мультиплексора 1.2.1 управляется трехразрядным адресным кодом. При этом команда сброса WE1 на выходе элемента И-НЕ 1.2.2, являющимся управляющим выходом мультиплексора 1.23, формируется при поступлении на все адресные входы 1, 2,...d высокого логического уровня, что соответствует считыванию последнего разряда из параллельного регистра 1.1.1.

Если на линии E1 присутствует высокий логический уровень, то все контактные группы стандартного мультиплексора 1.2 размыкаются [1, стр.223] и считывание сигнала им не производится. Тем самым осуществляется развязка последовательных сигналов одной функциональной группы на временной оси.

Генератор импульсов 2 обеспечивает синхронность процесса преобразования параллельного кода в последовательный код. С его выходов на 1-й коммутатор 3 подаются две взаимокоррелированные группы импульсов: тактовые импульсы { Fтакт} и стробирующие импульсы {Fстроб}.

{Fтакт} = {fтакт1, fтакт2,..., fтактk}

{Fстроб} = {fстроб1, fстроб2,..., fстробk} (1)

где

k - число скоростей передач на последовательных выходах, используемое в данном преобразователе параллельного кода в последовательный.

Т. к. предлагаемый преобразователь параллельного кода в последовательный должен позволять одновременно формировать на своих выходах последовательные цифровые потоки с любой из k различных скоростей передачи, то в составе генератора импульсов 2 предлагается иметь k стробирующих генераторов, обеспечивающих формирование соответствующей группы стробирующих импульсов { Fстроб} . Коррелированную с ним группу тактовых импульсов {Fтакт} предлагается получать путем деления соответствующих стробирующих последовательностей fстроб1 с помощью делителей с переменным коэффициентом деления - n, где n - разрядность используемого цифрового кода. Тем самым будет обеспечена взаимная синхронизация стробирующих и тактовых импульсов.

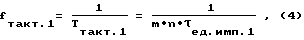

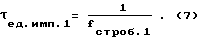

Таким образом, частоты тактовых и стробирующих импульсов соотносится в соответствии с выражением:

fтакт1 = m • n • fстроб1 (2)

или

tтакт.1= n•τед.имп.1, (3)

соответственно

Tтакт1 = m • tтакт1

где

Tтакт1 - период тактовых импульсов, определяющий длину объединенного последовательного кадра на j-м выходе преобразователя;

m - число тактовых импульсов, объединяемых в групповом последовательном кадре;

n - разрядность используемого цифрового кода;

tтакт1 - длительность тактового импульса, определяющего длину отдельного последовательного кадра на j-м последовательном выходе преобразователя (т.е. время опросного цикла одного параллельного регистра);

τед.имп.1 - длительность единичного импульса на j-м последовательном выходе преобразователя;

l - номер выбранной частоты тактовых (стробирующих) импульсов.

Работоспособность устройства преобразования параллельного кода в последовательный будет гарантирована при выполнении условия:

τз.сумм.max≪ τед.имп.min, (5)

где

τз.сумм.max - совокупное время задержки подключения управляющего импульса внутри наибольшей из возможных функционально объединенных групп регистров сдвига при отсутствии в них записанной информации;

τед.имп.min - длительность элементарной посылки в наиболее высокоскоростном из возможных последовательных выходных сигналов.

Таким образом, верхний порог скорости передачи информации с выхода преобразователя параллельного кода в последовательный будет ограничен показателями быстродействия используемой элементной базы.

Первый 3, второй 4, третий 6 и четвертый 7 коммутаторы позволяют сформировать из перечисленных выше функциональных узлов одновременно одну или L возможных функциональных структур преобразователя параллельного кода в последовательный.

Счетчик 5 обеспечивает формирование адресного опросного кода с скоростью, соответствующей частоте стробирующих импульсов. На фиг.10 представлена таблица, в соответствии с которой счетчик 5 формирует на своих адресных выходах опросный код. Его работа подробно описана в [5, стр.390-393], поэтому подробнее остановимся только на ситуациях, когда опросный цикл завершается.

При подаче на вход T первого T-триггера 5.21 последнего (восьмого) по счету импульса fстроб1 производится сброс счетчика в исходное состояние Q0Q1Q2 = 000 (см. таблицу на фиг.10). Это происходит следующим образом: элемент 5.3 формирует сигнал сброса счетчика 5 при появлении на всех его адресных выходах логической единицы Q0Q1Q2=111, тем самым завершая полный опросный цикл i-го регистра сдвига 1 в соответствии с приведенной на фиг.10 таблицей.

Так как по параллельной адресной (опросной) шине к одному счетчику 5 может быть подсоединено до M регистров сдвига 1, то при больших значениях M возможна его перегрузка. Для предотвращения перегрузки предлагается в составе счетчика 5 иметь буферные усилители тока без инверсии 5.1, усиливающие импульсы адресного кода (кода опроса) по току [1, стр.27]. Необходимое число буферных элементов NБЭ* определяется из выражения:

где

nБЭ - допустимая (паспортная) нагрузочная способность буферного усилителя тока без инверсии;

┌ ┐ - - оператор округления до ближайшего целого числа вверх по числовой оси.

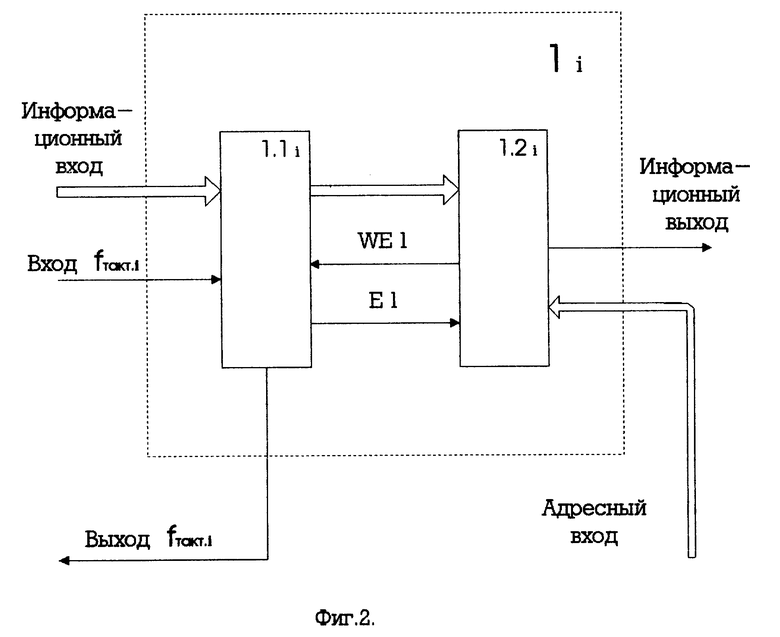

В зависимости от выбранного максимального числа L - последовательных выходов преобразователя параллельного кода в последовательный код выбирается число используемых счетчиков 5. При этом скорость опроса (определяющая длину элементарного импульса τед.имп.j на последовательном выходе преобразователя) будет соответствовать частоте стробирующих импульсов fстроб1 на входе конкретного счетчика:

После окончания считывания информации из i-го параллельного регистра 1.1.1i и проключения тактового импульса на тактовый вход i+1-го параллельного регистра 1.1.1i+1 для него полностью повторяется описанный выше опросный цикл. Опрос параллельных регистров 1.1.1 продолжается до тех пор, пока не будет полностью сформирован объединенный последовательный кадр на j-м выходе преобразователя, т.е. опрошены все параллельные регистры 1.1.1, включенные в единую j-ю функциональную группу.

Остальные L-1 трактов работают идентично, что позволяет достичь заданной цели, т.е. получить группу перестраиваемых функциональных трактов преобразования параллельного кода от M источников в L групп последовательного кода. Высокая управляемость реализуемых при этом функциональных структур, полученная за счет введения в заявляемый преобразователь целой группы коммутирующих устройств, позволяет оперативно перераспределять исходящие информационные потоки между несколькими широкополосными каналами, предоставленными доставляемыми первичной сетью связи при переменном их числе и изменяющейся величине максимальной пропускной способности.

Источники информации

1. Шило В. Л. Популярные цифровые микросхемы. Справочник. 2-е издание, испр.-Челябинск: Металлургия, Челябинское отд., 1989. -352 с.

2. Микросхемы памяти, ЦАП и АЦП: Справочник - 2-е изд., стереотип/О.Н. Лебедев, А.-Й.К.Марцинкявичус, Э.-А.К.Багданскис и др.; -М.: КУбК-а, 1996 - 384 с.

3. Алексеенко А. Г., Шагурин И.И. Микросхемотехника: Учеб. пособие для вузов/Под ред. И.П. Степаненко. -М.: Радио и связь, 1982. -416 с.

4. Фано Р. Передача информации. Статистическая теория связи. -М.: Мир, 1965. -439 с.

5. Гусев В.В., Зеличенко Л.Г., Конев К.В. Основы импульсной и цифровой техники. М.: Сов. радио, 1975, -440 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СТАТИСТИЧЕСКОГО УПЛОТНЕНИЯ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 1997 |

|

RU2110897C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| СПОСОБ И УСТРОЙСТВО РАСПОЗНАВАНИЯ КЛАССОВ СИГНАЛОВ | 1998 |

|

RU2133501C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1994 |

|

RU2099868C1 |

| ИНТЕРПОЛЯТОР | 1998 |

|

RU2132568C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127903C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах преобразования цифровых данных и их передачи по широкополосным каналам. Техническим результатом является расширение возможной области применения преобразователя параллельного кода в последовательный путем реализации функциональной возможности оперативно перераспределять исходящие информационные потоки между несколькими прозрачными каналами, предоставляемыми первичной сетью связи при переменном их числе и изменяющейся величине максимальной пропускной способности. Результат достигается тем, что преобразователь параллельного кода в последовательный содержит генератор импульсов, М регистров сдвига, счетчиков, коммутаторы, L D-триггеров, где М ≥ L и М = 2,3, ..., а L = 2,3,... Благодаря новой совокупности существенных признаков, заключающихся во введении новых информационных и управляющих связей между элементами преобразователя, появляется возможность получить несколько (L) последовательностей цифровых сигналов на его выходах с произвольным их числом и произвольной переадресацией между ними входных сигналов. 1 з.п.ф-лы, 10 ил.

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1425848A1 |

| Преобразователь параллельного кода в последовательный | 1988 |

|

SU1603529A2 |

| ЭКСТРУЗИОННАЯ ГОЛОВКА ДЛЯ ИЗГОТОВЛЕНИЯ ИЗДЕЛИЙ, КОМБИНИРОВАННЫХ ИЗ РАЗЛИЧНЫХ ТЕРМОПЛАСТОВ | 0 |

|

SU397358A1 |

Авторы

Даты

1998-11-10—Публикация

1997-06-19—Подача