Изобретение относится к информационно-измерительной технике и пред назначено для использования в системах сбора и обработки информации различного назначения, в системах автоматического управления и регулирования.

Целью изобретения является повышение быстродействия,,

На фиг.1 приведена функциональная схема устройства; на фир.2 - функциональная схема блока смещения; на фиг.З - функциональная схема блок управления; на фиг.4 - функциональны схемы первого и второго преобразователей напряжения в частоту; на фиг,5 - временные диаграммы работы устройства.

шого-цифровой преобразователь содержит преобразователь 1 напряжения в частоту, счетчик 2 тактовых импульсов, блок 3 сравнения кодов,

25

35

блок 4 постоянной памяти, адресный счетчик 5, регистр 6, блок 7 управления, генератор 8 тактовых импульсов, преобразователь 9 напряжения в частог ту, блок JO смещения, счетчик П тактовых импульсов, блок 12 сравненияЗО кодов, блок 13 постоянной памяти, адресный счетчик 14, блок 15 управления, элементы ИЛИ 16-18(, элемент ИЛИ- НЕ 19, элемент И-НЕ 20, выходные шины 21 и 22 генератора тактовых импульсов, входную шину 23, шину 24 запуска, выходную шину 25 преобразова- . теля, выходную шину 26 преобразователя 9, шины 27 и 28 сброса преобразователей 1 и 9, выходную шину 29 блока 40 4, выходную шину 30 блок а шины 31-35 управления блока 7 управления, шину 36 конца преобразования, шину 37 сбоя, выходную шину 38 блока 13, выходную шину 39 блока 12 сравнения, дс шины 40-44 управления блока 15 уцрав- ления.

Блок 10 (фиг.2) содержит резисторы 45 и конденсатор 46. .

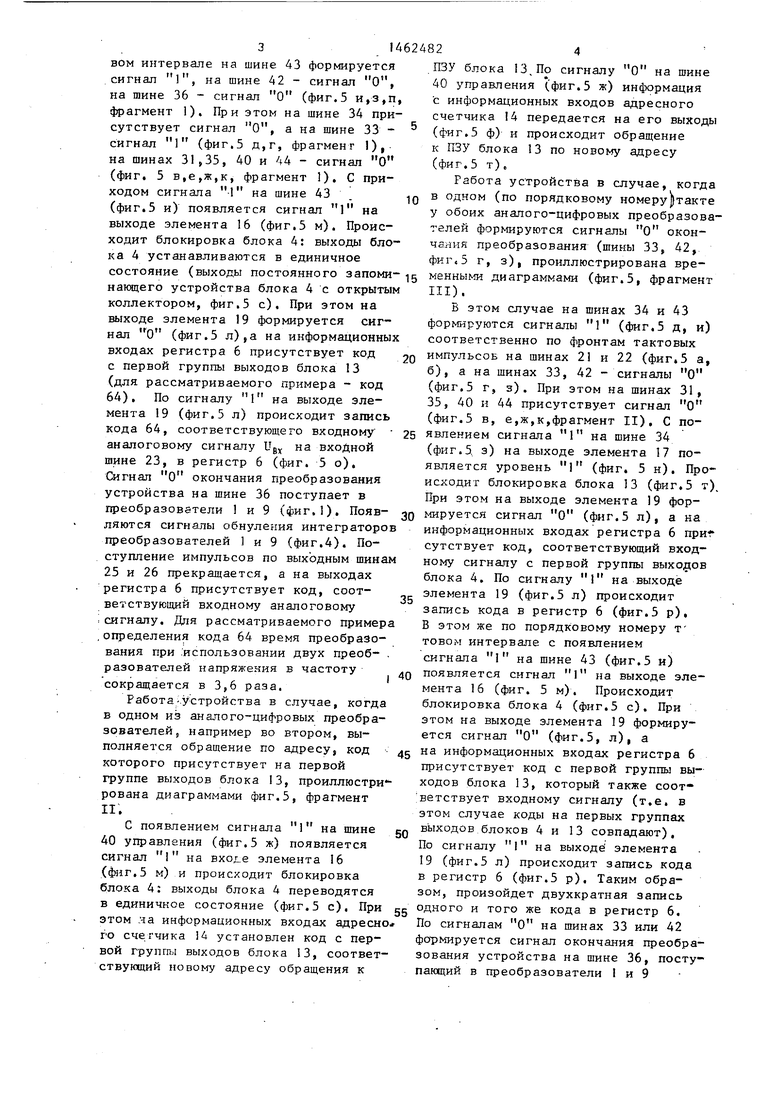

-Блок 7 управления (фи-г.З) содержит элементы НЕ 47 - 51, элементы И 52 - 61, элемент ИЛИ 62.

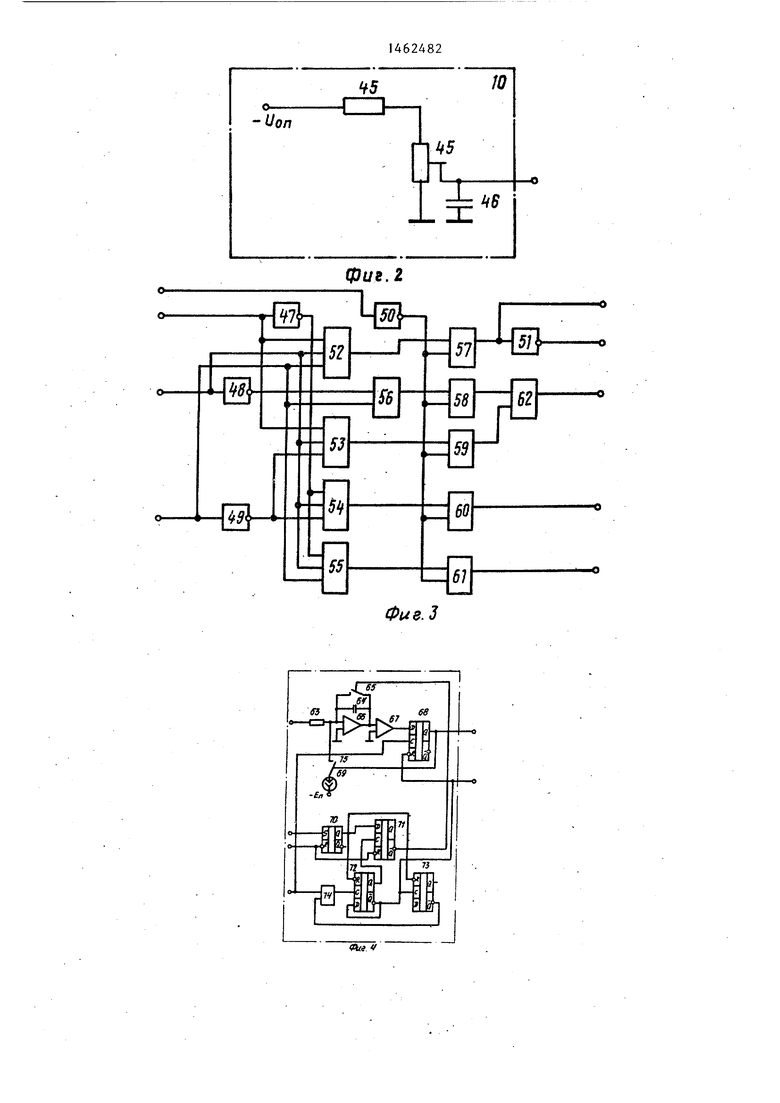

Первый и второй преобразователи напряжения в частоту (фиг.4) содержат резистор 63, конденсатор 64, ключ 65,j-c операционные усилители 66 и 67, D- триггер 68, источник 69 тока, RS- триггер 70, D-триггеры 71, 72 и 73, элемент И 74 и ключ 75. Во втором

50

.

д

5

0

5

5

О . 0с

c

0

ВХ

преобразователе напряжения в частоту неинвертирующий вход усилителя 66 является пятым входом преобразователя,

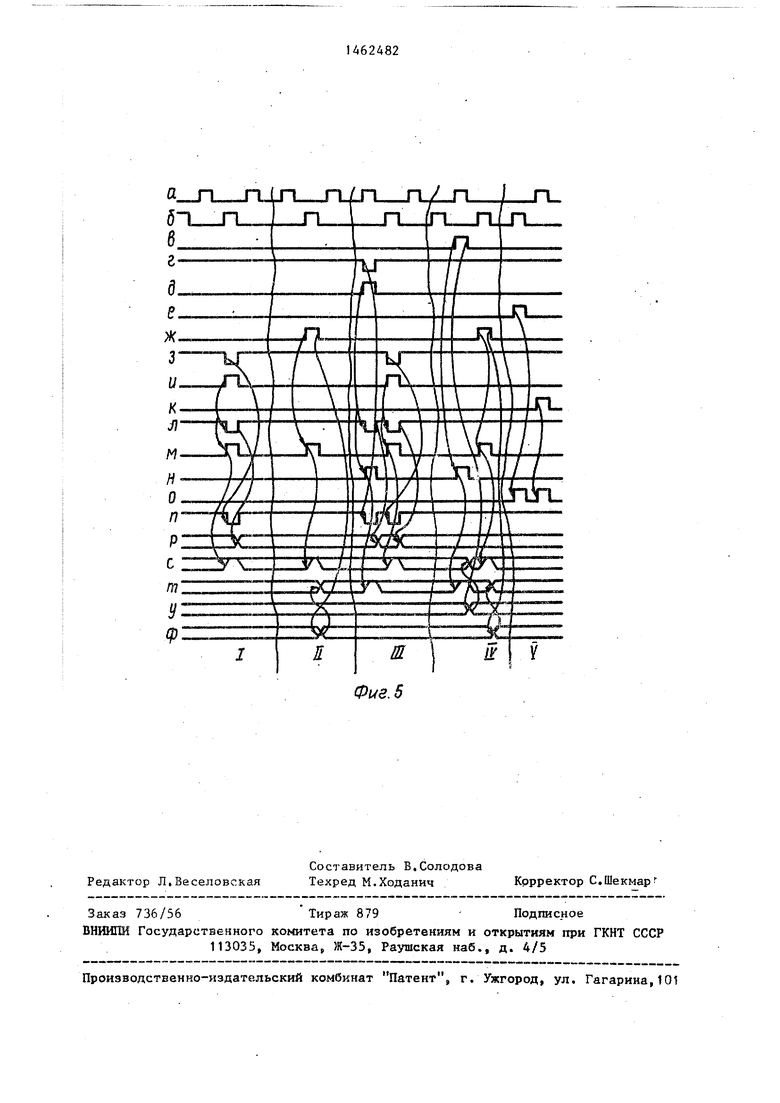

На фиг.5 обозначено: а, б - тактовые импульсы соответственно на выходных шинах 21 и 22; в,г,д,е - сигналы на шинах управления 31-35 соответственно; ж,з,и,к - соответственно сигналы на шинах управления 40-44; л,м,,п - соответственно сигналы на выходах элементов 19-20; р - сигналы на входах регистра 6; с, т - соответственно сигналы на выходах блоков 4 и 13; у, ф - сигналы на выходах адресных счетчиков 5 и 14.

Работа устройства может быть рассмотрена как одновременное функционирование двух идентичных параллельно включенных аналого-цифровых преобразователей, на вход одного из которых подается аналоговый сигнал U| а на вход другого - сигнал (g - шаг квантования АЦП),

Преобразователь, на входе которого установлен сигнал U г соответствующий значени:х кода т, и преобразователь, на входе которого установлен сигнал Ugx+ 4g, соответствующий значению код а т+4, работает аналогич но. При этом на- первой группе выходов блока 13 в тех случаях, когда на ней присутствует выходной код хранится значение кодов т-4. I.

Если последовательность на выходе

преобразователя 9 соответствует зна- чению кода т+4, то из блока 13 в ре- гистр 6 записывается код т соответствующий сигналу Ug на входе устройства, С помощью элементов 16-20 осу-;- ществляется выбор минимального из времени определения кодов m или т+4 и управление всем устройством в целом.Пусть, например, на входной шине 23 устройства установлен аналоговый сигнал UBX соответствующий значению кода . - {Три этом на выходе преобразователя 1 формируется последовательность импульсов, соответствующих коду m 64, а на выходе преобразователя 9 - последовательность, соответствующая коду ..Время определения значения кода 64 больше времени огфеделения значения кода 68: код 64 определяется в 68-м тактовом интервале, а код 68 - в 19-м тактовом интервале. В этом случае в 19-м тактоBOM интервале на шине 43 формируется сигнал 1, на шине 42 - сигнал О, на шине 36 - сигнал О (фиг.5 и,з,п, фрагмент 1). При этом на шине 34 присутствует сигнал О, а на шине 33 - сигнал (фиг.5 д,г, фрагмент 1),. на шинах 31,35, 40 и 44 - сигнал О (фиг, 5 в,е,ж,к, фрагмент 1), С приходом сигнала на шине 43 (фиг.5 и) появляется сигнал 1 на выходе элемента 16 (фиг.5 м). Происходит блокировка блока 4: выходы блока 4 устанавливаются в единичное

10

.ПЗУ блока 13,По сигналу О на шине 40 управления (. фиг.5 ж) ин4юрмация с информационных входов адресного счетчика 14 передается на его выходы (фиг.5 ф) и происходит обращение к ПЗУ блока 13 по новому адресу (фиг.5 т)е

Работа устройства в случае, когда в одном (по порядковому номеру))такте у обоих аналого-цифровых преобразова телей формируются сигналы О окончания преобразования (шины 33, 42, фиг.5 г, з), проиллюстрирована вреч «- I fvjnjijjBji. 1 iJMjjuBiiHa вре- состояние (выходы постоянного запоми-15 менными диаграммами (фиг.5, фрагмент

нающего устройства блока 4 с открытым коллектором, фиг.5 с). При этом на выходе элемента 19 формируется сигнал 0 (фиг.5 л),а на информационных входах регистра 6 присутствует код с первой группы выходов блока 13 (для рассматриваемого примера - код 64). По сигналу 1 на выходе элемента 19 (фиг.5 л) происходит запись кода 64, соответствующего Bxof(HOt4y аналоговому сигналу Ug на входной шине 23, в регистр 6 (фиг. 5 о). Сигнал О окончания преобразования устройства на шине 36 поступает в преобразователи и 9 (фиг.). Появляются сигналы обнуления интеграторов преобразователей 1 и 9 (фиг.4). Поступление импульсов по выходным шинам 25 и 26 прекращается, а на выходах регистра 6 присутствует код, соответствующий входному аналоговому :сигналу. Для рассматриваемого примера .определения кода 64 время преобразования при .использовании двух преоб- . разователей напряжения в частоту сокращается в 3,6 раза.

Работа .устройства в случае, когда в одном из аналого-цифровых преобразователей например во втором, выполняется обращение по адресу, код . которого присутствует на первой группе выходов блока 13, проиллюстрирована диаграммами фиг.5, фрагмент II.

С появлением сигнала 1 на шине 40 управления (фиг.5 ж) появляется сигнал на элемента 16 (фиг.5 м) и происходит блокировка блока 4: выходы блока 4 переводятся в единичное состояние (фиг.5 с). При этом ла информационных входах адресно- Г О счетчика 14 установлен код с первой групгш выходов блока 13, соответствующий новому адресу обращения к

20

III).

В этом случае на шинах 34 и 43 формируются сигналы 1 (фиг.5 д, и) соответственно по фронтам тактовых импульсов на шинах 2 и 22 (фиг,5 а, б), а на шинах 33, 42 - сигналы О (фиг.5 г, з). При этом на шинах 31,

30

35

40

35, 40 и 44 присутствует сигнал О (фиг.5 в, е,ж,к,фрагмент II), С по- 25 явлением сигнала 1 на шине 34

(фиг.5 з) на выходе элемента 17 появляется уровень 1 (фиг, 5 н), Происходит блокировка блока 13 (фиг,5 т) При этом на выходе элемента 19 формируется сигнал О (фиг.5 л), а на информационных входах регистра 6 при сутствует код, соответствующий входному сигналу с первой группы выхо{5ов блока 4. По сигналу 1 на выходе элемента 19 (фиг.5 л) происходит запись кода в регистр 6 (фиг.5 р), В этом же по порядковому номеру т товом интервале с появлением сигнала 1 на шине 43 (фиг.5 и) появляется сигнал 1 на выходе элемента 16 (фиг. 5 м). Происходит блокировка блока 4 (фиг,5 с). При этом на выходе элемента 19 формируется сигнал О (фиг.5, л), а 45 на информационных входах регистра 6 присутствует код с первой группы выходов блока 13, который также соответствует входному сигналу (т.е. в этом случае коды на первых группах выходов блоков 4 и 13 совпадают). По сигналу 1 на выходе элемента 19 (фиг.5 л) происходит запись кода в регистр 6 (фиг.5 р). Таким образом, произойдет двухкратная запись одного и того же кода в регистр 6. По сигналам О на шинах 33 или 42 формируется сигнал окончания преобразования устройства на шине 36, поступающий в преобразователи и 9

50

55

1462482

.ПЗУ блока 13,По сигналу О на шине 40 управления (. фиг.5 ж) ин4юрмация с информационных входов адресного счетчика 14 передается на его выходы (фиг.5 ф) и происходит обращение к ПЗУ блока 13 по новому адресу (фиг.5 т)е

Работа устройства в случае, когда в одном (по порядковому номеру))такте у обоих аналого-цифровых преобразователей формируются сигналы О окончания преобразования (шины 33, 42, фиг.5 г, з), проиллюстрирована вреч «- I fvjnjijjBji. 1 iJMjjuBiiHa вре- менными диаграммами (фиг.5, фрагмент

ч «- I fvjnjijjBji. 1 iJMjjuBiiHa вре- 15 менными диаграммами (фиг.5, фрагмент

20

III).

В этом случае на шинах 34 и 43 формируются сигналы 1 (фиг.5 д, и) соответственно по фронтам тактовых импульсов на шинах 2 и 22 (фиг,5 а, б), а на шинах 33, 42 - сигналы О (фиг.5 г, з). При этом на шинах 31,

30

35

0

35, 40 и 44 присутствует сигнал О (фиг.5 в, е,ж,к,фрагмент II), С по- 25 явлением сигнала 1 на шине 34

(фиг.5 з) на выходе элемента 17 появляется уровень 1 (фиг, 5 н), Происходит блокировка блока 13 (фиг,5 т), При этом на выходе элемента 19 формируется сигнал О (фиг.5 л), а на информационных входах регистра 6 при сутствует код, соответствующий входному сигналу с первой группы выхо{5ов блока 4. По сигналу 1 на выходе элемента 19 (фиг.5 л) происходит запись кода в регистр 6 (фиг.5 р), В этом же по порядковому номеру т товом интервале с появлением сигнала 1 на шине 43 (фиг.5 и) появляется сигнал 1 на выходе элемента 16 (фиг. 5 м). Происходит блокировка блока 4 (фиг,5 с). При этом на выходе элемента 19 формируется сигнал О (фиг.5, л), а 5 на информационных входах регистра 6 присутствует код с первой группы выходов блока 13, который также соответствует входному сигналу (т.е. в этом случае коды на первых группах выходов блоков 4 и 13 совпадают). По сигналу 1 на выходе элемента 19 (фиг.5 л) происходит запись кода в регистр 6 (фиг.5 р). Таким образом, произойдет двухкратная запись одного и того же кода в регистр 6. По сигналам О на шинах 33 или 42 формируется сигнал окончания преобразования устройства на шине 36, поступающий в преобразователи и 9

0

5

(фиг.1). При этом сигнал О на шине 36, сформированный, например, по сигналу О на шине 33, появившемуся раньше, чем сигнал О на шине 42, не влияет на работу устройства Б таком режиме, поскольку адреса обращения к блокам 4 и 13 формируются до появления сигналов на шинах 33 и .42, т.е. в предыдущем такте. I Работа устройства в случае, когда :В одном (по порядковому номеру) так :те в обоих аналого-цифровых преобразователях выполняется обращение по адресам, коды которых присутствуют на первых группах выходов блоков 4 и 13, проиллюстрирована временными диаграммами фиг.5, фрагмент IV.

В этом случае с приходом тактовых импульссз на шины 2 и 2.2 на шинах ;31 и 40 формируются сигналы 1 :(фиг.5 в.ж), с приходом сигнала I ;на шину 31 (фиг.5 в) появляется сигнал 1 на выходе элемента 17 (фиг.5 н) и происходит блокировка блока 13 (фиг.5 т). При этом на информационных входах адресного счетчика 5 установлен код с первой группы выходов блока 4, соответствующий адресу обращения к ПЗУ блока 4. По сигналу О на шине управления 3 (фиг.5 в) информация с информационных входов адресного счетчика 5 передается на его выходы (фиг,5 у) и происходит обращение к ПЗУ блока 4 по новому адресу (фиг,5 с). На выходах адресного счетчика 14 при этом присутствует код,

соответствующий адресу предыдущего обращения к блоку 13 (фиг.5 ф). В этом же по порядковому так- товом интервале с приходом сигнала 1 на шину 40 управления (фиг.5 ж) появляется сигнал 1 на выходе элемента 16 (фиг.5 м), и происходит блокировка блока 4 (фиг, 5 с). При этом на информационных входах адрес- нога счетчика 14 установлен к.од с первой группы выходов блока 13, соот ветствукщий новому адресу обращения к ПЗУ блока 13. По сигналу О на шине 40 управления (фиг,5 ж) информация с информационных входов адресног счетчика 14 передается на его выходы (фиг.5 ф) и происходит обращение к ПЗУ блока 13 по новому адресу (фиг.5 т). При этом на выходах адресного счетчика 5 присутствует

5

0

5

0

5

0

5

0

5

код, соответствукший адресу предыду- шего обращения к блоку 4 (фиг.5 у).

Пример формирования сигнала сбоя устройства на шине 37 (фиг.5 о) при наличии сбоя хотя бы у одного из аналого-цифровых преобразователей, например у первого преобразователя (фиг.5 е), представлен на фиг.5 фрагмент V.

С появлением сигнала 1 хотя бы на одной из шин управления 35 или 44 (фиг.5 е,к) форсируется сигнал 1 на выходе элемента 18 (фиг.5 о), характеризующий сбой устройства. .

Работа устройства начинается с прихода нулевого сигнала запуска на шину 24. При поступлении нулевых тактовых импульсов по выходным шинам 21 и 22 на шинах 27 и 28 формируются сигналы сброса (нулевые), длительность которых равна периоду тактовых импульсов. По сигналам сброса на шине 27 устанавливаются в О счетчик 2, адресный счетчик 5, регистр 6 и D- триггер преобразователя 1. По сигналу сброса на шине 28 устанавливаются в О счетчик 11, адресный счетчик 14 и D-триггер 58 преобразователя 9. Все возможные с лучаи взаимодействия обоих аналого-цифровых преобразователей описаны выше.

I Повьипение быстродействия достигается путем использования специфического характера зависимости времени преобразования от входного сигнала. Эта зависимость имеет характер, близкий к периодическому, что позволяет, используя два аналогичных преобразователя с таким сдвигам по входному сигналу, чтобы пики характеристики одного преобразователя совмещались с провалами характеристики другого преобразователя, получить более чем двукратное повышение быстродействия устройства. Величина сдвига в квантах выбирается из условия максимального выигрыша в быстродействии и прямо пропорциональна разрядности аналого-цифрового преобразователя. Например, для N 7 по сравнению с прототипом максимальное время преобразования сокращается в 5 раз. При этом 98,4% кодов определяются в устройстве меньше чем за 371 , а в известном устройстве - меньше, чем за 86 ( 2 - период тактовых импульсов) ,

7 Формула изобретения

1.Аналого-цифровой преобразовател содержащий генератор тактовых импулсов, первый выход которого соединен с тактовым входом первого счетчика тактовых импульсов, с первым входом первого преобразователя напряжения в частоту и с первым входом первого блока .управления, второй вход которого соединен с первым выходом перв го преобразователя напряжения в частоту, третий вход соединен с выходо первого блока сравнения кодов, четвертый вход соединен с выходом первого блока постоянной памяти, а первый и второй выходы первого блока управления соединены соответственно с первым и вторым управляющими вхо- первого адресного счетчика, вхо сброса которого соединен с вторым выходом первого преобразователя напряжения в частоту, входами сброса первого счетчика тактовых импульсов и регистра, информационные, входы ко- тррого объединены с соответствующими информационными входами первого адресного счетчика и соединены с соответствующими выходами первой группы выходов первого блока постоянной памяти, адресные входы которого соединены с соответствующими вы одами , первого адресного счетчика,.вторая группа выходов первого блока постоянной памяти соответственно соединена с первой группой входов первого блока сравнения кодов, вторая группа входов которого соединена соответственно с выходами первого счетчика тактовых импульсов, второй вход первого преобразователя напряжения в частоту является входной шиной, третий вход является шиной запуска, выходы регистра являются выходными

отличающийся -тем что, с целью повышения быстродействия, в него введены второй преобразователь напряжения в частоту, второй блок постоянной памяти, второй адресный счетчик, второй блок управ- пеккя, второй блок сравнения кодов, второй счетчик тактовых им - пульсов, блок смещения, три элемента ИЛИ, элемент ИЛИ-НЕ, элемент И-НЕ, первый вход которого соединен с третьим выходом первого блока управления, а выход соединен с четвертым вхо- аом первого преобразователя напряжения

8

10

15

20

tt

в частоту и является шиной конца преобразования, второй выход генератора тактовых импульсов соединен с первым входом второго блока управления, тактовым входом второго счетчика тактовых импульсов и первым входом второго преобразователя напряжения в частоту, второй вход которого является входной шиной, третий и четвертый входы объединены соответственно с третьим и четвертым входами первого преобразователя наЪряжения в частоту пятый вход соединен с выходом блока смещения, первый выход второго преобразователя напряжения в частоту соединен с вторым входом второго блока управления, второй выход - с входами сброса второго адресного счетчика и второго счетчика тактовых импульсов, причем третий вход второго .блока управления соединен с выходом второго блока сравнения кодов, первый выход - с первым входом перво- 25 го элемента первым управлякщим входом второго адресного счетчика,второй выход - с вторым управлягацим входом .второго адресного счетчика, управля- кхций вход регистра соединен с выходом элемента ИЛИ-НЕ, первый вход которого объединен с первым.входом второго элемента ИЛИ и соединен с четвертым выходом первого блока управления, второй вход второго элемент а ИЛИ соединен с первым выходом первого блока управления, а выход соединен с управляющим входом второго блока постоянной памяти, первая группа выходов которого соединена с со- 0 ответствующими информационными вход at-, ми регистра и второго адресного счетчика, выходы которого соединены с адресными входами бло ка постоянной памяти, вторая группа выходов которого соединена соответственно с пер- врй группой выходов второго блока сравнения кодов, вторая группа входов которого соединена соответственно с выходами второго счетчика тактовых импульсов, выход второго блока постоянной памяти соединен с четвертым входом второго блока управления, третий выход которого соединен с вторым входом элемента И-НЕ, четвертый выход соединен с вторыми входами первого элемента ИЛИ и элемента ИЛИ- НЕ, пятый выход соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с пятым выхо30

35

0

5

дом первого блока управления, а выход является линией сбоя, выход первого элемента ИЛИ соединек с управляющим входом первого блока постоянной памяти.

2. Аналого-цифровой преобразователь по п., отличающийся тем, что каждый блок управления выпо нен на пяти элементах НЕ, десяти элементах И и элементе ИЛИ, выход которого является пятым выходом блокаt первый и второй входы соединены соответственно с выходами первого и второго злементов И, первые входы которых объединены с первыми , входами третьего,, четвертого и пятог элементов И и соединены с выходом - первого элемента НЕ, вторые входы первого., второго, третьего, четверто го и пятого элементов И соединены соответственно с выходами щестого, седьмого, восьмого, девятого и десятого элементов И, первый, четвертый, третий и второй входы блока являются

соответственно входами первого, рого, третьего и четвертого элементов НЕ, входы которых объединены с первыми десятого, щестого и девятого элементов И, выход четвертого элемента НЕ соединен с первыми входами седьмого и восьмого элементов Ир вторые входы которых объединены с вторыми входами девятого и деся того элементов И и входом третьего ; элемента НЕ, третий вход десятого элемента И объединен с третьим входом седьмого элемента И и входом второго элемента НЕ, выход которого соединен с третьими входами восьмого и девятого элементов И, выход третьего элемента НЕ соединен с вторым входом шестого элемента И, выход пятого элемента И соединен с входом пятого элемента НЕ и является четвер- выходом блока, третьим, вторым и,первым выходами блока являются соответственно выходы пятого элемента НЕ, третьего и четвертого .элементов И.

3, Аналого-цифровой преобразователь по п. 1 , отличающийся

10

-- 20

15

6248210

тем, что первый преобразователь напряжения в частоту выполнен на резисторе, конденсаторе, двух ключах, двух операционных усилителях, источнике тока, четырех В триггерах, RS- триггере, элементе И, первый вход которого объединен с- С-вход ом первого D-триггера и является первым вхо- дом преобразователя, второй вход соединен с инверсным выходом второго D-триггера, а выход соединен с С- входом третьего D-триггера, R-вход которого объединен с R-входом второго D-триггера, D-входом четвертого D- триггера и соединен с прямым выходом RS-триггера, D-вход третьего D-триггера объединен с R-входом первого D-триггера, С-входом второго D-триг- гера, соединен с инверсным выходом третьего В-триггера и является вторым выходом блока, прямой выход первого D-триггера соединен с управ- лякщим входом первого ключа и являет25 ся первым выходом, блока, информационный вход первого ключа через источник тока соединен с шиной напряжения отрицательной полярности, выход первого ключа соединен с инфор30 мационным .вх-одЪм второго ключа, ин- вертирумцим входом первого операционного усилителя, первой обкладкой конденсатора и первым выводом резистора, второй вывод которого является

25 вторым входом блока, выход второго ключа объединен с второй обкладкой конденсатора, выходом первого операционного усилителя и соединен с инвертирующим входом второго операционного

40 усилителя, неинвертирующие входь: пер вого и второго операционных усилителей являются шиной нулевого потенциала, выход второго операционного усилителя соединен с D-входом первого

45 D-триггера, прямой выход третьего )-триггера соединен с С-входом четвертого Б триггерар R-вход которого объединен с R-входом RS-триггера и является третьим входом блока, инверсный выход четвертого D-триггера соединен с управляющим входом второго ключа.

SO

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой записи-воспроизведения речевой информации | 1986 |

|

SU1327174A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Многоканальное аналого-цифровое устройство задержки | 1983 |

|

SU1256150A1 |

| Цифровой регистратор | 1984 |

|

SU1164549A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Аналого цифровой преобразователь | 1987 |

|

SU1550622A1 |

| Измерительный прибор | 1989 |

|

SU1661653A1 |

Изобретение относится к информЭ ционно-измерительной технике и может быть использовано в системах сбора данных для контроля параметров образцовых источников. Изобретение позволяет повысить быстродействие устройства. Это достигается тем, что в аналого-цифровой преобразователь, содержащий преобразователь 1 напряжения в частоту, генератор 8 тактовых импульсов, блок 7 управления, блок 4 постоянной памяти, адресный счетчик 5, блок 3 сравнения кодов, счетчик 2 тактовых импульсов, регистр 6, введены преобразователь 9 напряжения в частоту, блок 10 смещег кия, адресный счетчик 14, блок 13 постоянной памяти, блок 15 управле ния, блок 12 сравнения кодов, счетчик 11 тактовых импульсов, элементы ИЛИ 16,7,18, элемент ИЛИ-НЕ 19 элемент 20. 2 з.п. ф-лы , 5 ил. S (Л с KD 4ib СХ) ю

Ла ч

Фие.З

Авторы

Даты

1989-02-28—Публикация

1987-08-10—Подача