1239867

Изобретение относится к импульсной технике и может быть использовано в системах сброса и обработки информации различного назначения, сие- темах автоматического управления и регулирования.

Цель изобретения - повьшение быстродействия.

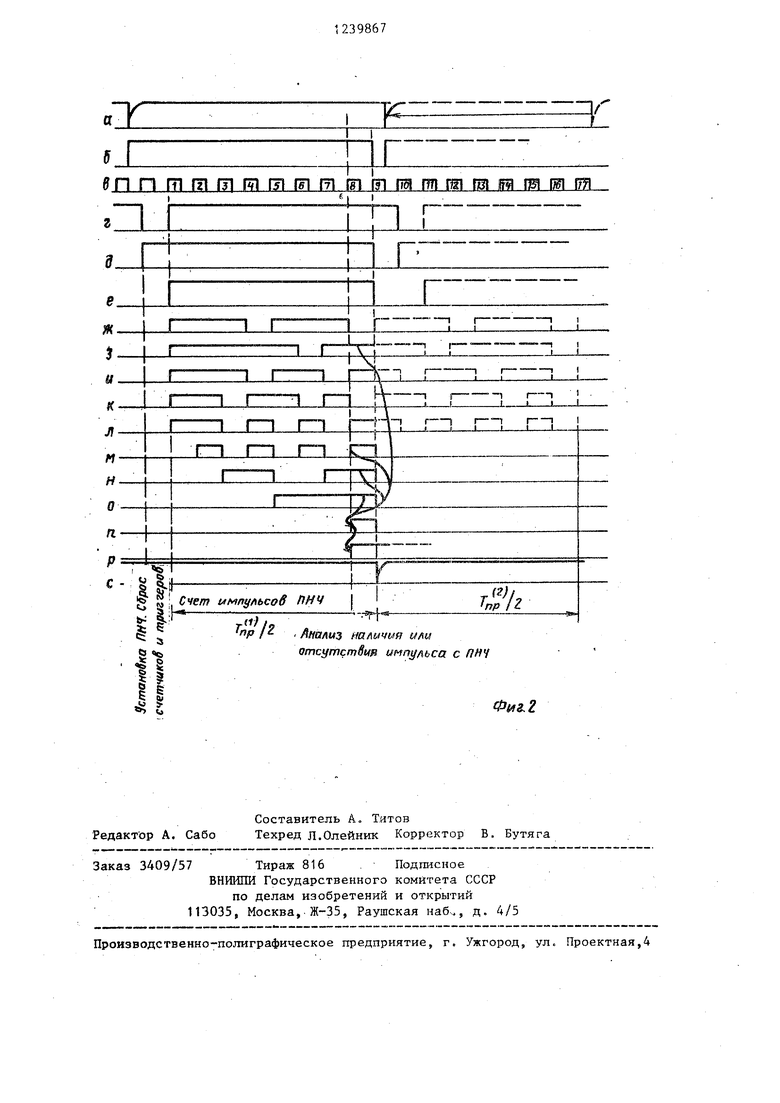

На фиг.1 приведена функциональная Схема аналого-ци фрового преобразователя на фиг.2 - временные диаграммы работы аналого-цифрового преобразователя . .

Устройство содержит преобразователь 1 напряжения в частоту, который имеет вход 2, элемент И 3, блок 4 формирования временного интервала, блок 5 управления, который имеет вход 6, генератор 7 тактовых импуль- сов, элемент И 8, D-триггер 9,счетчик. 10 импульсов, шину 11 логической единицы.

Блок 4 выполнен на элементе И 12, счетчике 13 импульсов, шины Г4 выходного кода, преобразователь 1 выполнен на операционном усилителе 15, конденсаторе 16, ключе.17, компараторе 18, D-триггере 19, ключе 20, резисторе 21, источнике 22 разрядного тока, шине 23 источника положительной полярности. Блок 5 выполнен

где q 1,,..5 N-1,

пь номер тактового импульса, одновременно с которым появляется импу:аьС на выходе преобразователя 1J

Uj напряжение на входе 2 устройства

IP - значение разрядного тока генератора 22, .

R - сопротивление резистора 21,

1 - номер ш- пульса преобразователя 1, положение которого определяется .

Р1з этого соотношения следует, что I том случае, если входной сигнал

и

5 такой, что число импульсов на

иьгходе преобразователя 1 за интернал Т,

9

четное, то в интервалах /2 и /2 (фиг, 2) оказывают- :я две совершенно одинаковые импульсные последовательности. Вследствие :зтого отпадает необходимость в сче9867

на RS-триггере 24, трех D-тригге- рах (втором 25, третьем 26 и первом 27), элементе И 28, дифференцирующем блоке 29, шине 30 логической 5 единицы. .

.На фиг.2 обозначено; а- сигнал запуска; § - сигнал на выходе RS- триггера 24; f - тактовые импульсы;

г,А - сигналы на выходах блока 5, Р - сигнал на первом выходе блока 4, « ; b .i.- сигналы на инверсном выходе преобразователя 1 соответственно для 4,3,5,6,и 7 импульсов; м ,н ,0сигналы на выходах с второго по N-ый- блока 4; г1 - сигнал на выходе элемента 8; Р сигнал на выходе D-триг- гера 9; с - сигнал окончания преобразования.

Аналого-цифровой преобразователь работа€ Т .следующим образом.

В устройстве испо.льзован преобра- зоватепь 1 с де.пьта-сигма модуляцией и предварительной установкой. При опреде.ленной величине входного сигнала И положение каждого импульса на выходе преобразователя 1 относительно последовательности тактовых

импульсов описывается следующим соотношением :

те всех импульсов в течение промежутка времени Т,р , а достаточно осуществить счет в интервале , а затем произвести умножение полученного кода на два.

В том случае, если входной сиг- нал Uj такой, что число импульсов 45;за интервал нечетное, то в интервале Т„р /2 оказывается на один импульс меньше, чем в интервале т ,р /2, что дает возможность получить правильный результат путем счета числа импульсов в интервале

50

Tnj,/2, умножения результата на 2 и добавления единицы в младший разряд выходного кода устройства. Необходимость добавления единицы в младший 55 разряд выходного кода устройства выясняется анализом импульсов последовательности на выходе преобразователя 1: если число импульсов в интервале 2 1: четное, то импульс совпадает с последним периодом следования тактовых импульсов в интервале , а если нечетное, то импульс пре.образователя- 1 не совпадает с аналогичным периодом тактовых импульсов, т.е. наличие или отсутствие импульса на выходе преобразователя 1 в конце интервала . /2 является условием для определения четности или нечетности выходного кода устройства, т.е. добавлять или не добавлять единицу в младший разряд кода устройства .

Процесс преобразования заклю.чает- ся в счете числа импульсов, поступающих от. преобразователя 1 на счетчик 10 через элемент 3 за промежуток времени Т„р 2 t, где N - число разрядо выходного кода устройства, Т - дли- тельность периода тактовых импульсов . Выходной код счетчика 10 образует N-1 разряд выходного кода устройства. Кроме того, в течение 2 -го периода тактовых импульсов осущест- вляется проверка наличия или отсутствия импульса с выхода преобразователя 1. Его наличие говорит о том, что число импульсов в интервале счет

N41

2 ;: четное, и для получения пра- вильного результата преобразования число, записанное в счетчике 10, не- обходимо удвоить без добавления единицы, что обеспечивается сохранением нулевого состояния D-триггера 9.При

отсутствии импульса в указанный мо-.

. /-

мент времени,что означает,что число импульсов в интервале преобразования 2 Ч нечетное,для получения правильного результата преобразования чи сло записанное в счетчике 10, также удваивается, а затем добавляется единица в младший разряд (триггер : 9). Условие добавления единицы в младший разряд кода образуется в резуль- тате сравнения уровней на N-1-м выходе блока 4 и преобразователя 1.

Удвоение результата производится при помощи сдвига вправо на 1 разряд . При этом сама операция сдвига отсутствует, но первый разряд счетчика 10 .считывается как второй разряд кода, второй - как третий и т.д.

При подаче сигнала запуска (фиг.) на вход 6 блока 5 по нулевому тактовому импульсу (фиг.26) от генератора 7 на первом управляющем

выходе блока 5 появляется сигнал логической единицы (фиг.2() и в течение периода тактовых импульсов осуществляется установка преобразователя 1 в исходное состояние, а на втором управляющем выходе блока 5 появляется сигнал логического нуля (фиг.2г), что вызывает -сброс счетчика 10, блока 4 и триггера 9. По первому тактовому импульсу (фиг.2б) на втором выходе блока 5 устанавливается- логическая единица, а на первом выходе блока 4 появляется также логическая единица, которая открывает элемент 3, через который импульсы с прямого выхода преобразователя 1 начинают поступать на тактовый вход счетчика 9.

Временные диаграммы (фиг.2) приведены для следующих значений параметров . Полное время преобразова- ниу; 161 (фиг. 2 б), тогда максимальное число импульсов -на выходе преобразователя 1 составляет семь. На фиг.2,i , W ,к,ц приведены временные диаграммы на инверсном выходе преобразователя 1 соответственно для 4,5,6,3,7 импульсов, сплошной линией - для предлагаемого устройства, пунктиром - для известного устройства.

Пусть напряжение U на входе 2

ex

таково, что на выходе преобразователя 1 должно появиться три импульса (фиг,2). За промежуток времени 81 осзтцествляется счет одного импульса, а далее алгоритм работы устройства таков, что при поступлении восьмого (2 -го) тактового импульса на каждом выходе из группь выходов с второго по четвертый (N-й) блока 4 (фиг.2|,н,о ) появляется логическая единица, и при наличии в этот момент на инверсном выходе преобразователя 1 логической единицы, на выходе элемента И 8 также появляется уровень единицы, который вызывает появление логической единицы на выходе триггера 9 и соответственно в младшем разряде выходного кода. Таким- образом выходной код будет 011, что соответствует трем импульсам.

Аналогичные операции производятся для числа импульсов 5 (фиг.2«) и 7 (фиг.2л). Для чисел 4 и 6 осущетвляется только счет числа имульсов за промежуток 81 , а состояие тактируемого триггера 9 не изеняется, так как на выходе преоб

разователя 1 в интервале (8i-9 t ) присутствует уровень логического нуля.

Преобразователь работает следую- щим образом.

Поступление сигнала логического нуля с .второго выхода блока 5 на R-вход триггера 19 вызывает появление логической единицы на его прямо выходе. Одновременно с первого выхода блока 5 .(р выход D-триггера 27) поступает логический нуль, осуществляющий размыкание ключа 17. Интегратор на операционном усилите- ле 15, конденсаторе 16, резисторе 21 начинает интегрировать разность разрядного Jj) и входного 1 токов преобразователя 1 в течение одного периода следования тактовых- импуль- сов t. При этом напряжение на выходе усилителя 15 становится равным

и;:Г (I,-I,,)t/C где ,, /R, 1 де R - сопротивление резистора 21. При поступлении первого тактового импульса от генератора 7 на прямом выходе триггера 19 устанавливается ло1 ический нуль, разрядной ключ 20 : paз ш кaeтcя, генератор 22 тока отклчается от выхода усилителя 15, и напряжение на его выходе начинает уг-:екьшаться. При достижении этим напряжением уровня О В на выходе компаратора 18 появляется логическая единица, и при поступлении на С-вхо тактового импульса записывается в D-триггер 19, замыкается разрядный клК Ч 20 и начинается вновь интегрирование разности токов )-По

V ех

следую цему тактовому импульсу состояние D-трнггера 19 изменяется на логический нуль, и тем самым на выходе преобразователя 1 формируется импульс длительностью Ь ., Далее процесс повторяется. Входное напряже- ние оказывается пропорциональным ср едней частоте следования импульсов на выходе преобразователя.

Блок 5 управления осуществляет по первому выходу формирование сиг- нала размыкания ключа 17 на время Т.,„ +1 , где Т - время преобразования АЦП, а по второму выходу формирование сигналов сброса счетчиков 10 и 13 и D-триггера 9.

Сигнал запуска поступает на S-вх RS-триггера 24 При этом на его прямом выходе появится логическая еди-

5

O 5 0

5

5

5

0

0

ница, которая подготавливает срабатывание первого D-триггера 27 и вызывает установку третьего и второго D-триггеров 25 и 26 в состояние логической единипдз, что открывает элемент 28 для тактовых импульсов с генератора 7. Поступление нулевого тактового импульса (фиг.2в) вызывает переброс третьего D-триггера 25 в состояние Q 1, Q О, а на инверсном выходе первого D-триггера 27 устанавливается логический нуль. Первый тактовый импульс вызывает обратный переброс третьего D-триггера 25, и на его инверсном выходе появляется сигнал логической единицы (фиг.2г), т.е. сформирован сигнал сброса. Это, в свою очередь, вызывает переброс второго D-триггера 26 по инверсному выходу в состояние логического нуля, элемент И. 28 закрывается и не пропускает более тактовых

. ,-..-.,-

импульсов. При поступлении сигнала с выхода переполнения счетчика 13 RS-триггер 24 и первый D-триггер 27 перебрасываются, при этом на инверсном выходе последнего появляется логическая единица (сформирован сигнал замыкания ключа 17),. такой же уровень возникает на прямых выходах третьего и второго D-триггеров 25 и 26. При поступлении нового импуль- са запуска процесс повторяется.

Таким образом, .предлагаемый ака- лого-цифровой преобразователь позволяет точно определить результат преобразования на основании счета импульсов от преобразователя напряжения в частоту на половине интервала счета известного устройства, т.е. обеспечивается увеличение быстродействия в 2 раза.

Ф 13 р мула изобретения

1. Аналого-цифровой преобразователь, содержащий преобразователь напряжения в частоту, первый вход которого является входной шиной,второй вход объединен с первыми входами блока управления и блока формирования временного интервала и соединен с выходом генератора тактовых импульсов, третий вход соединен с первым выходом блока управления, четвертый вход объединен с входом сброса счетчика импульсов, вторым входом блока формирования временных интер7

валов и соединен с втогзым выходом блока управления, второй вход которого является шиной Пуск, а третий вход соединен с первым выходом блока формирования временных интервалов, отличающий.с я тем что, с целью повышения быстродействия, в него введены первый и второй элементы И и D-триггер, D-вход которого является шиной логической единицы, R-вход объединен с R-входом сброса счетчика импульсов, а С-вход соединен с выходом первого элемента И, первые входы которого соединены с вторыми выходами блока формирования временного интервала, второй вход соединен с первым выходом преобразователя напряжения в частоту, второй вход которого соединен с первым входом второго элемента И, второй вход которого объединен с третьим входом блока управления, а выход соединен со счетным входом счетчика импульсов, выходы которого и прямой выход. D-триггера являются вы- ходньми шинами.

2. Преобразователь по п.1, о т- личающийся тем, что преобразователь напряжения в частоту выполнен на резисторе, источнике разрядного тока, двух ключах, конденсаторе, операционном усилителе,компараторе, D-триггере, инверсный выход которого является первым выходом преобразователя напряжения в частоту-, прямой выход соединен с первым входом первого ключа и является вторым выходом преобразователя напряжения в частоту, второй вход первого ключа через источник разрядного тока соединен с шиной источника питания отрицательной полярности, а выход - с первьми входами операционного усилителя, второго ключа, первой обкладкой конденсатора и первым выводом резистора, второй вывод которого является первым входом преобразователя напряжения в частоту, выходы . операционного усилителя и второго ключа объединены и соединены с второй обкладкой конденсатора и первым входом компаратора, вторые входы компаратора и операционного усилителя объединены и являются общей шиной выход Компаратора соединен с D-BXO398678

дом D-триггера, С- и R-входы которого являются соответственно вторым и четвертым входами преобразователя напряжения в частоту, третий вход

5 которого является вторым входом второго ключа.

3. Преобразователь по п.1, о т- ли чающийся тем, что блок формирования временного интервала

10 выполнен на элементе И-и счетчике импульсов, выходы которого являются вторыми выходами блока формирования временного интервала, выход переполнения счетчика импульсов соедиJ5 нен с первым входом элемента И и

является первым выходом блока формирования временного интервала,второй вход элемента И является первым входом блока формирования временного

20 интервала, вторым входом которого является вход сброса счетчика импульсов, счетный вход которого соединен с выходом элемента И.

25 4. Преобразователь по п.1, о т- личающийся тем, что блок управления выполнен на дифференцирующем блоке, элементе И, трех D-триггерах, RS-триггере, инверсньй

30 выход первого D-триггера является первым выходом блока управления, D-вход объединен с R-входами второго и третьего D-триггеров и соединен с прямым выходом RS-триггера, а вход первого D-триггера соединен с. прямым выходом третьего D-триггера, R-вход первого D-триггера объединен с Н-входом RS-триггера и соединен с выходом дифференцирующего блока, второй выход которого является общей шиной, а вход - третьим входом блока управления, вторым входом которого является S-вход RS-триггера, первым входом блока управления является первый вход элемента И, второй вход которого соединен с инверсным выходом второго D-триггера, а выход элемента И.соединен с С-входом третьего D-триггера, D-вход ко- то.рого объединен с С-входом второго D-триггера, соединен с инверсным выходом третьего D-триггера и является вторым выходом блока управления, D-вход второго D-триггера яв- ляется шиной логической единицы.

35

40

50

omcymcmSufs с ПНЧ

J

«о

Редактор А. Сабо

Составитель А. Титов

Техред Л.Олейник Корректор В, Бутяга

Заказ 3409/57 Тираж 816 . Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб, д. 4/5

Производственно-полиграфическое предприятие г. Ужгород, ул. Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345204C2 |

| Многоканальный аналого-цифровой преобразователь | 1987 |

|

SU1444945A1 |

| Аналого цифровой преобразователь | 1987 |

|

SU1550622A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Генератор спектрометрических импульсов | 1986 |

|

SU1325671A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

Изобретение относится к импульсной технике и может быть использовано в системах сбора и обработки ий- формации и сисФемах автоматического управления и регулирования. Изобретение позволяет повысить быстродействие устройства, что достигается тем, что в аналого-цифровой преобразова- -тель, содержащий преобразователь 1 напряжения в частоту, блок 5 управления, генератор 7 тактовых импульсов, блок 4 формирования временного интервала, счетчик 10 импульсов, введены элементы И 3 и В, D-триггер. 3 з.п. ф-лы, 2 ил. . , с

| Бахтияров Г,Д | |||

| Аналого-цифровые преобразователи | |||

| - М.: Советское радио, 1980, с | |||

| ПАРОВАЯ ИЛИ ГАЗОВАЯ ТУРБИНА | 1914 |

|

SU278A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1132357A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-23—Публикация

1984-02-24—Подача