динены с первыми разрядными -входами блока возведения десятичной цифры в квадрат и умножителя, выход которого соединен с первым входом преобразователя десятичного числа в двоичньй код, выход которого соединенсо счет ным входом,десятичного счетчика, раз рядные входы которого соединены с выходом блока возведения десятичной цифры в квадрат, вторые разрядные входы которого Соединены с разрядными выходами вычитающего счетчика и с вторыми разрядными входами умножителя, разрядные выходы регистра основа ния соединены соответственно с первой группой управляющих входов схемы сравнения, вторая группа управляющих входов которой соединена соответстве но с разрядными выходами десятичного счетчика, первый информационньй вход схемы сравнения соединен с первым входом первого элемента И и с шестым выходом группы элементов ИЛИ, .выход схемы сравнения соединен с вторым входом первого элемента И, третий вход которого соединен с вторым информационным входом схемы сравнения и с вторым выходом третьего дешифратора, третий, четвертый пятый, шестой и седьмой выходы третьего деишфратора соединены соответственно с вторыми управляющими входами блока 1 3 возведения десятичной здифры в квадрат, умножителя, регистра основания, преобразователя десятичного числа в двоичньй код и десятичного счетчика, вьгход первого элемента И соединен со счетным входом вычитающего счетчика, вход начальной установки которого соединен с седьмым выходом второго дешифратора, выход генератора импульсов соединен с вторым входом преобразователя десятичного числа в двоичньй код и с четвертым входом первого элемента И, отличающееся тем, что, с целью повышения его быстродействия, в него введены дешифратор и коммутатор, информационные входы которого соединены с выходами блока задания констант, управляюи(ий вход которого соединен с управляющим входом дешифратора, стробирующим входом коммутатора и седьмым выходом второго дешифратора, управляющи:е входы коммутатора соединены соответственно с выходами дешифратора, входы которого соединены соответственно с разрядными выходамиРегистра основания, выходы коммутатора соединены соответственно с разрядными входами вычитающего счетчика, выход схемы сравнения соединен с вторым входом второго триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для возведения в степень | 1982 |

|

SU1076904A1 |

| Устройство для возведения в степень | 1982 |

|

SU1084787A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Устройство для возведения в квадрат | 1977 |

|

SU703807A2 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1644054A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Способ определения индукции магнитного поля в зазоре магнитопровода | 1987 |

|

SU1688211A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1675810A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1712911A2 |

УСТРОЙСТВО ДДЯ ВОЗВЕДЕНИЯ В КВАДРАТ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ, содержащее регистр основанияj блок возведения десятичной цифры в квадрат, умножитель, десятичный счетчик, преобразователь двсятичногр числа в двоичный код, схему сравнения генератор импульсов, блок задания констант, первый элемент И, блок управления, вычитающий счетчик, причем блок управления содержит генератор такт9в, счетчик, первьм второй и третий деамфраторы, второй, третий и четвертый элементы И, счетчик lyiKлов, счетчик тактов, первый и второй триггеры, элемент ИЛИа группу элементов ИЛИ, триггер операций, выход генератора тактов соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами первого дешифратора, выходы с первого по пятый которого соединены с пepвы rи входами элементов ИЛИ группы, вторые входы которых соединены с первого по пятьш выходами TiTbporo дешифратора, информа1 ионные входы которого соединены с разрядными выходами счетчика 11 1клов, счетный вход которого соединен с выходом второго элемента И, перыый вход которого соединен с выходом генератора тактов и с первым входом третьего элемента И, выход которого соединен со счет-. ным входом счетчика тактов, разрядные вьссоды которого соединены с информационными входами третьего дешифратора, первый выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом сброса счетчика циклов и с первым входом элемента ИЛИ, выход которого соединен с первым входом первого триггера, первый выход которого соединен с вторым входом второ-, го элемента И, второй вход первого триггера соединен с шестым выходом второго дешифратора, с вторым входом элемента ИЛИ и с первым входом второго триггера, выход которого соедиS нен с вторым входом четвертого эле- мента И, первый выход триггера операций соединен с входами стробирования первого ч второго дешифраторов, вто-, рой выход триггера операций соединен СА 00 СП с входом стробирования третьего дешифратора, второй выход nepBolro триггера соединен с вторым входом ф со третьего элемента И, вьЬсоды элементов ИЛИ группы соединены соответственно с первыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, умножителя, преобразователя десятичного числа в двоичньй код и десятичного счетчика, входы выбора операций устройства соединены с первым и вторым входами триггера операций, информационный вход устройства соединен с входом установки числа регистра основания, разрядные выходы которого сое

Изобретение относится к области вычислительной техники и может быть применено в цифровых приборах для обработки результатов измерения. Известно устройство, содержащее регистр основания, матрицу разрядов матрицу произведения двух разрядов, накопитель, преобразователь числа в код, генератор импульсов и схему управлеш1я Ш . Недостатком данного устройства является невозможность извлечения квадратного корня из заданного числа. Наиболее близким техническим решением к изобретению является устрой ство для возведения в квадрат и извлечения квадратного корня, содержаще регистр основания, матрицу возведения десятичной цифры в квадрат, матрицу произведения двух разрядов, десятичньй счетчик, преобразоватэль десятичного числа в двоичный код, схему сравнения, генератор импульсов, блок констант, элемент И, блок управления, вычитающий счетчик, разрядные выходы которого соединены с разрядными входами матриц возведения десятичной цифры в квадрат и произведения двух разрядов, выходы которых соединены соответственно с входами десятичного счетчика и преобразователя десятичного числа в двоичньй код, выход которого соединен со счетным входом десятичного счетчика, выход которого соединен с первой группой управляющих входов

схемы сравнения, вторая группа управлйющих входов которой соединена с выходами регистра основания.

Извлечение квадратного корня в данном устройстве производится методом последовательных проб за несколько циклов, начиная с максимального числа, определяемого разрядностью устройства z .

Недостатком известного устройства является большое время, необходимое для достижения результата при малых значениях подкоренного числа.

Целью изобретения является повышение быстродействия устройства (уменьшение времени выполнения операций) .

Поставленная цель достигается тем, что в устройство для возведения в квадрат и извлечения квадратного корня,, содержащее регистр основания, блок возведения десятичной цифры в квадрат, умножитель, десятичньй счетчик, преобразователь десятичного числа в двоичньй код, схему сравнекия, генератор импульсов, блок задания констант, первый элемент И, блок управления, вычитающий счетчик, причем блок управления содержит генератор тактов, счетчик,.первый, второй и третий дешифраторы, второй, третий и четвертый элементы И, счетчик циклов, счетчик тактов, первый и второй триггеры, элемент ИЛИ-, группу элементов ИЛИ, триггер операций, выход генератора тактов соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами первого дешифратора, выходы с первого по пятый которого соединены с первыми входами элементов ИЛИ группы вторые входы которььс соединены с первого по пятый выходами второго дешифратора f информационные входы которого соединены с разрядными выходами счетчика циклов, счетный вход которого соединен с выходом второго элемента И, первый вход которого соединен с выходом генератора тактов и с первым входом третьего элемента И, выход которого соединен со счетным входом счетчика тактов, разрядные выходы которого соединены с информационными входами третьего дешифратора, первый выход которого соединен с первым входом четвертого элемента И, выход которого соединен с входом сброса счетчика циклов и с первым входом элемента

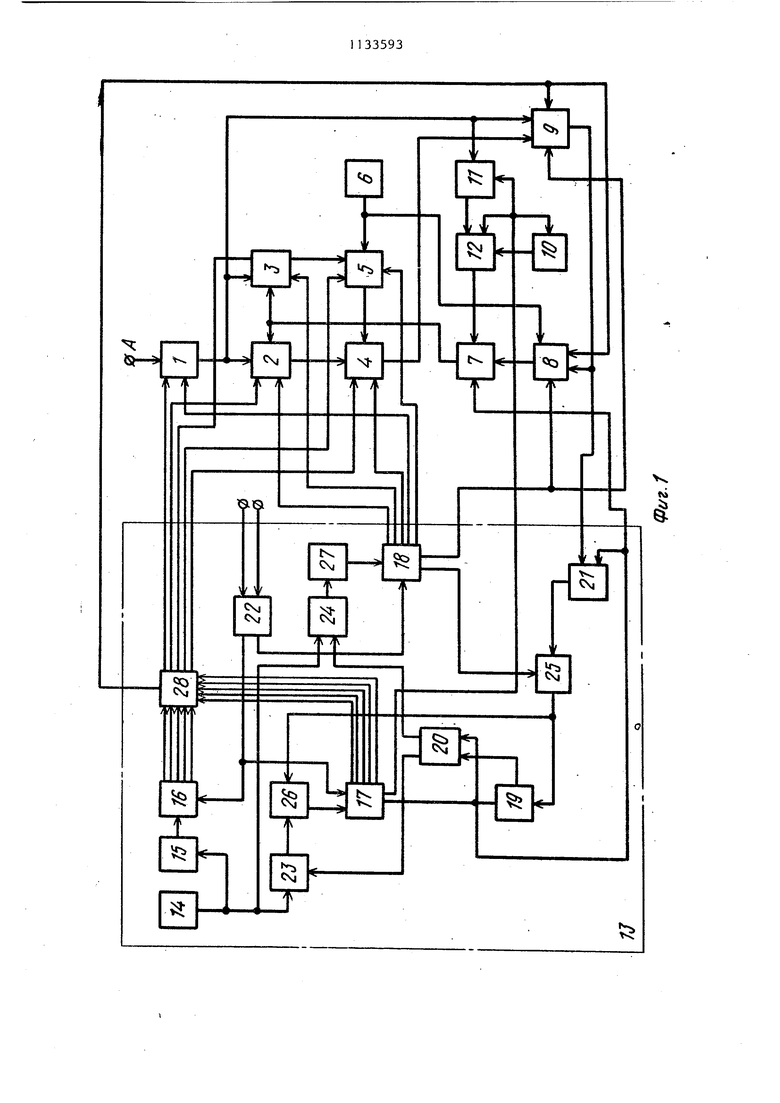

ИЛИ, выход которого соединен с первым входом первого триггера, первый выход которого соединен с вторым входом второго элемента И, второй вход первого триггера соединен с шестым выходом второго дешифратора, с вторым входом элемента ИЛИ и с первым входом второго триггера, выход которого соединен с вторым входом четвертого элемента И перзый выход триггера операций соединен с входами стробирования первого и второго дешифраторов, второй выход триггера операций соединен с входом стробирования третьего дешифратора, второй выход первого триггера соединен с вторым входом третьего элемента И, выходы элементов ИЛИ группы соединены соответственно с первыми управляющими входами блока возведения десятичной цифры в квадрат, регистра основания, умножителя, преобразователя десятичного числа в дв.оичный код и десятичного счетчика,- входы выбора операций устройства соединены с первым и вторым входами триггера операций, информационный вход устройства соединен с входом установки числа регистра основания разрядные выходы которого соединены с первыми разрядными входами блока возведения десятичной цифры в квадрат и умно- жителя- выход которого соединен с первым входом преобразователя десятичного числа в двоичньй код, выход которого соединен со счетным входом десятичного счетчика, разрядные входы которого соединены с выходом блока возведения десятичной цифры в квадрат, вторые разрядные входы которого соединены с разрядными выходами вычитающего .счетчика и р вторыми разрядными входами умножителя, разрядные выходы регистра основания соединены соответственно с первой группой управляющих входов схемы сравнения, вторая группа управляющих входов которой соединена соответственно с разрядными выходами десятичного счетчика, первый информационный вход схемы сравнения соединен с первым входом первого элемента И и с шестым выходом группы элементов ИЛИ, выход схемы сравнения соединен с вторым входом первого элемента И, третий вход которого соединен с вторым информационным входом схемы сравнения и с вторым выходом третьего дешифратора, третий, четS1вертый, пятый, шестой и седьмой вькоды третьего дешифратора соедине ны соответственно с вторыми управля клцими входами блока возведения десятичной цифры в квадрат, умножител регистра основания,преобразователя десятичного числа в двоичный код и десятичного счетчика, выход первого элемента И соединен со счетным входом вычитающегося счетчика, вход начальной установки которого соединен с седьмым выкодом второго дешиф paTopaj выход генератора импульсов соединен с вторым входом преобразователя десятичного числа в двоичньш код и с четвертым входом первого элемента И, введены дешифратор и коммутатор J информационные входы которого соединены с выходами блока задания констант, управляющий вход которого соединен с управляющим входом дешифратора, стробирующим входом коммутатора и седьмьм выходом второго дейифратора, управляющие входы коммутатора соединены соответственно с выходами дешифратора, входы которого соединены соответственно с разрядными выходами регистра основания вькоды коммутатора соединены соответственно с разряпньми зхопами вычитающего счетчика, выход схемы сравнения соединен с вторым входом второго триггера. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 блок-схема преобразователя десятичного числа в двоичньш код. Устройство для возведения в квадрат и изотечения квадратного корня (фиг. 1) содержит регистр 1 основания, блок 2 возведения десятичной цифры в квадрат, умножитель 3, десятичньш счетчик 4, преобразователь 5 десятичного числа в двоичный код, генератор 6 импульсов, вычитающий счетчик 7, первый элемент И 8, схему 9 сравнения, блок 10 задания констант, дешифратор 11, коммутатор 12 блок 13 управления, содержащий генератор 14 тактов, счетчик 15, первый дешифратор 16, второй дешифратор 17, третий дешифратор 18, элемент ИЛИ 19, первый триггер 20, второй триггер 21, триггер 22 операций, второй элемент И 23, третий элемент И 24, четвертьй элемент И 25, счетчик 26 циклов, счетчик 27 тактов и группу элементов ШШ 28. 3 Преобразователь десятичного числа в двоичный код (фиг. 2) содержит сдвиговый регистр 29, элеме.нты И 3034, схему ИЛИ 35, триггер 36 и схему И 37, В предлагаемом устройстве возведение десятичного числа, например, А аЬс в квадрат, где с - цервый разряд числа, b - второй разряд числа, а - третий разряд, алгоритм работы устройства будет следую1Щ1й. Сначала первый разряд числа умножается на все разряды числа А, начиная с первого разряда. Затем на все разряды числа А умножается второй i разряд и т.д. Полученные; частные произведения суммируются, причем каждое последующее произведение сдвигается относительно предьщущего на один разряд влево. При основании числа, равном десяи, произведение одного разряда на ру1ой (oib,bci сс|) занимает два разяда, а их удвоенное произведение ри разряда. Преобразуем приведенную форму заиси в форму, удобную для анализа

Как видно из приведенной формы записи, суммирование частных произведений для возведения десятичного числа в крадрат реализуется при помощи десятичного счетчика.

Частные произведения, равные квадрату каждого разряда, записываются в определенные разряды счетчика: квадрат 1-го разряда (с) записывается в 1-й и 2-й разряды счетчика, квадрат 2-го разряда (Ь) записывается в 3-й и 4-й разряды счетчика, квадрат 3-го разряда (а) записывается в 5-й и 6-й разряды счетчика. Частны произведения, равные удвоенным прои ведениям двух разрядов (2сЬ, 2са, 2Ьа) преобразуются в число-импульсный код и поступают в определенные разряды счетчика, где суммируются с числом, находящимся там. Число-импульсньтй код удвоенного произведения 2с поступает на счетн вход 2-го разряда счетчика (единицы и на счетный вход 3-го разряда счет чика (десятки). Число-импульсный код удвоенного произведения 2 са поступает на счет ный вход 3-го разряда счетчика (еди ницы) и на счетньм вход 4-го разряд счетчика (десятки). Число-импульсный код удвоенного произведения 2Ьа поступает на счетный вход 4-го разряда счетчика (еди ницы) и на счетньш вход 5-го разряд счетчика (десятки) . Извлечение квадратного корня в предлагаемом устройстве из десятичного числа А производится методом последовательных проб за несколько циклов. Для этого последовательно возводятся в квадрат числа натураль ного ряда , ...,а,, отличающиеся друг от друга на одну градацию (единицу), начиная с максимального числа, которое можно извлечь из максимального числа А, и сравниваются с числом А. Последовательность таких операций продолжается до тех пор, пока вьшолняется нераА,

венство ЦТ.е. осуществляет2

ся условие а - - А О. Операция извлечения квадратного корня из де-, сятичного числа А оканчивается в тот момент, когда выполнено неравенство а А. Квадратный корень. из числа А равен числу а, когда впервые получена отрицательная или равная нулю разность А s 0.

В зависимости от величины числа А, изменяющегося от максимального зна- чения до нуля, извлечение квадратного корня начинается возведением в квадрат только тех разрядов числа натурального ряда а,, 0 квадрат которых равен максимальному

числу А для данного числа разрядов,

Операция возведения в квадрат производится следуюпщм образом.

При поступлении первого импульса из генератора 14 тактов в счетчик 15 дешифратор 16 вьщает разрешанмщтй сигнал через группу элементов ИЛИ 28

При поступлении 5-го и 6-го импульсов генератора 14 тактов в счет-. чик 15 производится преобразование удвоенного произведения 2 са в пропорциональное число импульсов, которое поступает в десятичный счетчик 4.

При поступлении 7-го и 8-го импульсов из генератора 14 тактов в счетчик 15 дешифратор 16 через группу элеменна регистр 1 ocнoвaния пo которому в него записывается число А alic которое необходимо возвести в квадрат . При 1юступлении в счетчик 15 второго импульса из генератора 14 тактов дешифратор 16 вьщает разрешающий сигнал, которьй через группу элементов ИЛИ 28 поступает на блок 2 возведения десятичньй цифры в квадрат. По этому сигналу квадрат каждого разряда а Ь , с числа А поступает на соответствующие установочные входы определенных двоично-десятичных счетчиков десятичного счетчика 4. Пои поступлении в счетчик 15, треть его импульса из генеоатоиа 14 тактов дешифратог) 16 вьшает через группу элементов ИЛИ 28 разрешающий сигнал на умножитель 3 и на преобразователь 5 десятичного числа в двоичный код. По этому сигналу удвоенное произведение 2сЬ (единицы) из умножителя 3 поступает на преобразователь 5 десятичного числа в двоичный код. При поступлении в счетчик 15 четвертого импульса из генератора 14 тактов дешифратор 16 выдает через группу элементов ИЛИ 28 разрешающий сигнал на умножитель 3 и на преобразователь 5 десятичного числа в двоичный код. По этому сигналу удвоенное произведение 2сЬ (десятки) из умножителя 3 постзпает на преобразователь 5 десятичного числа в двоичный код. 9113 тов или 28 вьщает разрешающий сигнал на умножитель 3 и преобразователь 5 десятичного числа в двоичный код, по которому производится преобразование удвоенного произведения-2Ьа, ; находящегося в умножителе 3, в пропор циональное число импульсов, которое поступает в десятичный счетчик 4. Операция извлечения квадратного корня производится следующим образом. Дешифратор 11 анализирует число А, поступившее в регистр 1 основания. /число (9, ,92,. ., 9), если (9,, число (9,,92,..«, 9,.,), если (9, ,92 число 9, , 92,..., , если (9, , 9, число (9 ,9), если (9,, А(9 число 9 если 9t А- О, 9р) из вычита Число (9,, 9,.. . э щего счетчика 7 поступает на блок 2 возведения десятичной цифры в квадрат и возводится в квадрат за несколько тактов, как было описано ранее. Затем производится сравнение . квадрата числа (9, ходящегося в десятичном счетчике 4, с числом AJ находящимся в регистре основания, схемой 9 сравнения. В первом цикле, если (9,9,..., 9fj) AS схема 9 сравнения вьдает разрешение на первьв элемент И 8. П следний выдает импульс, который пос пает на вычитающий счетчик 7. В вычитающем счетчике 7 находится число (9,92,..., 8„) . Это число возводит ся в квадрат и сравнивается с числом А. Во втором цикле, если (9;|,9,... 8j)2 А, схема 9 сравнения вьщает разрешение .на первый элемент И 8. Последний вьиает импульс, которьш йоступает на вычитающий счетчик 7. В вычитающем счетчике 7 находится число (9,925..., 7). Это число возводится в квадрат и сравнивается с числом А. Такие операции возведения числа, находящегося в вычитающем счетчике 7, в квадрат и сравнения полученного результата с числом А продолжаются до тех пор, пока выполняется усло3В зависимости от разрядности числа А дешифратор 11 вьщает командный сигнал на коммутатор 12, по которому из блока 10 задания констант в вы.читающий счетчик 7 записывается определенное число разрядозз натурального ряда а,, а, ...jQn S квадрат которых равен максимальному числу А для данного числа разрядов. В вычитающий счетчик 7 записьшаются:9) vA(9,92,. 9„.,) А (9, ,9 , о . ) 2 . n-l) , 9,.,) А .. . О У,.. )2; вне а (а, а а„)2 А. Когда число о станет меньше числа А , т.е. впервые будет получена отрицательная разность а - А -0, схема 9 сравнения запрещает прохождение сигналов генератора 6 кмпульсов, через первый элемент И 8 на счетньш вход выиитающего счетчиха 7. На этом операция извлечения квадратного корня из данного числа оканчивается. Изобретение характеризуется значительно меньшим временем вьтолнения операции извлечения квадратного корня из числа А, изменяющегося от максимального значения до нуля, В зависимости от величины числа А извлечение квадратного корня начинается возведением в квадрат только тех разрядов числа натурального ряда а , а,...,а„, квадрат которых равен максимальному числу А для данного числа разрядов. При двухразрядном десятичном числе А, из которого извлекается квадратньй корень, максимальное знаЧение которого равно 2, количество последовательных операций возведения числа в квадрат составляет 10 а в известном устройстве, таких операций 10. Таким образом, в предлагаемом устройстве время выполнения операции извлечения квадратного корня уменьшено в -75 раз.

to

Авторы

Даты

1985-01-07—Публикация

1982-04-05—Подача