блок контроля количества элементов в строках изображения, блок контроля количества.плоскостей, блок буферных регистров масок и коммутатор масок, вход признаков блока управления соединен с информационными входами блока контроля количества элементов в строках изображения, блока контроля количества плоскостей и коммутатора масок, входы дешифратора соединены с соответствующими входами команды блока управления, первый и второй выходы дешифратора соединены с первым и вторым выходами первой группы выходов блока управления, выходы с третьего по девятый дешифратора соединены с соответствующим входом управления блока контроля количества элементов в строках изображения, блока контроля количества плоскостей, блока буферных регистров масок и коммутатора масок, выход уравновешивания информационных потоков и выход признака циклического сдвига блока контроля количества элементов в строках изображения являются соответствующими выходами группы выходов блока управления, первый и второй выходы сброса блока контроля количества элементов в строках изображения подключены к счетному входу и входу установки блока контроля количества плоскостей, выход признака режима работы блока контроля количества элементов в строках изображения подключен к соответствующему выходу первой группы выходов блока управления и к первому синхровходу блока буферных регистров масок, выход признака конца загрузки которого подключен к соответствующему входу управления блока контроля количества элементов в строках изображения, выход управления режимом блока буферных регистров масок подключен к входу разрешения коммутатора масок, информацион ный вход которого объединен с информационным входом блока буферных ре.гистров масок и подключен к информационному выходу блока контроля количества плоскостей, выход сброса которого подключен к входу запуска очередного прохода блока контроля количества элементов в строках изображения, выход коммутатора масок подключен к входу разрешения приема масок блока буферных регистров масок, груп6179

па информационных выходов которого подключена к соответствующим выходам второй группы выходов блока управления,

2. Устройство по п.1, о т л и чающееся тем, что блок хранения масок содержит восьмиразрядный регистр сдвига, семиразрядный регистр сдвига, элемент ИЛИ, восемь коммутаторов, селектор, содержащий группу элементов И и элемент ИЛИ, причем информационные входы регистра с первого по восьмой подключены к выходу соответствующего коммутатора, первые информационные входы коммутатора с второго по восьмой подключены к выходам регистра с первого по седьмой, выходы с второго по восьмой которого подключены к группе информационных входов селектора соответственно, к группе управляющих входов которого подключены выходы с первого по седьмой регистра сдвига, выход селектора подключен к выходу признака маскирования блока и информационному входу первого коммутатора, вторые информационные входы коммутаторов подключены к соответствующим входам приема цепочки масок блока, управляющие входы всех коммутаторов объединены и подключены к входу признака режима работы блока, управляющий вход регистра сдвига подключен к выходу элемента ИЛИ, первый вход которого подключен к входу признака циклического сдвига блока, второй вход элемента ИЛИ подключен к входу признака режима работы блока, информационный вход регистра сдвига подключен к входу признаков блока, управляющий вход регистра сдвига подключен к входу управления сдвигом блока, причем первые входы группы элементов И подключены к группе управляющих входов селектора, а вторые входы - к группе информационных входов селектора, выходы элементов И группы подключены к входам элемента ИЛИ, выход которого подключен к выходу селектора, а каждый коммутатор содержит два элемента И, элемент ИЛИ, элемент НЕ, причем управляющий вход коммутатора соединен с первым входом первого элемента И и через элемент НЕ - с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к первому и второму информа ционным входам коммутаторасоответст венно, а выходы - к первому и втором входам элемента ИЛИ, выход которого является выходом коммутатора. 3, Устройство по n.l, отличающее ся тем, что блок формирования адресов содержит два элемента НЕ, четыре элемента И, два элемента задержки, первую группу эле ментов ИЛИ, вторую группу элементов ИЛИ, три линии задержкиJ причем первые входы первого и второго элементо И объединены и подключены к первому информационному входу блока, первые входы третьего и четвертого элементов И объединены и подключены к второму информационному входу блока третий информационный вход которого подключен к входу первой линии задер ки, выходы первого и второго элемеитов НЕ подключены к вторым входам первого и третьего элементов И соответственно, входы первого и второго элементов НЕ, второй вход второго эл мент.а И и второй вход четвертого эле мента И объединены и подключены к входу уравновешивания информационных потоков блока, выходы первого и третьего элементов И подключены к первым входам первого и второго зле- ментоз ИЛИ первой группы соответственно, выходы второго и четвертого элементов И подключены к входам первого и второго элементов задержки соответственно, выходы которых подключены к вторьм входам первого и второго элементов ИЛИ первой группы соответственно, первые входы элементов ИЛИ второй группы подколочены к cooтвeтcтвyюD IJм входам адреса блока, j-й выход. -и линии задержки (i 1, 2, 3; j 1, 2, 3) подклзочен к второму входу ё го элемента ИЛИ второй группы ( ((-1)+), выход каждого элемента ИЛИ второй группы подключен к соответствующему выходу адреса блока, второй выход первой линии задержки подключен к выходу признака центрального элемента блока. А. Устройство по п.1, отличающееся тем. что блок контроля количества плоскостей содержит два счетчика, два компаратора, два формирователя сигналов, четыре элемента ИЛИ, три элемента И линию задержки, элемент задержки,, причем выход первого формирователя сигналов подключен к выходу очередности масок блока, вход формирователя сигналов подкл 1чен к вьгхомУ парвого элемента МК, первый вход которого подключен к выходу парвого элемента И, а второй вход первого элемента ИЛИ объединен с первым входом второго элемента ИЛИ и подключет к выходз линии задержки, вход сброса первого счетчика подключен к выходу второго элемента 1ШИ, второй вход которого объединен с входом сброса второго счетчика и подключен к соответствующему входу блока, первый вход первого элемента И через элемент задержки подключен к входу управления первого счетчика и входу разрешения сброса блока, счетный вход первого счетчика подключен к счетному входу блока, прямые выходы первого счетчика подключены к соответств: ;эщим входам первого компаратора, иыход которого, подключен к инверсному входу первого элемента И, входу второго формирователя сигналов, первым входам второго н третьего элементов И и первому входу третьего элемента - lUtti, второй вход которого подключен к управляющему входу блока, выход третьего элемента ИЛИ подключен к входу управления второго счетчика, счетный вход которого под кл:очен : выходу четвертого элемента РШИ, первый вход которого подключен к выходу второго формирователя сигналов, а второй вход - к информационному входу блока, прямые выходы второго счетчика подключены к соответствующим входам второго компаратора, выход которого подключен к второму прямому входу третьего элемента И и второму инверсному входу второго элемента И, выход которого под- ключен к входу линии задержки и выходу очередности масок блока, выход третьего элемента И подключен к вы- . ходу Останов блока. 5. Устройство по П.1, отличающееся тем, что блок контроля количества элементов в строкахизображения содеряа1т счетчик, четыре триггера, компаратор, два формирователя сигнала, четыре элемента И, три элемента ИЛИ, первую и вторую группы элементов ИЛИ, линшо задержки, причем вькод первого элемента И подключен к выходу урар.повепшпания информационных потоков блока, первый и второй входы первого элемента И 11одк.таочены к прямьм выходам пеового и второго триггеров соответственно, вход данных первого триггера объединен с первым входом второго элемента И и подключен к информационному входу блока, вход управления первого триггера подключен к первому управляющему входу блока, второй вход второго элемента И подключен к второму управляющему входу блока, выход второго элемента И подключён к первому входу первого элемента ИЛИ первой группы элементов ИЛИ, второй вход которого подключен к входу запуска блока, а третий вход первого элемента ИЛИ первой группы объединен с первым входом первого элемента ИЛИ второй группы и подключен к выходу первого формирователя сигналов, выход которого подключен также к счетному выходу блока, второй вход первого элемента ИЛИ второй группы объединен с первым входом первого элемента ИЛИ и подключен к выходу второго формирователя сигнала, выход которого подключен также к выходу признака режима работы блока, выходы первых элементов ИЛИ первой и второй групп подключены к объединенным первым входам второго и третьего элементов ИЛИ каждой группы, вторые входы - прямой и инверсный - второго и третьего элементов ИЛИ каждой группы объединены с вторым входом -- первого элемента ИЛИ и подключены к третьему управляющему входу блока, выход первого элемента ИЛИ подключен к входу сброса счетчика, выходы вторых элементов ИЛИ каждой rpynni i под1

79

ключены к входам J второго и третьего триггеров соответственно, выходы третьих элементов ИЛИ каждой группы подключены к входам К второго и третего триггеров соответственно, прямой выход второго триггера подключен к первому входу третьего элемента И, первый вход которого подключен к входу признака загрузки последнего элемента блока, выход третьего элемента И подключен к входу второго формирователя сигналов, прямой выход третьего триггера подключен к первому входу четвертого элемента И, второй инверсный вход которого объединен с входом первого формирователя сигналов, первыми входами второго и третьего элементов ИЛИ и подключен к выходу компаратора, выход которого также подключен к выходу сигнала сброса блока, вторые входы - прямой и инверсный - второго и третьего элементов ИЛИ объединены и подключены к третьему управляющему входу блока, выход четвертого элемента И подключен к объединенным управляющему входу счетчика и входу линии задержки, выход которой является выходом циклического сдвига блока, выходы второго и третьего элементов ИЛИ подключены к J и К входам первого триггера соответственно, прямые выходы счетчика подключены к соответствующим входам компаратора , входы синхронизации счетчика и второго триггера подключены к соответствующим входам блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный процессор | 1987 |

|

SU1534466A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1988 |

|

RU1637638C |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1439671A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Ассоциативное запоминающее устройство | 1983 |

|

SU1095238A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

1. МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ЛОГИЧЕСКОЙ ОБРАБОТКИ БИНАРНЫХ ИЗОБРАЖЕН, содержащее блок управления, h табличных запоминающих блоковS блок формирования адресов , блок хранения масок и п злементов И, причем вход команды блока управления соединен с входом команд устройства, первый выход первой группы выходов блока управления соединен с адресным входом группы входов блока хранения масок, второй выход группы выходов блока управления сое:динеи с информационным входом каждого из табличных запоминающих блоков, выход каждого из которых соединен с первь1м входом соответствующего элемента И, выходы элементов И образуют выход устройства, отличаю-. щ е е с я тем, что, с целью увеличеняя производительности, в него введены (п-1) блоков формирования адресов и (п-1) блоков хранения масок. teli. , --- ..| причеь адресн1,:е и информационные входы.блоков хранения масок со второго по п -и объединены и подклточены первой группе выходов блока управления, второй и третий выходы первой группы выходов которого подключены к соответствующим входам адреса и информационным группам входов первого блока хранения масок, вход запиcit масок каждого из Ц блоков хранения масок соединен с соответствующим вь ходом второй группы выходов блока управления, кг1ждого из П блоков хранения масок соединен с вторым входом соответствующего элемента И, третий вход которого соединен с выходом признака центрального (О элемента соответствующего блока формирования адресов, вход разрешения обработки каждого блока формирования адресов соединен с выходом уравновешивания 1шформационных потоков блока управления, j -и вход группы информационных входов -го блока формирования адресов (,3,4; -i 1, СО 9д ..., V ) соединен с 6 -м входом группы информацио1п-1ых входов устройства () 2) 5 вход признака адреса каждого блока формирования адресов ;о соединен с входом признака адреса устройства, информационньз выход каждого блока формирования адресов соединен с адресным входом соответствующего табличного запоминающего блока, вход признаков блока управления, а также информационный вход каждого табличнг.го запоминающего блока и информацио гный вход каждого блока хранения масок соединены с входом признака ycTpoficTBa, причем блок управления содержит деишфратор.

Изобретение относится к специализированным устройствам цифровой вычислительной техники, ориентированным на логическую (на основе клеточной логики) обработку двухградационных изображений.

Известны устройства обработки бинарных изображений на основе информации от центрального элемента (ЦЭ) и от его ближайших соседей (соседних элементов), содержащие блок коммутаторов управляющих линий, блок

суммирования заданных значений соседних элементов и блок квантования по порогу 1J .

Однако в данных устройствах реализован принцип параллельной обработки всех элементов изображения, что приводит к сложной структуре устройства в целом.

Наиболее близким к изобретению по технической сущности является процессор Престона-Херрона (РНР), включающий логику трансляции команд 3 управляющей ЭВМ (устройство управле ния), три буферных запоминающих уст ройства емкостью 32 К бит каждое, регистровую логику управления кой названных запоминающих устройст шестнадцать табличных запоминающих устройств емкостью 512 бит каждое, матричное устройство формирования табличных адресов, а также 16-разрядный регистр маски подполей (устройство хранения масок) и логику (вентили) маскирования 2J. Однако в известном процессоре число одновременно обрабатываемых точек изображения п (в данном случае ) и оборудование процессора в целом жестко связаны с шириной каналов управляющей ЭВМ; количество обрабатываемых в единицу времени то чек изображения ограничено быстродействием управляющей ЭВМ и (когда не требуется динамического изменени характеристик маскирования) не може превосходить валичинь jb r, (1) где П - число одновременно обрабат ваемых точек изображения; - тактовая частота управляющей ЭВМ. Цель изобретения - увеличение производительности путем увеличения функциональных возможностей специализированного устройства логической обработки бинарных изображений и упрощение аппаратного изменения его вычислительной мощности (количества одновременно обрабатываемых точек изображения). Поставленная цель достигается тем, что в устройство, содержащее блок управления, О табличньпс запоминающих блоков, блок формирования адресов, блок хранения масок и П элементов И, причем вход команды блока управления соединен с входом команд устройства, первый выход первой группы выходов блока управления соединен с адресньм входом группы входов блока хранения масок второй выход группы выходов блока управления соединен с информационны входом каждого из табличных запоминающих блоков, выход каждого из KO рых соединен с первым входом соответствующего элемента И, выходы эл ментов И образуют выход устройства 79Л введены (Г)-1) блоков формирования адресов и (п-1) блоков хранения масок, причем адресные и информационные входы блоков хранения масок со второго по п-и объединены и подключены к первой группе вь ходов блока управления, второй и третий выходы первой группы выходов которого подключены к соответствующ м входам адреса и информационным группам входов первого блока хранения масок, вход записи масок каждого из f) блоков хранения масок соединен с соответствующим выходом второй группы выходов блока управления, выход каждого из iJVблоков хранения масок соединен с вторым входом соответствующего элемента И, третий вход которого соединен с выходом признака центрального элемента соответствующего блока формирования адресов, вход разрешения обработки каждого блока формирования адресов соединен с выходом уравновешивания информационных потоков блока управления, j -и вход группы информационных входов -го блока формирования адресов (2, 3, 4;( 1, ...,ц ) соединен с -м входом группы информационных входов устройства ( +( ч- 2), вход признака адреса каждого блока формирования адресов соединен с входом признака адреса устройства,информационный выход каждого блока формирования адресов соединен с адресным входом соответствующего табличного запоминающего блока, вход признаков блока управления, а также информационньй вход каждого табличного запоминающего блока и информационный вход каждого блока хранения масок соединен с входом признака устройства, причем блок Управления содержит дешифратор, блок контроля количества элементов строках изображения, блок.контроля количества плоскостей, блок буферных регистров масок и коммутатор масок, вход признаков блока управления соединен с информационными входами блока контроля количества элементов в строках изображения, блока контроля количества плоскостей и коммутатора масок, входы дешифратора соединены с соответствующими входами команды блока управление, первый и второй выходы дешифратора соединены с первым и вторым выходами первой группы выходов блока управления, выходы с третьего по девятый дешифратора соединены с соответствующим входом управления блока контроля количества элементов в строках изображения, блока контроля количества плоскоетей, блока буферных регистров масок и коммутатора масок, выход уравновеишвания информационных потоков и выход признака циклического сдвига блока контроля количества элементов в строках изображения являются соответствующими выходами группы выходов блока управления, первый и второ выходы сброса блока контроля количества элементов в строках изображения подключены к счетному входу и вы ходу установки блока контроля количества плоскостей, выход признака режима работы блока контроля количества элементов в строках изображения подключен к соответствующему вы ходу первой группы выходов блока уп.равления и к первому синхровходу бл ка буферных регистров масок, выход признака конца загрузки которого подключен к соответствующему входу управления блока контроля количества элементов в строках изображения, выход управления режимом блока буферных регистров масок подключен к входу разрешения коммутатора масок, информационный вход которого объеди нен с информационным входом блока б ферных регистров масок и подключен информационному выходу блока контроля количества плоскостей, выход сброса которого подключен к входу запуска очередного прохода блока контроля количества элементов в строках изображения, выход коммутатора масок подключен к входу разреш ния приема масок блока буферных регистров масок, группа информационны выходов которого подключен к соответствующим выходам второй группы выходов блока управления. Блок хранения масок содержит восьмиразрядный регистр сдвига,семиразрядный регистр сдвига, элемент ИЛИ восемь коммутаторов, селектор, соде жащий группу элементов И и элемент ИЛИ, причем информационные входы регистра с первого по восьмой подключены к выходу соответствующего коммутатора, первые информационные входы коммутатора с второго по вось мой подключены к выходам регистра с первого по седьмой, выходы с втор го по восьмой которого подключены к группе информационных входов селектора соответственно, к группе управляющих входов которого подключены выходы с первого по седьмой регистра сдвига, выход селектора подключен к выходу признака маскирования блока и информационному входу первого коммутатора, вторые информационные входы коммутаторов.подключены к соответствующим ,входам приема це- . почки масок блока, управляющие входы всех коммутаторов объединены и подключены к входу признака режима работы блока, управляющий вход регистра сдвига подключен к выходу элемента ИЛИ, первый вход которого подключен к входу признака циклического сдвига блока, второй вход элемента ИЛИ подключен к входу признака режима работы блока, информационньй вход регистра сдвига подключен к входу признаков блока, управляющий вход регистра сдвига подключен к входу управления сдвигом блока, причем первые входы группы элементов И подключены к группе управляющих входов селектора, а вторые входы - к группе информационных входов селектора, выходы элементов И группы подключены к входам элемента ИЛИ, выход которого подключен к выходу селектора, а каждый коммутатор содержит два элемента И, элемент ИЛИ, элемент НЕ, причем управляющий вход коммутатора соединен с первым входом первого элемента И и через элемент НЕ - с первым входом второго элемента И, вторые входы первого и второго элементов И подключены к первому и второму о информационным входам коммутатора соответственно, а выходы - к первому и второму входам элемента ИЛИ, выход которого является выходом коммутатора. Блок формирования адресов содержит два элемента НЕ, четыре элемента И, два элемента задержки, первую группу элементов ИЛИ, вторую группу элементов ИЛИ, три линии задержки, причем первые входы первого и второго элементов И объединены и подключены к первому информационному входу блока, первые входы третьего и четвертого элементов И объединены и подключены к второму информационному входу блока, третий информационный вход которого подключен к .входу первой линии

задержки, выходы первого и второго элементов НЕ подключены к вторым входам первого и третьего элементов И соответственно, входы первого и второго элементов НЕ,, второй вход т второго элемента И и второй вход четвертого элемента И объединены и подключены к входу уравновешивания информационных потоков блока, выходы первого и третьего элементов И подключены к первым входам первого и второго элементов ИЛИ первой группы соответственно, выходы второго и четвертого элементов И подключены к входам первого ,и второго элементов задержки соответственноэ выходы которых подключены к вторым входам первого и второго элементов Р1ЛИ первой группы соответственно, первые входы элементов ИЛИ второй группы подключены к соответствующим входам адреса блока, j-и выход -и линии задержки (, 2, 3; , 2, 3) подключен к второму, входу -го элемента ИЛИ второй группы ( (i-D + j), выход каж,цого элемента ИЛИ второй группы подключен к соответствующему выходу адреса блока, второй выход ;первой линии задержки подключен к выходу признака центрального элемен;та блока,

«

; Блок контроля количества плоскостей содержит два счетчика, два компаратора, два формирователя сигналов четыре элемента ИЛИ, три элемента И линию задержки, элемент задержки, причем выход первого формирователя сигналов подключен к выходу очередности масок блока, вход формирователя сигналов подключен к выходу первого элемента ИЛИ, первый вход кото; рого подключен к выходу первого эле: мента И, а второй вход первого элемента ИЛИ объединен с первым входом второго элемента ИЛИ и подключен к выходу линии задержки, вход сброса первого счетчика подключен к выходу второго элемента ИЛИ, второй вход которого объединен с входом сброса второго счетчика и подключен к соответcтвyюn eмy входу блока, первый вход первого элемента И через элемент задержки подключен к входу управления первого счетчика и входу разрешения сброса блока, счетный вход первого счетчика подключен к счетному входу блока, прямые выходы первого счетчика подключены к соответствующим входам первого компаратора, выход которого подключен к инверсному входу первого элемента И, входу второго формирователя сигналов, первым входам второго и третьего элементов И и первому входу третьего элемента ИЛИ, второй вход которого подключен к упраБляюп(ему входу блока, выход третьего элемента ИЛИ подключен к входу управления второго счетчика, счетный вход которого подключен к выходу четвертого элемента ИЛИ, первый вход которого подключен к выходу второго формирователя сигналов, а второй вход - к информационному входу блока, прямые выходы второго счетчика подключены к соответствующим входам второго компаратора, выход которого подключен к второму прямому входу третьего элемента И и второму инверсному входу второго элемента И, выход которого подключен к входу линии задержки и выходу очередности масок блока, выход третьего элемента И подключен к выходу Останов блока.

Блок контроля- количества элементов в строках изображения содержит счетчик, четыре триггера, компаратор два формирователя сигнала, четыре элемента И, три элемента ИЛИ, первую и вторую группы элементов ИЛИ, линию задержки, причем выход первого элемента И подключен к выходу уравновешивания информационных потоков блока,первый и второй входы первого элемента И подключены к прямым выходам первого и второго триггеров соответственно, вход данных первого триггера объединен с первым входом второго элемента И и подключен к информационному входу блока, вход управления первого триггера подключен к первому управляющему входу блока, второй вход второго элемента И подключен к второму управляющему входу блока, выход второго элемента И подключен к первому входу первого элемента ИЛИ первой группы элементов ИЛИ второй вход которого подключен к входу запуска блока, а третий лход первого элемента ИЛИ первой группы объединен с первым входом первого элемента ИЛИ вторгй группы и подключен к выходу первого формирователя сигналов, выход которого подключен также к счетному выходу блока, второй вход первого элемента ИЛИ второй группы

1

объединен с первым входом первого элемента РШИ и подключен к, выходу второго формирователя сигнала , выхо которого подключен также к выходу признака режима работы блока, выходы первых элементов ИЛИ первой и второй. групп подключены к объединенным первым входам второго и третьего элементов ИЛИ каждой группы, вторые входы - прямой и инверсньй - второго и третьего элементов ИЛИ каждой группы объединены с вторым входом первого элемента ИЛИ и подключены к третьему управляющему входу блока, выход первого элемента ИЛИ подключен к входу сброса счетчика, выходы вторых элементов ИЛИ каждой группы подключены к входам J второго и третьего триггеров соответственно, выходы третьих элементов ИЛИ каждой группы подключены к входам К второго и третьего триггеров соответственно, прямой выход второго триггера подключен к первому входу третьего элемента И, первьй вход которого подключен к входу признака загрузки последнего элемента блока, выход третьего элемента И подключен к входу второго формирователя сигналов, прямой выход третьего триггера подключен к первому входу четвертого элемента И, второй инверсный вход которого объединен с входом первого формирователя сигналов, первыми входами второго и третьего элементов ИЛИ и подключен к выходу компаратора, выход Которого также подключен к выходу сигнала сброса блока, вторы входы - прямой и инверсный, - второго и третьего элементов ИЛИ объединены и подключены к третьему управляющему входу блока, выход четвертого элемента И подключен к объединенным управляющему входу счетчика и входу линии задержки, выход которой являет ся выходом циклического сдвига блока, выходы второго и третьего элементов ИЛИ подключены к J и К входам первого триггера соответственно, прямые выходы счетчика подключены к соответствующим входам компаратора, входы синхронизации счетчика и второго триггера подключены к соответствующим входам блока.

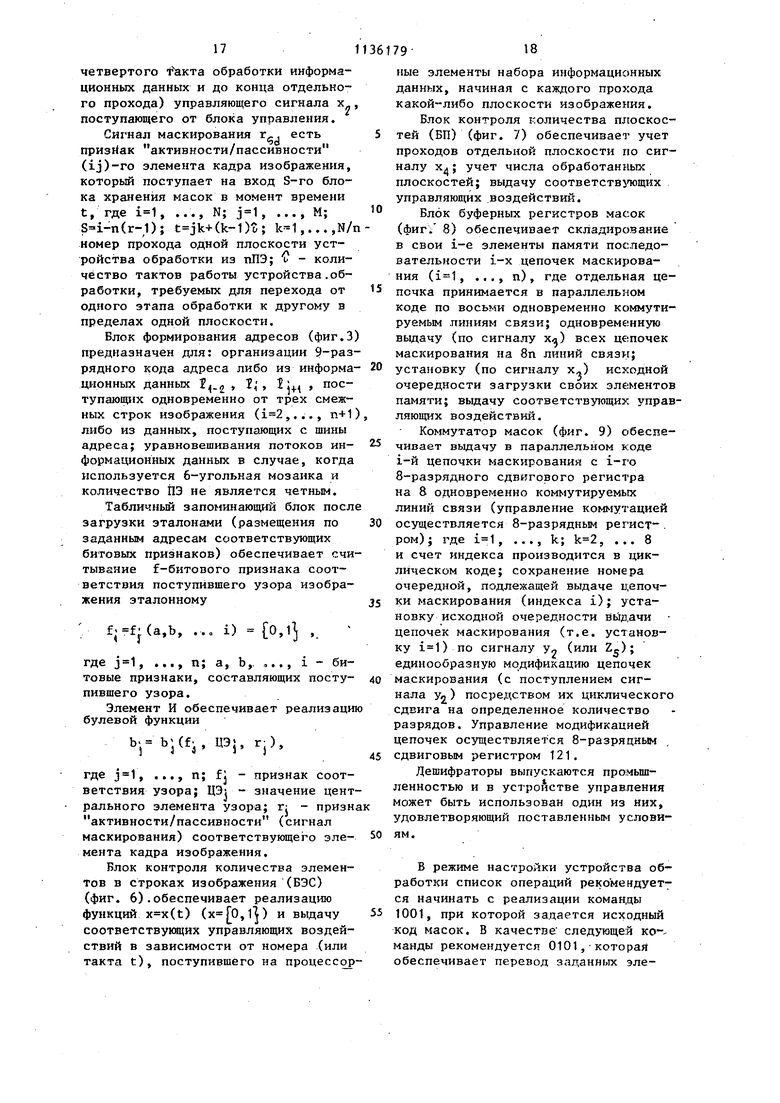

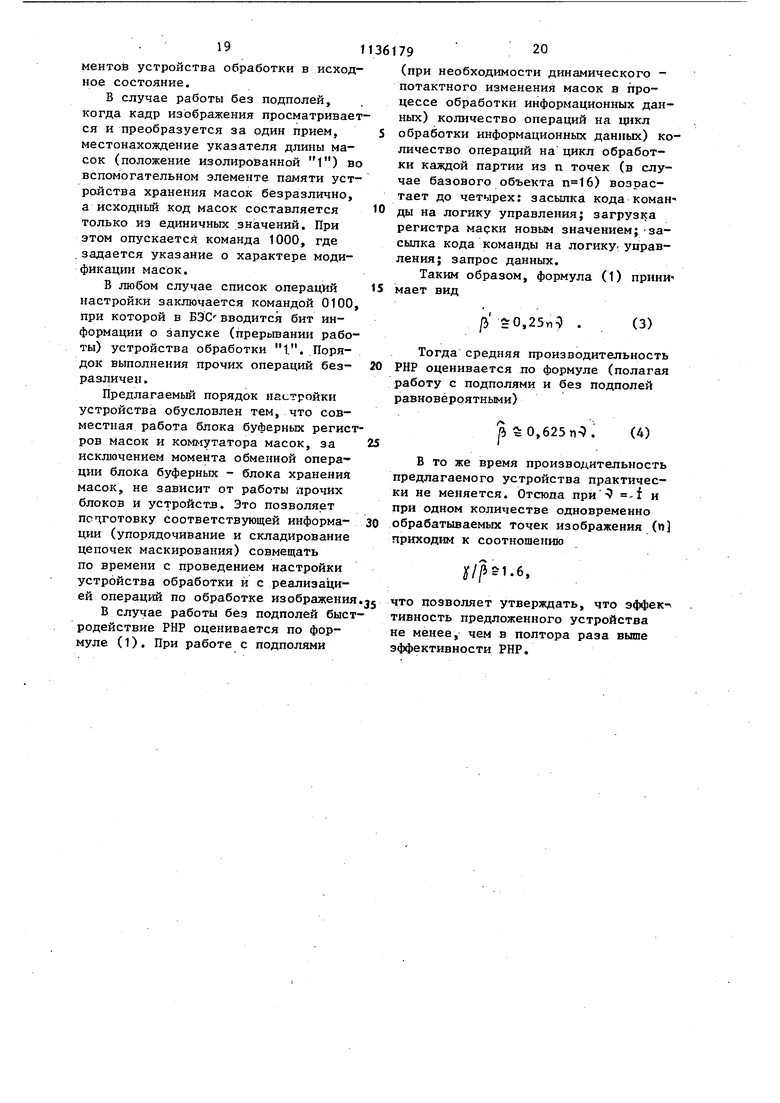

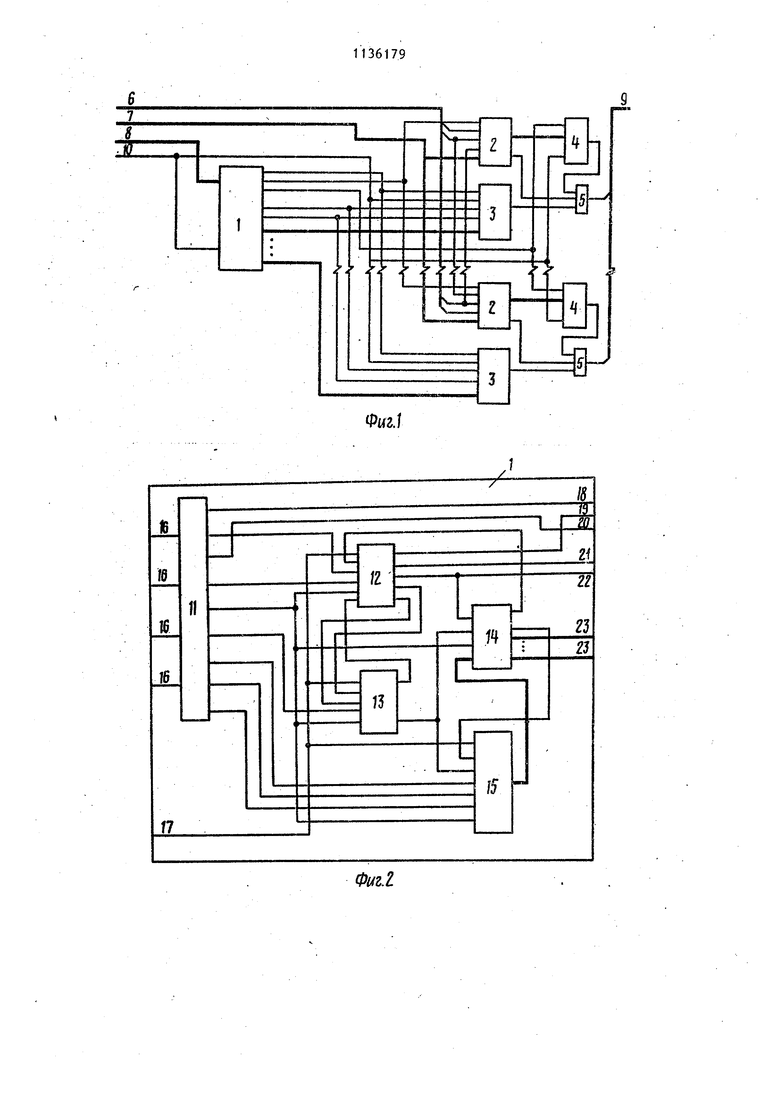

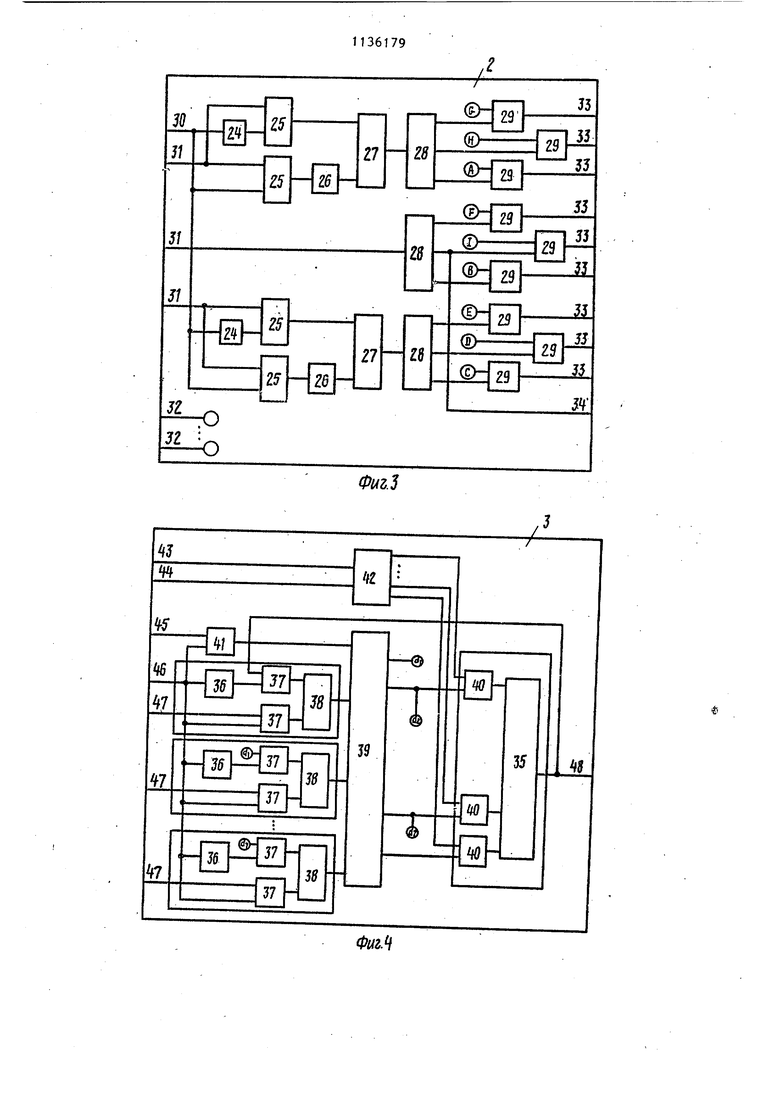

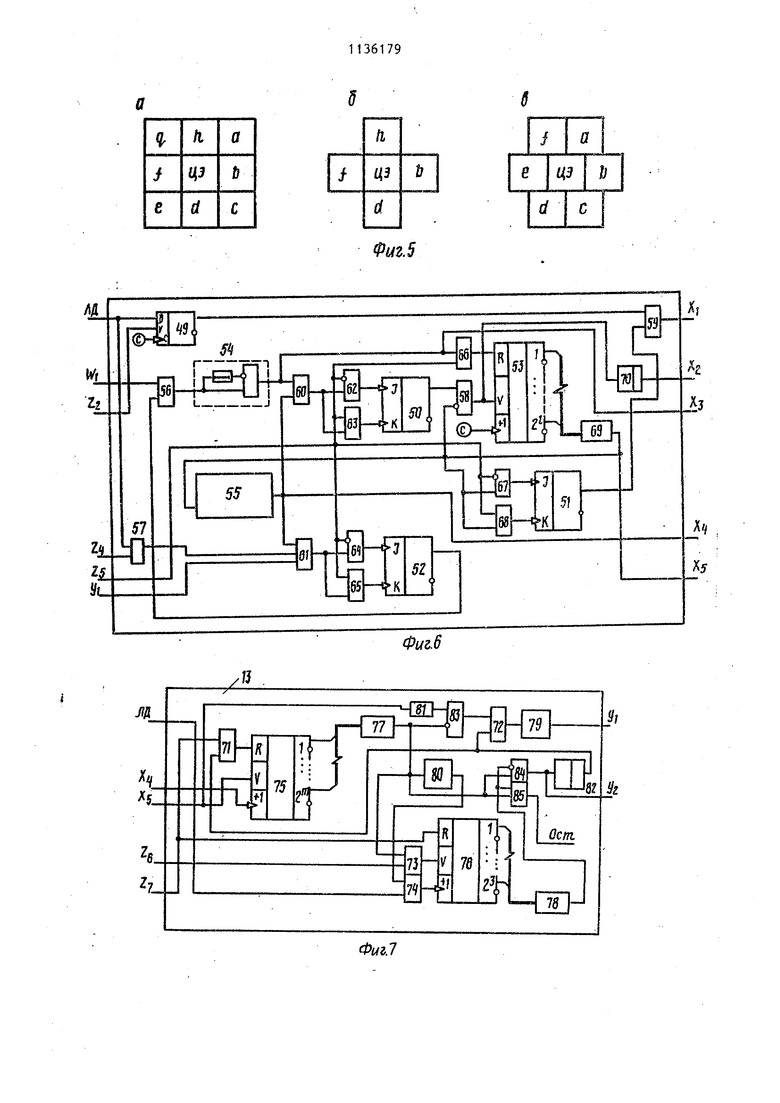

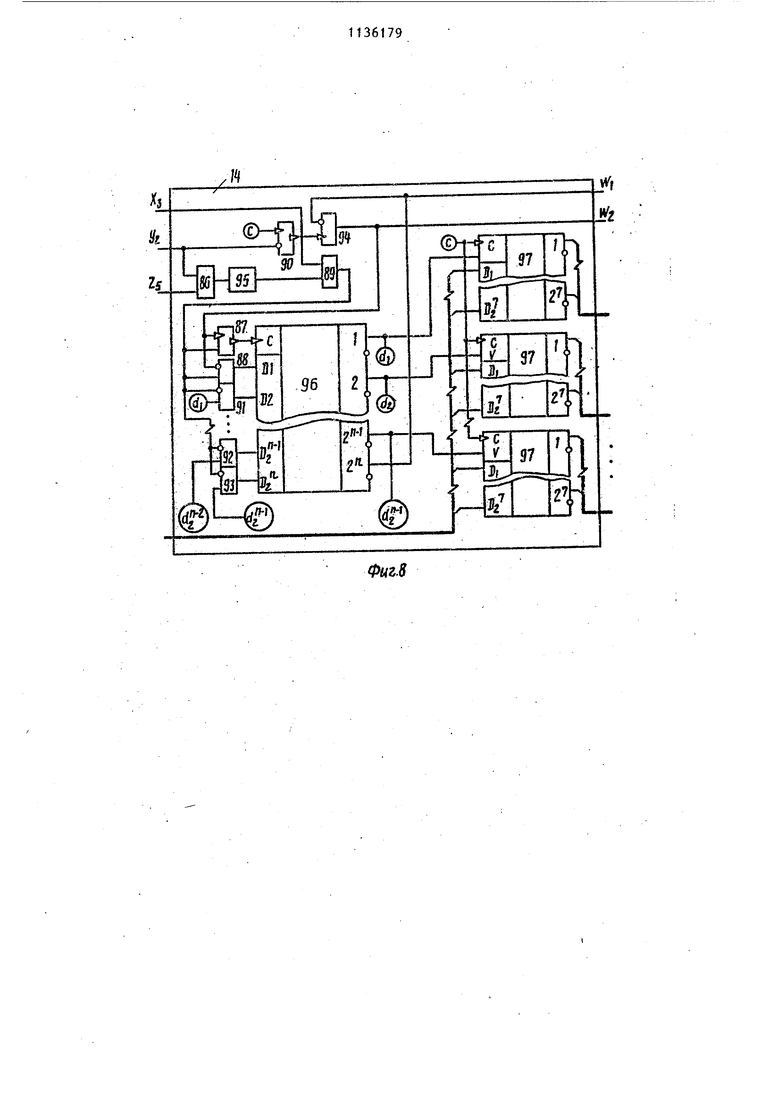

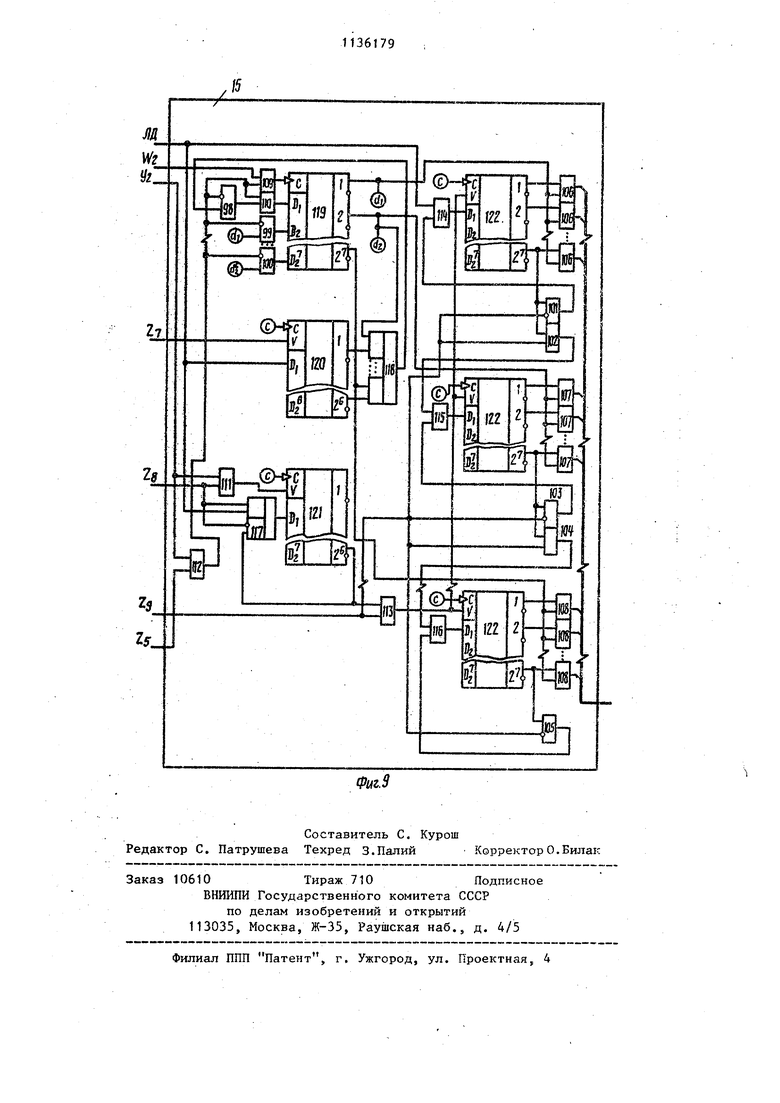

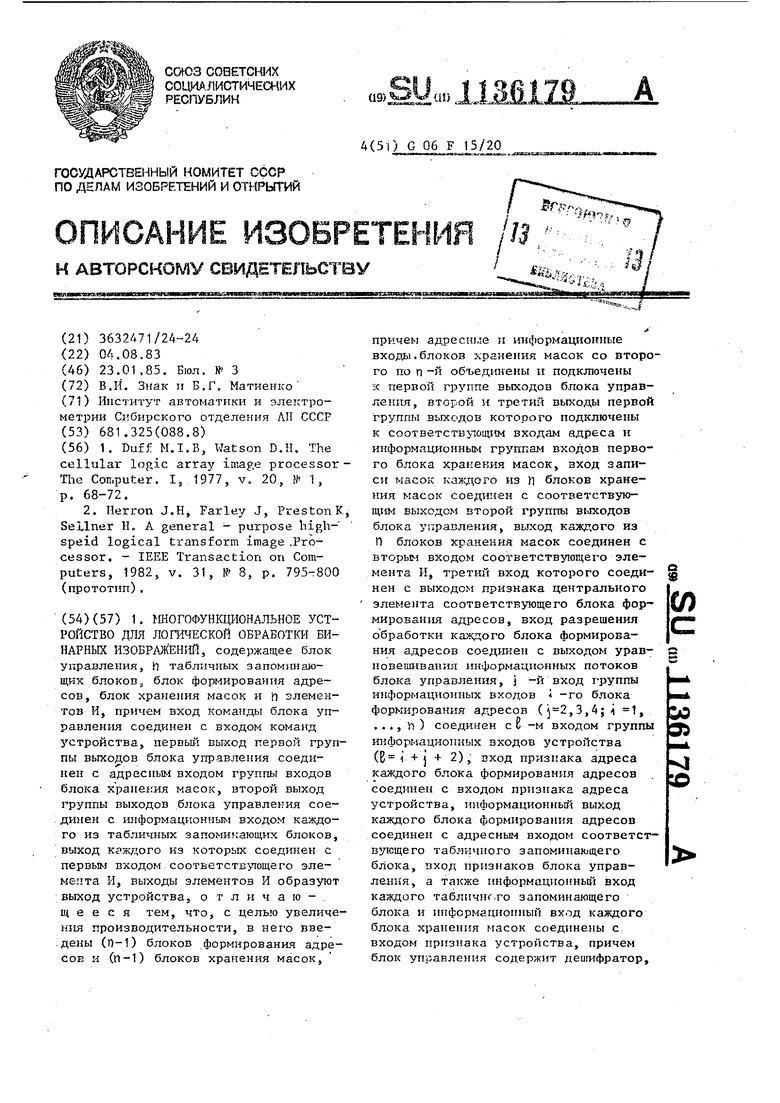

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 блок управления; на фиг. 3 - блок формирования адресов; на фиг. А 10

79

блок хранения масок; на фиг. 5а-в основные конфигурации окон (окрестностей центрального элемента), используемых для анализа изображений (на фиг. 5а - окно из 9 элементов, на фиг. 56 - окно из 5 элементов, на фиг. 5в - окно из семи эле-.ментов) на фиг. 6-9 - схемы блоков контроля количества элементов в строках изображения, контроля количества плоскостей, буферных регистров масок и коммутатора масок.

Многофункциональное устройство содержит блок 1 управления, блоки 2 формирования адресов, блоки 3 хранения масок, табличные запоминающие блоки 4, элементы И 5, шину 6 входных данных, шину 7 адреса, шину 8 команд, шину 9 выходных данных, линию 10 данных.

Блок 1 управления содержит дешифратор 11, блок 12 контроля количества элементов в строках изображения, блок 13 контроля количества 1ШОСкостей, блок 14 буферных регистров масок, коммутатор 15 масок, управляющие входы 16, информационный вход 17, управляющие выходы 18-22 с первого по пятый, групповые выходы 23 связи с блоками хранения масок.

Блок 2 формирования масок содержит элементы НЕ 24, элементы И 25, элемент 26 задержки первой группы. Элементы ИЛИ 27 первой группы, элементы 28 задержки второй группы, элементы ИЛИ 29 второй группы, управляющий вход 30, информационные входы 31 первой группы, информационные входы 32 второй группы, 1 ЫХОДЫ 3

связи, выход 34 признака центрального элемента.

Блок 3 хранения масок сод€:ржит первый элемент ИЛИ 35, элементы НЕ 36, восемь пар элементов К 37 первой группы, элементы ИЛИ 38, восьмиразрядный регистр 39, элем€;нты И 40 второй группы, второй элемент ИЛИ 41, сдвиговый регистр 42, первый управляющий вход 43, информационный вход 44, второй и третий управляющие входы 45 и 46, входы 1-1 связи выход 48 йризнака маскирования.

Блок 12 контроля количества элементов в строках изображения содержи триггеры 49-52, счетчик 53, формирователи 54 и 55 сигналов, элементы И 56-59, элементы ИЛИ 60-68, компаратор 69, линию 70 задержки.

Блок 13 контроля количества плоскостей содержит элементы ИЛИ 71-74, счетчики 75-76, компараторы 77-78, формирователи 79-80 сигналов, элеент 81 задержки, линию 82 задерж- 5 ки, элементы И 83-85.

Блок 14 буферных регистров масок содержит элементы ИЛИ 86-89, элементы И 90-94, Формирователь 95 сигналов,

регистр 96, группу регистров 97. О

Коммутатор 15 масок содержит элементы И 98-105, первую группу элементов И 106, вторую группу элементов И 107, третью группу элементов И 108, элементы ИЛИ 109-116, элемент 5 24 содержит элемент ИЛИ 117, селектор 118, регистры 119-121, группу регистров 122.

Предлагаемое устройство ориентировано на логическую обработку двух- 20 градационных изображений. Однако возможности устройства позволяют использовать его также дль цчлей квантования по порогу rti-разрядных двоичных чисел (). При этом прием информации, принятие.решения и выдача результата производятся на каждом такте работы такого устройства обработки, где тактовая частота ограничена сверху только временем 30

обращения к табличному запоминающему блоку.

Специфика работы устройства состоит в том, что исходная информация исследуется параллельно-последова- 35 тельно: параллельно по строкам изображения, последовательно по элементам строк. При этом информация разбита на ДГ потоков, где отдельный поток включает информацию от центральной 40 и двух смежных строк. В соответствии с этим в конструктивном плане устройство состоитИЗ процессорных элементов -(ПЭ), каждый из которых включает запоминающий блок (табличный - ТЗБ) 45 на 512 бит, блок формирования адресов ТЗБ, блок хранения масок и элемент И. ПЭ идентичны друг другу и. работают под управлением одного блока управления (БУ).. 50

Таким образом, дпя обработки одного кадра бинарного изображения размерности MN требуется N/n этапов (или проходов), где отдельный этап обработки состоит из М тактов - чис- 53 ла элементов в строке кадра. Перед началом каждого этапа обработки блоком управления во все ПЭ через внутрисхемные шины связи вводится скорректированная информация о характеристиках подполей (корректировка производится параллельно и независимо от работы ПЭ). Вьщача результатов обработки на каждом этапе начинается с третьего такта, где задержка определяется требованием подготовки информации для ТЗБ. Таким образом, скорость работы устройства определяется величиной

(2)

nf,

где n - количество ПЭ (одновременно обрабатываемых точек изображения );

f - тактовая частота работы устройства, не зависящая от тактовой частоты управляющей ЭВМ (или любого другого внешнего устройства управления) на весь период обработки кадра. I

Специально организованная исходная информация, хранимая в соответствующих устройствах памяти, поступает с шины входных данных на трехразрядные линии задержки блока формирования адресов либо непосредственно, либо через одноразрядные элементы задержки в зависимости от состояния схемы переключения, определяемой БУ (конкретно-- блоком контроля количества, элементов в строках изображения, фиг. 2). Трехразрядные линии задержки формирзтот содержимое 9-разрйдного регистра адреса ТЗБ. Считывание признака соответствия поступившего узора изображения заданному (эталонному) можно произйодить с третьего такта каждого этапа работы устройства (первые два требуются для формирования исходного узора). При этом признак ЦЭ, хранимый в течение такта в среднем разряде цент- : рального ЭЗ (элемента хранения составляющих центральной строки) , пос- тупает также на логику маскирования.

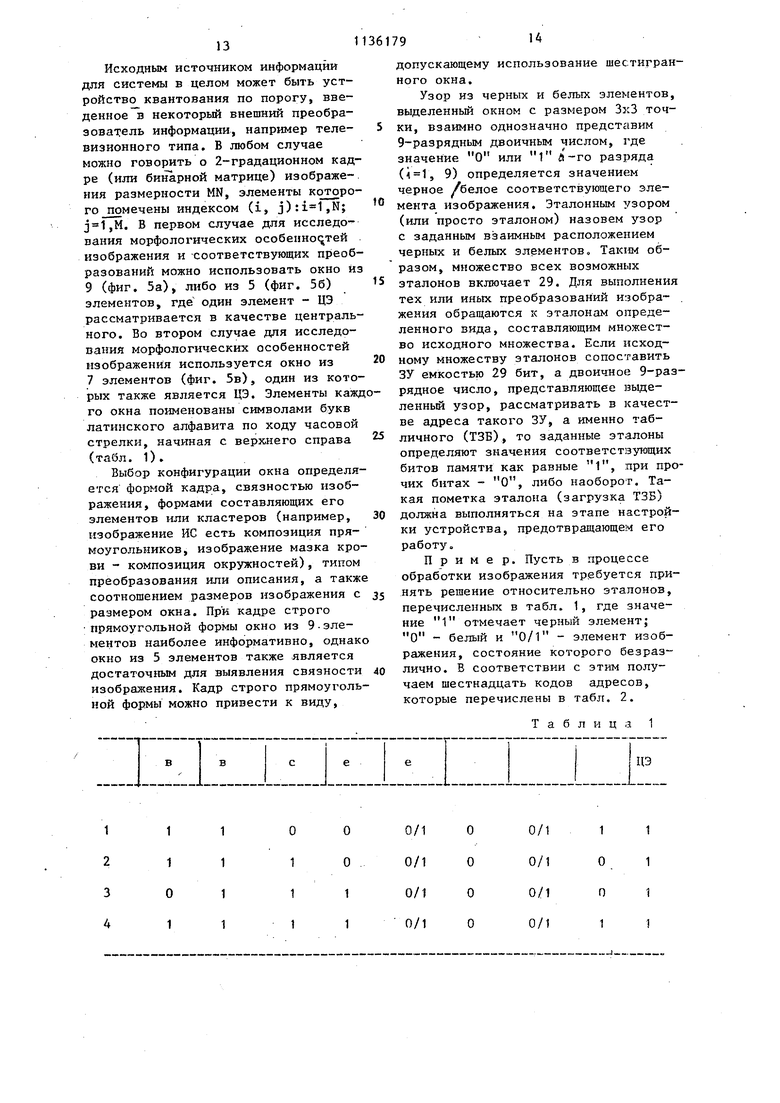

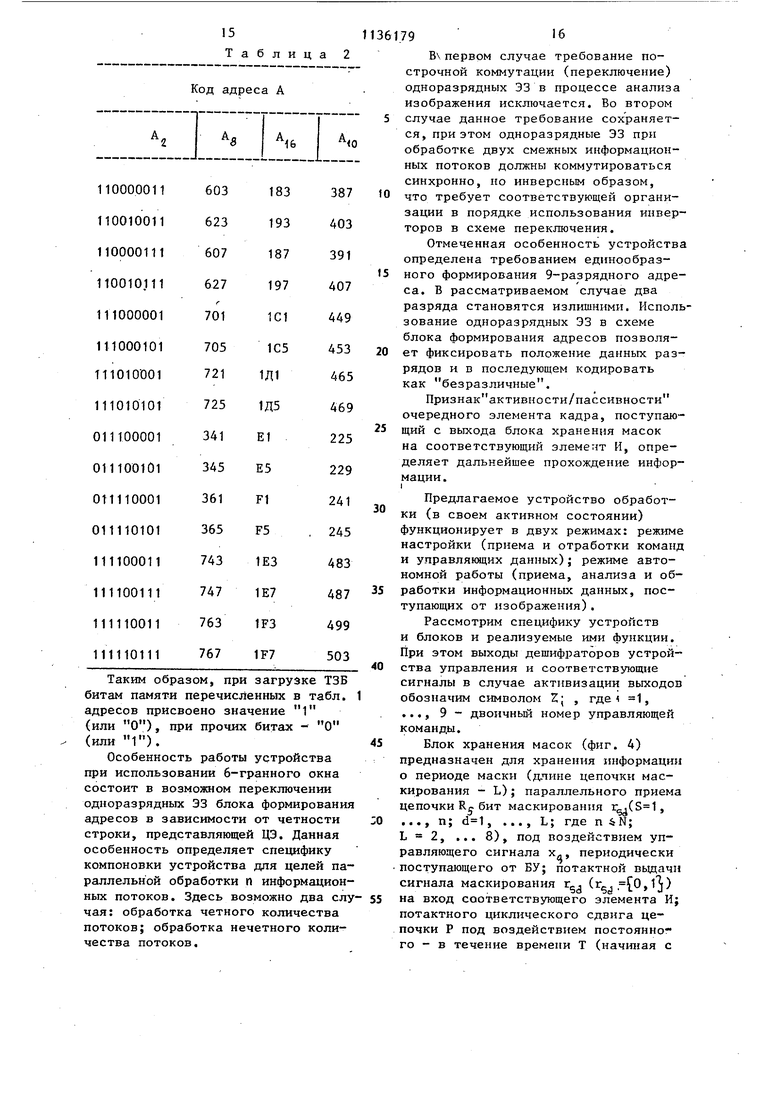

В основе работы предлагаемого устройства лежит возможность представления исходной информации (элементов изображения) битами данных и использования кода, представляющего узор изображения (ЦЭ+окрестность), в качестве кода адреса для .ТЗБ. Исходным источником информации для системы в целом может быть устройство квантования по порогу, введенное в некоторый внешний преобразователь информации, например телевизионного типа. В любом случае можно говорить о 2-градационном кад ре (или бинарной матрице) изображения размерности MN, элементы которо го помечены индексом (i, j),N; ,M. В первом случае для исследования морфологических особенностей изображения и соответствующих преоб разований можно использовать окно и 9 (фиг, 5а), либо из 5 (фиг. 56) элементов, где один элемент - ЦЭ рассматривается в качестве централь ного. Во втором случае дпя исследования морфологических особенностей изображения используется окно из 7 элементов (фиг. 5в), один из кото рых также является ЦЭ. Элементы каж го окна поименованы символами букв латинского алфавита по ходу часовой стрелки, начиная с верхнего справа (табл. 1). Выбор конфигурации окна определя ется формой кадра, связностью изображения, формами составляющих его элементов или кластеров (например, изображение ИС есть композиция прямоугольников, изображение мазка кро ви - композиция окружностей), типом преобразования или описания, а такж соотношением размеров изображения с размером окна. При кадре строго прямоугольной формы окно из 9элементов наиболее информативно, однак окно из 5 элементов также является достаточным для выявления связности изображения. Кадр строго прямоуголь ной формы можно привести к виду.

1 1 О 1

О

1 1 1

о о 1 1

0/1

о о о о

1 0/1

о п 1 0/1 0/1 допускающему использование шестигранного окна. Узор из черных и белых элe eнтoв, выделенный окном с размером 3x3 точки, взаимно однозначно представим 9-разрядным двоичным числом, где значение О или 1 Д-го разряда (, 9) определяется значением черное белое соответст зующего элемента изображения. Эталонным узором (или просто эталоном) назовем узор с заданным взаимным расположением черных и белых элементов. Таким образом, множество всех возможных эталонов включает 29, Для выполнения тех или иных преобразований изображения обращаются к эталонам определенного 1зида, составляющим множество исходного множества. Если исходному множеству эталонов сопоставить ЗУ емкостью 29 бит, а двоичное 9-разрядное число, представляющее выделенный узор, рассматривать в качестве адреса такого ЗУ, а именно табличного (ТЗБ), то заданные эталоны определяют значения соответстзующих битов памяти как равные 1, при прочих битах - О, либо наоборот. Такая пометка эталона (загрузка ТЗБ) должна выполняться на этапе настройки устройства, предотвращающем его работу Приме р. Пусть в процессе обработки изображения требуется принять решение относительно эталонов, перечисленных в табл. 1, где значение 1 отмечает черный элемент; О - белый и 0/1 - элемент изображения, состояние которого безразлично. В соответствии с этим получаем шестнадцать кодов адресов, которые перечислены в табл. 2. Таблица 1

151

Таблица 2

Таким образом, при загрузке ТЗБ битам памяти перечисленных в табл. адресов присвоено значение 1 (или О), при прочих битах - О (или 1).

Особенность работы устройства при использовании 6-гранного окна состоит в возможном переключении одноразрядных ЭЗ блока формирования адресов в зависимости от четности строки, представляющей ЦЭ. Данная особенность определяет специфику компоновки устройства для целей параллельной обработки п информационных потоков. Здесь возможно два случая: обработка четного количества потоков; обработка нечетного количества потоков.

361796

В первом случае требование построчной коммутации (переключение) одноразрядных ЭЗ в процессе анализа изображения исключается. Во втором 5 случае данное требование сохраняется, при этом одноразрядные ЭЗ при обработке двух смежных информационных потоков должны коммутироваться синхронно, но инверсным образом, что требует соответствующей организации в порядке использования инверторов в схеме переключения.

Отмеченная особенность устройства определена требованием единообразного формирования 9-разрядного адреса. В рассматриваемом случае два разряда становятся излишними. Использование одноразрядных ЭЗ в схеме блока формирования адресов позволяет фиксировать положение данных разрядов и в последующем кодировать как безразличные.

Признак активности/пассивности очередного элемента кадра, поступающий с выхода блока хранения масок на соответствующий элемент И, определяет дальнейшее прохождение информации. I

Предлагаемое устройство обработки (в своем активном состоянии) функционирует в двух режимах: режиме настройки (приема и отработки команд и управляющих данных); режиме автономной работы (приема, анализа и обработки информационных данных, поступающих от изображения).

Рассмотрим специфику устройств и блоков и реализуемые ими функции. При этом выходы дешифраторов устройства управления и соответствующие сигналы в случае активизации выходов обозначим символом Z; , где i 1, ..., 9 - двоичньй номер управляющей команды.

Блок хранения масок (фиг. А) предназначен для хранения информации о периоде маски (длине цепочки маскирования - L); параллельного приема цепочки R бит маскирования r(,

п; ,

L; где п N;

8), под воздействием упL 2,

равляющего сигнала х,, периодически поступающего от БУ; потактно вьщачи сигнала маскирования г (г, {0,1) на вход соответствующего элемента И; потактного циклического сдвига цепочки Р под воздействием постоянного - в течение времени Т (начиная с 17 четвертого обработки информационных данных и до конца отдельного прохода) управляющего сигнала х поступающего от блока управления. Сигнал маскирования г. есть призйак активности/пассивности (ij)-ro элемента кадра изображения, который поступает на вход S-ro блока хранения масок в момент времени t, где , ..., N; j 1М; (r-O; (k-1)o; номер прохода одной плоскости устройства обработки из пПЭ; t - количество тактов работы устройства.обработки, требуемых для перехода от одного этапа обработки к другому в пределах одной плоскости. Блок формирования адресов (фиг.З предназначен для: организации 9-раз рядного кода адреса либо из информа ционных данных J. 1 j+ поступаюпц х одновременно от трех смежных строк изображения (,..., п+1 либо из данных, поступающих с шины адреса; уравновешивания потоков информационных данных в случае, когда используется 6-угольная мозаика и количество ПЭ не является четным. Табличный запоминающий блок посл загрузки эталонами (размещения по заданным адресам соответствующих битовых признаков) обеспечивает счи тывание f-битового признака соответствия поступившего узора изображения эталонному ; f.f-(a,b, ... i) 0,15 ,. где , ..., n; а, b,. ,.., i - битовые признаки, составляющих поступившего узора. Элемент И обеспечивает реализаци булевой функции Ь. b(f. , ЦЭ, Г-), где , ..., п; fj - признак соответствия узора; ЦЭ: - значение цент рального элемента узора; г; - призн активности/пассивности (сигнал маскирования) соответствующего элемента кадра изображения. Блок контроля количества элементов в строках изображения (БЭС) (фиг. 6).обеспечивает реализацию функций (t) (,l|) и выдачу соответствующих управляющих воздействий в зависимости от номера .(или такта t), поступившего на процессор 79 ные элементы набора информационных данных, начиная с каждого прохода какой-либо плоскости изображения. Блок контроля количества плоскостей (БП) (фиг. 7) обеспечивает учет проходов отдельной плоскости по сигналу х.; учет числа обработанных плоскостей ; выдачу соответств5тощих управляющих воздействий. Блок буферных регистров масок (фигУ 8) обеспечивает складирование в свои i-е элементы памяти последовательности i-x цепочек маскирования (, .,., п), где отдельная цепочка принимается в параллельном коде по восьми одновременно коммутируемым линиям связи; одновреме нную выдачу (по сигналу Хл) всех цепочек маскирования на 8п линий связи; установку (по сигналу х-) исходной очередности загрузки своих элементов памяти; выдачу соответствующих управляющих воздействий. Коммутатор масок (фиг. 9) обеспечивает выдачу в параллельном коде 1-й цепочки маскирования с 1-го 8-разрядного сдвигового регистра на & одновременно коммутируемых линий связи (управление коммутацией осуществляется 8-разрядным регнет-. ром); где , ..., k; , ... 8 и счет индекса производится в циклическом коде; сохранение номера очередной, подлежащей выдаче цепочки маскирования (индекса 1); установку исходной очередности выдачи цепочек маскирования (т.е. установку ) по сигналу УО (или 2); единообразную модификацию цепочек маскирования (с поступлением сигнала Уо) посредством их циклического сдвига на определенное количество разрядов. Управление модификацией цепочек осуществляется 8-разряцным сдвиговым регистром 121. Дешифраторы выпускаются про;мьш1ленностью и в устройстве управления может быть использован один из них, удовлетворяющий поставленным условиям. В режиме настройки устройства обработки список операций рекомендуется начинать с реализации команды 1001, при которой задается исходный код масок. В качестве следующей ко-манды рекомендуется 0101,-которая обеспечивает перевод заданных эле19ментов устройства обработки в исход ное состояние. В случае работы без подполей, когда кадр изображения просматривае ся и преобразуется за один прием, местонахождение указателя длины масок (положение изолированной 1) в вспомогательном элементе памяти уст ройства хранения масок безразлично, а исходный код масок составляется только из единичных значений. При этом опускается команда 1000, где задается указание о характере модификации масок, В любом случае список операций настройки заключается командой 0100 при которой в БЭСвводится бит информации о запуске (прерьшании рабо ты) устройства обработки 1, Порядок выполнения прочих операций безразличен. Предлагаемый порядок настройки устройства обусловлен тем, что совместная работа блока буферных регис ров масок и коммутатора масок, за исключением момента обменной операции блока буферных - блока хранения масок, не зависит от работы прочих блоков и устройств. Это позволяет подготовку соответствующей информации (упорядочивание и складирование цепочек маскирования) совмещать по времени с проведением настройки устройства обработки и с реализацией операций по обработке изображени В случае работы без подполей быс родействие РНР оценивается по формуле (1). При работе с подполями 79 20 (при необходимости динамического потактного изменения масок в процессе обработки информационных данных) количество операций на цикл обработки информационных данных) количество операций на цикл обработки каждой партии из п точек (в случае базового объекта ) возрастает до четырех: засылка кода команды на логику управления; загрузка регистра маски новым значением;-засылка кода команды на логику управления; запрос данных. Таким образом, формула (1) принИ мает вид /З $0,25п9 Тогда средняя производительность РНР оценивается по формуле (полагая работу с подполями и без подполей равновероятными) и 0,625 п-. В то же время производительность предлагаемого устройства практически не меняется. Отсюда при- f и при одном количестве одновременно обрабатываемых точек изображения (п) приходим к соотношению У/ 1.6, что позволяет утверждать, что эффективность предложенного устройства не менее, чем в полтора раза выше эффективности РНР,

3

ад

J7

-в

37

J

7

J7

©J7

5

35

5

ад

ад

ц Ц.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Duff МЛ.В, Watson D.H | |||

| The cellular logic array image processor The Computer | |||

| I, 1977, v | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Способ получения смеси хлоргидратов опийных алкалоидов (пантопона) из опийных вытяжек с любым содержанием морфия | 1921 |

|

SU68A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| llerron J.Hj Farley J, Preston K, SeLlner H, A general - purpose highspeid logical transform image .Processor, - IEEE Transaction on Computers, 1982, V | |||

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Способ десульфитации фруктовых и ягодных соков, напитков и т.п. продуктов | 1921 |

|

SU795A1 |

Авторы

Даты

1985-01-23—Публикация

1983-08-04—Подача