Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля цифровых блоков.

Целью изобретения является повышение надежности и достоверности контроля за очет обеспечения режима самоконтроля .

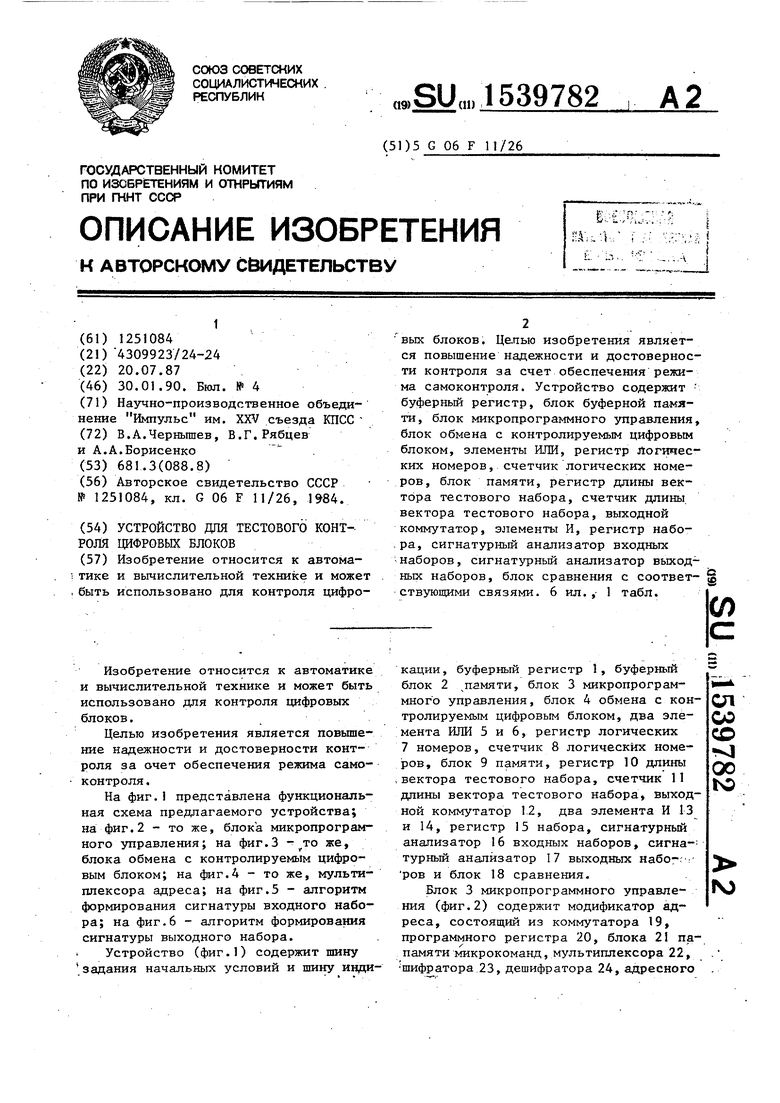

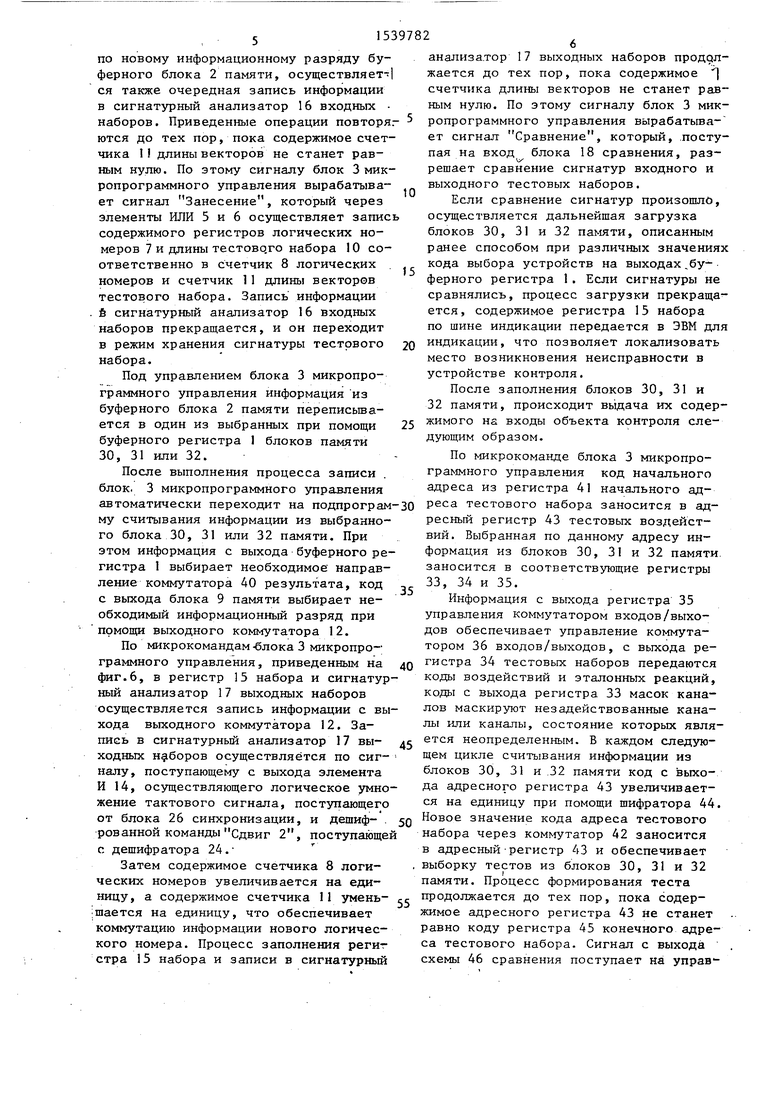

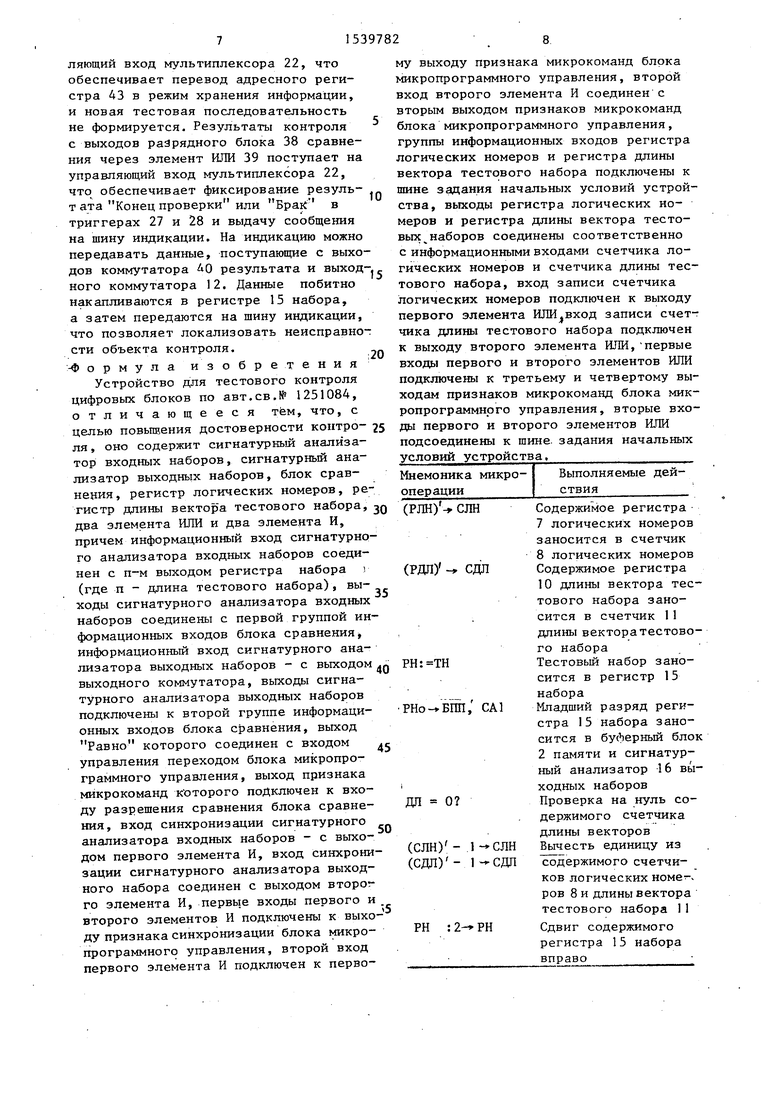

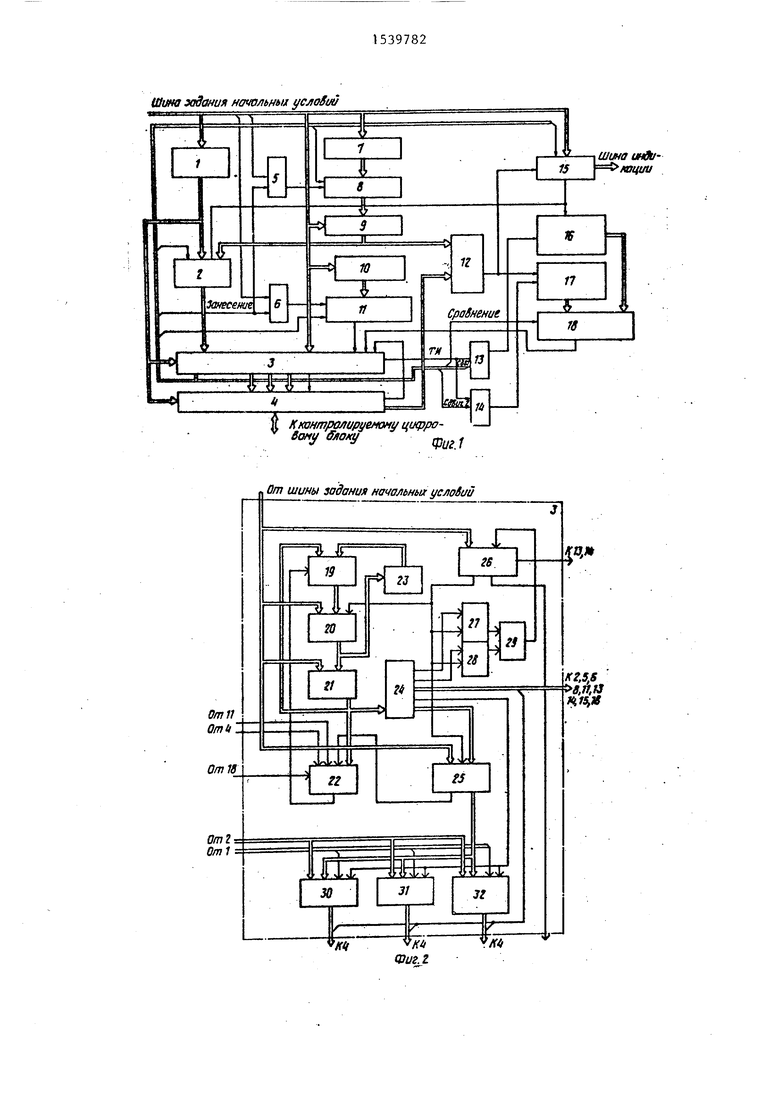

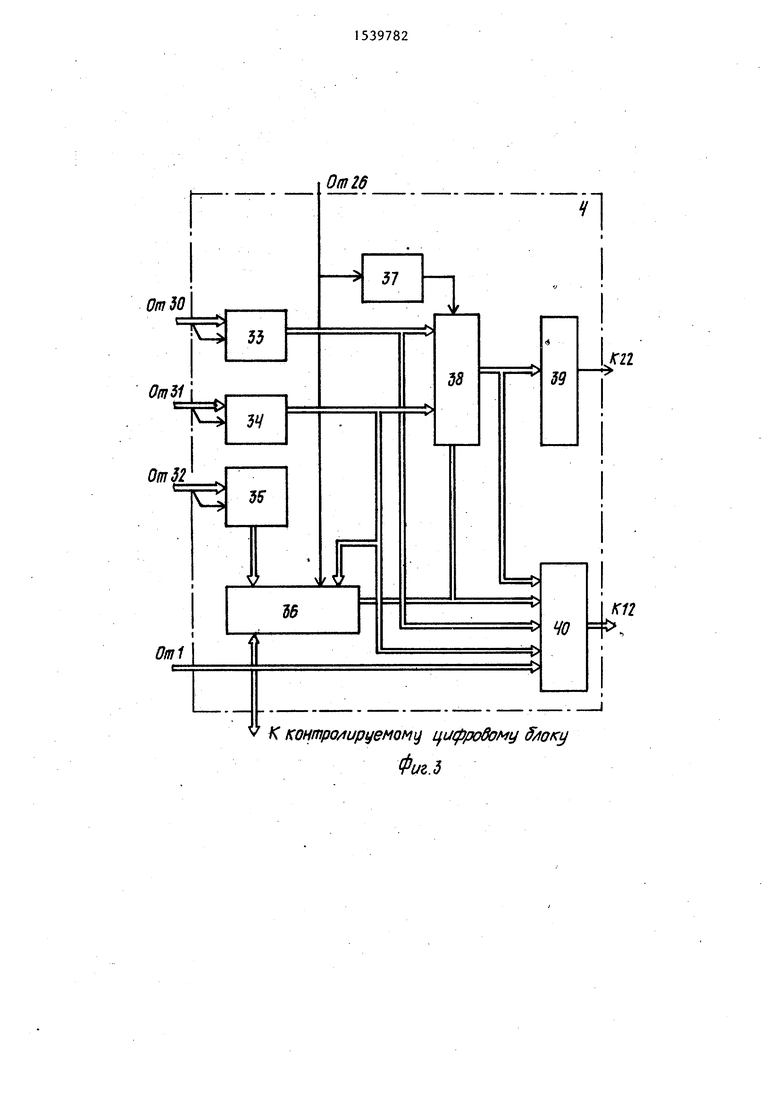

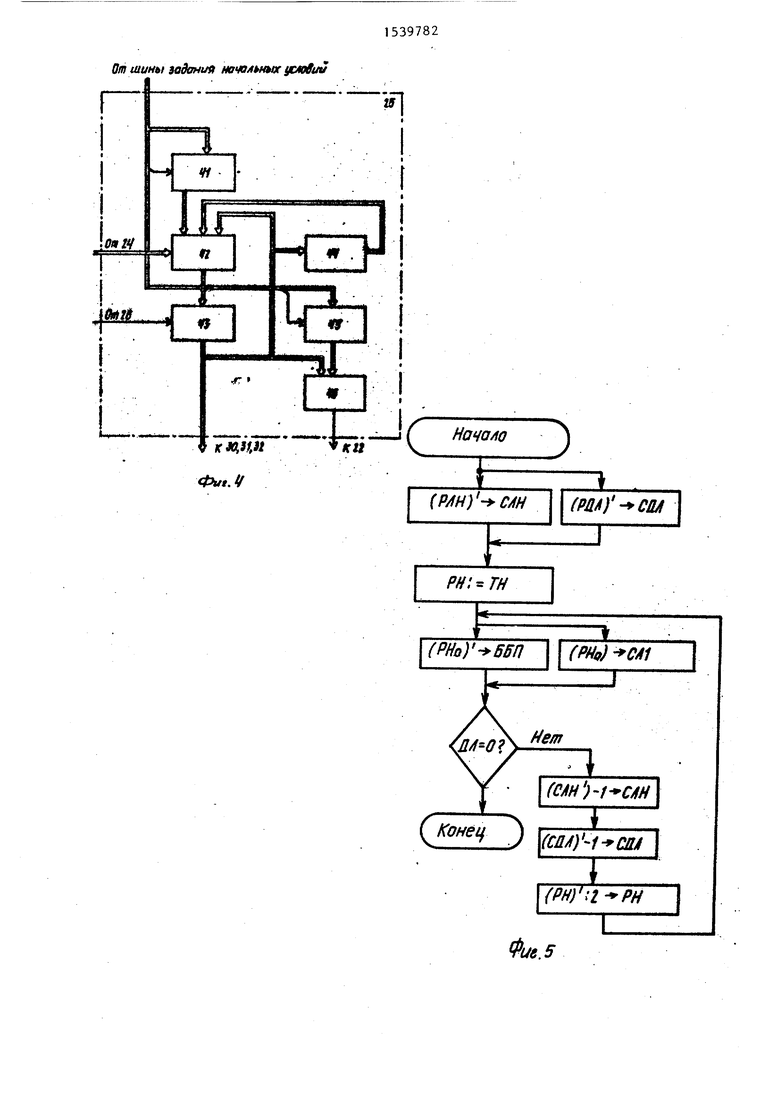

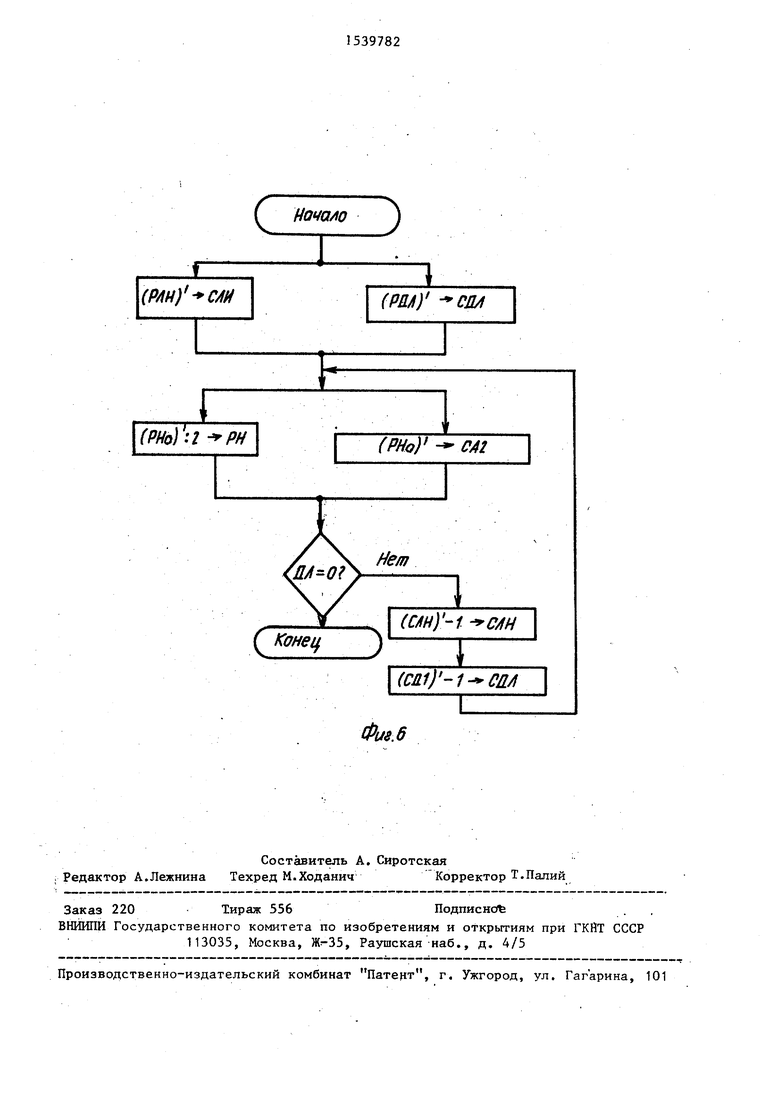

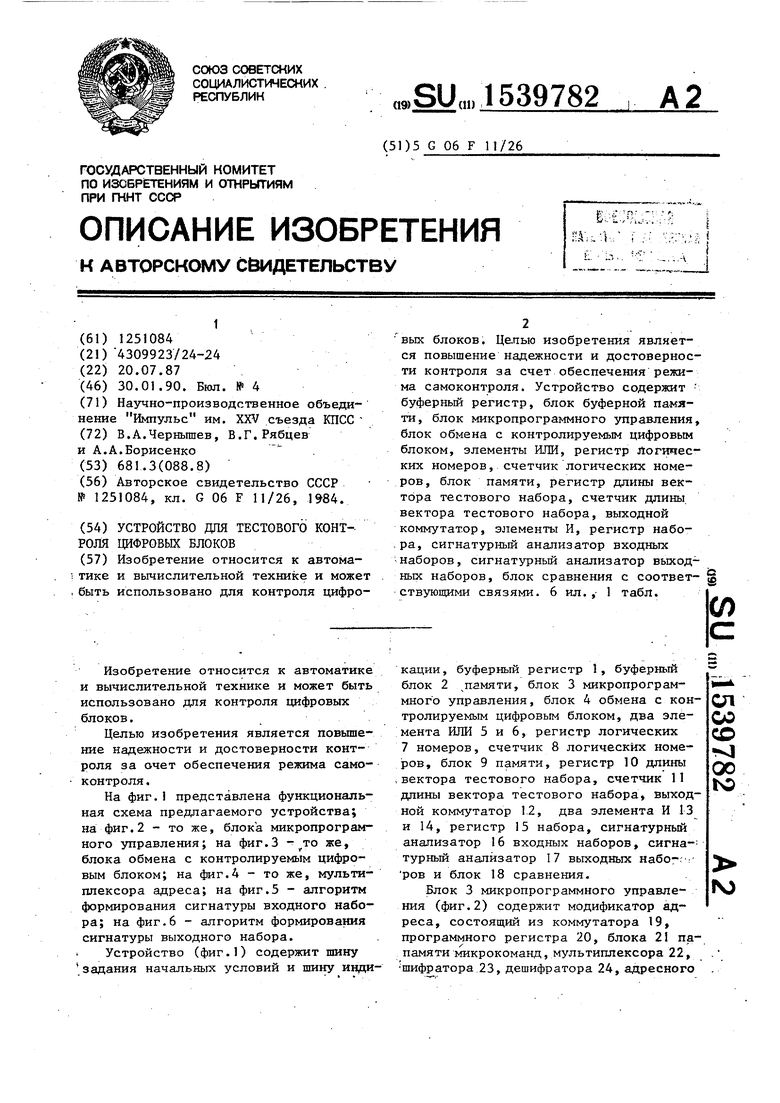

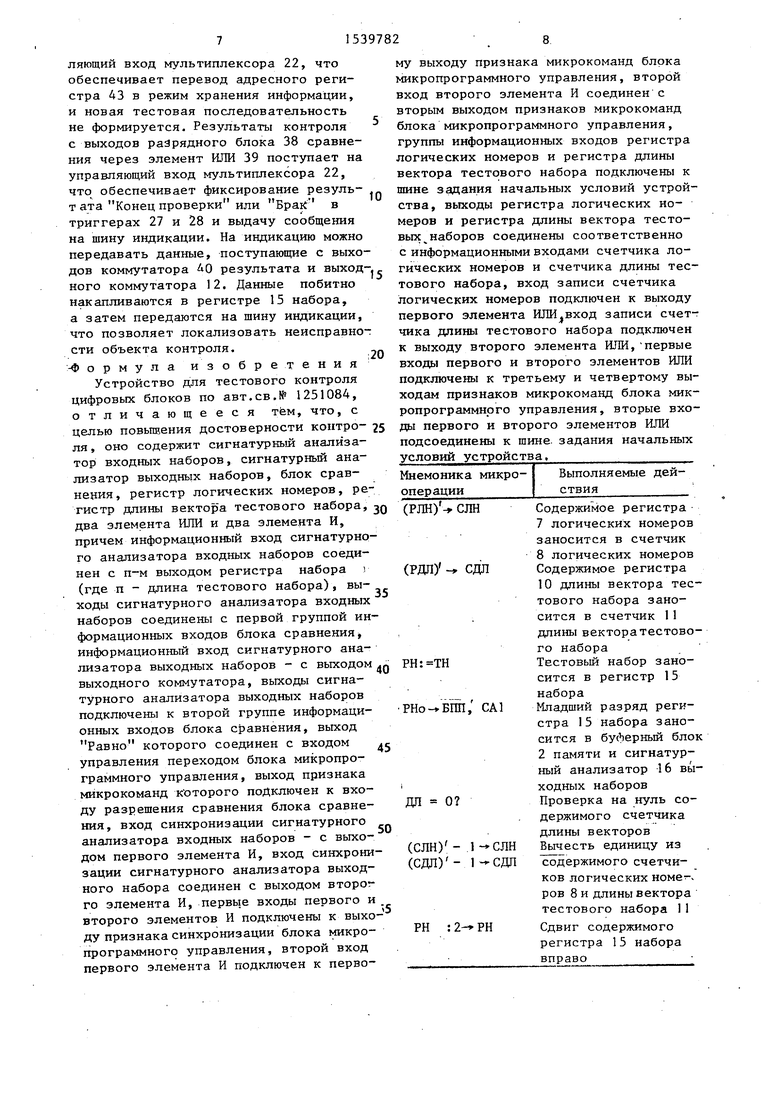

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - то же, блока микропрограм- ного управления; на фиг.З же, блока обмена с контролируемым цифровым блоком; на фиг.4 - то же, мультиплексора адреса; на фиг.5 - алгоритм формирования сигнатуры входного набора; на фиг.6 - алгоритм формирования сигнатуры выходного набора.

Устройство (фиг.1) содержит шину задания начальных условий и шину индикации, буферный регистр 1, буферный блок 2 чпамяти, блок 3 микропрограммного управления, блок 4 обмена с контролируемым цифровым блоком, два элемента ИЛИ 5 и 6, регистр логических 7 номеров, счетчик 8 логических номеров, блок 9 памяти, регистр 10 длины ,вектора тестового набора, счетчик 11 длины вектора тестового набора, выходной коммутатор 12, два элемента И 13 и 14, регистр 15 набора, сигнатурный анализатор 16 входных наборов, сигнатурный анализатор I7 выходных набо- ров и блок 18 сравнения.

Блок 3 микропрограммного управления (фиг.2) содержит модификатор адреса, состоящий из коммутатора 19, программного регистра 20, блока 21 па- памяти микрокоманд, мультиплексора 22, Шифратора 23, дешифратора 24, адресного

сл

со со 1

00 ГС

к

мультиплексора 25, блока 26 синхронизации, триггеров 27 и 28 и элемента ИЛИ 29, а также блок памяти, образованный блоком 30 памяти масок каналов, бло- ком 31 памяти тестовых наборов и блоками 32 памяти кодов управления коммутаторами входов/выходов.

Блок 4 обмена с контролируемым цифровым блоком (фиг.З) содержит узел памяти, образованный регистром/33 масок каналов, регистром 34 тестовых наборов и регистром 35 кодов управления коммутатором входов/выходов, коммутатор 36 входов/выходов, элемент 37 задержки, разрядный блок 38 сравнения , элемент ИЛИ 39 и коммутатор 40 результата.

Мультиплексор 25 адреса( фиг.4) содержит регистр 41 адреса тестового набора, коммутатор 42, адресный регистр 43, шифратор 44, регистр 45 конечного адреса тестового набора и схему 46 сравнения.

Микрооперации, выполняемые по ал«- горитмам (фиг.5 и 6), приведены в таблице .

Устройство работает следующим об- разом.

Цифровой контролируемый блок под- ключается к входам/выходам коммутатора входов/выходов блока обмена с контролируемым цифровым блоком (объект контроля, цепи питания и общего сброс не показаны).

В тесте содержится таблица соответствия логических номеров контролируемого цифрового блока его физическим контактам выходных разъемов, В блок 9 памяти с шины задания начальных условий записываются физические номера контактов контролируемого цифрового блока, соответствующие логическим номерам. Запись информации в блок 9 памяти осуществляется следующим обра- зом. Код логического номера контакта цифрового контролируемого блока .по входной шине св-язи с ЭВМ заносится в регистр 7 логических номеров, а затем в счетчик 8 логических номеров, при этом управление занесением осуществля ется элементом ИЛИ 5. По заднему адресу в блок 9 памяти с входной шины связи с ЭВМ заносится код физического адреса контакта контролируемого блока. С шины задания начальных условий в блок 3 микропрограммного управления заносятся микропрограммы работы. Адрес микрокоманд заносится в програм

Q

,-

0

0

мный регистр 20, коды микрокоманд - в блок 21 памяти микрокоманд, начальный адрес теста - в регистр 41 адреса тестового набора, конечный адрес - в регистр 45 конечного адреса тестового набора, а коды частоты функционального контроля и временного положения строба контроля, обеспечивающего прием информации с контролируемого цифрового блока - в блок 26 синхронизации.

В тестовом наборе, необходимом для каждого такта контроля, содержатся входные воздействия и эталонные реакции, коды маскирования каналов цифрового блока и коды управления коммутатором входов/выходов. Вначале тестовый набор заносится в буферный блок 2 памяти следующим образом. В счетчик 8 логических номеров через ре-, гистр 7 логических номеров под управлением сигнала с выхода элемента ИЛИ 5 заносится начальный логический номер- контакта цифрового контролируемого блока. В счетчик 11 через регистр 10 под управлением сигнала с выхода элемента ИЛИ 6 заносится код длины группы шин, которым соответствует данная тестовая последовательность. Тестовый набор заносится в регистр 15 набора. Код информации блока 9 памяти выбирает информационный разряд буферного блока 2 памяти, в который записывается код информации старшего разряда регистра 15 набора, этот же код записывается в сигнатурный анализатор 16 входных наборов. Запись осуществляется по микрокомандам, формируемым дешифратором 24. Алгоритм побитной распаковки регистра 15 набора и формирования сигнатуры входного набора приведен на фиг.5.Запись в сигнатурный анализатор входных наборов 16 осуществляется сигналом, поступающим с выхода элемента И 13, который осуществляет логическое умножение тактового импульса, поступающего с блока 26 синхронизации, и дешифрированной микрокоманды Сдвиг 1, поступающей с дешифратора 24. Г

По микрокоманде блока модификации адреса увеличивается на единицу значение счетчика 8 логических номеров и уменьшается на единицу состояние счетчика 11 длины векторов тестового набора, а также осуществляется сдвиг влево содержимого регистра 15 набора. Процесс записи информации выполняется

по новому информационному разряду буферного блока 2 памяти, осуществляет ся также очередная запись информации в сигнатурный анализатор 16 входных наборов. Приведенные операции повторя.- ются до тех пор, пока содержимое счетчика 1 длины векторов не станет равным нулю. По этому сигналу блок 3 микропрограммного управления вырабатывает сигнал Занесение, который через элементы ИЛИ 5 и 6 осуществляет запись содержимого регистров логических номеров 7 и длины тестово.го набора 10 соответственно в счетчик 8 логических номеров и счетчик 11 длины векторов тестового набора. Запись информации в сигнатурный анализатор 16 входных наборов прекращается, и он переходит в режим хранения сигнатуры тестового набора.

Под управлением блока 3 микропрограммного управления информация из буферного блока 2 памяти переписывается в один из выбранных при помощи буферного регистра 1 блоков памяти 30, 31 или 32.

После выполнения процесса записи блок. 3 микропрограммного управления

o

5

0

5

анализатор 17 выходных наборов продолжается до тех пор, пока содержимое счетчика длины векторов не станет равным нулю. По этому сигналу блок 3 микропрограммного управления вырабатывает сигнал Сравнение, который, поступая на вход блока 18 сравнения, разрешает сравнение сигнатур входного и выходного тестовых наборов.

Если сравнение сигнатур произошло, осуществляется дальнейшая загрузка блоков 30, 31 и 32 памяти, описанным ранее способом при различных значениях кода выбора устройств на выходах,буферного регистра 1. Если сигнатуры не сравнялись, процесс загрузки прекращается, содержимое регистра 15 набора по шине индикации передается в ЭВМ для индикации, что позволяет локализовать место возникновения неисправности в устройстве контроля.

После заполнения блоков 30, 31 и 32 памяти, происходит выдача их содержимого на входы объекта контроля следующим образом.

По микрокоманде блока 3 микропрограммного управления код начального адреса из регистра 41 начального ад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1430957A2 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1545222A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля и диагностики цифровых узлов | 1987 |

|

SU1587513A1 |

| Микропрограммное устройство управления с самоконтролем | 1987 |

|

SU1427367A1 |

Изобретение относится к автоматике и вычислительной технике, может быть использовано для контроля цифровых блоков. Целью изобретения является повышение надежности и достоверности контроля за счет обеспечения режима самоконтроля. Устройство содержит буферный регистр, блок буферной памяти, блок микропрограммного управления, блок обмена с контролируемым цифровым блоком, элементы ИЛИ, регистр логических номеров, счетчик логических номеров, блок памяти, регистр длины вектора тестового набора, счетчик длины вектора тестового набора, выходной коммутатор, элементы И, регистр набора, сигнатурный анализатор входных наборов, сигнатурный анализатор выходных наборов, блок сравнения с соответствующими связями. 6 ил., 1 табл.

автоматически переходит на подпрограм-30 Рес тестового набора заносится в ад

му считывания информации из выбранного блока 30, 31 или 32 памяти. При этом информация с выхода буферного регистра 1 выбирает необходимое направление коммутатора ДО результата, код с выхода блока 9 памяти выбирает необходимый информационный разряд при помощи выходного коммутатора 12.

По микрокомандам-блока 3 микропрограммного управления, приведенным на фиг.6, в регистр 15 набора и сигнатурный анализатор 17 выходных наборов осуществляется запись информации с выхода выходного коммутатора 12. Запись в сигнатурный анализатор 17 вы- ходных наборов осуществляется по сигналу, поступающему с выхода элемента И 14, осуществляющего логическое умножение тактового сигнала, поступающего от блока 26 синхронизации, и дешиф- рованной команды Сдвиг 2, поступающей с дешифратора 24.

Затем содержимое счетчика 8 логических номеров увеличивается на единицу, а содержимое счетчика 11 уменьшается на единицу, что обеспечивает коммутацию информации нового логического номера. Процесс заполнения регистра 15 набора и записи в сигнатурный

5

0

5 0

5

ресный регистр 43 тестовых воздействий. Выбранная по данному адресу информация из блоков 30, 31 и 32 памяти заносится в соответствующие регистры 33, 34 и 35.

Информация с выхода регистра 35 управления коммутатором входов/выходов обеспечивает управление коммутатором 36 входов/выходов, с выхода регистра 34 тестовых наборов передаются коды воздействий и эталонных реакций, коды с выхода регистра 33 масок каналов маскируют незадействованные каналы или каналы, состояние которых является неопределенным. В каждом следующем цикле считывания информации из блоков 30, 31 и 32 памяти код с выхода адресного регистра 43 увеличивается на единицу при помощи шифратора 44. Новое значение кода адреса тестового набора через коммутатор 42 заносится в адресный регистр 43 и обеспечивает выборку тестов из блоков 30, 31 и 32 памяти. Процесс формирования теста продолжается до тех пор, пока содержимое адресного регистра 43 не станет равно коду регистра 45 конечного адреса тестового набора. Сигнал с выхода схемы 46 сравнения поступает на управ

ляющий вход мультиплексора 22, что обеспечивает перевод адресного регистра 43 в режим хранения информации, и новая тестовая последовательность не формируется. Результаты контроля с выходов разрядного блока 38 сравнения через элемент ИЛИ 39 поступает на управляющий вход мультиплексора 22, что обеспечивает фиксирование резуль- т ата Конец проверки или Bpatf 1 в триггерах 27 и 28 и выдачу сообщения на шину индикации. На индикацию можно передавать данные, поступающие с выходов коммутатора АО результата и выходного коммутатора 12. Данные побитно накапливаются в регистре 15 набора, а затем передаются на шину индикации, что позволяет локализовать неисправности объекта контроля. -Формула изобретения Устройство для тестового контроля цифровых блоков по авт.св.№ 1251084, отличающееся тем, что, с целью повышения достоверности контро- ля, оно содержит сигнатурный анализатор входных наборов, сигнатурный анализатор выходных наборов, блок сравнения, регистр логических номеров, регистр длины вектора тестового набора, два элемента ИЛИ и два элемента И, причем информационный вход сигнатурного анализатора входных наборов соединен с п-м выходом регистра набора i (где п - длина тестового набора), вы- ходы сигнатурного анализатора входных наборов соединены с первой группой информационных входов блока сравнения, информационный вход сигнатурного анализатора выходных наборов - с выходом выходного коммутатора, выходы сигнатурного анализатора выходных наборов подключены к второй группе информационных входов блока сравнения, выход Равно которого соединен с входом управления переходом блока микропрограммного управления, выход признака микрокоманд которого подключен к входу разрешения сравнения блока сравнения, вход синхронизации сигнатурного анализатора входных наборов - с выходом первого элемента И, вход синхронизации сигнатурного анализатора выходного набора соединен с выходом второе- го элемента И, первые входы первого и второго элементов И подключены к выходу признака синхронизации блока микропрограммного управления, второй вход первого элемента И подключен к перво

му выходу признака микрокоманд блока микропрограммного управления, второй вход второго элемента И соединен с вторым выходом признаков микрокоманд блока микропрограммного управления, группы информационных входов регистра логических номеров и регистра длины вектора тестового набора подключены к шине задания начальных условий устройства, выходы регистра логических номеров и регистра длины вектора тесто- вых наборов соединены соответственно с информационными входами счетчика логических номеров и счетчика длины тестового набора, вход записи счетчика логических номеров подключен к выходу первого элемента записи счетт чика длины тестового набора подключен к выходу второго элемента ИЛИ, первые входы первого и второго элементов ИЛИ подключены к третьему и четвертому выходам признаков микрокоманд блока микропрограммного управления, вторые входы первого и второго элементов ИЛИ подсоединены к шине, задания начальных условий устройства.

микро

Выполняемые действия

Н

- СЛН

СДЛ

БПП, СА1

О

- 1 -СЛН - 1-СДП

: 2- РН

Содержимое регистра

7логических номеров заносится в счетчик

8логических номеров Содержимое регистра 10 длины вектора тестового набора заносится в счетчик 11 длины вектора тестового набора

ТЕСТОВЫЙ набор заносится в регистр 15 набора

Младший разряд регистра 15 набора заносится в буферный блок 2 памяти и сигнатурный анализатор 16 выходных наборов Проверка на нуль содержимого счетчика длины векторов Вычесть единицу из содержимого счетчиков логических номе-, ров 8 и длины вектора тестового набора 11 Сдвиг содержимого регистра 15 набора вправо

Шина задания начальных условий

Н К контролируемому цифровому Окнуфигг

От 11 ОтЬ

Шина ин8и15

/v.v

в,п,а

ЦГ5

v к контролируемому цифровому &/юку

Фж.З

ппдоаК влнарое ннпт шд

Z8Ј6C5l

С

Начало

(РМ) + СМ

I

I

(Ptto): 2 РН

(РНоГ - Ml

Конец J

)

1

(Рилу

(СЛН)Ч -+C/IH

(Сй1) -1 + С1М

Фиг.б

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-07-20—Подача