4iib СО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Устройство для контроля полупроводниковой памяти | 1985 |

|

SU1319079A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1314344A1 |

Изобретение относится к области автоматики и цифровой вычислительной техники, может быть использовано в управляющих комплексах и вычислительных центрах с разнородной цифровой техникой и является усовершенствованием изобретения по а.с. № 1251084. Целью изобретения является расширение функциональных возможностей контроля блоков различного функционального назначения. Поставленная цель достигается тем, что в устройство дополнительно введен блок реконфигурации памяти. Введение в устройство блока реконфигурации памяти дает возможность производить перестройку памяти каналов в зависимости от степени сложности цифровых контроли-. руемых блоков, что позволяет рационально использовать оборудование, повысить его производительность. Так, при тестовом контроле цифровых блоков средней и малой степени сложности перестройка памяти каналов позволяет увеличить емкость памяти для тестовых наборов в 2-3 раза, это дает возможность снизить количество перегрузок канальной памяти от ЭВМ, в процессе которых в основном и теряется производительность устройства. Кроме того, перестройка памяти позволяет увеличить скорость контроля также в 2-3 раза. 5 ил. (Л с

СП

s|

1Ч

Изобретение относится к автоматике и вычислительной технике и может быть использовано дЛя контроля цифровых блоков.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности контроля блоков различного функционального назначения.

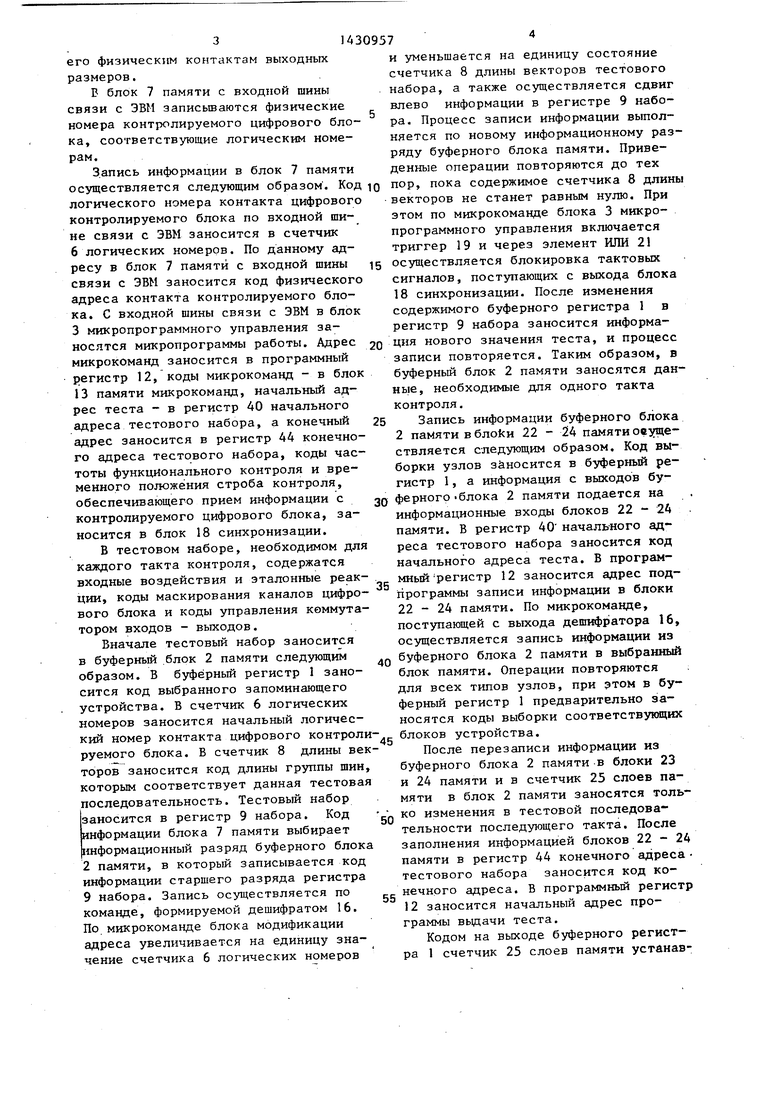

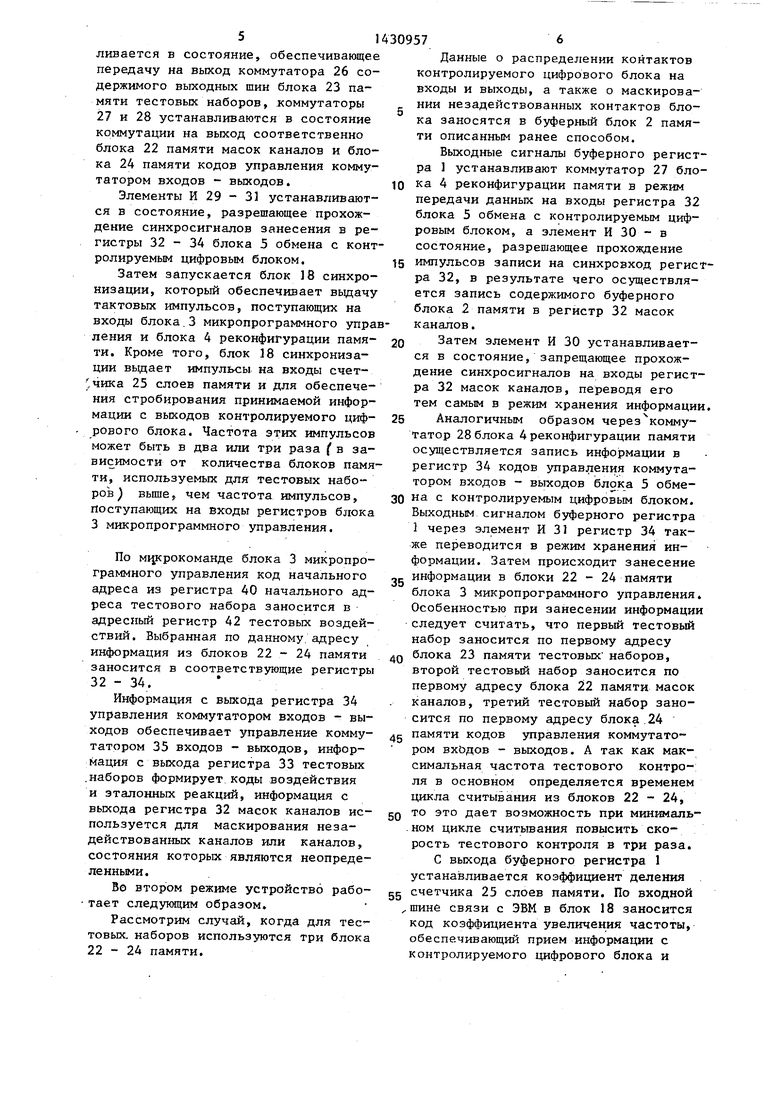

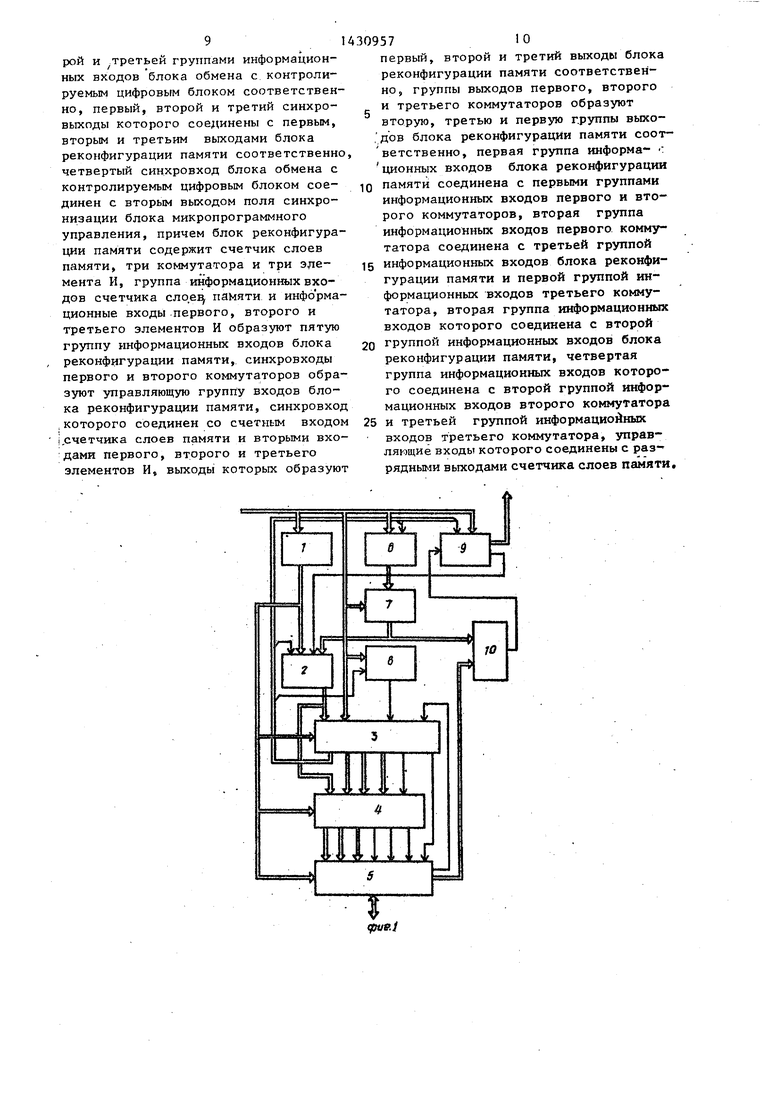

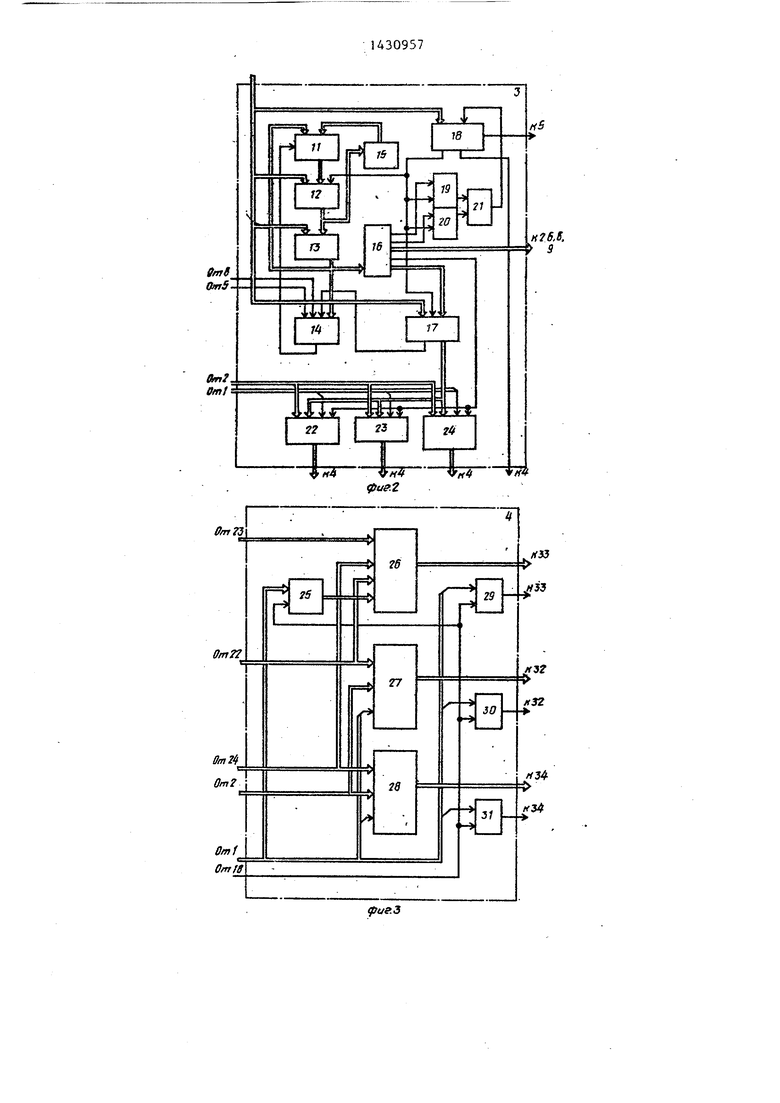

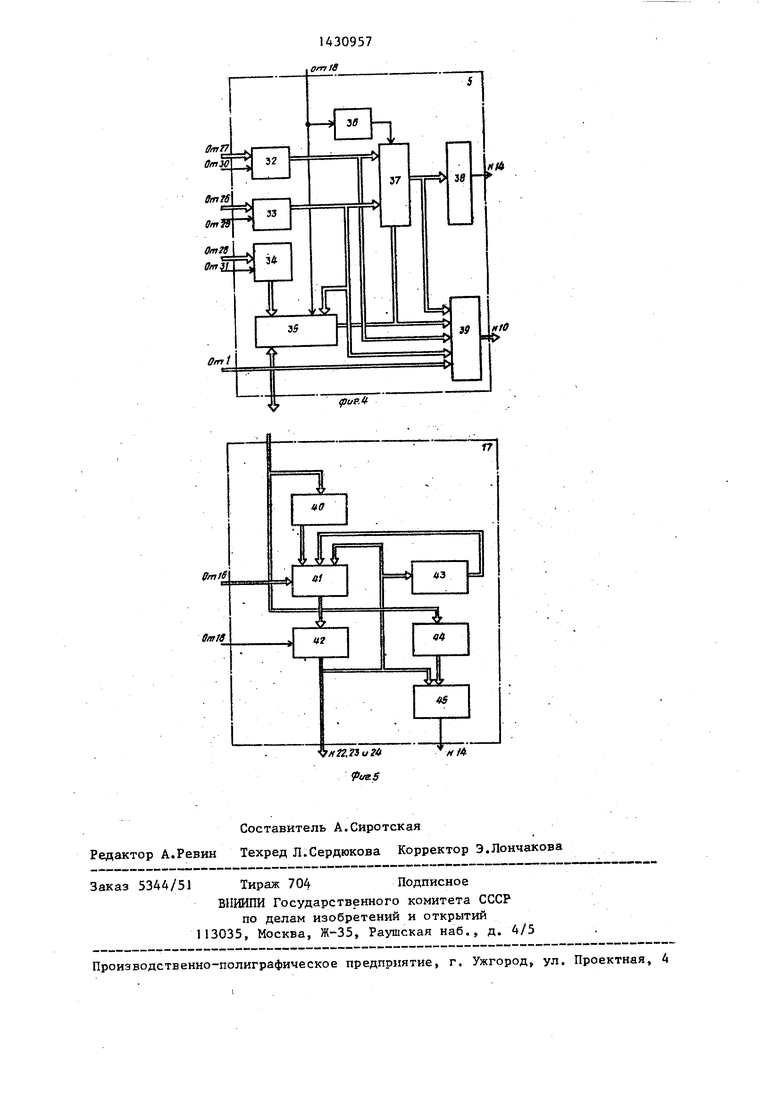

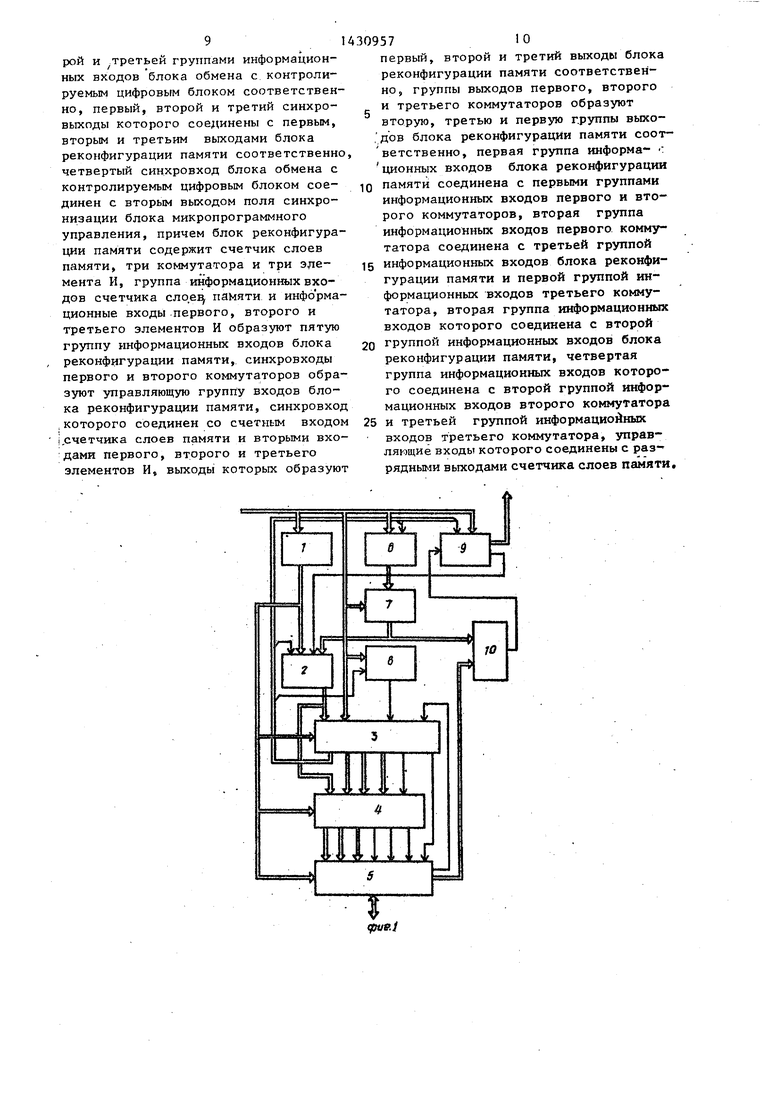

На фиг. изображена функциональная блок-схема предлагаемого устройства; на фиг.2 - блок микропрограммного управления; на фиг.З - блок реконфигурации памяти; на фиг.4 - блок обмена с контролируемым цифро- BbiM блоко1и на фиг.З - мультиплексор адреса.

Устройство содержит входную и выходную шины связи с ЭВМ, буферный регистр J, буферный блок 2 памяти, блок 3 микропрограммного управления, блок 4 реконфигурации памяти, блок 5 обмена с контролируемым цифровым блоком, счетчик 6 логических номеров, блок 7 памяти, счетчик 8 длины векторов, регистр 9 набора и выходной коммутатор 10.

Блок 3 микропрограммного управления содержит модификатор адреса, состоящий из коммутатора 11, программного регистра 12, блока 13 памяти микр команд, мультиплексора 14, шифратора 15, дешифратора 16, адресного-мультиплексора 17, ,блока 18 синхронизации, триггеров 19 и20 и элемента ИЛИ 21. Кроме того, блок 3 содержит блок памяти, образованный блоком 22 памят масок каналов, блоком 23 памяти тестовых наборов и блоком 24 памяти кодов управления коммутатором входов - выходов.

Блок 4 реконфигурации памяти соде жит счетчик 25 слоев памяти, коммутаторы 26 - 28 и элементы И 29-31.

Блок 5 обмена с контролируемым цифровым блоком содержит узел памяти образованный регистром 32 масок каналов, регистром 33.тестовых наборов и регистром 34 кодов управления коммутатором входов - выходов. Кроме то го, блок 5 содержит коммутатор 35 входов - выходов, элемент 36 задержки, разрядный блок 37 сравнения, элемент ИЛИ 38 и коммутатор 39 результата. .

Мультиплексор адреса содержит.регистр 40 адреса тестового набора, коммутатор 41, адресный регистр 42, шифратор 43, регистр 44 конечного

0

5

0

5

0

5

0

5

адреса тестового набора и схему 45 сравнения.

Матричная организация канальных ОЗУ, используемая в устройстве, ориентирована на тестовый контроль цифровых блоков большой сложности (т.е. блоков, имеющих шинную организацию структуры, содержащих микропроцессоры, БИС ОЗУ и т.п.).

Контроль таких блоков, в частности, предполагает смену направления обмена данными между устройством контроля -и контролируемого блока, а такде маскирование результата контроля по любому числу контактов в каждом такте контроля.

Однако, в настоящее время удельный вес цифровых блоков большой слож- нос.ти в общей номенклатуре изделий составляет 15-20%,

В остальных случаях цифровые блоки являются блоками средней и малой степени сложности. При их необходимость в блоках памяти кодов управления коммутатором входов - выходов и памяти масок каналов отпадает.

Поэтому в устройстве предлагают- ся средства для перекрнфигурации бло- ка памяти в зависимости от степени : сложности контролируемых цифровых блоков.

в случае контроля цифровых блоков средней и малой степени сложности блока памяти кодов управления коммутатором входов - выходов и памяти масок каналов используются в качестве дополнительной памяти тестовых наборов, а распределение контактов блока на входы и выходы, а также маскирование незадействованных контактов осуществляется соответствзпощими регистрами.

Устройство работает в двух режимах: в режиме тестового контроля цифровых блоков большой сложности и в режиме тестового контроля цифровых блоков средней и малой степени сложности.

В первом режиме устройство работает следующим образом. Цифровой контролируемый блок подключается к входам - выходам коммутатора входов - выходов блока обмена с контролируемым цифровым блоком (объект контроля не показан). В тесте содержится таблица соответстния логических коме- .Р.9..контролируемого цифрового блока

31 30957

его физическим контг ктам выходныхи уменьшается на единицу состояние

размеров..счетчика 8 длины векторов тестового

В блок 7 памяти с входной шинынабора, а также осуществляется сдвиг связи с ЭВМ записьшаготся физическиевлево информации в регистре 9 набо- номера контролируемого цифрового бло-ра. Процесс записи информации выпол- ка, соответствующие логическим номе-няется по новому информационному раз- рам,ряду буферного блока памяти. ПривеЗ.апись информации в блок 7 памятиденные операции повторяются до тех осуществляется следующим образом . Код IQпор, пока содержимое счетчика 8 длины логического номера контакта цифровоговекторов не станет равным нулю. При контролируемого блока по входной ши-этом по микрокоманде блока 3 микроне связи с ЭВМ заносится в счетчикпрограммного управления включается 6 логических номеров. По данному ад-триггер 19 и через элемент ИЛИ 21 ресу в блок 7 памяти с входной шины 15осуществляется блокировка тактовых связи с ЭВМ заносится код физическогосигналов, поступающих с выхода блока адреса контакта контролируемого бло-18 синхронизации. После изменения ка, С входной шины связи с ЭВМ в блоксодержимого буферного регистра 1 в 3 микропрограммного управления за-регистр 9 набора заносится информа- носятся микропрограммы работы. Адрес 20Ч нового значения теста, и процесс микрокоманд заносится в программныйзаписи повторяется. Таким образом, в регистр 12, коды микрокоманд - в блокбуферный блок 2 памяти заносятся дан- 13 памяти микрокоманд, начальный ад-ные, необходимые для одного такта рее теста - в регистр 40 начальногоконтроля.

адреса тестового набора, а конечный 25 Запись информации буферного блока адрес заносится в регистр 44 конечно-2 памяти в блokи 22 - 24 памяти овуще- го адреса тестового набора, коды час-ствляется следующим образом. Код вы- тоты функционального контроля и вре-борки узлов з&носится в буферный ременного положения строба контроля,гистр 1, а информация с выходов бу- обеспечивающего прием информации с Qферного-блока 2 памяти подается на контролируемого цифрового блока, за-информационные входы блоков 22 - 24 носится в блок 18 синхронизации.памяти. В регистр 40 начального адВ тестовом наборе, необходимом дляреса тестового набора заносится код

каждого такта контроля, содержатсяначального адреса теста. В програмвходные воздействия и эталонные реак-мный регистр 12 заносится адрес подции, коды маскирования каналов цифро- программы записи информации в блоки

вого блока и коды управления кеммута-22 - 24 памяти. По микрокоманде,

тором входов - выходов.поступающей с выхода дешифратора 16,

Вначале тестовый набор заноситсяосуществляется запись информации из в буферный .блок 2 памяти следующим буферного блока 2 памяти в выбранный образом. В буферный регистр 1 зано-блок памяти. Операции повторяются ; сится код выбранного запоминающегодля всех типов узлов, при этом в бу- устройства. В счетчик 6 логическихферный регистр 1 предварительно за- номеров заносится начальный логичес-носятся коды выборки соответствующих кий номер контакта цифрового контроли-блоков устройства, руемого блока. В счетчик 8 длины век- После перезаписи информации из торов заносится код длины группы шин,буферного блока 2 памяти в блоки 23 которым соответствует данная тестоваяи 24 памяти и в счетчик 25 слоев па- последовательность. Тестовый набормяти в блок 2 памяти заносятся толь- заиосится в регистр 9 набора. Код ко изменения в тестовой последова- информации блока 7 памяти выбираеттельности последующего такта. После информационный разряд буферного блоказаполнения информацией блоков 22 - 24 2 памяти, в который записывается кодпамяти в регистр 44 конечного адреса информации старшего разряда регистратестового набора заносится код ко- 9 набора. Запись осуществляется понечнрго адреса. В программный регистр команде, формируемой дешифратом 16.12 заносится начальный адрес про- По микрокоманде блока модификацииграммы выдачи теста. адреса увеличивается на единицу зна- Кодом на выходе буферного регист- чение счетчика 6 логических номеровра 1 счетчик 25 слоев памяти устанав10

15

51430957

ливается в состояние, обеспечивающее передачу на выход коммутатора 26 содержимого выходных шин блока 23 памяти тестовых наборов, коммутаторы 27 и 28 устанавливаются в состояние коммутации на выход соответственно блока 22 памяти масок каналов и блока 24 памяти кодов управления коммутатором входов - выходов.

Элементы И 29 - 31 устанавливаются в состояние, разрешающее прохождение синхросигналов занесения в регистры 32 - 34 блока 5 обмена с контролируемым цифровым блоком.

Затем запускается блок 18 синхронизации, который обеспечивает выдачу тактовых импульсов, поступающих на входы блока.3 микропрограммного управения и блока 4 реконфигурации памя- 20 ти. Кроме того, блок 18 синхронизации выдает импульсы на входы счет- чика 25 слоев памяти и для обеспечения стробирования принимаемой информации с выходов контролируемого цифрового блока. Частота этих импульсов может быть в два или три раза f в зависимости от количества блоков памяти, используемых для тестовых наборов ) выше, чем частота импульсов, поступающих на входы регистров блока 3 микропрограммного управления.

25

ко вх ни ка ти

ра ка пе бл ро со им ра ет бл ка

ся де ра те

та ос ре то 30 на Вы 1 же фо ин бл Ос сл на бл вт пе ка си па си ля ци то но

По макрокоманде блока 3 микропрограммного управления код начального адреса из регистра 40 начального адреса тестового набора заносится в адресный регистр 42 тестовьпс воздействий. Выбранная по данному/адресу информация из блоков 22 - 24 памяти заносится в соответствующие регистры 32-34.

Информация с выхода регистра 34 управления коммутатором входов - выходов обеспечивает управление коммутатором 35 входов - выходов, информация с выхода регистра 33 тестовых .наборов формирует коды воздействия и эталонных реакций, информация с выхода регистра 32 масок каналов используется для маскирования незадействованных каналов или каналов, состояния которых являются неопределенными.

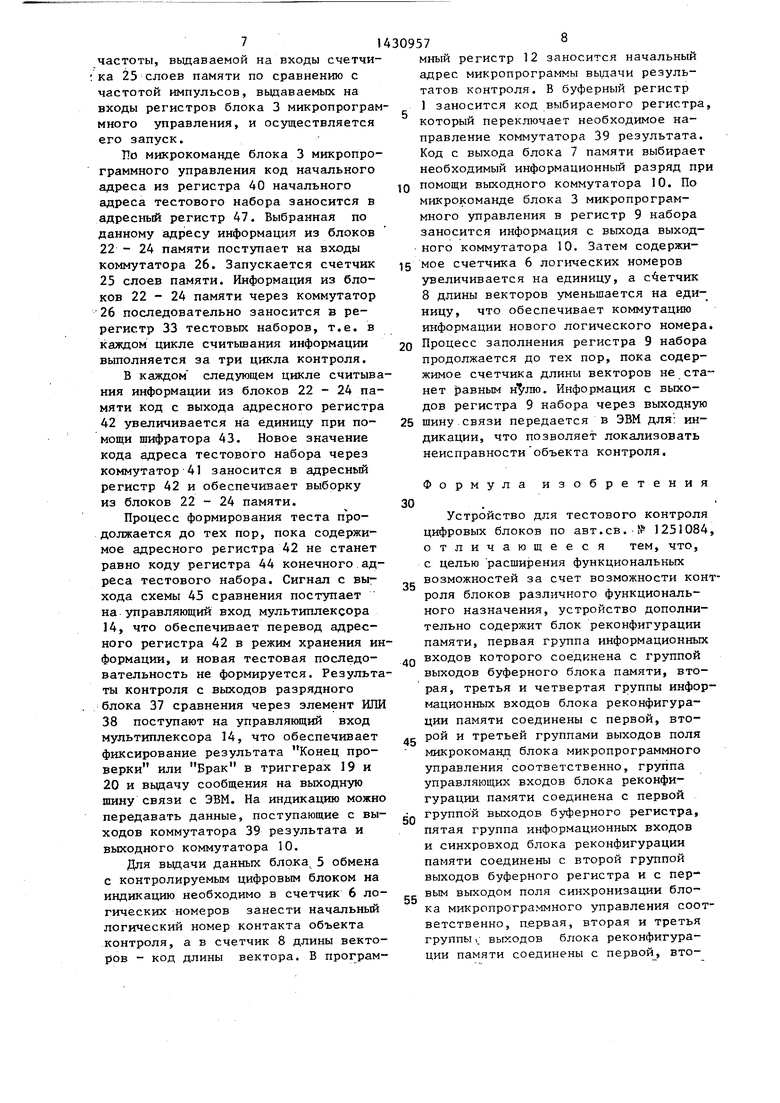

Во втором режиме устройство работает следующим образом.

Рассмотрим случай, когда для тес товых. наборов используются три блока 22 - 24 памяти.

5

0

5

Данные о распределении контактов контролируемого цифрового блока на входы и выходы, а также о маскировании незадействованных контактов блока заносятся в буферный блок 2 памяти описанным ранее способом.

Выходные сигналы буферного регистра 1 устанавливают коммутатор 27 блока 4 реконфигурации памяти в режим передачи данных на входы регистра 32 блока 5 обмена с контролируемым циф- ровьпу блоком, а элемент И 30 - в состояние, разрешающее прохождение импульсов записи на синхровход регистра 32, в результате чего осуществляется запись содержимого буферного блока 2 памяти в регистр 32 масок каналов.

Затем элемент И 30 устанавливается в состояние, запрещающее прохождение синхросигналов на входы регистра 32 масок каналов, переводя его тем самым в режим хранения информации.

Аналогичным образом через коммутатор 28 блока 4 реконфигурации памяти осуществляется запись информации в регистр 34 кодов управления коммутатором входов - выходов блока 5 обме- 0 на с контролируемым цифровым блоком. Выходным сигналом буферного регистра 1 через элемент И 31 регистр 34 также переводится в режим хранения информации. Затем происходит занесение информации в блоки 22-24 памяти блока 3 микропрограммного управления. Особенностью при занесении информации следует считать, что первый тестовый набор заносится по первому адресу блока 23 памяти тестовых наборов, второй тестовый набор заносится по первому адресу блока 22 памяти масок каналов, третий тестовый набор заносится по первому адресу блока.24 памяти кодов управления коммутатором вхьдов - выходов. А так как максимальная частота тестового контро-: ля в основном определяется временем цикла считывания из блоков 22 - 24, то это дает возможность при минимальном цикле считьгеания повысить скорость тестового контроля в три раза.

С выхода буферного регистра 1 устанавливается коэффициент деления счетчика 25 слоев памяти. По входной шине связи с ЭВМ в блок 18 заносится код коэффициента увеличения частоты, обеспечивающий прием информации с контролируемого цифрового блока и

5

0

5

0

5

7

частоты, выдаваемой на входы счетчика 25 слоев памяти по сравнению с частотой импульсов, выдаваемых на входы регистров блока 3 микропрограм много управления, и осуществляется его запуск.

ТТо микрокоманде блока 3 микропрограммного управления код начального адреса из регистра 40 начального адреса тестового набора заносится в адресный регистр 47. Выбранная по данному адресу информация из блоков 22 - 24 памяти поступает на входы коммутатора 26. Запускается счетчик 25 слоев памяти. Информация из блоков 22 - 24 памяти через коммутатор 26 последовательно заносится в ре- регистр 33 тестовых наборов, т.е. в каждом цикле считьшания информации выполняется за три цикла контроля.

В каждом следующем цикле считыва ния информации из блоков 22 - 24 памяти код с выхода адресного регистра 42 увеличивается на единицу при помощи шифратора 43. Новое значение кода адреса тестового набора через коммутатор 41 заносится в адресный регистр 42 и обеспечивает выборку из блоков 22 - 24 памяти.

Процесс формирования теста продолжается до тех пор, пока содержимое адресного регистра 42 не станет равно коду регистра 44 конечного,адреса тестового набора. Сигнал с выхода схемы 45 сравнения поступает на управляющий вход мультиплексора 14, что обеспечивает перевод адресного регистра 42 в режим хранения ин формации, и новая тестовая последовательность не формируется. Результа ты контроля с выходов разрядного блока 37 сравнения через элемент ИЛИ 38 поступают на управляющий вход мультиплексора 14, что обеспечивает фиксирование результата Конец проверки или Брак в триггерах 19 и 20 и вьщачу сообщения на выходную шину связи с ЭВМ. На индикацию можно передавать данные, поступающие с выходов коммутатора 39 результата и выходного коммутатора 10.

Для выдачи данных блока 5 обмена с контролируемым цифровым блоком на индикацию необходимо в счетчик 6 логических номеров занести начальный логический номер контакта объекта контроля, а в счетчик 8 длины векторов - код длины вектора. В програм30957

мный регистр 12 заносится начальный адрес микропрограммы выдачи результатов контроля. В буферный регистр 1 заносится код выбираемого регистра, который переключает необходимое направление коммутатора 39 результата. Код с выхода блока 7 памяти выбирает необходимый информационный разряд при

jQ помощи выходного коммутатора 10. По микрокоманде блока 3 микропрограммного управления в регистр 9 набора заносится информация с выхода выходного коммутатора 10. Затем содержи-

15 мое счетчика 6 логических номеров увеличивается на единицу, а с етчик 8 длины векторов уменьшается на еди- ницу, что обеспечивает коммутацию информации нового логического номера.

20 Процесс заполнения регистра 9 набора продолжается до тех пор, пока содержимое счетчика длины векторов не станет равным . Информация с выходов регистра 9 набора через выходную

25 щину связи передается в ЭВМ для; индикации, что позволяет локализовать неисправности объекта контроля.

Формула изобретения

Устройство для тестового контроля

цифровых блоков по авт.св. № 1251084, отличающееся тем, что, с целью расщирения функциональных возможностей за счет возможности контроля блоков различного функционального назначения, устройство дополнительно содержит блок реконфигурации памяти, первая группа информационных

Q входов которого соединена с группой выходов буферного блока памяти, вторая, третья и четвертая группы информационных входов блока реконфигурации памяти соединены с первой, вто.g рой и третьей группами выходов поля микрокоманд блока микропрограммного управления соответственно, группа управляющих входов блока реконфигурации памяти соединена с первой

СП группой выходов буферного регистра, пятая группа информационных входов и синхровход блока реконфигурации памяти соединены с второй группой выходов буферного регистра и с первым выходом поля синхронизации блока микропрограммного управления соответственно, п.ервая, вторая и третья группы , выходов блока реконфигурации памяти соединены с первой, вто35

55

От 73

От 24

От

Ofrrfg

/с

HS5

SmfJ

OmtS

H/ttfe

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-15—Публикация

1987-01-27—Подача