в каждом блоке определения ряда расп; еделения объединены и подключены к выходу соответствующего регистра, входы сброса всех счетчиков каждого канала блоков определения ряда распределения объединены с вторым входом второго элемента ИЛИ и входом сброса генератора импульсов блока формирования кодов углов фазовых сдвигов, с первым входом второго триггера и входом сброса узла пересчета блока управления и являются входом сброса анализатора, вход пуска которого подключен к второму входу второго триггера блока управления, каждый выход дешифратора ,которого подключен к первому входу соответствующего элемента И блока формирования кодов углов фазовых сдвигов и первому входу узла переноса соответствующего блока определения ряда распределения, вторые входы узлов переноса объединены и подключены к выходу счетчика блока формирования кодов

6182

углов фазовьпс сдвигов, выход четвертого элемента И которого подключен к входу второго делителя частоты блока управления и третьим входам узлов переноса блоков определения ряда распределения, а второй вход четвертого элемента И блока формирования кодов углов фазовых сдвигов соединен с выходом первого триггера блока управления, счетный вход узла пересчета которого и управляющ гй вход первого делителя частоты соединены соответственно с выходом нуль-органа блока формирования кодов углов фазовых сдвигов и выходом генератора импульсов блока формирования кодов углов фазовых сдвигов, при этом измерительные входы анализатора подключены соответственно к вторым входам элементов И блока фйрьгарования кодов углов фазовых сдвигов, третий вход первого элемента И которого соединен е выходом второго триггера блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Цифровое устройство для коммутации симистора | 1982 |

|

SU1039005A1 |

| Импульсно-фазовая следящая система | 1982 |

|

SU1023280A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1146803A1 |

| Устройство для поверки преобразователей фаза-код | 1990 |

|

SU1774298A1 |

| Способ определения мгновенных значений фазового сдвига электрических сигналов | 1988 |

|

SU1559308A1 |

| Устройство для преобразования координат | 1984 |

|

SU1179324A1 |

СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР, содержащий три блока определения ряда распределения, каждый из которых содержит R каналов и счетчики по числу каналов, блок управления, состоящий из двух триггеров и последовательно соединенных узлов пересчета и дешифратора, отличающийс я тем, что, с целью повьшения точности, в него введен блок формирования кодов углов фазовых сдвигов, содержащий четыре элемента И, нульорган, генератор импульсов, элемент задержки, счетчик и два элемента ИГЩ, входы первого из которых соединены соответственно с выходами первых трех элементов И, а выход первого элемента ИЛИ блока формирования кодов углов фазовых сдвигов соединен с входом нуль-органа, выход которого подключен к входу запуска генератора импульсов, первому входу четвертого элемента И и входу элемента задержки, выход которого связан с первЕ 1м входом второго элемента ИЛИ, выкод генератора импульсов соединен с входом записи счетчика, а выход второго элемента ИЛИ соединен с входом сброса счетчика блока формирования кодов углов фазовых сдвигов, в блок управления введены два делителя частоты, первый информационный вход перпого из которых является входом задания переменного коэффициента анализатора, второй информационный вход соединен с первым выходом дешифратора, а выход первого делителя частоты блока управления соединен с первым входом первого триггера, второй вход кото(Л рого подключен к выходу второго дес лителя частоты блока управления, при этом в каждый блок определения § ряда распределения введены последовательно соединенные узел переноса и регистр, а в каждый канал - две схемы сравнения на неравенство и со Од элемент И, выход которого соединен со счетным входом счетчика своего канала, первьй и второй входы эле00 tsD мента И в каждом канале подключены соответ&твенно к выходам схем сравнения на нераве вство своего канала, первые входы первых схем сравнения на неравенство каждого канала блоков определения ряда распределения соединены с соответствующим входом задания значений нюкней границы канала, первые входы вторых схем сравнения на неравенство каящого канала - с соответствующим входом задания зна гений верхней границы канала, а вторые входы схем сравнения на неравенство

t

Изобретение относится к автоматике и может быть использовано длч статистического анализа параметров электрической сети.

Известен статистический анализатор качества напряжения, содержащий элементы НЕ, релаксационный элемент и идентичные цепочки последовательно соединенных измерительных органов, логических элементов И и счетчиков, причем вторые входы элементов И объединены и подключены к выходу релаксационного элемента, входы измерительных органов также объединены, а их выходы через элементы НЕ связаны с третьими входами элементов И у .

Это устройство позволяет осуществлять статистический анализ уровня напряжения и обладает сравнительно невысокой точностью анализа.

Наиболее близким к изобретению по технической сущности является статистический анализатор качества налряжения, содержащий последовательно соединенные входное устройство, первый шаговый распределитель, пороговое

устройство, первый триггер, усилитель, второй шаговьй распределитель и схему индикацииj состоящую из счетчиков, причем второй вход первого триггера

подключен к выходу элемента времени и первому входу второго триггера, второй вход которого связан с вторым выходом первого триггера, а через схему задержки и формирователь импульсов сброса - с третьим входом первого триггера и через пересчетяую схему с третьим входом второго триггера, выход которого подключен к второму входу порогового устройства и

последовательно соединенным генератору тактовых импульсов, пересчетной схеме, дешифратору, блоку усилителей и схеме коммутации .

Анализатор САКН-1 осуществляет

анализ аналоговой функции, представляющей собой уровень напряжения, При анализе с помощью функций, задаваемых в цифровой форме, например, угла фазового сдвига необходимо осуществлять

дополнительное преобразование код напряжение, что требует дополнитель31

ных аппаратурных затрат и снижает точность анализа.

Кроме того, первый и второй шаговые распределители представляют собо контактные группы реле, обмотки кото рых входят в схему коммутации. Наличие реле может вызвать ложное сраба.тывание контактных групп и появление неконтролируемого отказа при сваривании контактов реле. Это понижает надежность устройства и точность анализа.

Целью изобретения является повышение точности и надежности.

Поставленная цель достигается тем, что в статистический анализатор содержащий три блока определения ряда распределения, каждый из которых содержит п каналов и счетчики по числу каналов, блок управления, состоящий из двух триггеров и последовательно соединенных узлов пересчета и. дешифратора, введен блок формирования кодов углов фазовых сдвигов, содержащий четьгре элемента И, нуль-орган, генератор импульсов, элемент задержки, счетчик и два элемента ИЛИ, входы первого из которых соединены соответственно с выходами первых трех элементов И, а выход первого элемента ИЛИ блока формирования Кодов углов фазовых сдвиго соединен с входом нуль-органа, выход которого подключен к входу запуска генератора импульсов, первому входу четвертого элемента И и входу элемента задержки, выход которого связан с первым входом второго элемента ИЛИ выход генератора импульсов соединен с входом записи счетчика, а выход . второго элемента ИЛИ соединен с входом сброса счетчика блока формирования кодов углов фазовых сдвигов, в блок управления введены два делителя частоты, первый информационный вход первого из которых является входом задания переменного коэффи- . циента анализатора, второй информационный вход соединен с первым выходом дешифратора, а выход первого делителя частоты блока управления соединен с первым входом первого триггера, второй вход которого подключен к выходу второго делителя частоты блока управления, при этом.в.каждый блок определения ряда распределения введены последовательно соединенные узел переноса и регистр, а в каждый

182Л

канал - две схемы сравнения на неравенство и элемент И, выход которого соединен со счетным входом счетчика своего канала, первый и второй входы элемента И в каждом канале подк11ючен соответственно к выходам схем сравнения на неравенства своего канала, первые входы первых схем сравнения на неравенство каждого канала блоков определения ряда распределения соединены с соответствующим входом задания значений нцжней границы канала, первые входы вторых схем сравнения на неравенство каждого канала - с соответствующим входом задания значений верхней границы канала, а вторые входы схем сравнения на неравенство в каждом блоке определения ряда распределения обьединены и подключен к выходу соответствующего регистра, входы сброса всех счетчиков каждого канала блоков определения ряда распределения объединены с вторым входом второго элемента ИЛИ и входом сброса генератора импульсов блока формирования кодов углов фазовых сдвигов, с первым входом второго триггера и входом сброса узла пересчета блока управления и являются входом сброса анализатора, вход пуск которого подключен к второму входу второго триггера блока управления, каждый выход дешифратора которого подключен к первому входу соответствующего элемента И блока формировани кодов углов фазовых сдвигов и первом входу узла переноса соответствующего блока определения ряда распределения вторые входы уэлов переноса объединены и подкгоочены к выходу счётчика блока формирования кодов углов фа:зовых сдвигов, выход четвертого элемента И которого подключен к входу второго делителя частоты блока управления и третьим входам узлов переноса блоков определения ряда- распределения , а второй вход четвертого элемента И блока формирования кодов углов фазовых сдвигов соединен с выходом первого триггера блока управления, «хчетный вход узла пересчета которого и управляюв ай вход перво.го делителя частоты соединены соответственно с выходом нуль-органа блока формирования кодов углов фазовых сдвигов и выходом генератора импульсов блока формирования кодов углов фазовых сдвигов, при этом измеритель51

иые входы анализатора подключены сооветственно к вторым входам элементов И блока формирования кодов углов фазовых сдвигов, третий вход первого элемента И которого соединен с выходом второго триггера блока управления.

Блок управления обеспечивает запуск устройства и совместное функционирование элементов и узлов статистического анализатора.

Блок формирования кодов углов фазовых сдвигов осуществляет измерение углов фазовых сдвигов между фазными напряжениями трехфазной сети.

Каждый блок определения ряда распределения углов фазового сдвига осуществляет формирование ряда распределения угла фазового сдвига меясду определенными фазными напряжениями трехфазной сети.

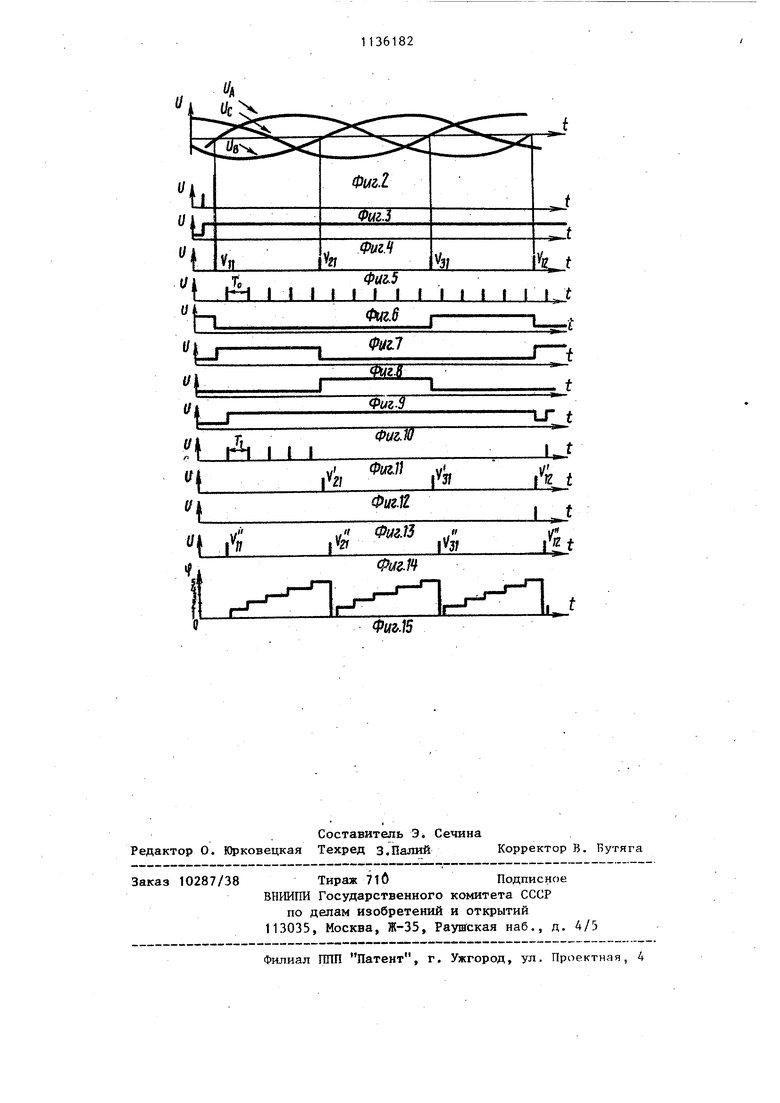

На фиг.1 изображена функциональная схема статистичЬркого анализатора; на фиг. 2 - 15 - временные диаграммы работы анализатора.

Анализатор содержит блок 1 управления, включающий триггер 2, последовательно соединенные узел 3 пересчета , дешифратор 4, делитель 5 частоты, триггер 6 и делитель 7 частоты блок 8 формирования кодов углов фазовых сдвигов, которьй состоит из трех элементов И 9 - 11, последовательно соединенных элемента ИЛИ 12, нульоргана 13 и генератора 14 импульсов, последовательно соединенных элемента ИЛИ 15 и счетчика 16, элемента И 17 и элемента 18 задержки. Узел 19 анаг лиза состоит из трех блоков 20-22 определения ряда распределения углов фазового сдвига, каждый из которых содержит узел 23 переноса, последовательно соединенные схему 24 сравнения на неравенство, элемент И 25 и счетчик 26, схему 27 сравнения на неравенство, регистр 28, последовательно соединенные схему 29 сравнения на неравенство, элемент И 30 и счетчик 31, схему 32 сравнения на неравенство, последовательно соединенные схему 33 сравнения на неравенство, элемент И 34 и счетчик 35, схему 36 сравнения на неравенство.

В исходном состоянии узел 3 пересчета, счетчики 16, 26, 31 и 35 обнулены, элемент И 9 закрыт по второму входу триггером 2, элементы И 10 и 11 закрыты дешифратором 4, генера1826

тор 14 импульсов не работает, элемен И 17 закрыт триггером 6.

Сигнал Пуск (фиг.З) поступает на установочный вход триггера 2 и перебрасывает его (фиг.4), при этом разрешающий потенциал с выхода триггера 2 поступает на элемент И 9.

Нулевое состояние узла 3 пересчет дешифрируется дешифратором 4, при этом на первомвыходе дешифратора 4 разрешающий сигнал (фиг.7), а на его втором и третьем выходах - запрещающие сигналы (фиг. 8 и 9).

Через элемент И 9, открытый триггером 2 и дешифратором 4, напряжение Од поступает, пройдя элемент ИЛИ 12, на вход нуль-органа 13.

При переходе напряжения ид через нуль (фиг.2) на выходе нуль-органа 13 вырабатьшается импульс V (фиг.5) Этот импульс, задержанный элементом 18 задержки (фиг.14), проходит через елемент ИЛИ 15 и подтверждает нулево состояние счетчика 16 (фиг.15). .

Импульс V поступает на вход элемента И 17, .но через этот элемент не проходит (фиг.12), так как элемен И 17 закрыт триггером 6 (фиг.10).

Импульс Vi изменяет состояние узл

3пересчета, при этом на втором выходе дешифратора 4 вьфабатывается разрешающий сигнал (фиг.8), а на первом и третьем выходах дешифратора

4- запрещающие сигналы (фиг.7 и 9). Запрещающим сигналом дешифратора 4 закрывается элемент И 9, а разрешающим сигналом дещфратор 4 открывает элемент И 10.

Напряжение Ug (фиг.2) через открытьй элемент И 10 и элемент ИЛИ 12 поступает на вход нуль-органа 13 (фиг.5).

Импульс V, (фиг.5) запускает г:енератор 14 импульсов, вырабатывающий последовательность импульсов с периодом следования TO (фиг.6), которые поступают на входы счетчика 16 и делителя 5 частоты с пер еменным коэффициентом деления q .

Каждый выходной импульс генератора 14, поступающий в счетчик 16, увеличивает- содержимое последнего на единицу (фиг.15).

На выходе делителя 5 частоты при наличии разрешающего сигнала с второго выхода дешифратора 4 (фиг.8) вырабатываются импульсы с периодом следования Т, То(фиг. 1 1 , при q 1).

Первый из выходных импульсов делителя 5 частоты поступает на установочный вход триггера 6 и взводит его (фиг.10) Триггер 6 открьгеает элемент И 17. При переходе напряжения Ug (фиг.2 через нуль на выходе нуль-органа 13 вырабатывается импульс Vj (фиг.5). Импульс Vgj поступает на вход элемент И 17, выходной импульс которого Vji (фиг,12) изменяет состояние делителя 7 частоты с коэффициентом деления К 3 и поступает на входы узла переноса блока 20, открытого разрешающ сигналом с второго выхода дешифратора 4 (фиг.8), блока 22, закрытого запрещающим сигналом с первого выход дешифратора 4 (фиг.7), и блока 21, закрытого запрещающим сигналом с третьего выхода дешифратора 4 (фиг.9 Импульс Vg (фиг.12) через узел 23 переноса переписывает содержимое счетчика 16 в регистр 28 блока 20. Блок 20 содержит узел 23 переноса регистр 28, схемы 24, 27, 29, 32, 33 и 36 сравнения на неравенство, элементы И 25, 30 и 34 и счетчики 26, 31 и 35. Диапазон ( , Cf изменения входной функции ( каждого из блоков 20-22 разбивается на п разрядов: (SiPo, S4,), (8cf, ,S(2l- . ,(4, .). гдеЬч-о 4mift; 4 4 nx xjS4i J 1,2,... ,i,... n - номер разряда; - ширина разряда. Каждому разряду соответствует счетчик (из числа счетчиков 26, 31 и 35), элемент И (из числа элементов И 25, 30 и 34) и две схемы сравнения на неравенство (из числа схем 24, 27 29, 32, 33 и 36 сравнения на неравенство.. .Одной из схем сравнения на неравенство каждого из каналов задается значение нижней границы разрядаЬ.,, а другой схеме сравнения на неравенство каждого из каналов - значение верхней границы разряда . Кроме того, на все схемы сравнения на неравенство подается из регистра 28 текущее значение с входной функции (угла фазового сдвига) блока. При попадании значения угла фазового сдвига в определенный канал , 8ч;., срабатывают схемы сравнения на неравенство, реализующие выражение Ц}., Ч (схемы 24, 29 и 33) и схемы сравнения на неравенство.

П361828

реализующие выражение qi s 5ц

(схемь- 27, 32, 36).

При одновременном срабатывании двух схем сравнения на неравенство определенного канала срабатывает элемент И этого канала и содержимое счетчика указанного канала увеличивается на единицу. Таким образом, в счетчиках 26, 31 и 35 фиксируется число попаданий текущего значений входной функции соответствующего блока 20 - 22 в. каждый канал, на которые разбит диапазон изменения входной функции, т.е. в этих счетчиках формируется ряд распределения входной функции. Импульс Vj (фиг.5), задержанный элементом 18 задержки (фиг.14, импульс Vj, ), проходит через элемент ИЛИ 15 и обнуляет счетчик 16 (фиг. 15). Импульс V. поступает также в узел 3 пересчета, изменяя его состояние. При этом на первом и втором выходах дешифратора 4 вьфабатываются запрещающие сигналы (фяг. 7 и 8), подающиеся на элементы И 9 и 10 и блоки 20 и 22. На третьем выходе дешифратора 4 (фиг.9) вырабатывается разрешающий сигнал, подающийся на элемент И 11 и блок 21. При переходе через нуль напряжения Ug (фиг,2), поступающего через открытьй элемент И 11 и элемент ИЛИ 12 на вход нуль-органа 13, последний вырабатывает импульс V (фиг.5). За период времени между импульсами V и V в счетчике 16, на вход которого поступают выходные импульсы генератора 14 (фиг.6), формируется . код, соответствующий углу фазового сдвига между напряжениями Ug и U (фиг.15). Импульс V , пройдя элемент И 17 (фиг. 12, импульс Vj) , открытый триггером 6 (фиг.10), переписывает содержимое счетчика 16 в блок 21, открытый разрешающим сигналом с третьего выхода дешифратора 4 (фиг.9). При этом увеличивается на единицу содержимое счетчика блока 21, соответствующего каналу, в. который попадает значение угла фазового сдвига, заФиксированного в счетчике 16 к моменту вьфаботки импульса V Выходной импульс V, (фиг.12) элемента И 17 изменяет состояние делителя 7 частоты с коэффициентом деления К 3.

Импульс V, (фиг.5) поступает на вход узла 3 и возвращает его в исходное состояние. При этом., на первом выходе дешифратора 4 вырабатывается разрешающий сигнал (фиг.7), открывающий блок 22 и элемент И 9, через который напряжение ид(фиг.2) поступает, пройдя элемент ИЛИ 12, на вход нуль-органа 13, а на втором и третье выходах дешифратора 4 вырабатываются запрещающие сигналы (фиг.8 и 9), закрывающие элементы И 10 и 11 и блоки 20 и 21.

Импульс V, (фиг.5), задержанный элементом 18 задержки (фиг.14, импульс ), проходит через элемент ИЛИ 15 и обнуляет счетчик 16 (фиг.15

При переходе напряжения U (фиг.2) через нуль на выходе нульоргана 13 вьфабатьюается импульс ч (фиг.5).

За период времени между импульсами V (фиг. 14) и V,2 (фиг.5) в счетчике 16, на вход которого поступают выходные импульсы генератора 14 (фиг.6), формируется код, соответствующий углу фазового сдвига между напряжениями Uj, и Ид (фиг. 15).

Импульс (фиг.5), пройдя элемент И 17 (фиг. 12, импульс ) , открытый триггером 6 (фиг.10), переписывает содержимое счетчика 16 в блок 22. При этом увеличивается на единицу содержимое счетчика блока 22 соответствующего каналу, в который попадает значение угла фазового сдвига, зафиксированное в счетчике 16 к моменту йыработки импульса.

Импульс (фиг.5), задержанньй элементом 18 задержки (фиг.14, импульс v ), проходит через элемент ИЛИ 15 и обнуляет счетчик 16 (фиг.15

Импульс V,, изменяет состояние узла 3. При этом на втором выходе дешифратора 4 вырабатьшается разрешающий сигнал (фиг.8), открывающий элемент И 10, через который напряжение иа поступает на вход нуль-органа 13, и блок 20, а на первом и третьем выходах дешифратора 4 вырабатываются запрещающие сигналы (фиг.7 и 9), закрьюающие элементы И 9 и 11 и блоки 21 и 22.,

Выходной импульс (Фиг. 12) элемента И 17 поступает на вход делителя 7 частоты с коэффициентом деления

К 3. По приходе на вход делителя 7 трех -импульсов V, , V, и V (фиг,12) он вырабатывает выходной и пульс (фиг.13), который перебрасьгаа триггер 6 (фиг.10), закрывая элемен И 17.

Один цикл работы статистического анализатора завершен.

В течение этого цикла блоком 1 управления последовательно открываются и закрываются элементы И 9 через которые напряжения Уд,Ug и UQ последовательно подаются на вход нуль-органа 13.

При переходе напряжений Пд, U и U(, через нуль на выходе нуль-органа

13вырабатьшаются импульсы V,,, V2,, Vj.H Интервалы времени между импульсами V, и V, V, и V, и соответствуют углам фазовых сдвигов между напряжениями U и Ug, Ug и Up , U и и д. .

Каждый из импульсов V, V,V и V, пройдя элемент 18 задержки, обнуляет счетчик 16., на вход которого постоянно подается последовательность выходных импульсов генератора

14(фиг.6). Таким образом, в счетчике 16 последовательно формируются коды углов фазового сдвига между напряжениями U и Un , Ug и Uj,, Up и и., которые соответственно поступают в блоки 20-22.

Длительность цикла определяется триггером 6 (фиг.10), который взводится по выходному сигналу делителя 5 частоты (фиг.11), открывая элемент И 17, и сбрасывается, закрывая элемент И 17, по выходному импульсу делителя 7 частоты (фиг.13), вьфабатьгоаемому по приходе на его вход с коэффициентом деления К 3 трех выходных импульсов Vj , V, и элемента И 17 (фиг.12).

Периодичность следования циклов определяется делителем 5 частоты с переменным коэффициентом деления q: после поступления q выходных импульсов генератора 14 и разрешающего сигнала с второго выхода дешифратора 4 на входы делителя 5 частоты последний вьфабатывает выход 1ой импульс, взводящий триггер 6.

Во всех пocлeдyюш x циклах работы статистический анализатор функционирует аналогично.

В блоке 20 формируется ряд распределения угла фазового сдвига между

напряжениями U и Ug; в блоке 21 ряд распределения угла фазового сдвига между напряжениями Un и в блоке 22 - ряд распределения угла фазового сдвига между напряжениями Uc и ид . . .

Изобретение позволяет осуществить статистический анализ угла фазового сдвига(известные устройства позволяют анализировать лишь уровень напряжения). Это дает возможность получить более полную информацию о состоянии трехфазной сети и, следовательно, повысить точность анализа.

Предложенное устройство позволяет анализировать функции, представленные

в цифровом виде (известные устройства анализируют аналоговую функцию, представляющую собой уровень напряжения) , и может непосредственно сопрягаться с различными цифровыми приборами, мащинами и системами, т.е. обладает большими функциональными

ВОЗМОЖНОСТЯМИ

Кроме того, техническими преш-iyществами предлагаемого устройства по сравнению с известным являются высокая надежность и точность, по- скольку ни в блоке формирования угла фазового сдвига, .ни в блоке анализа не содержится реле- и контактных групп.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Баркан Я.Д., Маркушевич Н.С | |||

| Использование статистической информации о качестве напряжения в электрических сетях | |||

| М., Энергия, 1972, с | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Говорящий кинематограф | 1920 |

|

SU111A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Техническое описание и инструкция по эксплуатации | |||

| Рижский опытный завод Латвэнерго, 1970, с | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-01-23—Публикация

1982-12-03—Подача