с выходами генератора импульсов, выходы делителей частоты соединены со входами соответствующих дешифраторов, выходы одного из дешифраторов через формирователь напряжения питания соединены со входами питания фазовращателей, а выходы другого дешифратора соединены со входами блока формирования опорного напряжения, другой вход которого соединен с выходом младших разрядов реверривного счетчика, вход которого соединен с выходом блока управления, выход фазовращателя точного отсчета соединен с одним из входов фазового детектора, к другому входу которого подключен выход блока формирования опорного напряжения, выход фазового детектора соединен со входом блока управления 2.

Недостатком данного преобразователя является его невысокая точность, вызванная нескомпенсированной погрешностью параметров синусного и косинусного каналов преобразования.

Цель изобретения - повышение точности преобразования.

Это достигается тем, что в него .введены блоки сравнения, фазосдвигающёе устройство, сумматор, избирательный усилитель, синхронные детекторы и блок преобразования кода в фазовый сдвиг двух напряжений, входы которого соответственно соединены с выходами второго делителя частоты, младших разрядов реверсивного счетчика и одного из синхронных детекторов, входы синхронизации которых соединены с выходами блока преобразования кода в фазовы .сдвиг двух напряжений, друтие выходы которого подключены к одним входам блока сравнения, другие входы которых соединены с выходами фазовращателя точного отсчета, выход одного из блоков сравнения подключен к одному из входов сумматора, к другому входу которого через фазосдвигающее устройство подключен выход другого блока сравнения, выход сумматора через избирательный усилитель подключен к сигнальным входам синхронных-детекторов, выход другого синхронного детектора соединен со входом блока управления ,

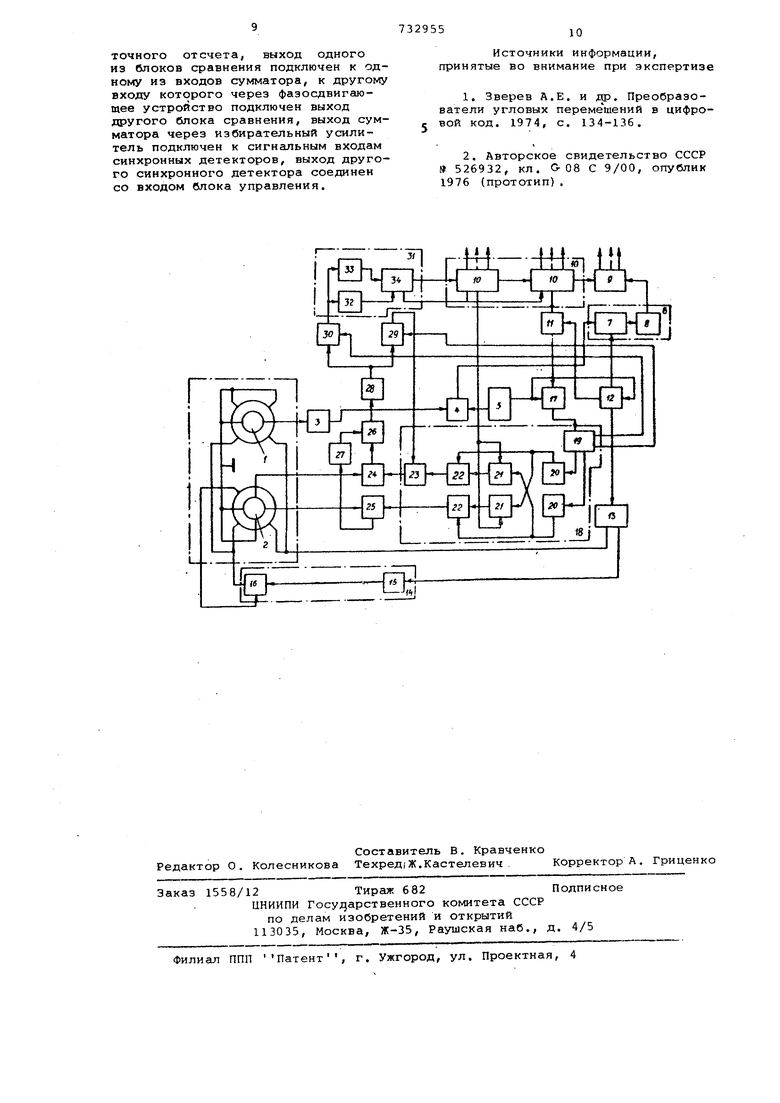

На чертеже представлена функциональная схема предлагаемого преобразователя .

Схема преобразователя содержит соединенные между собой фазоврашатели Грубого 1 и точного 2 отсчеTOiB, выполненные, например, в виде СКВТ, Выход фазовращателя 1 грубого отсчета через формирователь 3 соединен с одним входом синхронизатора 4, к другому входу которого подключен генератор 5 импульсов,вы

полненный на основе кварцевого генератора. Выход синхронизатора 4 соединен с одним из входов блока 6 формирования кода грубого отсчета, содержащего, например, блок 7 считывания кода и блок 8 памяти. Выход блока 6 формирования кода грубого отсчета подключен к одному входу блока 9 согласования отсчетов, к другому входу которого подключен выход реверсивного счетчика 10 ,выход старших разрядов которого соединен с одним из входов блока 11 ввода кода, к другому входу которого подключен выход первого делителя 12 частоты, соединенного с другим входом блока б формирования кода грубого отсчета и входом дешифратора 13, выходы которого через формирователь 14 напряжения питания соединен с входами питания фазоврашателей 1 и 2. Формирователь 14 напряжений питания включает формирователи 15 синусоидальных сигналов и усилители 16. Один вход второго делителя 17 частоты соединен с выходом блока 11 ввода кода, другие входш делителей 12 и 17 частоты соединены с выходом генератора 5 импульсов. Выход второго делителя 17 частоты соединен с одним из входов блока 18 преобразования кода в фазовый сдвиг, который включает дешифратор 19, формирователи 20 синусоидальных сигналов, блоки 21 преобразования кода в напряжение, сумматоры 22 и управляемый делитель 23 напряжения. Выход младших разрядов реверсивного счетчика 10 соединен со входами блоков 21 преобразования кода в напряжение, выходы блока 18 преобразования кода в фазовый сдвиг соединены с одними входами блоков 24 и 25 сравнения, другие входы которых соединены с выходами фазовращателя 2 точного отсчета, выход блока 24 сравнения подключен к одному входу сумматора 26 к другому входу которого через фазовращающее устройство 27 подключен выход другого блока 25 сравнения, выход сумматора 26 через избирательный усилитель 28 подключен к сигнальным входам синхронных детекторов 29 и 30, выход одного из синхронных детекторов 29 соединен с управляющим входом управляемого делителя 23 напряжения, являющегося одним из входов блока 18 преобразования кода в фазовый сдвиг двух напряжений. К входам синхронизации синхронных детекторов 29 и 30 подключены выходы деижфратора 19 блока 18 преобразования кода в фазовый сдвиг двух напряжений. Выход синхронного детектора 30 соединен со входом блока 31 управления, соединенного со входом реверсивного счетчика 10. Блок 3 управления включаег, например, блок 32 преобразования напряжения в частоту и блок 33 пороговых устройств и блок 34 управления счетчиком.

Предлагаемый двухотсчетный преобразователь работает следующим образом.

Стабильные по частоте импульсы подаются с генератора 5 импульсов на входы делителей 12 и 17 частоты выходные импульсы которых преобразуются дешифратором 13 в напряжение, из которых формируется питающее напряжение формирователями 14 фазовращателей 1 и 2.

Схема питания фазовращателей 1 и 2 предназначена для формирования и усилиления .синусоидальных напряжений , сдвинутых по фазе между собой на 90° с точностью 130 с. Формирование синусоидальных сигналов питания фазовращателей 1 и 2 выполнено так, что позволяет исключить применение избирательных цепей,что в свою очередь- обеспечивает высокую (не более ±20 с) температурную стабильность фазового сдвига. Принцип формирования синусоидальных сигналов основан на аппроксимации синусоиды вписанной ломанной. При разбиении периода формируемого питания на 16 участков в спектре сигнала присутствуют 15 и 17, 31 и 33 и т.д. гармоники с относительными амплитудами 0,44% и 0,34% и т.д. Формирователи 14, 15 синусоидальных сигнсшов состоят в свою очеред из 8 источников тока, заряжающи-х и разряжающих конденсатор, и ключей, коммутирующих токи источников по определенному закону от даиифратЪра 13. Источники тока усиливают по мощности сформированные напряжения и одновременно компенсируют постоянную составляющую, возникающую пр формировании синусоидального напряжения данным методом из-за неравенства токов :эаряда и разряда конденсатора, в результате чего с течением времени происходит накопление заряда на конденсаторе. Для компенсации постоянной составляющей она отделяется, инвертируется и подается по цепи обратной связи на конденсатор. Источники тока введены в преобразователь для устранения влияния изменения активных сопротивлений обмоток и магнитных свойств магнитопровода СКВТ. Как видно из блок-схемы источники стабилизуют ток в обмотках фазовращателя 2 точного отсчета СКВТ. В канале грубого отсчета питание СКВТ осуществляется от источников напряжения. Блок 18 преобразования кода в фазовый сдвиг двух напряжений преобразует число, записанное в реверсивном счетчике 10, в фазовый сдвиг по двум каналам.

Первый канап формирует большие фазовые сдвиги на основе информации от старших разрядов реверсивного счетчика 10. Он испопьзует принцип преобразования временной задержки в пропорциональный фазовый сдвиг. Если все триггеры делителя 17 частоты установлены в состояО

ние

, то при подаче импульсов

от генератора 5 импульсов дешифратором 19 и формирователями. 20 сину0соидальных сигналов будут генерироваться напряжения с О и 90Если за исходный момент выбрать момент, когда в младшем разряде делителя 17 частоты будет записана

5 , то фаза формируемых сигналов сместится на угол, пропорциональный весу единице младшего разряда, т.е. для 8-разрядного делителя это составит l24 22,5 .

0 Это дискретнос- ь изменения фазы компенсирующих сигналов за счет первого канала. В преобразователе это протекает следующим образом. Один раз за период формируемых сигналов по команде от делителя 17

5 частоты через блок 11 ввода кода число из старших разрядов реверсивного счетчика 10 записывается в делитель 17 частоты. Дешифратором 19 и формирователем 20 число транс0формируется в фазовый сдвиг формируемых сигналов относительно питающих напряжений, формируемых формирователем 14 питающих напряжений. Дешифратор 19 в отличие от дешифра5тора 13 форм}1рует еще два опорных прямоугольных напряжения, фаза которых изменяется аналогично компенсирующим напряжениям. В предлагаемом компенсационном преобразовате0ле дальнейшее уменьшение дискретности достигается введением второго канала, использующего принцип изменения фазы результирующего напряжения, получаемого при суммировании двух, находящихся в квадратуре, сиг5налов, один из которых модулируется по амплитуде. Для этого части напряжений от формирователей 20 , синусоидального сигнала модулируются кодом младших разрядов реверсив0ного счетчика 10 в блоках 21 преобразования напряжений в код. В сумматорах 22 осуществляется суммирование напряжений с соответствующими частями от блоков 21 преобразо5вания кода в напряжение. Результирующая дискретность изменения фазового сдвига компенсирующих напряжений определяется разрядностью всего реверсивного счетчика 10. Первое

0 компенсирующее напряжение от сумматора 22 через управляемый делитель 23 поступает на один блок 24 сравнения, а второе компенсирующее напряжение поступает прямо на другой блок 25 сравнения. Управляемый

5 делитель 23 изменяет амплитуду первого компенсирующего напряжения по сигналу от синхронного детектора 29. После блоков 25 и 26 сравнения напряжения рассогласования фазируют ся, для чего сигнал с блока 25 сравнения поворачивается по фазе на 90 фазовращающим устройством 27 и сумг/мруется с сигналом с блока 24 сравнения в сумматоре 26.Избирательным усилителем 28 выделяется первая гармоника частоты питания, а синхронные детекторы 30 и 29 выделяют две соответствующие: первую - пропорциональную разности фаз между сигн лами с СКВТ 2 и компенсирующими, вторую - пропорциональную разности амплитуд сравниваемых напряжений. Вторая составляющая подается на уп равляемый делитель 23 напряжения и изменяет амплитуду одного из ком пенсирующих напряжений, тем caivMM устраняется влияние неравенства амплитуд сравниваег ых напряжений на точность преобразования. Управляемый делитель 23 можно ставить в цепь любого компенсирующего напря,жения один и два в обе цепи, резул тат получается тот же. Напряжение, пропорциональное разности фаз срав ниваемых напряжений, поступает на блок 32 преобразования напряжения частоту и блок 33 пороговых устройств. Блок 32 преобразования напряжения в частоту формирует часто ту заполняющих импульсов, а блок 33 пороговых устройств совместно с блоком 34 управления реверсивным счетчиком определяют режим работы реверсивного счетчика 10, т.е. сум мирование или вычитание импульсов от блока 32 преобразования напряже ния в частоту или остановку счета, если напряжение синхродетектора 30 меньше пороговых уровней, В канале грубого отсчета код формируется с использованием метод стробирующей метки. Фазы питающих напряжений жестко связаны с числом в делителе 12 частоты. Из напряжения с СКВТ 1 формирователем 3 и синхронизатором 4 формируется импульс считывания, по которому код из делителя 12 частоты через блок считывания записывается в блок 8 памяти, В блоке 9 согласования отсчетов он корректируется по коду к нала точного отсчета, поступающему от двух или трех старших разрядов реверсивного счетчика 10.Синхронизатор 4 исключает перенос кода в блок 8 памяти в момент переходного процесса в делителе 17 частоты. Предлагаемый компенсационный .преобразователь угол-код позволяет чомпенсировать ряд технологических погрешностей изготовления СКВТ, а также неравенство амплитуд питгиощих напряжений и неортогональность их. Использование источников тока для питания обмоток точного отсчета и системы автоподстройки амплитуд сравниваемых обеспечивает требуемую стабильность преобразования. При испытаниях с серийными фазоврашателями с редукцией 32 и 64 точность преобразования составляет 5 угл, с в диапазоне.температур -40 + бОС. Формула изобретения Двухотсчетный преобразователь угла поворота вала в код, содержащий соединенные между собой фазовращатели грубого и точного отсчетов, выход фазовращателя грубого отсчета через формирователь подключен к одному входу синхронизатора, к другому входу которого подключен генератор импульсов, выход синхронизатора соединен с одним из входов блока формирования кода грубого отсчета, выход которого подключен к одному входу блока согласования отсчетов, к другому входу которого подключен выход реверсивного счетчика, выход старших разрядов которого соединен с одним из входов блока ввода кода, к другому входу которого подключен выход первого делителя частоты, соединенного с другим входом блока формирования кода грубого о-гсчета и с входом дешифратора, выходы которого через формирователь напряжений питания соединены с входами питания фазовращателей, входы реверсивного счетчика соединены с выходами блока управления, один вход второго делителя частоты соединен с выходом блока ввода кода, другие входы делителей частоты соединены с выходом генератора импульсов, отличающийся тем, что, с целью повышения точности преобразователя, в него введены блоки сравнения, фазовращающее устройство, сумматор, избирательный усилитель, синхронные детекторы и блок преобразования кода в фазовый сдвиг двух напряжений, входы которого соответственно соединены с выходами второго делителя частоты, младших разрядов реверсивного счетчика и одного из синхронных детекторов, входы синхронизации которых соедииены с выходами блока преобразования кода в фазовый сдвиг двух напряжений, другие выходы которого подключены к одним входам блоков сравнения, другие входы которых соединены с выходами фазовращателя

точного отсчета, выход одного из einoKOB сравнения подключен к одному из входов сумматора, к другому входу которого через фаэосдвигающее устройство подключен выход другого блока сравнения, выход сумматора через избирательный усилитель подключен к сигнальным входам синхронных детекторов, выход другого синхронного детектора соединен со входом блока управления.

Источники информации, принятые во внимание при экспертизе

1.Зверев А.Е. и др. Преобразователи угловых перемешений в цифровой код. 1974, с. 134-136.

2.Авторское свидетельство СССР 526932, кл. G-08 С 9/00, опублик 1976 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU669374A1 |

| Двухотсчетный преобразователь углового перемещения в цифровой код | 1977 |

|

SU651389A2 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU684578A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1979 |

|

SU924736A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU813487A1 |

| Компенсационный преобразователь угловых перемещений в код | 1975 |

|

SU546922A1 |

ГТпггзП tbilU

Авторы

Даты

1980-05-05—Публикация

1977-11-02—Подача