(54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД

зователя напряжение-частота, выходы которых соединены соответственно с первым и вторым входами блока управления, выход которого подключен к первому входу реверсивного счетчика, выход второго синхронного детектора соединен с входом интегратора 2.

Недостатком этого устройства является недостаточная точность и стабильность.

Цель изобретения - повышение точности и стабильности устройства.

Это достигается тем, что в устройство введены второй преобразователь код-напряжение, два масштабных усилителя, фазосдвигаюший блок и четыре сумматора, второй выход реверсивного счетчика соединен с первым входом второго преобразователя код-напряжение, выходы третьего и четвертого формирователей синусоидального сигнала соединены соответственно через первый и второй масштабные усилители с вторыми входами первого и второго преобразователей код-напряжение, выходы третьего формирователя синусоидального напряжения и второго преобразователя код-напряжение подключены ссответственно к перму и второму входам второго сумматора, первый и второй выходы синусно-косинусного вращающегося трансформатора подключены соответственно к первым входам третьего и четвертого сумматоров, вторые входы которых соединены соответственно с выходами второго сумматора и управляемого делителя напряжения, выход третьего сумматора непосредственно, а выход четвертого сумматора через фазосдвигающий блок подключены соответственно к первому и второму входам пятого сумматора, выход которого соединен с входом избирательного усилителя, выход задающего генератора подключен к второму входу формирователя импульса ввода кода, второй выход блока управления соединен с вторым и третьим входами реверсивного счетчика.

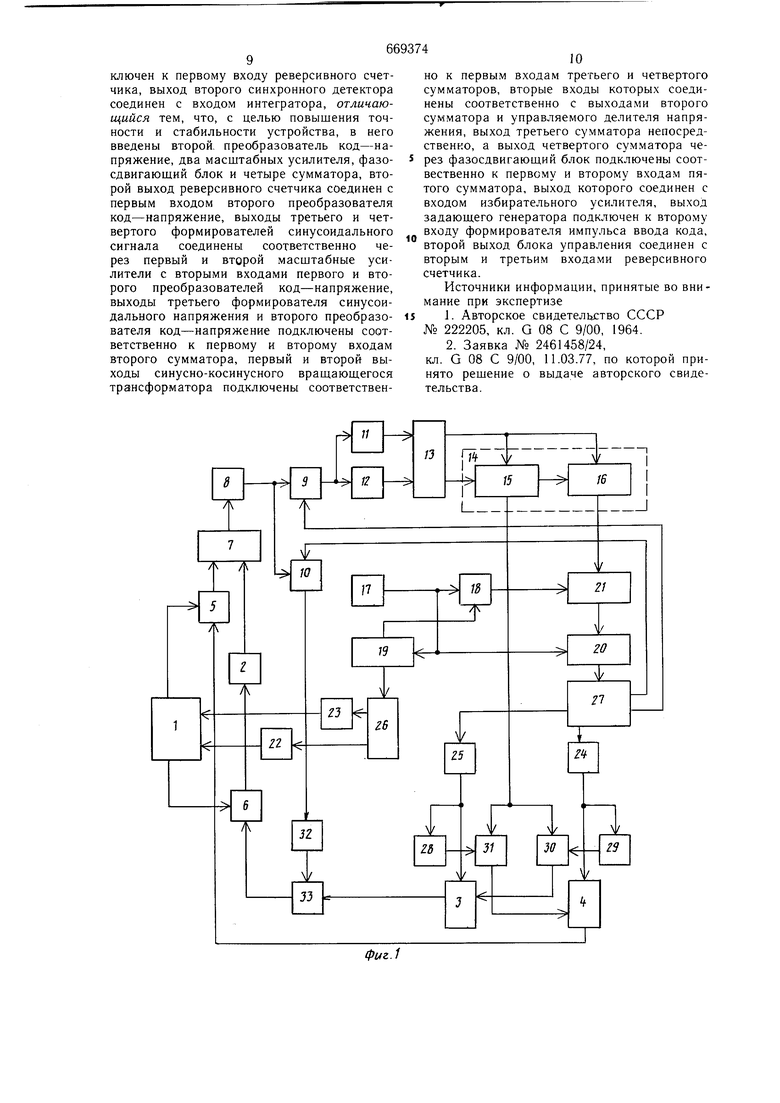

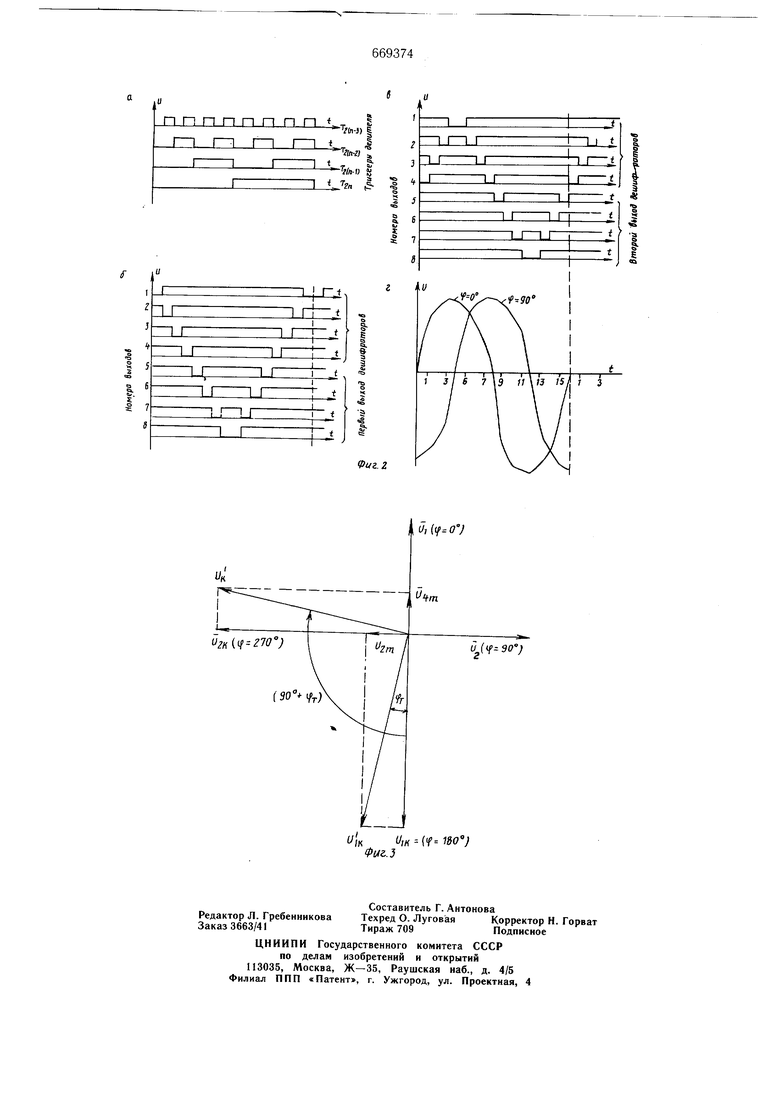

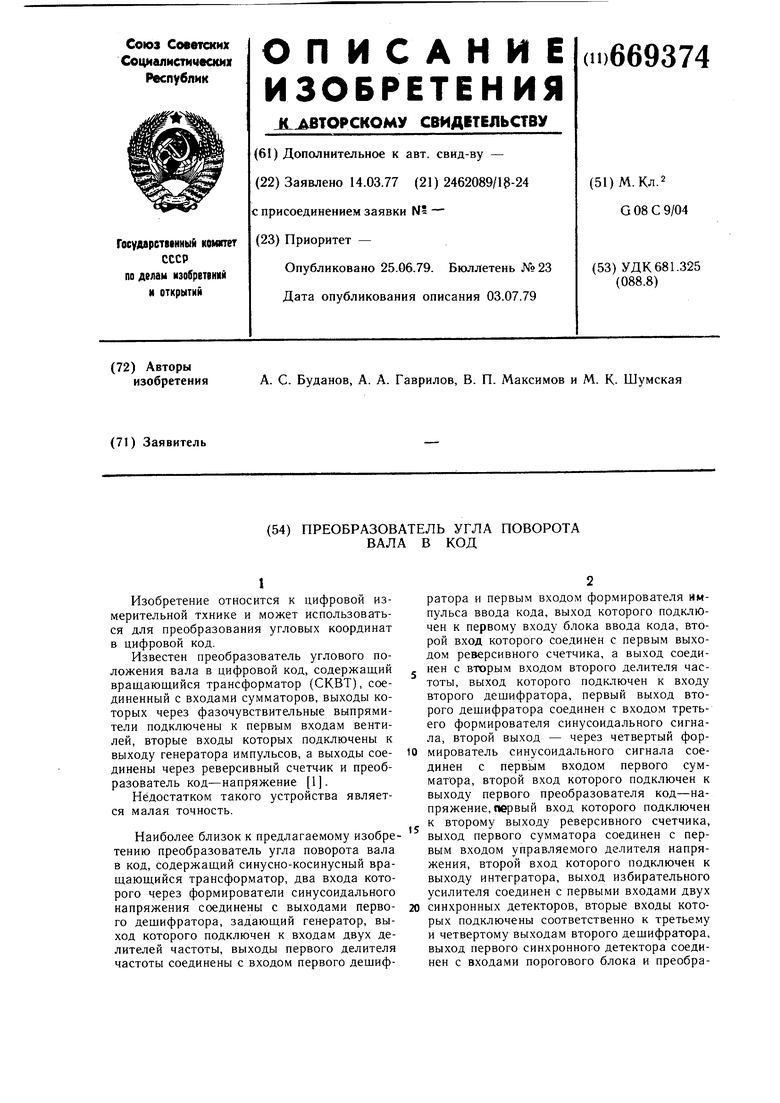

На фиг. 1 дана блок-схема предлагаемого преобразователя; на фиг. 2 - диаграммы, поясняющие работу устройства; на фиг. 3 - векторная диаграм.ма, поясняющая доворот по фазе компенсирующих напряжений точным каналом.

Устройство содержит синусно-косинусный вращающийся трансформатор 1, фазосдвигающий блок 2, первый, второй, третий, четвертый, пятый сумматоры 3-7, избирательный усилитель 8, первый и второй синхронные детекторы 9 и 10, пороговый блок И, преобразователь 12 напряжение- частота, блок 13 управления, реверсивный счетчик 14, младнше разряды 15, старшие разряды 16, задающий генератор 17, формирователь 18 импульса ввода кода, первый и второй делители 19 и 20 частоты, блок 21 ввода кода,первый,второй, третий и четвертый формирователи 22-25 синусоидального напряжения, дешифраторы 26 и 27 первый и второй, первый и второй масщтабные усилители 28 и 29, первый и второй преобразователи 30 и 31 код-напряжение, интегратор 32, управляемый делитель 33 напряжения.

Выход задающего генератора 17 соединен с входами первого и второго делителей 19 и 20 частоты. Выход первого делителя 19 частоты через первый дешифратор 26,

0 первый и второй формирователи 22 и 23 синусоидального напряжения подключены к обмоткам статора синусно-косинусного вращающегося трансформатора 1. Выход второго делителя 20 частоты через второй дешифратор 27 подключен к третьему формирователю 24 синусоидального на пряжения, второй вход второго делителя 20 частоты подключен к выходу блока 21 ввода кода. Первая обмотка ротора синусно-косинусного вращающегося трансформатора 1 через

0 третий сумматор 5 соединена с первым входом пятого сумматора 7, а вторая обмотка - через четвертый сумматор 6 и фазосдвигающий блок 2 соединена с другим входом пятого сумматора 7. Выход пятого сумматора 7 через избирательный усилитель 8 подключен к первым входам первого и второго синхронных детекторов 9 и 10. Выход первого синхронного детектора 9 через параллельно включенные пороговый блок 11 и преобразователь 12 напряжение-частота

0 соединен с блоком 13 управления, выход которого соединен с реверсивным счетчиком 14, а выход старших разрядов 16 реверсивного счетчика 14 подключен к одному из входов блока 21 ввода кода. Выход второго синхронного детектора 10 через интегратор 32, управляемый делитель 33 напряжения подключен к второму входу четвертого сумматора 6. Входы формирователя 18 импульса ввода кода подключены к выходу задающего генератора 17 и к второму выходу первого делителя 19 частоты, а выход формирователя 18 импульса ввода кода подключен к другому входу блока 21 ввода кода. Выход младших разрядов 15 реверсивного счетчика 14 подключен к первым входам первого и второго преобразователей 30

и 31 код-напряжение, выходы которых подключены к входам первого и второго сумматоров 3 и 4. Два выхода второго дешифратора 27 подключены к вторым входам первого и второго синхронных детекторов

0 9 и 10, другие два выхода - к входам третьего и четвертого формирователей 24 и 25 синусоидального напряжения. Выход третьего формирователя 24 синусоидального на-, пряжения подключен -к входу второго сумматора 4 и через второй масщтабный усили тель 29 к второму входу первого преобразователя 30 код-напряжение. Выход четвертого фор.мирователя 25 синусоидального напряжения подключен к входу первого сумматора 3 и через первый масштабный усилитель 28 к второму входу второго преобразователя 31 код-напряжение. Выход первого сумматора 3 соединен с одним из входов управляемого делителя 33 напряжения, а выход второго сумматора 4 - с вторым входом третьего сумматора 5.

СКВТ 1 преобразует угол поворота выходного вала Б напряжение, фазовый сдвиг которого пропорционален углу поворота входного вала. Два напряжения с роторных обмоток (синусной и косинусной) подаются на один из входов третьего и четвертого сумматоров 5 и 6. На вторые входы этих сумматоров подаются компенсирующие напряжения, которые сдвинуты друг относительно друга на 90°. В исходном состоянии, т. е. при равенстве фаз. напряжений с СКВТ 1 и компенсирующих напряжений, сигналы на входах сумматоров 5 и 6 сдвинуты на 180°. Напряжение с сумматора 6 фазируется с выходным напряжением сумматора 5, для этого фазосдвигающий блок 2 сдвигает на угол ±90° выходное напряжение сум.матора 6. Знак плюс или минус зависит от того, какое напряжение с СКВТ подается на сумматор 6 - с синусной или косинусной обмоток. Пятый сумматор 7 суммирует сфазированные напряжения, а избирательный усилитель 8 выделяет первую гармонику сигнала. На первом синхронном детекторе 9 фазовый сдвиг первой гармоники преобразуется в постоянное напряжение, пропорциональное фазовому сдвигу между напряжениями с СКВТ 1 и компенсационным, а второй синхронный детектор 10 выделяет только составляющую, пропорциональную амплитудному разбалансу между выходными напряжениями с СКВТ и компенсационными, снимае.мых с сумматоров 3 и 4.

После интегрирования интеграторов 32 напряжение, пропорциональное амплитудному разбалансу, поступает на управляемый делитель 33 напряжения, который изменяет амплитуду поступающего на него напряжения до тех пор, пока сигнал амплитудного разбаланса не станет равен нулю. Напряжение пропорциональное фазовому разбалансу с первого синхронного детектора 9 поступает на преобразователь 12 напряжение- частота и пороговый блок 11. Первый преобразует напряжение в частоту импульсов, заполняющих через блок 13 управления реверсивный счетчик 14, второй - вырабатывает команды на режим работы: с какого уровня выходного напряжения фазового разбаланса начинать заполнение и характер работы - суммирование или вычитание. Пороговый блок 11 исключает колебания по мере уменьщения фазового разбаланса, последнее влечет уменьщение частоты заполнения реверсивного счетчика 14. Порог чувствительности выбирается так, чтобы он был

меньще половины цены младщего разряда 15 реверсивного счетчика 14. До настоящего времени рассматривался тракт обработки выходных сигналов СКВТ после суммирования с компенсационными.

Импульсы задающего генератора 17 поступают одновременно на два делителя 19 и 20 частоты, при этом делитель 20 допускает начальную установку состояний своих триггеров. Состояние четырех последних триггеров делителя 19 частоты поступает на дешифратор 26, который в зависимости от состояния четырех триггеров делителя 19 вырабатывает импульсы на двух выходах (см. фиг. 2а, б,в). Формирователи 22 и 23 синусоидального напряжения вырабатывают путем кусочнолинейной аппроксимации два напряжения (см. фиг. 2г), сдвинутых друг относительно друга на 90°, для создания режима фазовращателля на СКВТ 1. В делитель 20 частоты один раз за период формируемого напряжения вводится число из старщих

0 разрядов 16 реверсивного счетчика 14. Команда на ввод числа вырабатывается формирователем 18 импульса ввода кода в момент, когда все триггеры делителя 19 частоты устанавливаются в нулевое состояние. Связь между задающим генератором 17 и формирователем 18 импульса ввода кода предназначена для строгой временной привязки импульсов задающего генератора 17 к .моменту установки делителя 19 частоты в нулевое положение и для стробирования им0 пульса ввода кода.

Таким образом, число из старшего разряда 16 реверсивного счетчика 14 через блок 21 ввода кода записывается в делитель 20 частоты и является исходнь м для него.

5 Так как коэффициенты делителей 19 и 20 равны, при завершении цикла делителем 19 частоты (переход в нулевое состояние) делитель 20 частоты вернется также к исходно.му числу, записанному ранее из старших

р разрядов 16 реверсивного счетчика 14. Полученный за счет ввода числа временной сдвиг между идентичными кодовыми комбинациями в делителях 19 и 20 частоты дешифраторы 26 и 27 и формирователи 22- 25 синусоидального напряжения трансформируют в фазовый сдвиг напряжений. Ранее уже говорилось, что разрешающая способность устройства при использовании то.тько преобразования временного сдвига кодовых комбинаций в делитетях 19 и 20 частоты в фазу компенсирующего напряжения составит -, гдеп - число разрядов делитлей 19 и 20 частоты. Если п 8, то разрешающая способность составит 1°2122Л

Одновременно работает другой канал изменения фазы компенсирующих напряже НИИ, который использует принцип изменения фазы результирующего напряжения, получаемого за счет суммирования двух, находящихся в квадратуре, .сигналов, один из которых модулирутся по амплитуде. При этом максимальная величина амплитуды модулированного напряжения определяется максимальным значением угла доворота компенсирующих напряжений точным каналом. Если амплитуда формируемого синусоидального сигнала составляет ЗВ, то Стилке 1°2422,5 «0,0245 рад V( m Vi «, ЗВ 0,0245 « 73 MB Доворот по фазе компенсирующих точным каналом поясняется фиг. 3 Vi и Vt - векторы выходных напряжений с СКВТ 1, их зависит от угла поворота ротора; VIK и Угк - векторы компенсирующих напряжений с формирователей 25и 24 синусоидального напряжения. На фиг. 3 показано положение, когда канал грубой подстройки по фазе отработал разбаланс, а канал точной подстройки отрабатывает при этом разбаланс 1°2422,5. Выше уже говорилось, что условием равновесия является сдвиг на 180° напряжений, поступающих на сумматоры 6 и 5. Напряжения с формирователей синусоидальных напряжений поступают на масштабные усилители 28 и 29, при этом VZK- не инвертируется, а VfK - инвертируется. На преобразователях 30 и 31 код-напряжение максимальные величины V) и Уг,делятся пропорционально коду, записанному в младших разрядах 15 реверсивного счетчика 14. В сумматорах 3 и 4 сигналы с формирователей 24 и 25 синусоидального напряжения суммируются с квадратурными, снимаемыми с преобразователей 30 и 31 кодна.пряжение. Благодаря наличию двух каналов удается поднять разрешающую способность и точность устройства без увеличения частоты задающего генератора 17 и увеличения коэффициента деления делителей 19 и 20 частоты. Разрешающая способность предлагаемого устройства равна -|, где п - число разрядов в делителях 19 и 20 частоты и соответственно число старщих разрядов 16 реверсивного счетчика 14; m - число младших разрядов 15 реверсивного счетчика 14. При п 8 и ш 8 разрешающая способность составит Да 19,77. Использование напряжений с двух роторных обмоток СКВТ 1 позволяет уменьшить результирующую фазовую ощибку от неравенства и от неортогональности питающих напряжений. Стабильность результатов измерений обусловлена выбором структуры формирования питающих и компенсирую.. ших напряжений, не содержащей избирательных цепей, а также принятой структурой эле.мента сравнения фаз. При малых значениях фазовых сдвигов элемент сравнения фаз, включающий блоки 2, 5, 6, 7, 9, дает погрешность определения равенства фаз первых гармоник при от неравенства амплитуд при коэффициенте нелинейных искажений около 0,1% меньше, чем ±5 угловых секунд. Регулировкой добротности избирательного усилителя 8 легко снижается погрешность от высших гармонических составляющих до допустимой величины, а выбором коэффициента усиления первой гармоники избирательным усилителем 8 снижается приведенное значение дрейфа нулевого уровня синхронного детектора 9. Как уже говорилось, дальнейшему повышению точности определения равенства фаз первых гармоник препятствовало неравенство амплитуд напряжений с СКВТ I и компенсирующих. В данном устройстве введена обратная связь, с целью уменьшения неравенства амплитуд, а следовательно, и компенсация погрешности, обусловленная названной причиной. Блоки 10, 32, 33 реализуют это. Формула изобретения Преобразователь угла поворота вала в код, содержащий синусно-косинусный вращающийся трансформатор, два входа которого через формирователи синусоидального напряжения соединены с выходами первого дещифратора, задающий генератор, выход которого подключен к входам двух делителей частоты, выходы первого делителя частоты соединены с входом первого дешифратора и первым входом формирователя импульса ввода кода, выход которого подключен к первому входу блока ввода кода, второй вход которого соединен с первым выходом реверсивного счетчика, а выход соединен с вторым входом второго делителя частоты, выход которого подключен к входу второго дещифратора, первый выход второго дешифратора соединен с входом третьего формирователя синусоидального сигнала, второй выход - через четвертый формирователь синусоидального сигнала соединен с первым входом первого сумматора, второй вход которого подключен к выходу первого преобразователя код-напряжение, первый вход которого подключен к второму выходу реверсивного счетчика, выход первого сумматора соединен с первым входом управляемого делителя напряжения, второй вход которого подключен к выходу интегратора, выход избирательного усилителя соединен с первыми входами двух синхронных детекторов, вторые входы которых подключены соответственно к третьему и четвертому выходам второго дешифратора, выход первого синхронного детектора соединен с входами порогового блока и преобразователя напряжение-частота, выходы которых соединены соответственно с первым и вторым входами блока управления, выход которого подключей к первому входу реверсивного счетчика, выход второго синхронного детектора соединен с входом интегратора, отличающийся тем, что, с целью повышения точности и стабильности устройства, в него введены второй, преобразователь код-напряжение, два масштабных усилителя, фазосдвигающий блок и четыре сумматора, второй выход реверсивного счетчика соединен с первым входом второго преобразователя код-напряжение, выходы третьего и четвертого формирователей синусоидального сигнала соединены соответственно через первый и второй масштабные усилители с вторыми входами первого и второго преобразователей код-напряжение, выходы третьего формирователя синусоидального напряжения и второго преобразователя код-напряжение подключены соответственно к первому и второму входам второго сумматора, первый и второй выходы синусно-косинусного вращаюш,егося трансформатора подключены соответственно к первым входам третьего и четвертого сумматоров, вторые входы которых соединены соответственно с выходами второго сумматора и управляемого делителя напряжения, выход третьего сумматора непосредственно, а выход четвертого сумматора через фазосдвигающий блок подключены соотвественно к первому и второму входам пятого сумматора, выход которого соединен с входом избирательного усилителя, выход задающего генератора подключен к второму входу формирователя импульса ввода кода, второй выход блока управления соединен с вторым и третьим входами реверсивного счетчика. Источники информации, принятые во внимание при экспертизе J. Авторское свидетельство СССР № 222205, кл. G 08 С 9/00, 1964. 2. Заявка № 2461458/24, кл. G 08 С 9/00, 11.03.77, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухотсчетный преобразователь углапОВОРОТА ВАлА B КОд | 1979 |

|

SU840995A1 |

| Преобразователь угол-код | 1979 |

|

SU801020A1 |

| Преобразователь угла поворота вала в код | 1977 |

|

SU684578A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU771115A2 |

| Двухотсчетный преобразователь углового перемещения в цифровой код | 1977 |

|

SU651389A2 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU732955A1 |

| Преобразователь угла поворотаВАлА B КОд | 1979 |

|

SU813487A1 |

| Двухотчетный преобразователь углового перемещения в цифровой код | 1975 |

|

SU526932A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

Авторы

Даты

1979-06-25—Публикация

1977-03-14—Подача