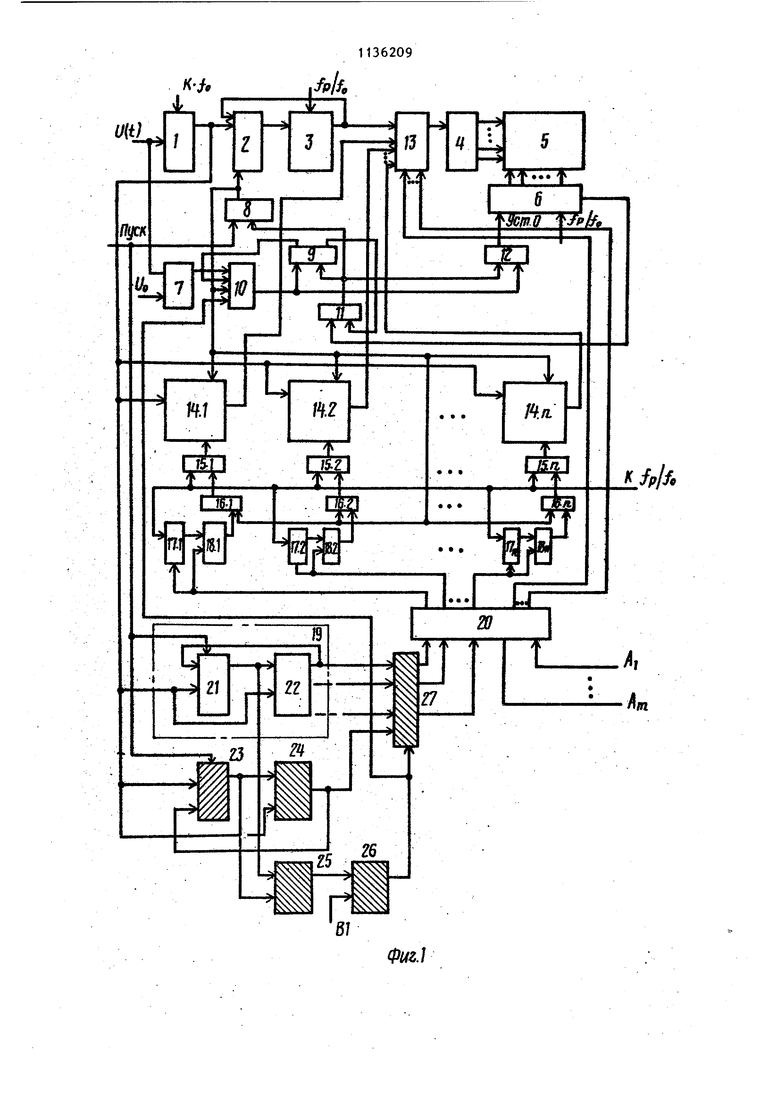

Изобретение относится к информационно-измерительной технике и мсшет быть использовано в цифровой осциллографии для обнаружения и регистрации однократных сигналов. Известно устройство для ивдикации содержащее последовательно соединенные аналого-цифровой преобразователь коммутатор, запоминающее устройство, дешифратор, матричную панель, распределитель импульсов, компаратор и устройство управления l . Для правильной установки уровня синхронизации необходимо знать форму ожидаемого сигнала. В данном устройстве нельзя вьщелить начало сигнала у процессов с постоянной составляющей. Кроме того, оно характеризуется наличием ручной установки уровня син хронизации, что не позволяет включать регистраторы данного типа в автоматизированные измерительные системы, а также невозможностью исследования задних фронтов у сигналов с неопределенной длительностью. По основному авт. св. № 963082 известно устройство для отображения информации, содержащее газоразрядную индикаторную панель, дешифратор, рас пределитель импульсов, аналого-цифро вой преобразователь, первый, второй и третий коммутаторы, блок памяти, схему сравнения, первый и второй три геры, первый и второй элементы И, эл мент ИЛИ, группу блоков памяти, грул пу элементов И, группу элементов ИЛИ группу счетчиков, группу триггеров, блок фиксации признака, группу регис ров максимума отображения сигнала и группу схем сравнения 2. Цель изобретения - расширение области применения путем обеспечения возможности отображения случайных процессов произвольной формы. Поставленная цель достигается тем что в устройство для отображения информации введены регистр минимума отображаемого сигнала, первый и второй компараторы, вычитающий блок и четвертый коммутаторj причем первые входы регистра минимума отображаемог сигнала и первого компаратора соединены с выходом аналого-цифрового пре образователя, второй вход первого компаратора соединен с выходом регистра минимума отображаемого сигнала и первым входом вычитающего блока, выход первого компаратора соединен с вторым входом регистра минимума отображаемого сигнала и входом четвертого коммутатора, второй вход вычитающего блока соединен с выходом группы регистров максимума отображаемого сигнала, а выход - с первым входом второго компаратора, второй вход которого является входом устройства, а выход соединен с управляющим входом четвертого коммутатора и входом первого элемента И, а выходы четвертого коммутатора соединены с входами треть- его коммутатора. На фиг. 1 показана блок-схема предлагаемого устройства; на фиг. 2 временные диаграммы сигналов, поясняющие его работу. Устройство для отображения информации содержит аналого-цифровой преобразователь 1 .первый коммутатор 2,блок ; 3 памяти, дешифра -ор 4, газоразрядную индикаторную панель 5, распределитель 6 импульсов, схему 7 сравнения, первый 8 и второй 9 триггеры, первый 10 и второй 11 элементы И, элемент ИЛИ 12, второй коммутатор 13, группу блоков 14 памяти, группу элементов И 15, группу элементов ИЛИ 16, группу счетчиков 17 группу триггеров 18, блок 19 фиксации признака, третий коммутатор 20, группу регистров 21 максимума отображаемого сигнала, группу схем 22 сравнения, регистр 23 минимума отображаемого сигнала, первый компаратор 24, вычитающий блок 25, второй ко1ипаратор 26 и четвертый коммутатор 27. Вход аналого-цифрового преобразователя 1 связан с входной шиной,, а выкод - с первым коммутатором 2, группой блоков 14 памяти, группой регистров 21 максимума отображаемого сигнала, группой схем 22 сравнения, регистром 23 минимума отображаемого сигнала и первым компаратором 24, выход первого коммутатора 2 соединен с блоком 3 памяти, выход которого соединен с первым входом второго коммутатора 13, другие входы которого связаны с выходами группы блоков 14 пам.яти, управляющие входы - с выходами третьего коммутатора 20, а его выход с дешифратором 4, выходы которого соединены с газоразрядной индикаторной панелью 5, другие входы которой соединены с распределителем 6 импульсов, вход которого соединен с выходом элемента ИЛИ 12, первый вход которой связан с выходом первого элемента И 10 и входом второго триггера 9, второй вход - с вторыми входами второго 9 и первого 8 триггеров и выходом второго элемента И 11, входы которого соединены с выхо дом второго триггера 9и выходом piac пределителя 6 импульсов, выход первого триггера 8 соединен с входами первого коммутатора 2 группы блоков 14 памяти и первого элемента И 10 другие входы которого связаны с выходом второго триггера 9, выходом второго компаратора 26 и выходом схемы 7 сравнения, вход которой соединен с входной шиной. Группа элементов И 15 соединена своими выходами с входами группы блоков 14 памяти, а входами - с выходами группы элементов ИЛИ 16 и с входами группы счетчиков 17, входы установки тз ноль которых соединены с выходами третьего коммутатора 20 и входами группы триггеров 18, а выходы - с другими входами группы триггеров 18, выходы которых связаны с входами группы эле ментов ИЛИ 16, другие входы которых соединены с выходом первого триггера 8, группа регистров 21 максимума .отображаемого сигнала соединена свои{ми входами с выходом группы схем 22 :сравнения и входом четвертого коммутатора 27, а выходами - с входами группы схем 22 сравнения, входы установки нуля регистра 23 минимума отображаемого сигнала связаны с шиной Пуск, вход - с выходом первого компаратора 24 и входом четвертого коммутатора 27 и выходы - с входами первого компаратора 24 и входами вычитающего блока 25, выходы которого соединены с первыми входами второго компаратора 26, вторые входы которого соединены с входами устройства, а выход - с входом четвертого коммутатора 27, выходы которого соединены с входами .третьего коммутатора 20.

Устройство работает следуюшим образом.

При поступпении сигнала Пуск первый триггер В переводится в состоя ние логической единицы, соответствукг щее режиму записи. При этом коды с вых.ода аналого-цифрового преобразователя 1 записываются последрватель1/Ь в блок 3 памяти. При срабатывании компаратора 7 (момент превышения сигналом уровня UQ) распределитель 6 импульсов сбрасывается в ноль и начинается счет записанных ординат в бло памяти (емкость распределителя 6 импульсов равна емкости блока памяти). При переполнении распределителя 6 импульсов триггер 8 переключается импульсом переполнения в ноль, что соответствует окончанию записи.

Для более детального изучения формы исследуемого сигнала в устройстве имеются п однородных каналов, которые работают следующим образом.

Коды с аналого-цифрового преобразвателя 1 поступают, на входы группы блоков 14 памяти и последовательно записываются в них, вытесняя старые значения. Длительность записи определяется объемом счетчика 17 группы. При его переполнении триггер 18 группы переключается в состояние логической единицы, что соответствует режиму воспроизведетшя.

Таким образом, момент обнуления счетчика 17 группы является моментом начала записи. Обнуление счетчика 17 группы производится блоком 19 фиксации признака, которьй в режиме синхрнизации максимуме работает следующим образом.

Коды с аналого-цифрового преобразователя сравниваются на схеме 22 сравнения и при поступлении кода большего, чем тот, который хранится в регистре 21 максимума отображаемого сигнала, формируется импульс синхронизации, который сбрасывает счетчик 17 группы в ноль, что является моментом начала записи. Одновременно зтот код записывается в регистр 21 максимума отображаемого сигнала и считается: максимумом сигнала. Если в дальнейшем появится большее значение, чем записанное, то сформируется новый импульс синхронизации и все повторится заново.

В тракте прохождения синхроимпуль са предлагаемое устройство работает следукхцим образом..

На выходе второго компаратора 26 формируется сигнал блокировки син хронизацки до некоторого момента и этим сигналом на данное время запрещается прох сясдение синхроимпульсов через первую схему И 10 и четвертый коммутатор 27.

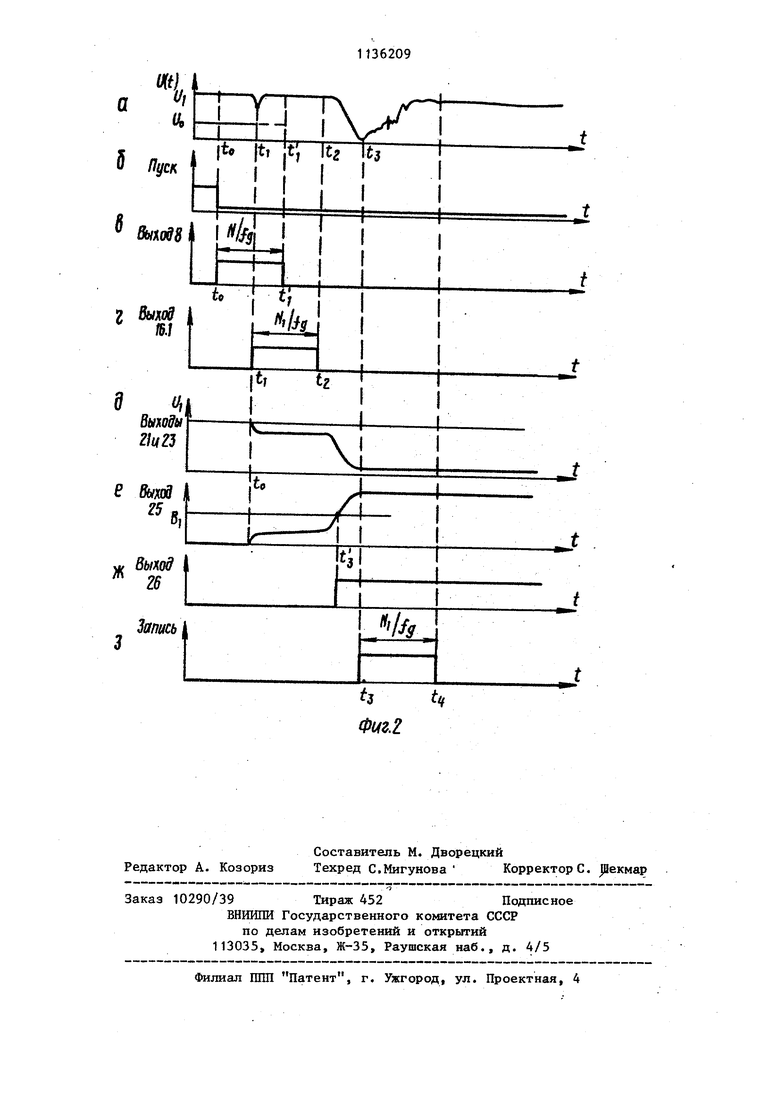

С приходом импульса Пуск -триггер 8 переводится в состояние Jfoгической единицы и начинается режиу записи. Одновременно в регистр 21 максимума отображаемого сигнала и регистр 23 минимума отображаемого сигнала записывается код ординаты сигнала в момент Ц, (фиг. 2д). В следующие моменты времени при появлении большего кода срабатывает группа схем сравнения, и этот код записывается в регистр 21 максимума отображаемого сигнала, соответственно меньшее значение кода записывается в регистр 23 минимума отображаемого сигнала (фиг. 2д). Коды с выходов этих регистров подаются на вычитающий блок 25, где вычисляется их разность (фиг. 2е) размах сигнала. При малом значении разности между максимальным и минимальным значениями кодов (например, когда размах сигнала не достигает 40% диапазона аналого-цифрового преобразователя - минимальное значение амплитуды сигнала, при которой обычно можно производить измерения в цифровом осциллографе), т.е. при код на выходе вычитающего блока 25 меньшем, чем заданное значение В1, у второго компаратора 26 на выходе буд сформирован логический ноль (фиг.2ж) который подается на вход первой схемы И и на вход разрешения четвертого коммутатора 27. При этом импул сы синхронизации, выработанные на выходе компаратора 7 и выходах блока фиксации признака, не проходят на входы установки в ноль распределителя импульсов 6 и счетчиков 17 группы Когда размах исследуемого сигнала достигнет заданного значения кода В1 (фиг. 2е), второй компаратор 26 сформирует на выходе логическую еди ницу (фиг. 2ж), после чего разреша196 ется прохождение импульсов синхронизации на входы установки в ноль соответствующих счетчиков 17 группы. В момент tj сформирован синхроимпульс, после которого в одну из групп 14 памяти будет записана часть сигнала на интервале (t3 и t,), что является наиболее информативным участком сигнала (фиг. 2з). Технический эффект от внедрения изобретения заключается . в сокращении необходимого числа повторений экспериментов; в упрощении работы оператора, так как не надо устанавливать уровень синхронизации, -.- . требований к априорным сведениям об исследуемьпс сигналах;в возможности включений предлагаемого устройства в автоматизированные измерительные системы. Экономический эффект от внедрения изобретения тесно связан со стоимостью проводимого эксперимента, в результате которого необходимо зарегистрировать однократный сигнал. С применением предлагаемого устройства нет надобности повторять эксперимент дважды, так как для точного вьщеления момента начала сигнала не Надо знать его форму для точной установки уровня синхронизации. Зачастую стоимость самого эксперимента зо много раз превосходит стоимость всего регистратора, поэтому экономический эффект от внедрения изобретения в таких областях исследования как ядерная физика, радиолокация, исследование различного рода взрывов, изучении природньк явлений ожидается очень большим.

J t

Ф{4г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации однократных процессов | 1981 |

|

SU959147A1 |

| Устройство для отображения информации | 1981 |

|

SU963082A1 |

| Устройство для отображения информации | 1985 |

|

SU1300547A1 |

| Цифровой вольтметр | 1979 |

|

SU845281A1 |

| Многоканальный анализатор электрофизиологических сигналов | 1991 |

|

SU1806603A1 |

| Устройство аналого-цифрового преобразования | 1981 |

|

SU1012435A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ВЫБРОСОВ И ПРОВАЛОВ НЕСТАЦИОНАРНОГО НАПРЯЖЕНИЯ | 2000 |

|

RU2189631C2 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Статистический анализатор | 1980 |

|

SU960847A1 |

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ по авт.св. 963082, отличающееся тем, что, с целью расширения области применения путем обеспечения возможности отображения случайных процессов произвольной формы, в него введены регистр ьинимума отображаемого сигнала, первый и второй компараторы, вычитающий блок и четвертый коммутатор , причем первые входы регистра минимума отображаемого сигнала и первого компаратора соединены с выходом аналого-цифрового преобразователя, второй вход первого компаратора соединен с выходом регистра минимума отображаемого сигнала и первым входом вычитающего блока, выход первого компаратора соединен с вторым входом регистра минимума отображаемого сигнала и входом четвертого коммутатора, второй вход вычитакщего блока соединен с выходом группы регистров максимума ртображаемого сигнала,)а выход - с., первым входом второго компаратора, второй вход которого является входом устройства, а выход соединен с управляхлрм входом четвертого коммутатора и входом первого элемента И, а выходы четвертого коммутатора соединены с входами третьего коммутатора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для индикации | 1974 |

|

SU525977A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отображения информации | 1981 |

|

SU963082A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1985-01-23—Публикация

1983-11-09—Подача