1

Изобретение относится к автоматизированным си-стемам управления и контроля и предназначено для сокращения избыточности при кодировании стационарных случайных процессов.

Известно устройство адаптивного кодирования с прогнозированием 1 .

Однако такое устройство требует априорного знания характеристик кодируемого процесса или введения в схему прогнозирующего устройства, вызывающего большие аппаратурные затраты . ..

Наиболее близким к предлагаемому по технической сущности является устройство адаптивного кодирования, содержащее сумматор, аналого-цифровой преобразователь, вход которого является входом устройства, а выходы подключены к первой группе входов коммутатора и соответствующим входам блоков статистической оценки максимума и минимума процесса, выходы которых соединены соответственно с вто-.

рой группой входов коммутатора и с первой группой входов сумматора., вторая группа входов которого подключена к соответствующим выходам коммутатора. Выходы всех разрядов сумматора подключены к первой груяпе входов дополнительного коммутатора, выходы старших разрядов которого подключены к соответствующим входам блог КЗ изменения масштаба, выходы кото10рого соединены соответственно с второй группой входов дополнительного коммутатора, выход которого является выходом устройства 2.

15

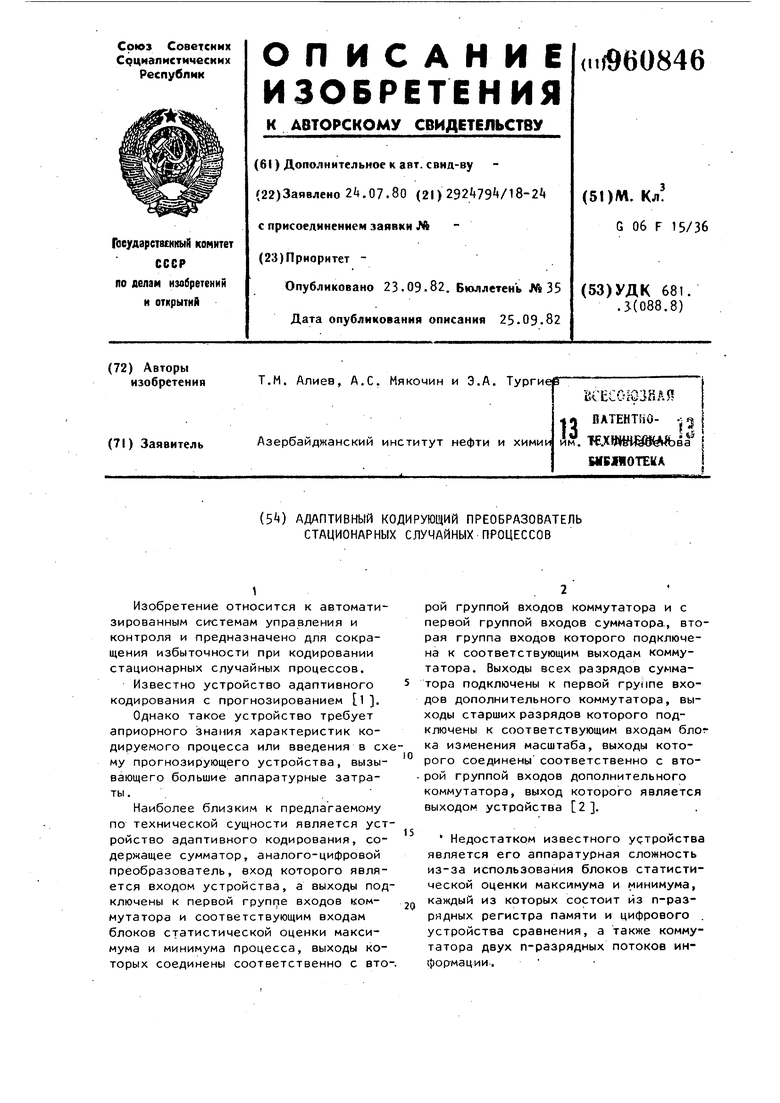

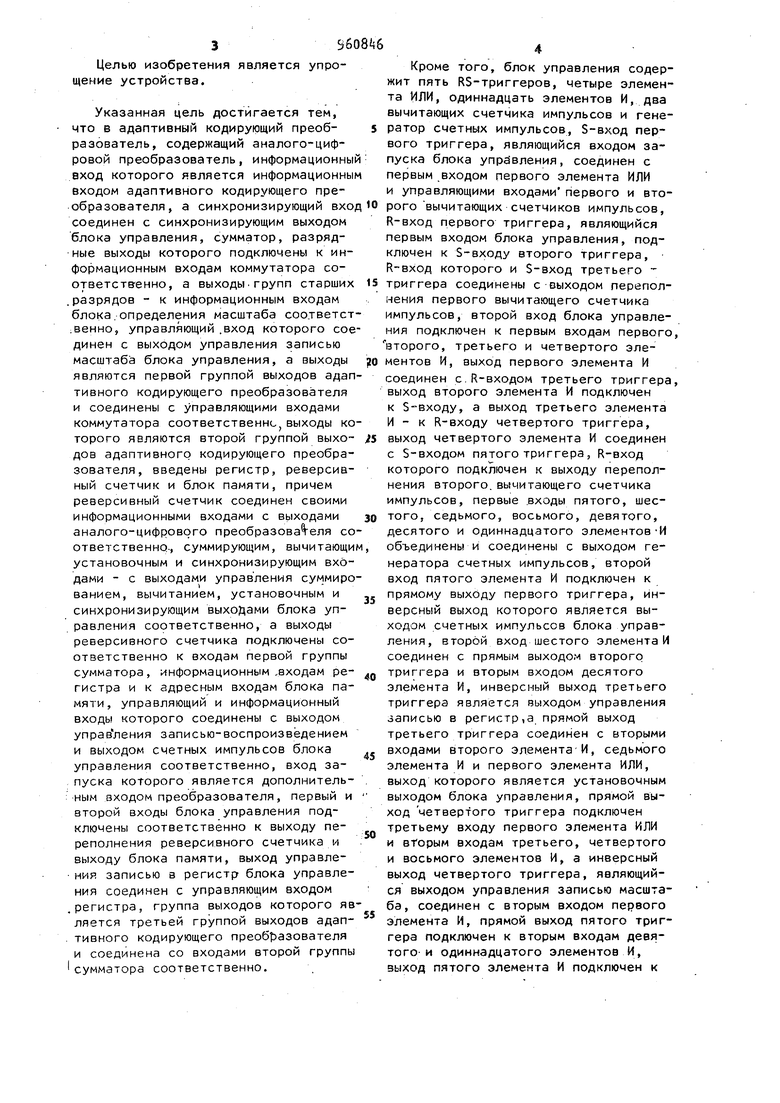

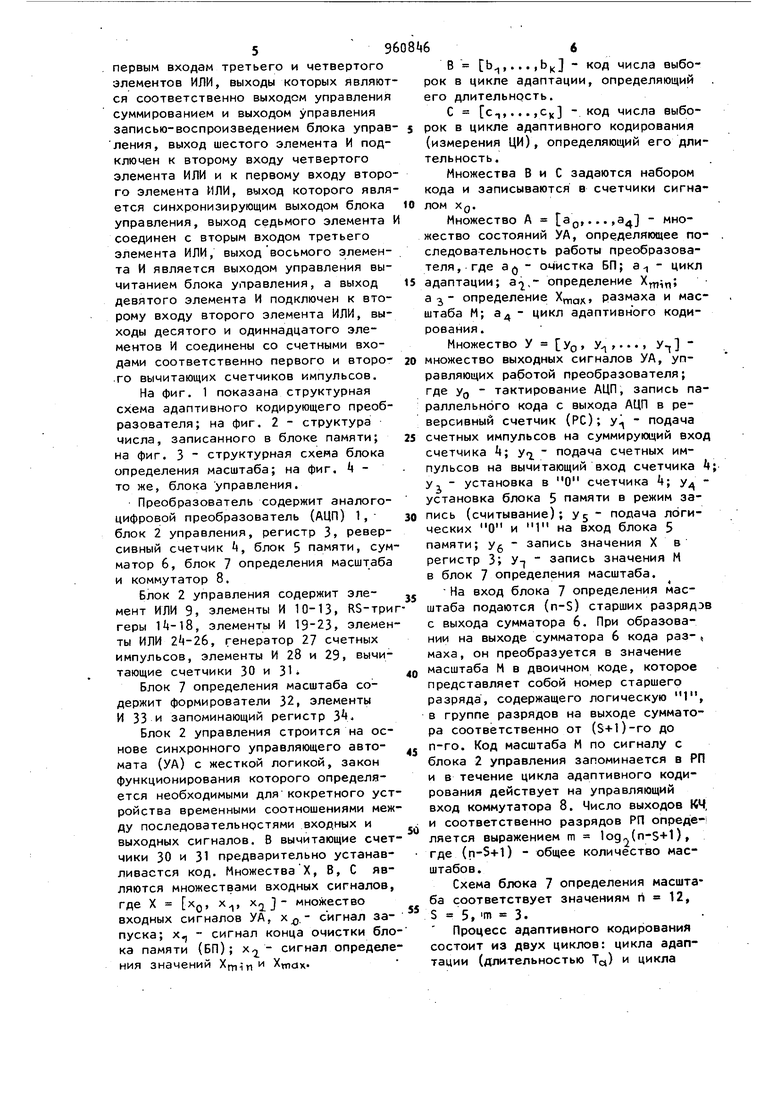

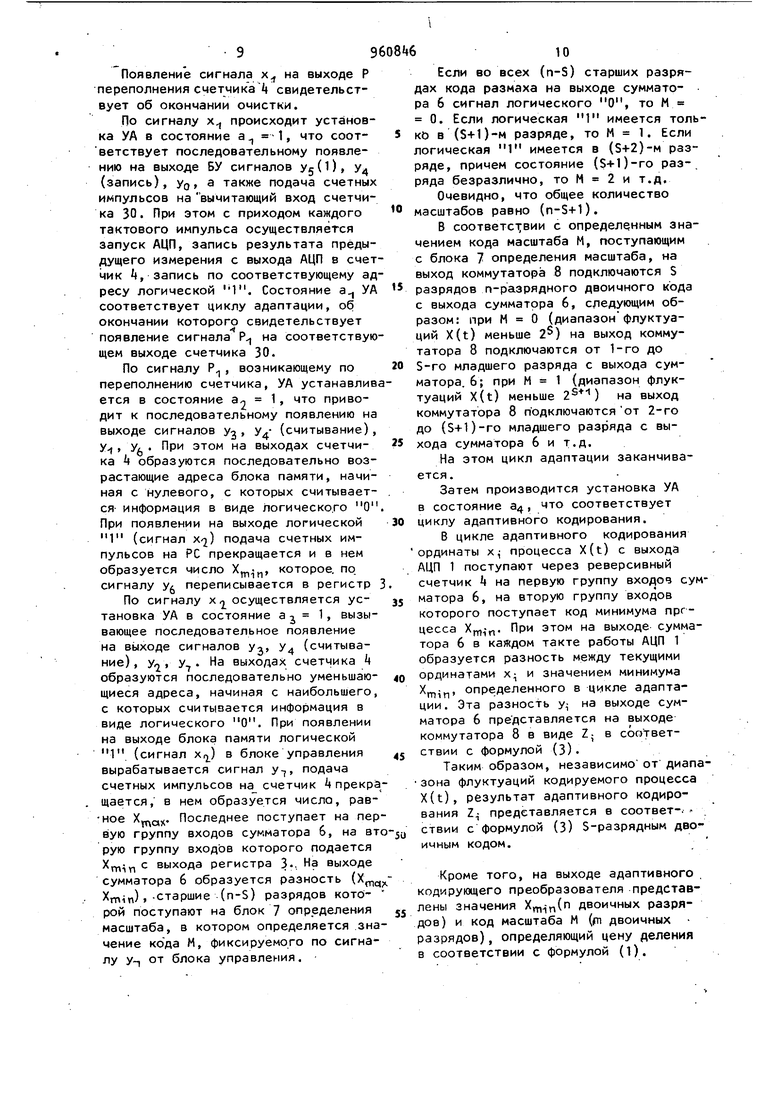

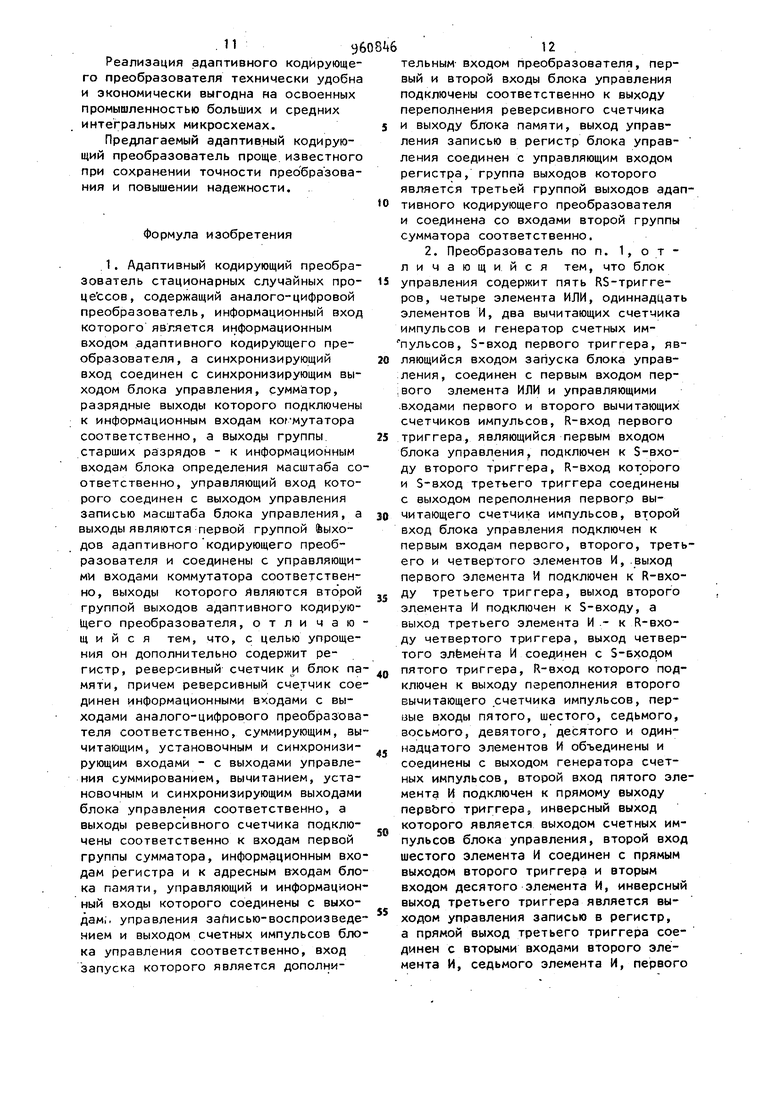

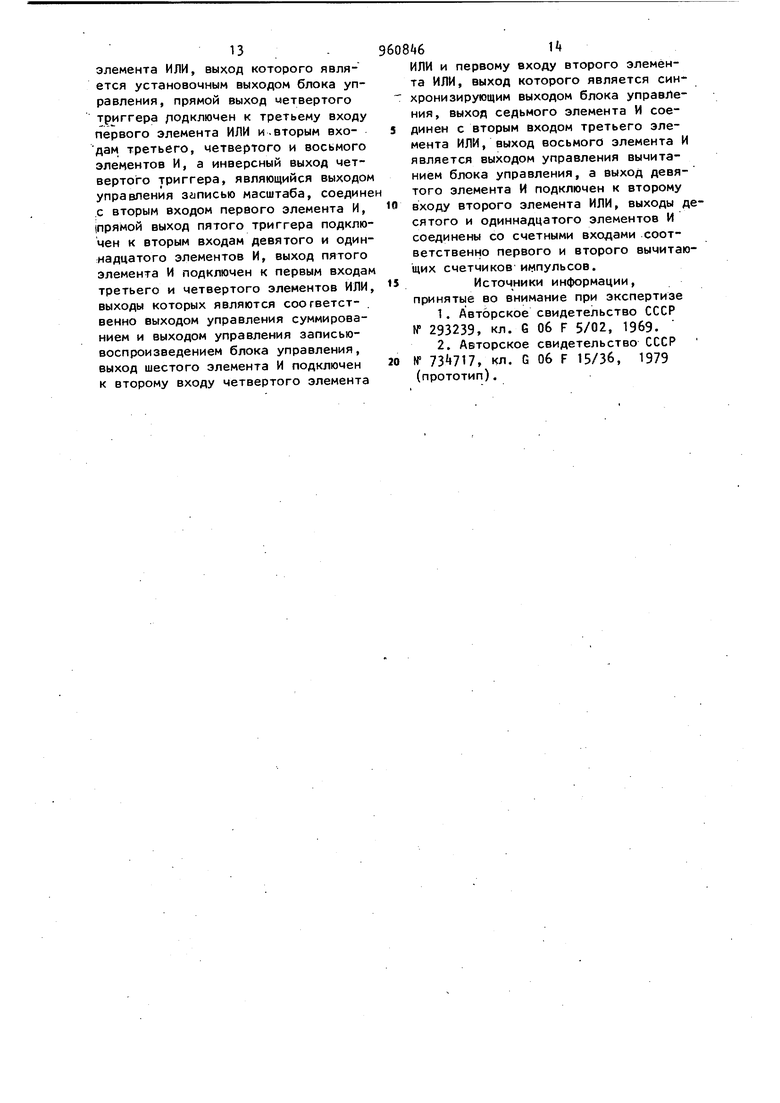

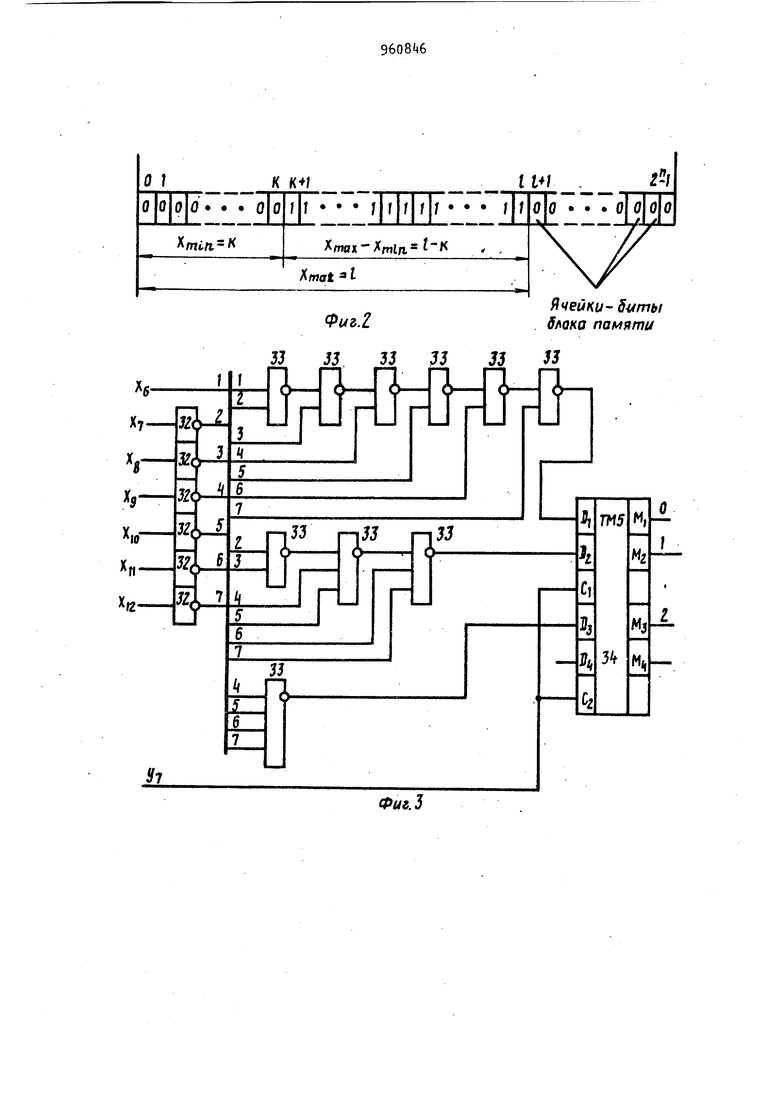

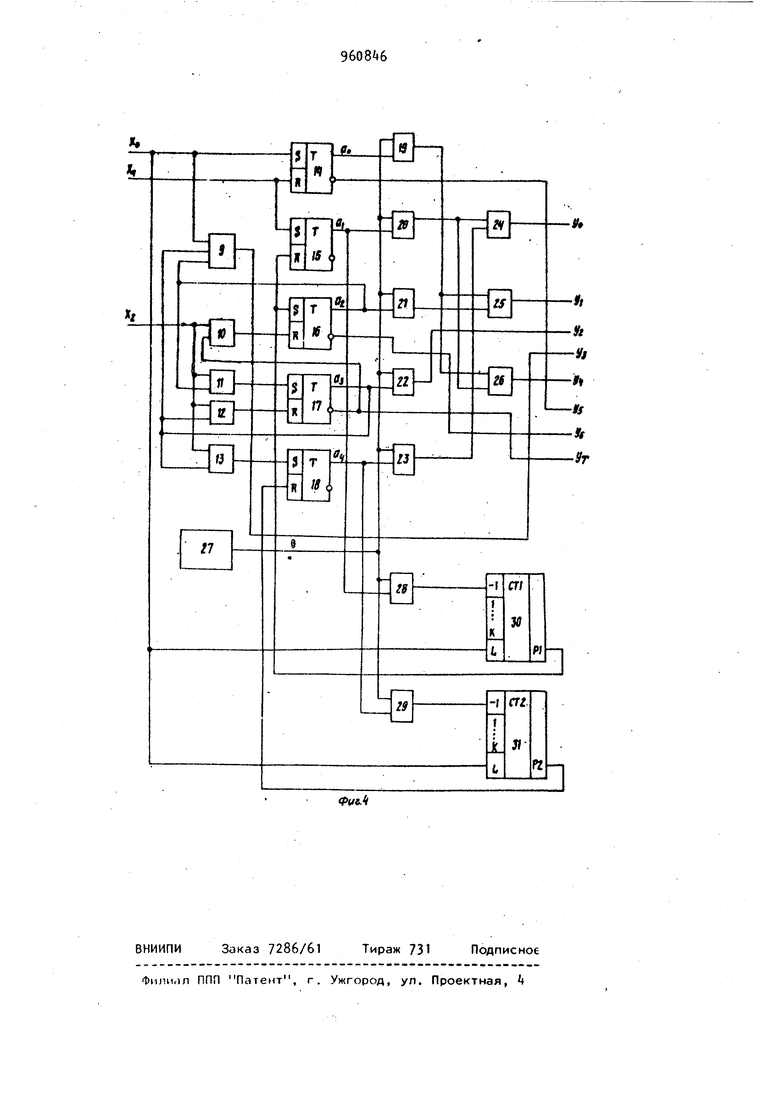

Недостатком известного устройства является его аппаратурная сложность из-за использования блоков статистической оценки максимума и минимума, каждый из которых состоит из п-раз20рядных регистра памяти и цифрового . устройства сравнения, а также коммутатора двух п-разрядных потоков информации. 3S6o Целью изобретения является упрощение устройства. Указанная цель достигается тем, что в адаптивный кодирующий преобразователь, содержащий аналого-цифровой преобразователь, информационный вход которого является информационным входом адаптивного кодирующего преобразователя, а синхронизирующий вход соединен с синхронизирующим выходом блока управления, сумматор, разрядные выходы которого подключены к информационным входам коммутатора соответств-енно, а выходы, групп старших .разрядов - к информационным входам блока.определения масштаба соответст:Венно, управляющий .вход которого соединен с выходом управления записью масштаба блока управления, а выходы являются первой группой выходов адаптивного кодирующего преобразователя и соединены с управляющими входами коммутатора соответственно выходы которого являются второй группой выходов адаптивного кодирующего преобразователя, введены регистр, реверсивный счетчик и блок памяти, причем реверсивный счетчик соединен своими информационными входами с вь1ходами аналого-цифрового преобразователя со ответственно-, суммирующим, вычитающи установочным и синхронизирующим входами - с выходами управления суммиро ванием, вычитанием, установочным и синхронизирующим выходами блока управления соответственно, а выходы реверсивного счетчика подключены соответственно к входам первой группы сумматора, информационным ,входам регистра и к адресным входам блока памяти, управляющий и информационный входы которого соединены с выходом управления записью-воспроизведением и выходом счетных импульсов блока управления соответственно, вход запуска которого является дополнительным входом преобразователя, первый и второй входы блока управления подключены соответственно к выходу переполнения реверсивного счетчика и выходу блока памяти, выход управления записью в регистр блока управления соединен с управляющим входом .регистра, группа выходов которого яв ляется третьей группой выходов адап. тивного кодирующего преобразователя и соединена со входами второй группы сумматора соответственно. Кроме того, блок управления содержит пять RS-триггеров, четыре элемента ИЛИ, одиннадцать элементов И, два вычитающих счетчика импульсов и генератор счетных импульсов, S-вход первого триггера, являющийся входом запуска блока управления, соединен с первым .входом первого элемента ИЛИ и управляющими входами первого и второговычитающих счетчиков импульсов, R-вход первого триггера, являющийся первым входом блока управления, подключен к S-входу второго триггера, R-вход которого и S-вход третьего триггера соединены с выходом переполнения первого вычитающего счетчика импульсов, второй вход блока управления подключен к первым входам первого, второго, третьего и четвертого элементов И, выход первого элемента И соединен c.R-входом третьего триггера, выход второго элемента И подключен к 5 входу, а выход третьего элемента И - к R-входу четвертого триггера. выход четвертого элемента И соединен с S-входом пятого триггера, R-вход которого подключен к выходу переполнения второго.вычитающего счетчика импульсов, первые .входы пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого элементовИ объединены и соединены с выходом генератора счетных импульсов, второй вход пятого элемента И подключен к прямому выходу первого триггера, инверсный выход которого является выходом счетных импульсов блока управления, второй вход шестого элемента И соединен с прямым выходом второго триггера и вторым входом десятого элемента И, инверсный выход третьего триггера является вы.ходом управления записью в регистр,а прямой выход третьего триггера соединен с вторыми входами второго элемента И, седьмого элемента И и первого элемента ИЛИ, выход которого является установочным выходом блока управления, прямой выход четвертого триггера подключен третьему входу первого элемента ИЛИ и вторым входам третьего, четвертого и восьмого элементов И, а инверсный выход четвертого триггера, являющийся выходом управления записью масштаба, соединен с вторым входом первого элемента И, прямой выход пятого триггера подключен к вторым входам девятого и одиннадцатого элементов И, выход пятого элемента И подключен к 59 первым входам третьего и четвертого элементов ИЛИ, выходы которых являют ся соответственно выходом управления суммированием и выходом управления записью-воспроизведением блока управ ления, выход шестого элемента И подключен к второму входу четвертого элемента ИЛИ и к первому входу второ го элемента ИЛИ, выход которого явля ется синхронизирующим выходом блока управления, выход седьмого элемента соединен с вторым входом третьего элемента ИЛИ, выход восьмого элемента И является выходом управления вычитанием блока управления, а выход девятого элемента И подключен к второму входу второго элемента ИЛИ, выходы десятого и одиннадцатого элементов И соединены со счетными входами соответственно первого и второго вычитающих счетчиков импульсов. На фиг. 1 показана структурная схема адаптивного кодирующего преобразователя; на фиг. 2 - структура числа, записанного в блоке памяти; на фиг. 3 структурная схеяа блока определения масштаба; на фиг. i то же, блока управления. Преобразователь содержит аналогоцифровой преобразователь (АЦП) 1,блок 2 управления, регистр 3, реверсивный счетчик «, блок 5 памяти, сум матор 6, блок 7 определения масштаба и коммутатор 8. Блок 2 управления содержит элемент ИЛИ 9 элементы И 10-13, RS-три геры , элементы И 19-23, элемен ты ИЛИ , генератор 27 счетных импульсов, элементы И 28 и 29 вычитающие счетчики 30 и 31 Блок 7 определения масштаба содержит формирователи 32, элементы И 33 и запоминающий регистр З Блок 2 управления строится на основе синхронного управляющего автомата (УА) с жесткой логикой, закон функционирования которого определяется необходимыми для кокретного устройства временными соотношениями между последовательностями входных и выходных сигналов. В вычитающие счетчики 30 и 31 предварительно устанавливается код. Множества X, В, С являются множествами входных сигналов, где X XQ, х, XQ J - множество входных сигналов УЯ, х - сигнал запуска; х - сигнал конца очистки блока памяти (БП); х - сигнал определения знамений Xmin Х ах46В Ь,...,Ь, - код числа выборок в цикле адаптации, определяющий его длительность. С CT,.,.,C - код числа выборок в цикле адаптивного кодирования (измерения ЦИ), определяющий его длительность. Множества В и С задаются набором кода и записываются в счетчики сигналом Хд. Множество А ад,.,,,а4 - множество состояний УА, определяющее по следовательность работы преобразователя, где а - очистка БП; а-, - цикл адаптации; а-,- определение а определение размаха и масштаба М; а - цикл адаптивного кодирования. Множество У УО, У. множество выходных сигналов УА, управляющих работой преобразователя; где уд - тактирование АЦП, запись параллельного кода с выхода АЦП в реверсивный счетчик (РС); у - подача счетных импульсов на суммирующий вход счетчика 4; у, - подача счетных импульсов на вычитающий вход счетчика k; у, - установка в О счетчика 4; у установка блока 5 памяти в режим запись (считывание); у подача логических О и 1 на вход блока 5 памяти; у - запись значения X в регистр 3; У-| запись значения М в блок 7 определения масштаба. На вход блока 7 определения масштаба подаются (n-S) старших разрядов с выхода сумматора 6. При образовании на выходе сумматора 6 кода раз-, маха, он преобразуется в значение масштаба М в двоичном коде, которое представляет собой номер старшего разряда, содержащего логическую 1, в группе разрядов на выходе сумматора соответственно от (S+l)-ro до п-го. Код масштаба М по сигналу с блока 2 управления запоминается в РП и в течение цикла адаптивного кодирования действует на управляющий вход коммутатора 8. Число выходов КЧ, и соответственно разрядов РП определяется выражением m log-(n-S+1), где (n-S+l) - общее количество масштабов. Схема 7 определения масштаба соответствует значениям ri 12, S 5, m 3. Процесс адаптивного кодирования состоит из двух циклов: цикла адаптации (длительностью Т) и цикла адаптивного кодирования или измерения (длительностью Т). Стационарный случайный процесс, представляется на выходе АЦП п-разрядным двоичйым кодом. В цикле адаптации число одноразрядных ячеек блока памяти равно числу градаций (уровней квантования) АЦП. Во всех ячейках блока памяти предварительно записан логический О При кодировании каждого значения случайного процесса в соответствующу ячейку блока памяти записывается логическая 1. При повторении кода на выходе АЦП логическая 1 в данной подтверждается. После окончания цикла адаптации в ячейках блока памяти оказывается записанной последовательность вида 00.... 011.... 1100.... 00 (фиг. 2), где номер бита данной последовательности соответствует адресу ячейки блока, памяти, которая характеризует минимальное и максимальное значения случайного процесса, также диапазон его изменения. Определение максимального и минимального значений случайного процес са производится в режиме считывания информации, записанной в блоке памяти. При считывании информации из ячеек с последовательно возрастающими адресами, начиная .с нулевого, производится подсчет числа ячеек памяти, содержащих логические О (ячейки с адресами О - К на фиг . 2). При появлении на выходе блока памяти первой логической 1 подсчет прекращается , а полученное число представляет собой значение минимума случайного процесса.„ Значение максимума случайного про цесса определяется аналогично при считывании информации из ячеек с последовательно убывающими адресами, начиная с наибольшего, также до появления на выходе блока памяти первой логической 1. Подсчитанное при этом число ячеек блока памяти, содер жащих логические О (ячейки с адресами (Р+1) - () на фиг.2), представляет собой значение максимума случайного процесса . Полученные значения Х позволяют определить диапазон флуктуации случайного процесса (размах) как разность -Х,у,), а также код мае значений (X picnT minb а .штаба М (т двоичных разрядов) цены деления. В зависимости от величины кода масштаба М осуществляется перестройка схемы таким образом, что к выходу адаптивного кодирующего преобразователя подключаютсяS разрядов (где ) из п-разрядного представления величины размаха, начиная со старшего значащего разряда. Это приводит к изменению цены деления лХ адаптивного кодирующего преобразователя при постоянной разрядности представления результата адаптивного кодироаания. Величина цены деления дХ связана с масштабом М соотношением ДХ 2.,(1) В цикле адаптивного кодирования (измерения) производится аналого-цифровое преобразование входного сигнала X(t) и из полученного кода (п разрядов) каждой ординаты х вычитается значение (п разрядов), определенное в цикле адаптации. При этом получаются значения ординат нового смещенного случайного процесса y(t) У X, - X Полученные ординаты представляютсяна выходе адаптивного кодирующего преобразователя S разрядным двоичным кодом с ценой деления, соответствующей определенному в цикле адаптации масштабу М. Число разрядов S выбирается в соответствии с требуемой,точностью измерения. В результате адаптивного кодирования на выходе преобразователя образуется массив значений выборок стационарного случайного процесса Z(t), определяемых следующим образом % i - ,.. i , Очевидно, что восстановить исходный случайный процесс можно в соответствии с выражением ,По сигналу Пуск осуществляется запись кодов в счетчики 30 и 31 и установка УА в состояние а 1(а О, a,j j 0),что соответствует последовательному появлению на выходе сигналов у, У(0), у (запись), у. При этом на выходах разрядов реверсивного счетчика k (его емкость равна количеству ячеек блока памяти) образуются коды адресов, начиная с нулевого-и выше, по которым в соответствующие ячейки БП осуществляется запись логического О, т.е.. производится очистка бло ка памяти.

Появление сигнала х., на выходе Р переполнения счетчикаЧ свидетельствует об окончании очистки.

По сигналу х происходит установка УА в состояние а -1, что соответствует последовательному появлению на выхо/ е БУ сигналов ygCl), у (запись), УО, а также подача счетных импульсов на вычитающий вход счетчика 30. При этом с приходом каждого тактового импульса осуществляется запуск АЦП, запись результата предыдущего измерения с выхода АЦП в счетчик i, запись по соответствующему адресу логической 1. Состояние а УА соответствует циклу адаптации, об окончании которого свидетельствует появление сигнала Р на соответствующем выходе счетчика 30.

По сигналу Р, возникающему по переполнению счетчика, УА устанавливается в состояние а,, 1 , что приводит к последовательному появлению на выходе сигналов уд, (считывание), у, у/ . При этом на выходах счетчика k образуются последовательно возрастающие адреса блока памяти, начиная с нулевого, с которых считывается- информация в виде логического О При появлении на выходе логической 1 (сигнал x-j) подача счетных импульсов на PC прекращается и в нем образуется число Х, которое, по. сигналу у переписывается в регистр 3

По сигналу X осуществляется установка УА в состояние а 1, вызывающее последовательное появление на выходе сигналов у, у (считывание), у,, у . На выходах счетчика Ц образуются последовательно уменьшающиеся адреса, начиная с наибольшего, с которых считывается информация в виде логического О. При появлении на выходе блока памяти логической 1 (сигнал XQ) в блоке управления вырабатывается сигнал у-,, подача счетных импульсов на счетчик k прекращается, в нем образуется число, равное . Последнее поступает на первую группу входов сумматора 6, на вто рую группу входов которого подается Xf с выхода регистра 3., На выходе сумматора 6 образуется разность (Xj jXmin) -старшие (n-S) разрядов кото- рой поступают на блок 7 определения масштаба, в котором определяется значение кода М, фиксируемого по сигналу У-, от блока управления.

Если во всех (n-S) старших разрядах кода размаха на выходе сумматора 6 сигнал логического О, то М 0. Если логическая 1 имеется только в (S+1)-M разряде, то М 1. Если огическая 1 имеется в (5+2)-м разряде, причем состояние (S+O-ro разряда безразлично, то М 2 и т.д.

Очевидно, что общее количество асштабов равно (n-S+1).

В соответст;вии с определенным значением кода масштаба М, поступающим с блока 7 определения масштаба, на выход коммутатора 8 подключаются S разрядов п-разрядного двоичного кода с выхода сумматора 6, следующим образом: при М О (диапазон флуктуации X(t) меньше 2) на выход коммутатора В подключаются от 1-го до S-го младшего разряда с выхода сумматора. 6; при М 1 (диапазон флуктуации X(t) меньше ) на выход коммутатора В подключаютсяот 2-го до (S+1)-ro младшего разряда с выхода сумматора 6 и т.д.

На этом цикл адаптации заканчивается.

Затем производится установка УА в состояние а4, что соответствует циклу адаптивного кодирования.

В цикле адаптивного кодирования ординаты х процесса X(t) с выхода АЦП 1 поступают через реверсивный счетчик на первую группу входоч сумматора 6, на вторую группу входов которого поступает код минимума пргцесса . При этом на выходе сумматора 6 в каждом такте работы АЦП 1 образуется разность между текущими ординатами xj; и значением минимума определенного в цикле адаптации. Эта разность у на выходе сумматора 6 представляется на выходе коммутатора 8 в виде Z- в соответствии с формулой (3).

Таким образом, независимо от диапазона флуктуации кодируемого процесса X(t), результат адаптивного кодирования Z представляется в соответ-. ствии с формулой (3) S-разрядным двоичным кодом.

Кроме того, на выходе адаптивного одирующего преобразователя представены значения Хт.„(п двоичных разряов) и код масштаба М (п двоичных азрядов), определяющий цену деления соответствии с формулой (1). Реализация адаптивного кодирующего преобразователя технически удобна и экономически выгодна на освоенных промышленностью больших и средних интегральных микросхемах. Предлагаемый адаптивный кодирующий преобразователь проще, известного при сохранении точности преобразования и повышении надежности. Формула изобретения .1. Адаптивный кодирующий преобразователь стационарных случайных процессов, содержащий аналого-цифровой преобразователь, информационный вход которого является информационным входом адаптивного кодирующего преобразователя, а синхронизирующий вход соединен с синхронизирующим выходом блока управления, сумматор, разрядные выходы которого подключены к информационным входам когмутатора соответственно, а выходы группы, старших разрядов - к информационным входам блока определения масштаба со ответственно, управляющий вход которого соединен с выходом управления записью масштаба блока управления, а выходы являются первой группой выходов адаптивного кодирующего преобразователя и соединены с управляющими входами коммутатора соответственно, выходы которого Являются втброй группой выходов адаптивного кодирующего преобразователя, отличаю щийся тем, что, с целью упрощения он дополнительно содержит регистр, реверсивный счетчик и блок па мяти, причем реверсивный счетчик сое динен информационными входами с выходами аналого-цифрового преобразова теля соответственно, суммирующим, вы читающим, установочным и синхронизирующим входами - с выходами управления суммированием, вычитанием, установочным и синхронизирующим выходами блока управления соответственно, а выходы реверсивного счетчика подключены соответственно к входам первой группы сумматора, информационным вхо дам регистра и к адресным входам бло ка памяти, управляющий и информацион ный входы которого соединены с выходам,, управления заПисью-воспроизведе нием и выходом счетных импульсов бло ка управления соответственно, вход запуска которого является дополниЗбтельным- входом преобразователя, первый и второй входы блока управления подключены соответственно к выходу переполнения реверсивного счетчика и выходу блока памяти, выход управления записью в регистр блока управления соединен с управляющим входом регистра, группа выходов которого является третьей группой выходов адаптивного кодирующего преобразователя и соединена со входами второй группы сумматора соответственно. 2. Преобразователь по п. 1, о т личающийся тем, что блок управления содержит пять RS-триггеров, четыре элемента ИЛИ, одиннадцать элементов И, два вычитающих счетчика импульсов и генератор счетных импульсов, S-вход первого триггера, являющийся входом запуска блока управления, соединен с первым входом первого элемента ИЛИ и управляющими .входами первого и второго вычитающих счетчиков импульсов, R-вход первого триггера, являющийся первым входом блока управления, подключен к S-входу второго триггера, R-вход которого и S-вход третьего триггера соединены с выходом переполнения первого вычитающего счетчика импульсов, второй вход блока управления подключен к первым входам первого, второго, третьего и четвертого элементов И, .выход первого элемента И подключен к R-BXOду третьего триггера, выход второго элемента И подключен к S-входу, а выход третьего элемента И .- к R-входу четвертого триггера, выход четвертого элемента И соединен с S-Бходрм пятого триггера, R-вход которого подключен к выходу переполнения второго вычитающего счетчика импульсов, первые входы пятого, шестого, седьмого, восьмого, девятого, десятого и одиннадцатого элементов И объединены и соединены с выходом генератора счетных импульсов, второй вход пятого элемента И подключен к прямому выходу первЬго триггера, инверсный выход которого является выходом счетных импульсов блока управления, второй вход шестого элемента И соединен с прямым выходом второго триггера и вторым входом десятого элемента И, инверсный выход третьего триггера является выходом управления записью в регистр, а прямой выход третьего триггера соединен с вторыми входами второго элемента И, седьмого элемента И, первого элемента ИЛИ, выход которого является установочным выходом блока управления, прямой выход четвертого триггера родхлючен к третьему входу первого элемента ИЛИ и.вторым входам третьего, четвертого и восьмого элементов И, а инверсный выход четвертого триггера, являющийся выходом управления згJПИcью масштаба, соедине с вторым входом первого элемента И, (Прямой выход пятого триггера подключен к вторым входам девятого и одиннадцатого элементов И, выход пятого элемента И подключен к первым входам третьего и четвертого элементов ИЛИ выходы которых являются соогветст- . венно выходом управления суммированием и выходом управления записьювоспроизведением блока управления, выход шестого элемента И подключен к второму входу четвертого элемента ИЛИ и первому входу второго элемента ИЛИ, выход которого является синхронизирующим выходом блока управления, выход седьмого элемента И соединен с вторым входом третьего элемента ИЛИ, выход восьмого элемента И является выходом управления вычитанием блока управления, а выход девятого элемента И подключен к второму входу второго элемента ИЛИ, выходы десятого и одиннадцатого элементов И соединены со счетными входами соответственно первого и второго вычитающих счетчиков импульсов. Источники информации, принять1е во внимание при экспертизе 1.Авторское свидетельство СССР № 293239, кл. е 06 F 5/02, 1969. 2.Авторское свидетельство СССР № , кл. G 06 F 15/36, 1979 (прототип).

иэ

A

м ,в; - Kil «eS:

«4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного кодированияСТАциОНАРНыХ СлучАйНыХ пРОцЕССОВ | 1979 |

|

SU822199A1 |

| Кодер телевизионного сигнала | 1990 |

|

SU1753596A2 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство кодирования сигналов цветного телевидения | 1978 |

|

SU745018A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Устройство для испытаний датчиков давления | 1983 |

|

SU1129624A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| УСТРОЙСТВО АДАПТИВНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ | 2000 |

|

RU2169431C1 |

- «Ч «s

a, r,

f « ffl VJ

.- «vj «i

.-ЖЫГ. L

- «s, E

. .1 « tag

Ij

S

Ml «e

ff

«v4

la

(..I U..I II

Ячейки- Si/imbi SfiOKO памяти

Фиг.З

Авторы

Даты

1982-09-23—Публикация

1980-07-24—Подача