Изобретение относится к медицинской технике и может найти применение при исследованиях в области психологии и физиологии в клиниках различного профиля при автоматизированной оценке функционального состояния человека.

Цель изобретения - расширение функциональных возможностей устройства.

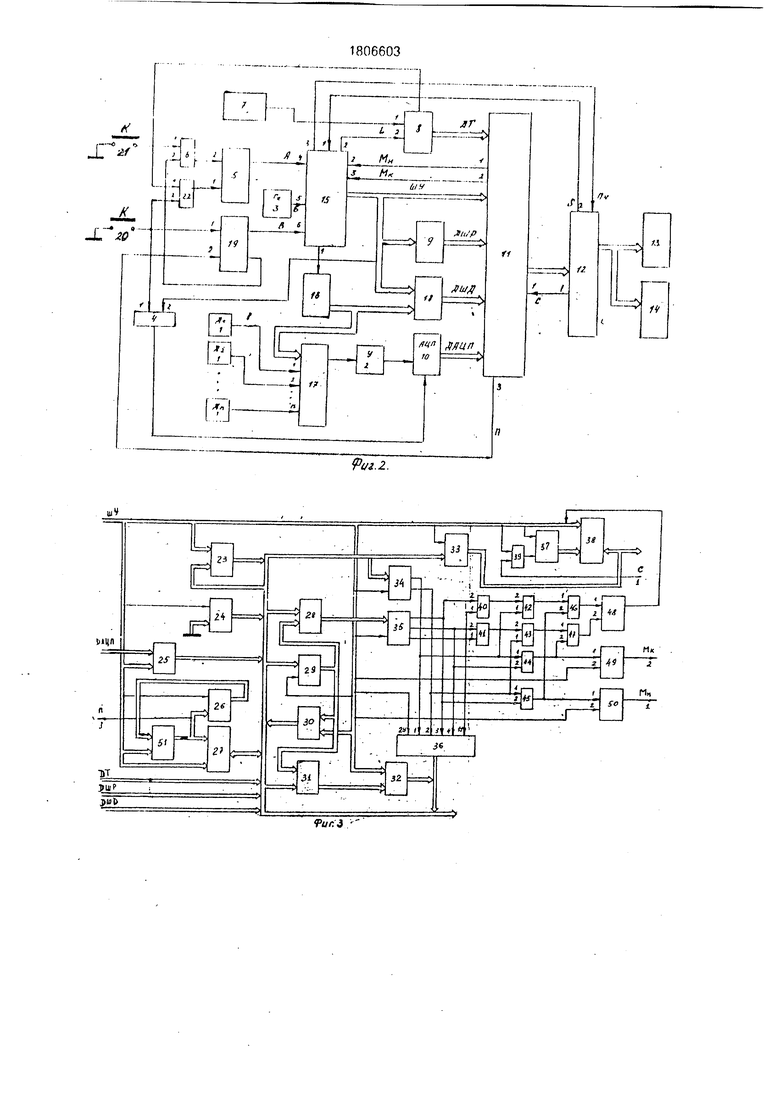

Поставленная цель достигается тем, что в многоканальный анализатор электрофизиологических сигналов, содержащий последовательно соединенные пульт 7, таймер 8, схему ИЛИ 22 и триггер 5, кнопку 20, подключенную ко вторым входам схем ИЛИ 22, Ам первому входу триггера 19, кнопку 21, соединенную с первым входом схемы И 6, а также генератор импульсов 3, датчик 1, усилитель 2, АЦП 10, шифратор 9 номера разложения, блок 11 выделения переключений, вычислитель 12, графический 13 и цифровой 14 регистраторы, дополнительно введены п

датчиков 1, аналоговый коммутатор 17, распределитель 15 импульсов, счетчик 16, шифратор 18 номера датчика, причем выходы датчиков 1 прдключены к информационным входам аналогового коммутатора 17, выход которого через усилитель 2 соединен с информационным входом АЦП 10, выходами подключенного к информационным входам блока 11, к шине данных которого подключены выходы шифраторов 9 и 18, таймера 8 и информационные входы вычислителя 12, импульсные выходы которого соединены соответственно с первыми входами блока 11 и распределителя 15 импульсов, второй и третий входы которого подключены к первому и второму выходам блока 11 выделения переключений, а четвертый, пятый и шестой входы соединены соответственно с выходами триггера 5, генератора 3 и первым выходом триггера 19, второй выход которого подключен ко второму входу схемы И 6, со00

о

Ov

о о

GJ

единенную выходом со вторым входом триггера 5, первый выход распределителя 15 импульсов подключен к входу счетчика 16, второй выход - ко второму входу таймера 8, а третий - к входу управления вычисилтеля 12, соединенного информационными выходами с графическим 13 и цифровым 14 регистраторами, остальные выходы распределителя импульсов 15, объединенные в шину управления, подключены к входам управления блока 11 выделения переключений, шифраторов 9,10 и первому вход схемы ИЛИ 4, соединенную выходом с входом управления АЦП, третий выход блока выделения переключений И соединен со вторым входом триггера 19, выходы счетчика 16 подключены к входам управления аналогового коммутатора 17 и к информационным входам шифратора 18 номера датчика.

Блок выделения переключений содержит два счетчика 51,37 и регистр адреса 26, память 27 и буферную память 38, два шинных коммутатора 24, 33 и коммутатор 36, шесть регистров 25,29,30,32,34, 35 и счетчик-регистр 23, сумматор 31 и схему сравнения 28, пять схем ИЛИ 39, 40, 41, 46, 47 и четыре схемы И 42, 45, три триггера 48-50, причем к шине данных блока подключены выходы первого регистра 25, информационными входами соединенного с выходами АЦП 10, третьего и четвертого регистров 30, 32 и первого шинного коммутатора 24, с заземленными информационными входами счетчика-регистратора 23, коммутатора 36, памяти 27 и информационными входами второго и пятого регистров 29,34, счетчика- регистра 23, схемы сравнения 28, сумматора 31 и второго шинного коммутатора 33, выходы которого соединены с информационными выходами буферной памяти 38, подключенной адресными входами к выходам второго счетчика адреса 37, а выход первого счетчика адреса 51 соединен с адресными входами памяти 27 и информационными входами регистра адреса 26, подключенного выходами к информационным входам первого счетчика адреса 51, выходы второго регистра 29 соеднены с информационными входами третьего регистра 30 и вторыми входами сумматора 31 и сехмы сравнения 28, выходы которых соответственно подключены к информационным входам четвертого и шестого регистров 32 и 35, первый выход пятого регистра 34 соединен с первыми входами первой и третьей схем И 42, 44 и коммутатора 36, а второй выход- с первыми входами второй и четвертой схем И 43, 45 и вторым входом коммутатора 36, первый выход шестого регистра 35, подключен ко

вторым входам второй схемы ИЛИ 40, четвертой схемы И 45 и третьим входом коммутатора 36, а второй выход - ко вторым входам третьей схемы ИЛИ 41, третьей схе- мы И 44 и четвертым входом коммутатора 36, первый вход управления которого соединен с третьим выходом шестого регистра 35 и первыми входами второй и третьей схем ИЛИ 40, 41 подключенных выходами соот

ветственно ко вторым входам первой и второй схем И 42, 43, выходы которых соединены с первыми входами четвертой и пятой схем ИЛИ 46, 47, выходами подключенных соответственно с первым и вторым 5 входами первого триггера 42, выход третьей схемы И 44 соединен со вторым входом пятой схемы ИЛИ 47 и первым входом второго триггера 49, а выход четвертой схемы И 45

- со вторым входом четвертой схемы ИЛИ

0 46 и первым входом триггера 50, шина управления блока подключена к управляющим входам памяти 27 и буферной памяти 38, первого счетчика 51 и регистра адреса 26, счетчика-регистра 23 и шести регистров 25,

5 29,30, 32, 34, 35, первого и второго шинных коммутаторов 24, 33, ко второму входу управления коммутатора 36 и второго счетчи- Р ка адреса 37, первым входом управления, соединенного с выходом первой схемы ИЛИ

0 39, а также ко вторым входам второго и третьего триггеров 49, 50, выходу первого триггера 48, второму входу первой схемы ИЛИ 39, первый вход которой подключен к входу блока 11, выходы которого соединены

5 с выходами триггеров 49, 50 и последним выходом счетчика адреса 51.

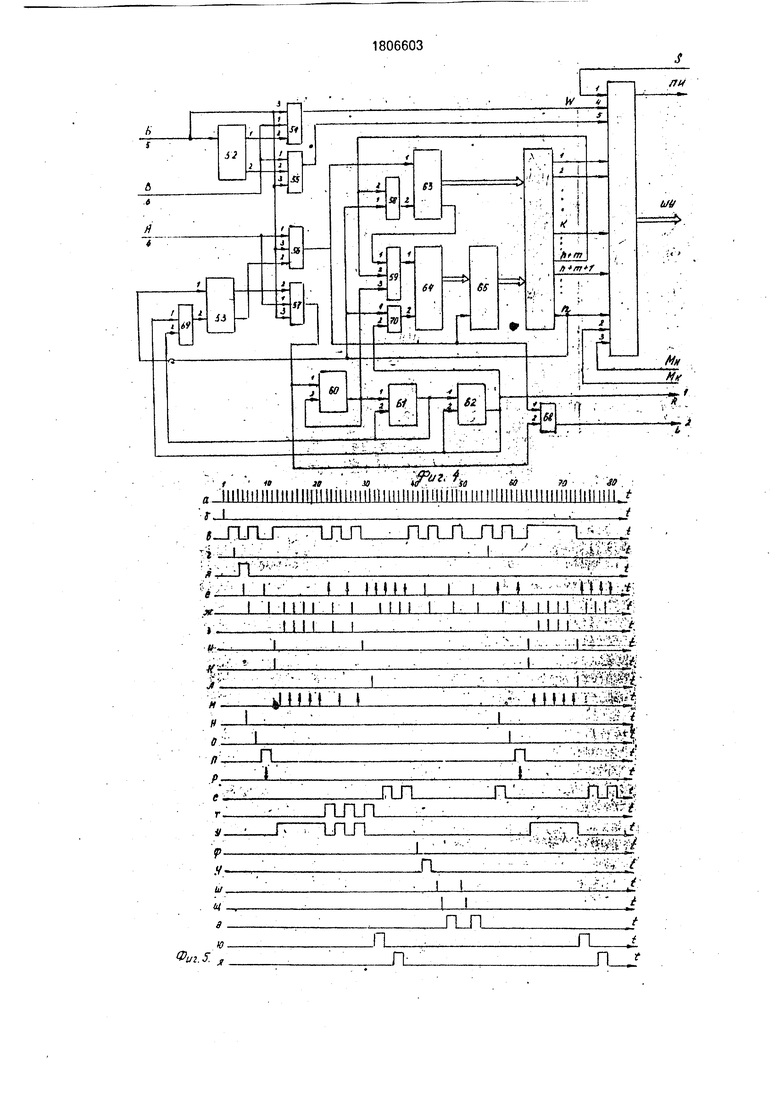

Распределитель импульсов содержит два триггера 52, 53, пять схем ИЛИ 58, 59, 68, 69, 70, четыре схемы И 54-57, четыре

0 счетчика 60-63, счетчик-дешифратор 64, блок дешифраторов 66, сборку схем И 65, блок комбинационных схем 67, причем первый, второй и третий входы распределителя подключены соответствующим входам бло5 ка комбинационных схем 67, четвертый вход

- к первым входам третьей и четвертой схем И 56, 57, шестой - к первым входам первой и второй схем И 54, 55, пятый - ко вторым входам четырех схем И 54-57 и первому

0 входу первого триггера 52, первым и вторым выходами соответственно подключенного к третьим входам первой и второй схем И 54, 55, выходы которых соединены с четвертым и пятым входами блока комбинационных

5 схем 67, выход третьей схемы И 56 подключен к первым входам четвертой схемы ИЛИ 68, сборки схем И 65 и четвертого счетчика

- 63, выходы которого подключены к информационным входам дешифраторов блока 66, а выход переполнения чветвертого счетчика

63 - к первому входу второй схемы ИЛИ 59, подсоединенной выходом к первому входу счетчика-дешифратора 64, выходы которого подключены соответственно ко вторым входам схем И сборки 65, соединенной выходами с входами управления соответствующих дешифраторов блока 66, выходы которого от первого до n-го и с (n + m + 1) до п-го подключены к входам блока комбинационных схем 67,n-й выход блока дешифраторов 66, кроме того, подключен к первым входам второго триггера 53, первой и третьей схем ИЛИ 58, 70, соединенных выходами со вторыми входами четвертого счетчика 63 и счетчика дешифратора 64, а (п + т)-й выход блока дешифраторов 66 подключен ко вторым входам первой и второй схем ИЛИ 58, 59, выходы второго триггера 53 соединены соответственно стретьими входами.третьей и четвертой схем И 56, 57, выход четвертой схемы И 57 подключен ко второму в ходу четвертой схемы ИЛИ 68, первому входу превого счетчика 60, выход которого соединен со вторым входом первого счетчика 60, третьим входом второй схемы ИЛИ 59 и первым входом второго счетчика 61, под ключейного выходом ко второму входу второго счетчика 61, первым входам пятой схемы ИЛ И 69 и третьего счетчика 62, выходы которого соединены со вторыми входами третьего счетчика 62, третьей и пятой схем ИЛИ 70, 69 и первому выходу распределителя, второй выход распределителя подключен к выходу четвертой схемы ИЛИ 68, первый выход блока комбинационных схем 67 соединен с третьим выходом распределителя, а остальные выходы объединены в шину управления.

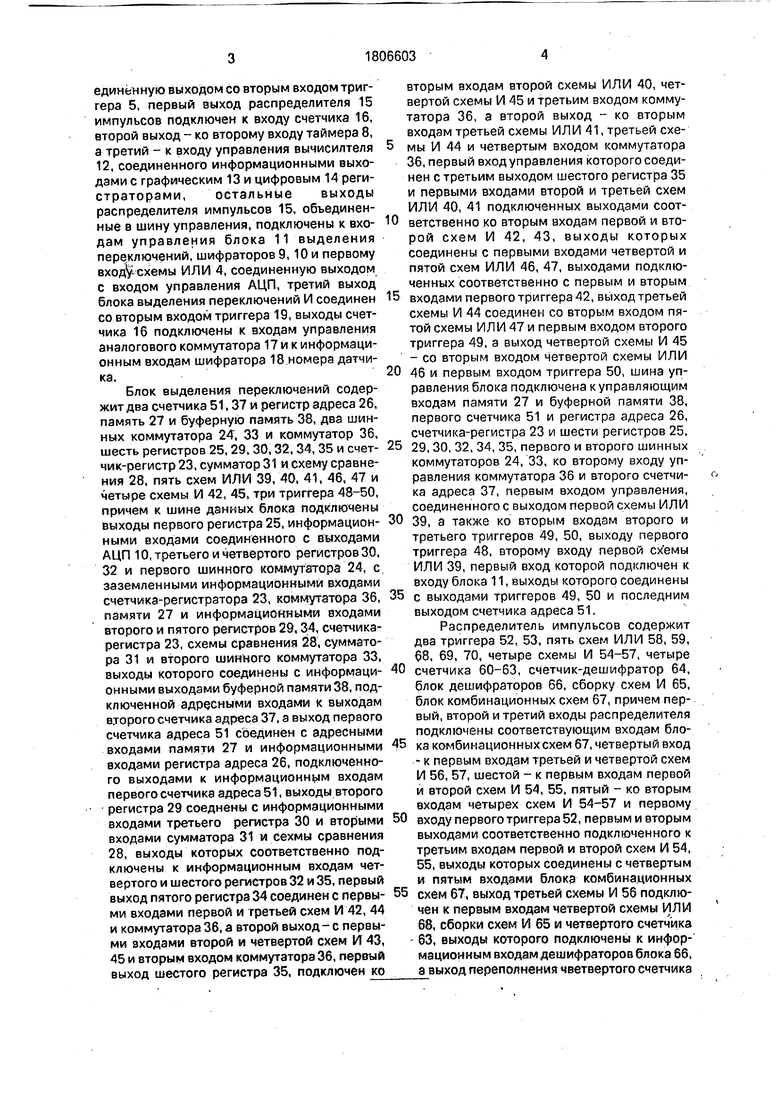

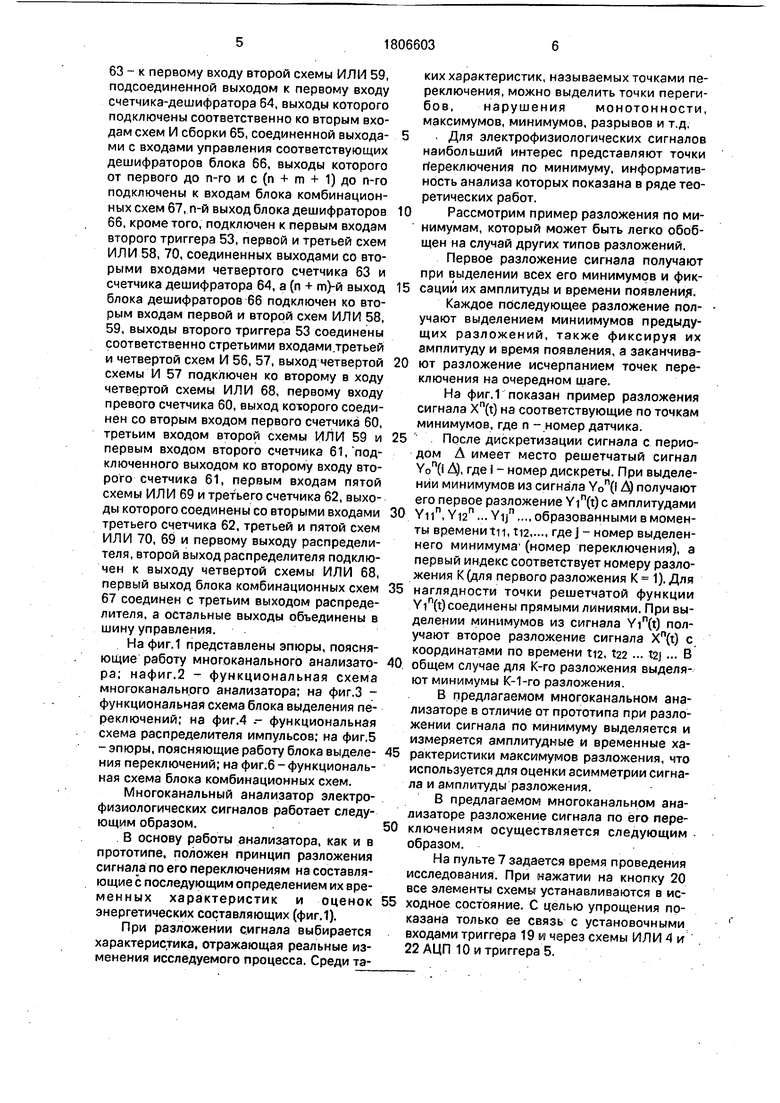

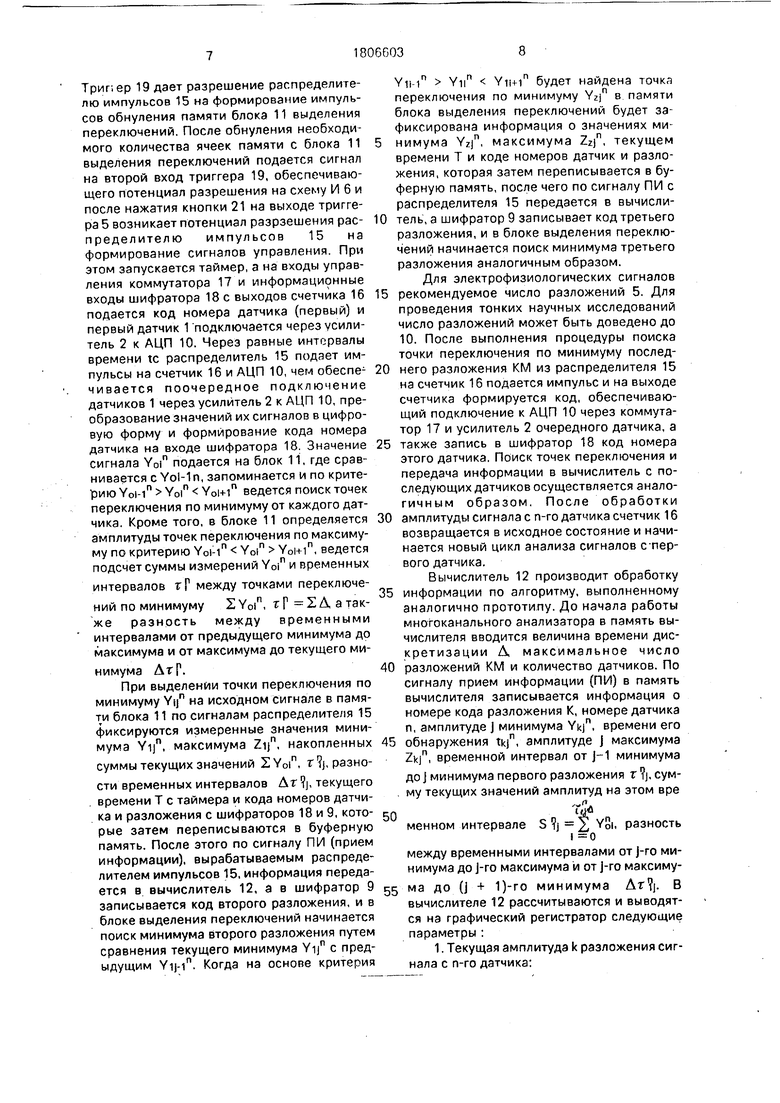

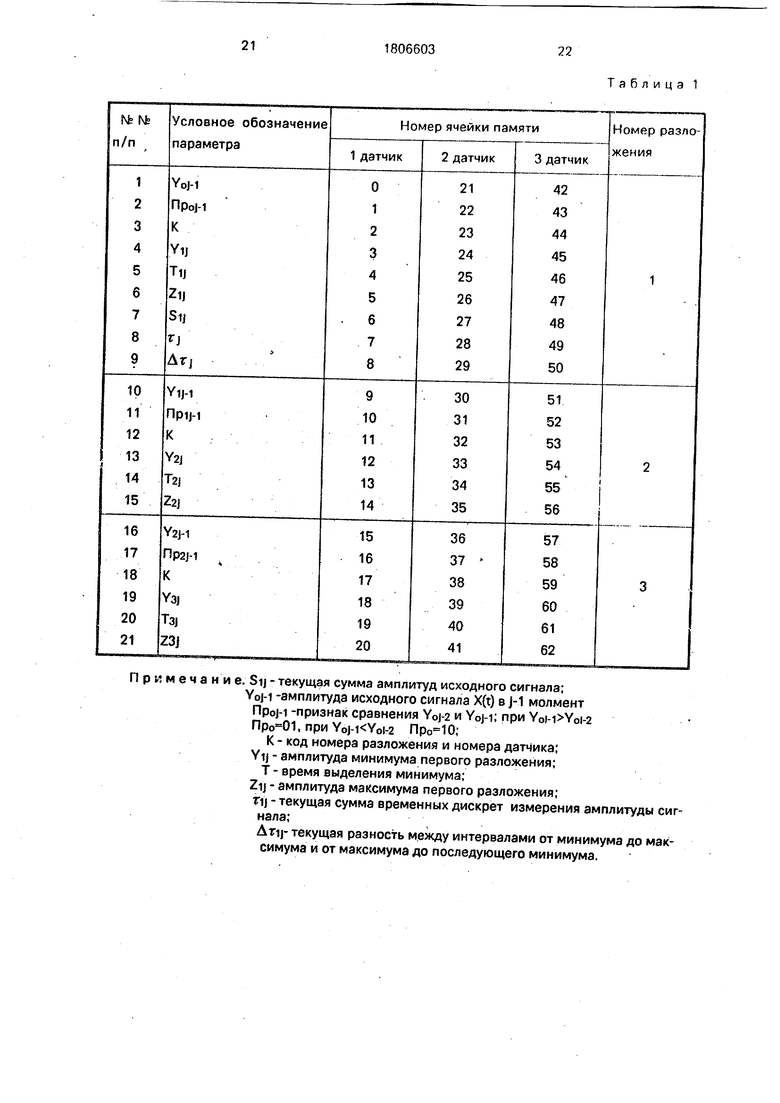

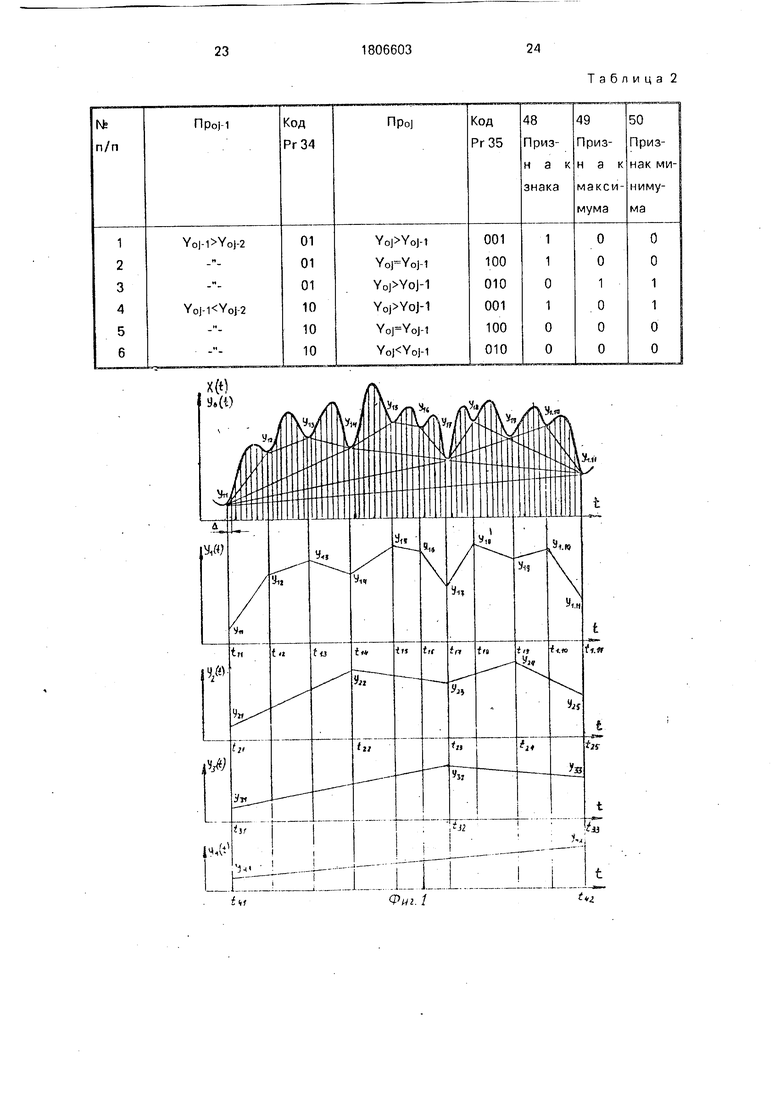

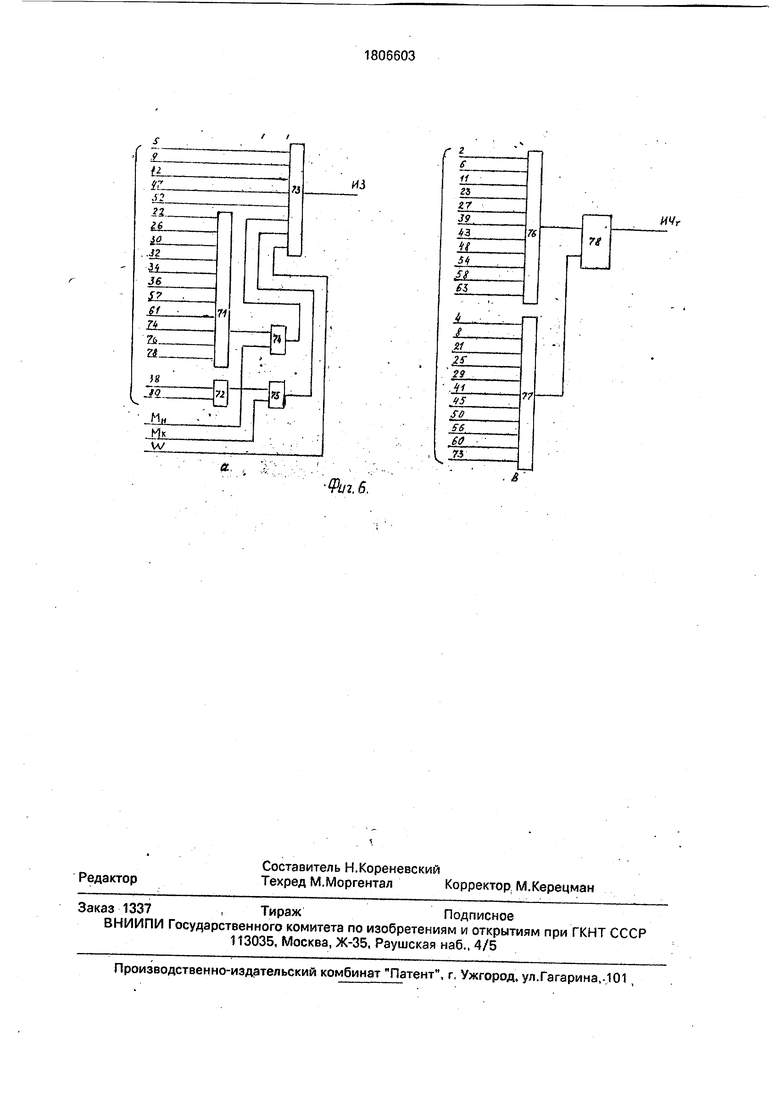

На фиг.1 представлены эпюры, поясняющие работу многоканального анализатора; нафиг.2 - функциональная схема многоканального анализатора; на фиг.З - функциональная схема блока выделения переключений; на фиг.4 - функциональная схема распределителя импульсов; на фиг,5 - эпюры, поясняющие работу блока выделения переключений; на фиг.б- функциональная схема блока комбинационных схем.

Многоканальный анализатор электрофизиологических сигналов работает следующим образом.

В основу работы анализатора, как и в прототипе, положен принцип разложения сигнала по его переключениям на составляющие с последующим определением их вре- менных характеристик и оценок энергетических составляющих (фиг.1).

При разложении сигнала выбирается характеристика, отражающая реальные изменения исследуемого процесса. Среди таких характеристик, называемых точками переключения, можно выделить точки перегибов, нарушения монотонности, максимумов, минимумов, разрывов и т.д. 5 - Для электрофизиологических сигналов наибольший интерес представляют точки переключения по минимуму, информативность анализа которых показана в ряде теоретических работ.

0 Рассмотрим пример разложения по минимумам, который может быть легко обобщен на случай других типов разложений.

Первое разложение сигнала получают при выделении всех его минимумов и фик5 саций их амплитуды и времени появления. Каждое последующее разложение получают выделением миниимумов предыдущих разложений, также фиксируя их амплитуду и время появления, а заканчива0 ют разложение исчерпанием точек переключения на очередном шаге.

На фиг.1 показан пример разложения сигнала Xn(t) на соответствующие по точкам минимумов, где п - номер датчика.

5 После дискретизации сигнала с периодом А имеет место решетчатый сигнал Y0n(i А), где I - номер дискреты. При выделении минимумов из сигнала Yon(f А) получают его первое разложение Yin(t) с амплитудами

0 Ynn, Yi2n... Yijn..., образованными в моменты временитп, ti2,..., где - номер выделен- него минимума1 (номер переключения), а первый индекс соответствует номеру разложения К (для первого разложения К 1). Для

5 наглядности точки решетчатой функции Yin(t) соединены прямыми линиями. При выделении минимумов из сигнала Yin(t) получают второе разложение сигнала Xn(t) с координатами по времени tia, t22 ... t2j... В

0 общем случае для К-ro разложения выделяют минимумы К-1-го разложения.

В предлагаемом многоканальном анализаторе в отличие от прототипа при разложении сигнала по минимуму выделяется и измеряется амплитудные и временные ха5 рактеристики максимумов разложения, что используется для оценки асимметрии сигнала и амплитуды разложения.

В предлагаемом многоканальном анализаторе разложение сигнала по его пере0 ключениям осуществляется следующим - образом.

На пульте 7 задается время проведения исследования. При нажатии на кнопку 20 все элементы схемы устанавливаются в ис5 ходное состояние. С целью упрощения показана только ее связь с установочными входами триггера 19 и через схемы ИЛИ 4 и 22 АЦП 10 и триггера 5.

Трипер 19 дает разрешение распределителю импульсов 15 на формирование импульсов обнуления памяти блока 11 выделения переключений. После обнуления необходимого количества ячеек памяти с блока 11 выделения переключений подается сигнал на второй вход триггера 19, обеспечивающего потенциал разрешения на схему И 6 и после нажатия кнопки 21 на выходе триггера 5 возникает потенциал разрзешения рас- пределителю импульсов 15 на формирование сигналов управления. При этом запускается таймер, а на входы управления коммутатора 17 и информационные входы шифратора 18 с выходов счетчика 16 подается код номера датчика (первый) и первый датчик 1 подключается через усилитель 2 к АЦП 10. Через равные интервалы времени tc распределитель 15 подает импульсы на счетчик 16 и АЦП 10, чем обеспечивается поочередное подключение датчиков 1 через усилитель 2 к АЦП 10, преобразование значений их сигналов в цифровую форму и формирование кода номера датчика на входе шифратора 18. Значение сигнала Y0in подается на блок 11, где сравнивается с Yol-1 п, запоминается и по критерию Y0i-in Y0in Y0i+i ведется поиск точек переключения по минимуму от каждого датчика. Кроме того, в блоке 11 определяется амплитуды точек переключения по максимуму по критерию Yoi-in Yoin Y0i-nn, ведется подсчет суммы измерений Y0in и временных

интервалов т между точками переключений по минимуму 2 Y0in, ъ Г 2 А а также разность между временными интервалами от предыдущего минимума до максимума и от максимума до текущего минимума Ат Г.

При выделении точки переключения по минимуму Yijn на исходном сигнале в памяти блока 11 по сигналам распределителя 15 фиксируются измеренные значения минимума , максимума Zijn, накопленных суммы текущих значений ZY0in, r fy, разности временных интервалов А г j, текущего . времени Т с таймера и кода номеров датчика и разложения с шифраторов 18 и 9, которые затем переписываются в буферную память. После этого по сигналу ПИ (прием информации), вырабатываемым распределителем импульсов 15, информация передается в вычислитель 12, а в шифратор 9 записывается код второго разложения, и в блоке выделения переключений начинается поиск минимума второго разложения путем сравнения текущего минимума Yijn с предыдущим Yi|-in. Когда на основе критерия

Yn-in Ynn Yn+in будет найдена точка переключения по минимуму Yzjn в памяти блока выделения переключений будет зафиксирована информация о значениях минимума Yzj, максимума Z2)n, текущем времени Т и коде номеров датчик и разложения, которая затем переписывается в буферную память, после чего по сигналу ПИ с распределителя 15 передается в вычислитель, а шифратор 9 записывает код третьего разложения, и в блоке выделения переключений начинается поиск минимума третьего разложения аналогичным образом.

Для электрофизиологических сигналов

рекомендуемое число разложений 5. Для проведения тонких научных исследований число разложений может быть доведено до 10. После выполнения процедуры поиска точки переключения по минимуму последнего разложения КМ из распределителя 15 на счетчик 16 подается импульс и на выходе счетчика формируется код, обеспечивающий подключение к АЦП 10 через коммутатор 17 и усилитель 2 очередного датчика, а

также запись в шифратор 18 код номера этого датчика. Поиск точек переключения и передача информации в вычислитель с последующих датчиков осуществляется анало- гичным образом. После обработки

амплитуды сигнала с п-го датчика счетчик 16 возвращается в исходное состояние и начинается новый цикл анализа сигналов с первого датчика.

Вычислитель 12 производит обработку

информации по алгоритму, выполненному аналогично прототипу. До начала работы многоканального анализатора в память вычислителя вводится величина времени дискретизации А максимальное число

разложений КМ и количество датчиков. По сигналу прием информации (ПИ) в память вычислителя записывается информация о номере кода разложения К, номере датчика п, амплитуде j минимума Ykj, времени его

обнаружения tkjn, амплитуде j максимума Zkjn, временной интервал от J-1 минимума

до j минимума первого разложения т сум- . му текущих значений амплитуд на этом вре

менном интервале S j У YSi, разность

I 0

между временными интервалами от j-ro минимума до j-ro максимума и от j-ro максимума до (j + 1)-го минимума Affy. В вычислителе 12 рассчитываются и выводятся на графический регистратор следующие параметры :

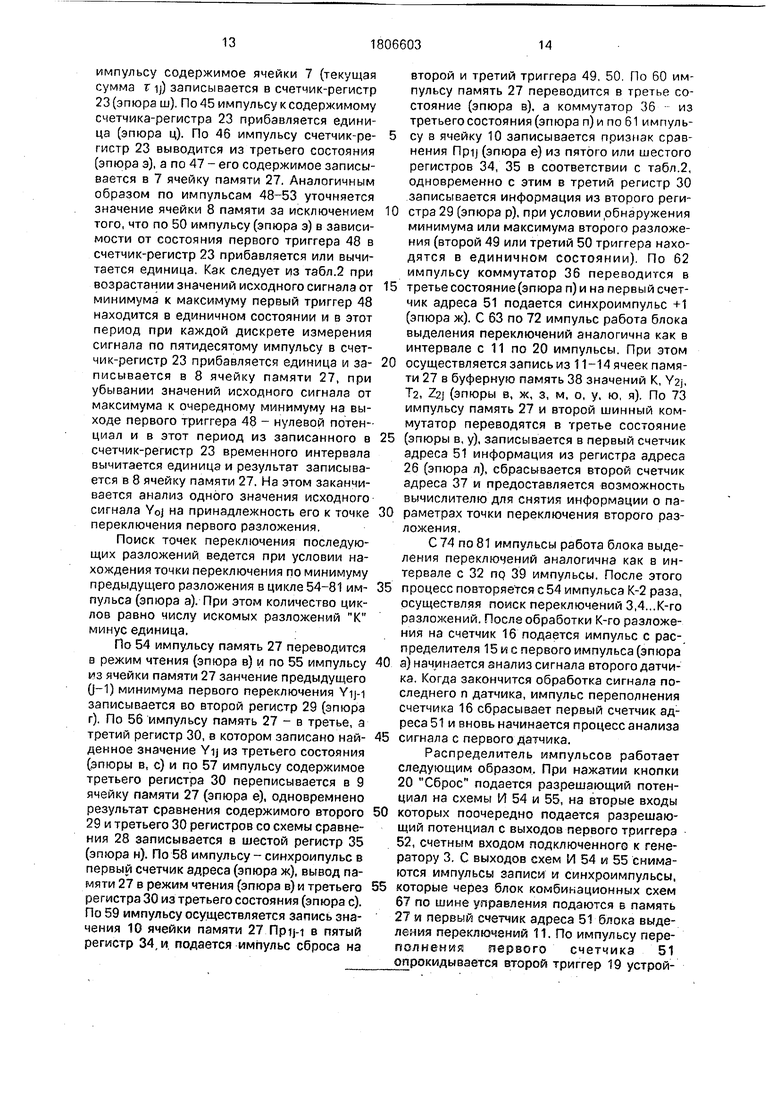

1. Текущая амплитуда k разложения сигнала с n-го датчика:

Akjn Zkjn - Ykjn.

2. Текущая длительность k разложения:

J+r

rCj SrC-i,,

d

где r - количество переключений (k - 1) разложения в интервале j-(J + 1) k-ro разложения сигнала с п-го датчика;

при k 1 SAi.

3. Текущая временная асимметрическая характеристика k разложения:

- &Лп ii --

А

Л

КГ

k-«j

k- }

j j+m где m - количество переключений (k-1) разложения в интервале от J переключения по минимуму до j переключения по максимуму k разложения сигнала с n-го датчика.

4. Текущая энергетическая характеристика разложения:

л /, rtki/uлП

SS в (vn +vn bbkj 5k.u .

Кроме того, в вычислителе рассчитываются математическое ожидание и средне- кавдратическое отклонение параметров с выводлом на цифровой регистратор согласно выражений:

«VviX-.i

.riA ,jtiA

ЛГ(лл / A1

iJlS-S J A

и Л

Wj:

-.tiA

А А ,д

Л СЛ +4-/Л f

k i г -г;пЧ-1Г/А Ј

ач-бч 1к1Ц- чН

)

+тНк- к

)

п ,п5 1 Г п Л и . hc т

V

r n5 ,- %

В этих формулах знак равенства () рассматривается как оператор присвоения в программе работы вычислителя.

Останов высилителя, как и в прототипе, 5 производится по внешним признакам после окончания работы анализатора, обеспечиваемого сигналом с таймера 8, устанавливающим первый триггер 5 в состояние О.

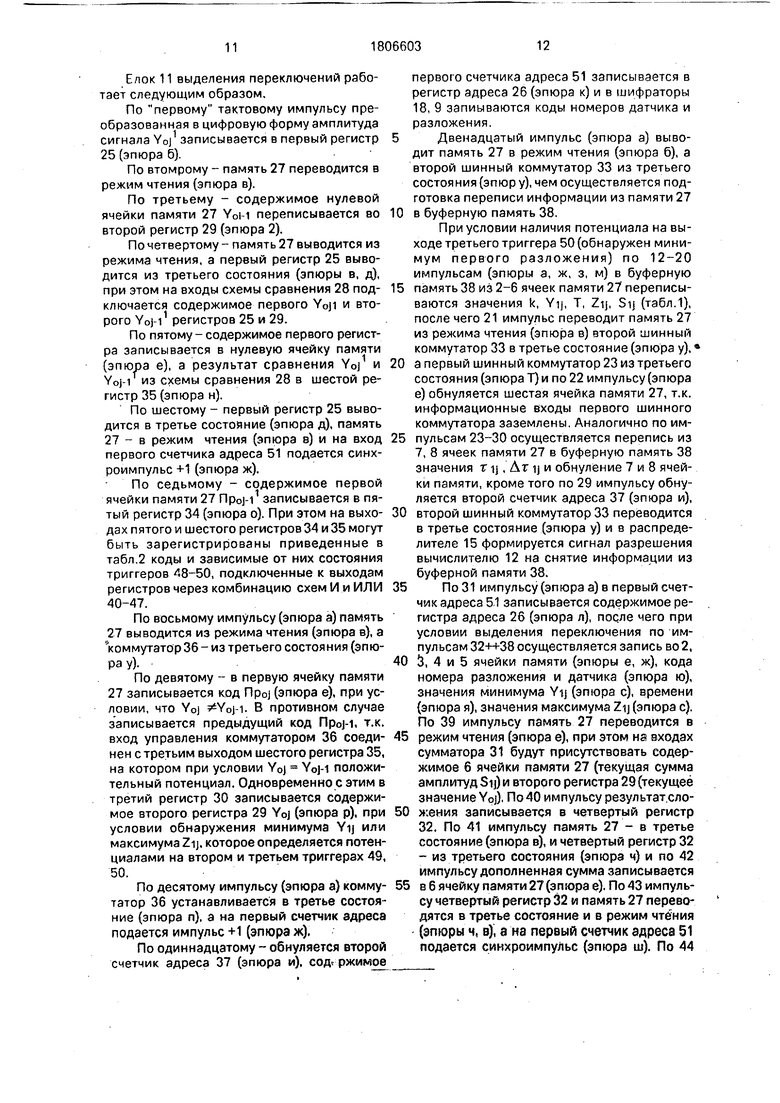

Работу блка 11 удобно рассматривать с 10 использованием представленных на фиг.5 эпюр основных сигналов шины управления (см. табл.1).

а - тактовые импульсы генератора 3 с условными номерами;

5 б-импульсы записи в первый регистр 25; в - сигналы чтения на память 27; г - импульсы записи во второй регистр 29; д - сигналы вывода первого регистра 25 из третьего состояния;

0 е, м - импульсы записи в память 27 и буферную память 58;

ж, з - синхроимпульсы (+1) в первый 51 и второй 37 счетчики адреса;

и - импульсы сброса второго счетчика 5 37 адреса;

к - импульсы записи в регистр адреса 26 данных из первого счетчика адреса 51;

л - импульсы записи в первый счетчик адреса 51 дакных из регистра адреса 26; 0 . н, о - импульсы записи в шестой 35 и пятый 34 регистры соответственно;

п - сигналы вывода коммутатора 36 из третьего состояния;

р- импульсы записи в третий регистр 30; 5 с, т, у - сигналы вывода третьего регистра 30, первого 24 и второго 33 шинных коммутаторов из третьего состояния соответственно;

ф - импульсы записи в четвертый ре- 0 гистр32;

ч, э - сигналы вывода четвертого регистра 32 и счетчика-регистра 23 из третьего состояния;

ш - импульсы записи информации из 5 памяти 27 в счетчик-регистр 23;

ц - синхроимпульсы (+1) в счетчик-регистр 23;

ю, я - сигналы вывода шифраторов 9,18 и таймера 8 из третьего состояния соответ- 0 ственно.

Стрелками вверх на эпюрах обозначены импульсы, которые формируются распределителем 15 при условии обнаруженя точек переключения по Минимуму. Стрелками 5 вниз - импульсы, которые формируются при условии обнаружения точек переключения по максимуму. Стрелками и вверх, и вниз - импульсы при условии обнаружения точек переключения по минимуму или по максимуму.

Елок 11 выделения переключений работает следующим образом.

По первому тактовому импульсу преобразованная в цифровую форму амплитуда сигнала Yoj1 записывается в первый регистр 25 (эпюра б).

По втомрому - память 27 переводится в режим чтения (эпюра в).

По третьему - содержимое нулевой ячейки памяти 27 Y0|-1 переписывается во второй регистр 29 (эпюра 2).

По четвертому - память 27 выводится из режима чтения, а первый регистр 25 выводится из третьего состояния (эпюры в, д), при этом на входы схемы сравнения 28 подключается содержимое первого Y0ji и второго Yoj-11 регистров 25 и 29.

По пятому-содержимое первого регистра записывается в нулевую ячейку памяти (эпюра е), а результат сравнения Y0j1 и Yoj-r из схемы сравнения 28 в шестой регистр 35 (эпюра н).

По шестому - первый регистр 25 выводится в третье состояние (эпюра д), память 27 - в режим чтения (эпюра в) и на вход первого счетчика адреса 51 подается синхроимпульс +1 (эпюра ж).

По седьмому - содержимое первой ячейки памяти 27 записывается в пятый регистр 34 (эпюра о). При этом на выходах пятого и шестого регистров 34 и 35 могут быть зарегистрированы приведенные в табл.2 коды и зависимые от них состояния триггеров 48-50, подключенные к выходам регистров через комбинацию схем И и ИЛИ 40-47.

По восьмому импульсу (эпюра а) память 27 выводится из режима чтения (эпюра в), а коммутатор 36 - из третьего состояния (эпюра у).

По девятому - в первую ячейку памяти 27 записывается код Пр0 (эпюра е), при условии, что YOJ Yoj-1. В противном случае записывается предыдущий код flpoj-1, т.к. вход управления коммутатором 36 соединен с третьим выходом шестого регистра 35, на котором при условии Y0j Y0j-i положительный потенциал. Одновременно с этим в третий регистр 30 записывается содержимое второго регистра 29 Y0j (эпюра р), при условии обнаружения минимума YIJ или максимума Zij. которое определяется потенциалами на втором и третьем триггерах 49, 50.

По десятому импульсу (эпюра а) коммутатор 36 устанавливается в третье состояние (эпюра п), а на первый счетчик адреса подается импульс +1 (эпюра ж).

По одиннадцатому - обнуляется второй счетчик адреса 37 (эпюра и), содержимое

первого счетчика адреса 51 записывается в регистр адреса 26 (эпюра к) и в шифраторы 18, 9 запиываются коды номеров датчика и разложения.

Двенадцатый импульс (эпюра а) выводит память 27 в режим чтения (эпюра б), а второй шинный коммутатор 33 из третьего состояния (эпюр у), чем осуществляется подготовка переписи информации из памяти 27

в буферную память 38.

При условии наличия потенциала на выходе третьего триггера 50(обнаружен минимум первого разложения) по 12-20 импульсам (эпюры а, ж, з, м) в буферную

память 38 из 2-6 ячеек памяти 27 переписываются значения k, YIJ, Т, 2ц, Sij (табл.1), после чего 21 импульс переводит память 27 из режима чтения (эпюра в) второй шинный коммутатор 33 в третье состояние (эпюра у),

а первый шинный коммутатор 23 из третьего состояния (эпюра Т) и по 22 импульсу (эпюра е) обнуляется шестая ячейка памяти 27, т.к. информационные входы первого шинного коммутатора заземлены. Аналогично по импульсам 23-30 осуществляется перепись из 7, 8 ячеек памяти 27 в буферную память 38 значения т ц , AT ij и обнуление 7 и 8 ячейки памяти, кроме того по 29 импульсу обнуляется второй счетчик адреса 37 (эпюра и),

второй шинный коммутатор 33 переводится в третье состояние (эпюра у) и в распределителе 15 формируется сигнал разрешения вычислителю 12 на снятие информации из буферной памяти 38.

По 31 импульсу (эпюра а) в первый счетчик адреса 51 записывается содержимое регистра адреса 26 (эпюра л), после чего при условии выделения переключения по импульсам 32++38 осуществляется запись во2,

3, 4 и 5 ячейки памяти (эпюры е, ж), кода номера разложения и датчика (эпюра ю), значения минимума Ytj (эпюра с), времени (эпюра я), значения максимума Zij (эпюра с). По 39 импульсу память 27 переводится в

режим чтения (эпюра е), при этом на входах сумматора 31 будут присутствовать содержимое 6 ячейки памяти 27 (текущая сумма амплитуд Sij) и второго регистра 29 (текущее значение Y0j). По 40 импульсу результат.сложения записывается в четвертый регистр 32. По 41 импульсу память 27 - в третье состояние (эпюра в), и четвертый регистр 32 - из третьего состояния (эпюра ч) и по 42 импульсу дополненная сумма записывается

в 6 ячейку памяти 27 (эпюра е). По 43 импульсу четвертый регистр 32 и память 27 переводятся в третье состояние и в режим чтения (эпюры ч, в), а на первый счетчик адреса 51 подается синхроимпульс (эпюра ш). По 44

импульсу содержимое ячейки 7 (текущая сумма г ij) записывается в счетчик-регистр 23 (эпюра ш). По 45 импульсу к содержимому счетчика-регистра 23 прибавляется единица (эпюра ц). По 46 импульсу счетчик-регистр 23 выводится из третьего состояния (эпюра э), а по 47 - его содержимое записывается в 7 ячейку памяти 27. Аналогичным образом по импульсам 48-53 уточняется значение ячейки 8 памяти за исключением того, что по 50 импульсу (эпюра э) в зависимости от состояния первого триггера 48 в счетчик-регистр 23 прибавляется или вычитается единица. Как следует из табл.2 при возрастании значений исходного сигнала от минимума к максимуму первый триггер 48 находится в единичном состоянии и в этот период при каждой дискрете измерения сигнала по пятидесятому импульсу в счетчик-регистр 23 прибавляется единица и записывается в 8 ячейку памяти 27, при убывании значений исходного сигнала от максимума к очередному минимуму на выходе первого триггера 48 - нулевой потенциал и в этот период из записанного в счетчик-регистр 23 временного интервала вычитается единица и результат записывается в 8 ячейку памяти 27. На этом заканчивается анализ одного значения исходного сигнала YOJ на принадлежность его к точке переключения первого разложения.

Поиск точек переключения последующих разложений ведется при условии нахождения точки переключения по минимуму предыдущего разложения в цикле 54-81 импульса (эпюра а). При этом количество циклов равно числу искомых разложений К минус единица.

По 54 импульсу память 27 переводится в режим чтения (эпюра в) и по 55 импульсу из ячейки памяти 27 занчение предыдущего (j-1) минимума первого переключения YIJ-I записывается во второй регистр 29 (эпюра г). По 56 импульсу память 27 - в третье, а третий регистр 30, в котором записано найденное значение YIJ из третьего состояния (эпюры в, с) и по 57 импульсу содержимое третьего регистра 30 переписывается в 9 ячейку памяти 27 (эпюра е), одновремнено результат сравнения содержимого второго 29 и третьего 30 регистров со схемы сравнения 28 записывается в шестой регистр 35 (эпюра н). По 58 импульсу - синхроипульс в первый счетчик адреса (эпюра ж), вывод памяти 27 в режим чтения (эпюра в) и третьего регистра 30 из третьего состояния (эпюра с). По 59 импульсу осуществляется запись значения 10 ячейки памяти 27 npij-i в пятый регистр 34, и. подается импульс сброса на

второй и третий триггера 49, 50. По 60 импульсу память 27 переводится в третье состояние (эпюра в), а коммутатор 36 из третьего состояния (эпюра п) и по 61 импуль- 5 су в ячейку 10 записывается признак сравнения npij (эпюра е) из пятого или шестого регистров 34, 35 в соответствии с табл.2, одновременно с этим в третий регистр 30 записывается информация из второго реги10 стра 29 (эпюра р), при условии обнаружения минимума или максимума второго разложения (второй 49 или третий 50 триггера находятся в единичном состоянии). По 62 импульсу коммутатор 36 переводится в

5 третье состояние (эпюра п) и на первый счетчик адреса 51 подается синхроимпульс +1 (эпюра ж). С 63 по 72 импульс работа блока выделения переключений аналогична как в интервале с 11 по 20 импульсы. При этом

0 осуществляется запись из 11-14 ячеек памяти 27 в буферную память 38 значений К, YZJ, Т2, Z2j (эпюры в, ж, з, м, о, у, ю, я). По 73 импульсу память 27 и второй шинный коммутатор переводятся в третье состояние

5 (эпюры в, у), записывается в первый счетчик адреса 51 информация из регистра адреса 26 (эпюра л), сбрасывается второй счетчик адреса 37 и предоставляется возможность вычислителю для снятия информации о па0 раметрах точки переключения второго разложения.

С 74 по 81 импульсы работа блока выделения переключений аналогична как в интервале с 32 пр 39 импульсы. После этого

5 процесс повторяется с 54 импульса К-2 раза, осуществляя поиск переключений 3,4...К-го разложений. После обработки К-го разложения на счетчик 16 подается импульс с распределителя 15 и с первого импульса (эпюра

0 а) начинается анализ сигнала второго датчика. Когда закончится обработка сигнала последнего п датчика, импульс переполнения счетчика 16 сбрасывает первый счетчик адреса 51 и вновь начинается процесс анализа

5 сигнала с первого датчика.

Распределитель импульсов работает следующим образом. При нажатии кнопки 20 Сброс подается разрешающий потенциал на схемы И 54 и 55, на вторые входы

0 которых поочередно подается разрешающий потенциал с выходов первого триггера 52, счетным входом подключенного к генератору 3. С выходов схем И 54 и 55 снимаются импульсы записи и синхроимпульсы,

5 которые через блок комбинационных схем 67 по шине управления подаются Б память 27 и первый счетчик адреса 51 блока выделения переключений 11. По импульсу переполнения первого счетчика 51 опрокидывается второй триггер 19 устройства, закрываются схемы И 54, 55 и открывается схема И 6 анализатора. При нажатии кнопки 21 пуск с первого триггера 5 устройства подается разрешающий потенциал на схемы И 56 и 57. При этом по второму входу схема И 56 открыта потецниалом со второго выхода второго триггера 53 и импульсы генератора 3 через схему И 56 поступают на вход счетчика 63, на первые входы схем И сборки 65 и через схему ИЛИ 68 на таймер 8. Импульс переполнения счетчика 63 через схему ИЛИ подается на вход счетчика-дешифратора 64. на выходах которого формируются разрешающие потенциалы на вторые входы соответствующих схем И сборки 65. При этом все дешифраторы блока 6 дешифруют код счетчика 63, однако импульс кода счетчика 63 будет сформирован на соответствующем выходе того дешифратора блока 66, номер которого соответевтву- ет коду счетчика дешифратора 64. Так например, в начальный период времени по каждому импульсу, поступающему на вход счетчика 63 будет формироваться на соответствующих выходах первого дешифратора блока 66, так как только на его вход управления будут поступать импульсы с выхода первой схемы И сборки 65, открытой потенциалом нулевого кода счетчика-дешифратора 64. По импульсу переполнения на выходе счетчика-дешифратора 64 будет первый код, по которому импульсы со второй схемы И сборки 65, открытой первым кодом счетчика-дешифратора 64, будут поступать на вход управления второго дешифратора блока 66. Таким образом на выходах блока дешифраторов будут последовательно формироваться импульсы, которые через блок комбинационных схем 67 подаются по шине управления в блок 11 выделения переключений. Примером распределения импульсов в шине управления являются эпюры, показанные на фиг.5:(1-п)импульсы (1-53 импульс фиг.5) обеспечивают процесс поиска точек переключения первого разложения; n + m +1 - п импульсы (54-81 импульс фиг.5) - для поиска точек переключения 2,3...к разложений; п + т импульс с выхода блока дешифраторов 66 обнуляет счетчик 63 и подается на вход счетчика-дешифратора 64, чем обеспечивается дальнейшее формирование импульсовcn+m+1-n для поиска точек переключения второго ранга (т определяется необходимой величиной задержки для обеспечения передача, записанной в буферной памяти 38 информации в вычислитель 12. В приведенном примере на фиг.5 m 0, п импульс с выхода блока дешифраторов 66 (на примере фиг.5 81 импульс) сбра- сывает второй триггер 53, запрещая

прохождение импульсов генератора 3 через схему И 56 и разрешая через схему И 57, Кроме того п импульс обнуляет счетчик 63 и счетчик-дешифратор 64. Тактовые импульсы

с выхода схемы И 57 поступают через схему ИЛИ 68 на таймер и на вход счетчика 60, который совместно с счетчиком 61 обеспечивает установление в счетчике-дешифраторе 64 кода, открывающего ту схему И сборки

65, выходы которой подключены к управля- ющему входу дешифратора блока 66 формирующего импульсы, начиная с п + m + 1 и задержку для передачи записанной в буферной памятим 38 информации в вычислитель

12. Импульс переполнения счетчика 61 подается на вход счетчика 62 и через схему ИЛИ 69 устанавливает второй триггер 53 в единичное состояние, закрывая схему И 57 и открывая схему И 56. С выхода схемы И 56

тактовые импульсы поступают на вход.счет- чика 63 и первые входы схем И сборки 65. При этом кодом счетчика дешифратора открыта та схема И сборки 65. импульсы с входа которой подаются на дешифратор

блока 66 начинающего формирование импульсов с п + m + 1. Таким образом, вновь формируются импульсы cn + m + 1-n, f обеспечивая поиск точек переключения третьего разложения. В счетчике 62 ведется

подсчет циклов поиска точек переключений, номера разложений которых больше единицы. При достижении значения счетчика 62 К-2 (К - заданное количество разложений) на его выходе формируется импульс, который

подается на счетчик 16 (выход R), переключающий аналоговый коммутатор 17 на следующий датчик 1. кроме того обнуляет

счетчик-дешифратор 64 и устанавливает второй триггер 53 в единичное сотсояние, и

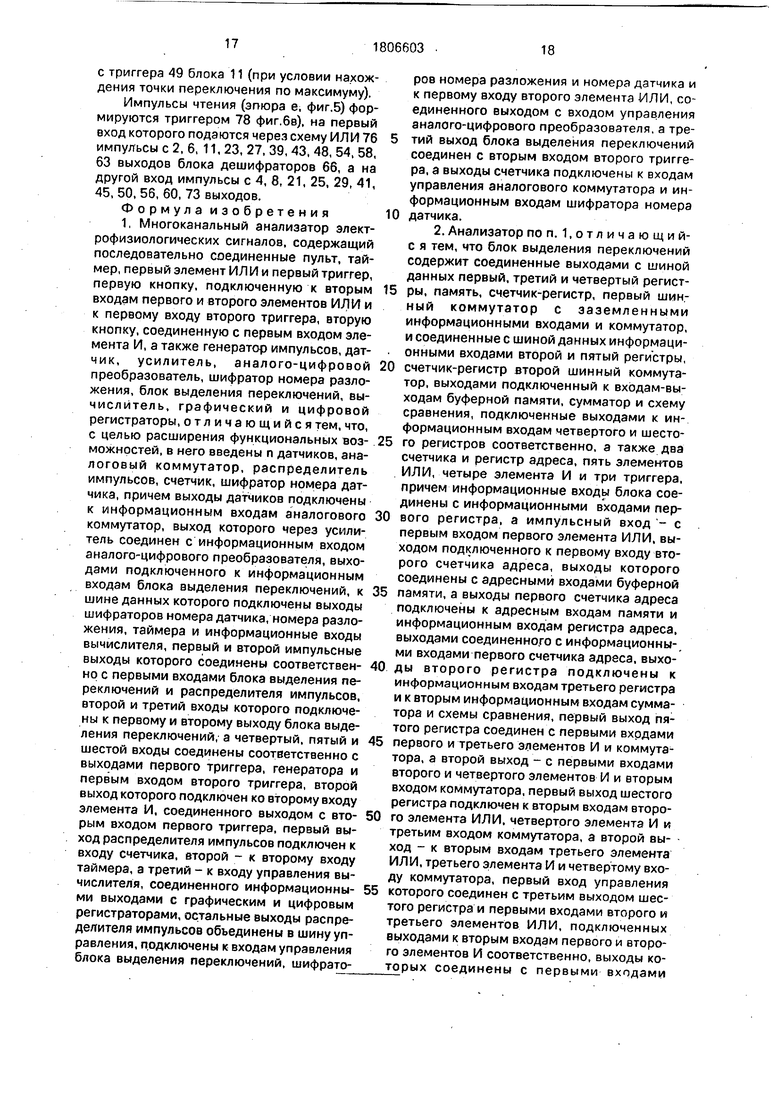

начинается новый цикл формирования импульсов, обеспечивающих поиск точек пере- ключений в исходном сигнале Y0j2 от второго, а затем третьего и т.д. датчиков 1. Работа блока комбинационных схем с

памятью 67 поясняется примерами формирования импульсов записи и чтения (фиг.ба, б), подаваемых на память 27 блока 11.

Из примера фиг.ба видно, что импульсы записи (эпюра е фиг.5) поступают на вход

памяти 27 блока 11 через схему ИЛИ 73 с выхода схемы И 54 (вход W) и выходов 5, 9, 42,47, 52 блока дешифраторов 66, а также с выходов 22, 26, 30, 32, 34, 36, 57, 61. 74, 76, 78 через схему ИЛИ 71 и схему И 74, открываемую потенциалом Мне триггера 50 блока 11 выделения переключений (при условии нахождения точки переключения по минимуму) и выходов 38, 80 через схему ИЛИ 72 и схему И 75, открываемую потенциалом Мк

с триггера 49 блока 11 (при условии нахождения точки переключения по максимуму).

Импульсы чтения (эпюра е, фиг.5) формируются триггером 78 фиг.бв), на первый вход которого подаются через схему ИЛИ 76 импульсы с 2, 6, 11, 23, 27, 39, 43, 48, 54, 58, 63 выходов блока дешифраторов 66, а на другой вход импульсы с 4, 8, 21, 25, 29, 41, 45, 50, 56, 60, 73 выходов.

Формула изобретения 1, Многоканальный анализатор электрофизиологических сигналов, содержащий последовательно соединенные пульт, таймер, первый элемент ИЛ И и первый триггер, первую кнопку, подключенную к вторым входам первого и второго элементов ИЛИ и к первому входу второго триггера, вторую кнопку, соединенную с первым входом элемента И, а также генератор импульсов, датчик, усилитель, аналого-цифровой преобразователь, шифратор номера разложения, блок выделения переключений, вычислитель, графический и цифровой регистраторы, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены п датчиков, аналоговый коммутатор, распределитель импульсов, счетчик, шифратор номера датчика, причем выходы датчиков подключены к информационным входам аналогового коммутатор, выход которого через усилитель соединен с информационным входом аналого-цифрового преобразователя, выходами подключенного к информационным входам блока выделения переключений, к шине данных которого подключены выходы шифраторов номера датчика, номера разложения, таймера и информационные входы вычислителя, первый и второй импульсные выходы которого соединены соответственно с первыми входами блока выделения переключений и распределителя импульсов, второй и третий входы которого подключены к первому и второму выходу блока выделения переключений, а четвертый, пятый и шестой входы соединены соответственно с выходами первого триггера, генератора и первым входом второго триггера, второй выход которого подключен ко второму входу элемента И, соединенного выходом с вторым входом первого триггера, первый выход распределителя импульсов подключен к входу счетчика, второй - к второму входу таймера, а третий - к входу управления вычислителя, соединенного информационными выходами с графическим и цифровым регистраторами, остальные выходы распределителя импульсов объединены в шину управления, подключены к входам управления блока выделения переключений, шифраторов номера разложения и номера датчика и к первому входу второго элемента ИЛИ, соединенного выходом с входом управления аналого-цифрового преобразователя, а тре- 5 тий выход блока выделения переключений соединен с вторым входом второго триггера, а выходы счетчика подключены к входам управления аналогового коммутатора и информационным входам шифратора номера 0 датчика.

2. Анализатор по п. 1,отличающий- с я тем, что блок выделения переключений содержит соединенные выходами с шиной данных первый, третий и четвертый регист- 5 ры, память, счетчик-регистр, первый шинный коммутатор с заземленными информационными входами и коммутатор, и соединенные с шиной данных информаци- . онными входами второй и пятый регистры,

0 счетчик-регистр второй шинный коммутатор, выходами подключенный к входам-выходам буферной памяти, сумматор и схему сравнения, подключенные выходами к информационным входам четвертого и шесто5 го регистров соответственно, а также два счетчика и регистр адреса, пять элементов ИЛИ, четыре элемента И и три триггера, причем информационные входы блока соединены с информационными входами пер0 вого регистра, а импульсный вход - с первым входом первого элемента ИЛИ, выходом подключенного к первому входу второго счетчика адреса, выходы которого соединены с адресными входами буферной

5 памяти, а выходы первого счетчика адреса подключены к адресным входам памяти и информационным входам регистра адреса, выходами соединенного с информационны-, ми входами первого счетчика адреса, выхо0 ды второго регистра подключены к информационным входам третьего регистра и к вторым информационным входам сумматора и схемы сравнения, первый выход пятого регистра соединен с первыми входами

5 первого и третьего элементов И и коммутатора, а второй выход - с первыми входами второго и четвертого элементов И и вторым входом коммутатора, первый выход шестого регистра подключен к вторым входам второ0 го элемента ИЛИ, четвертого элемента И к третьим входом коммутатора, а второй выход - к вторым входам третьего элемента ИЛИ, третьего элемента И и четвертому входу коммутатора, первый вход управления

5 которого соединен с третьим выходом шестого регистра и первыми входами второго и третьего элементов ИЛИ, подключенных выходами к вторым входам первого и второго элементов И соответственно, выходы которых соединены с первыми входами

четвертого и пятого элементов ИЛИ, выходами подключенных соответственно к первому и второму входам первого триггера, выход третьего элемента И соединен с вторым входом пятого эелмента ИЛИ и первым входом второго триггера, а выход четвертого элемента И - с вторым входом четвертого элемента ИЛИ и первым входом третьего триггера, шина управления блока выделения переключений подключена к управляющим входам памяти и буферной памяти, первого счетчика и регистратора адреса, счетчика-регистра и шести регистров, первого и второго шинных коммутаторов, к вторым входам управления коммутатора второго счетчика адреса, первого элемента ИЛИ, второго и третьего триггеров, а также к выходу первого триггера, первый, второй и третий выходы блока выделения переключений соединены с последним выходом первого счетчика адерса и выходами второго и третьего триггеров соответственно.

3. Анализатор по п,1, от л и ч а ю щи й- с я тем, что распределитель импульсов содержит два триггера, пять элементов ИЛИ, четыре элемента И, четыре счетчика, счетчик-дешифратор, блок дешифраторов, сборку элементов И, блок комбинационных схем, причем первый, второй и третий входы распределителя подключены к соответствующим входам блока комбинационных схем, четвертый вход - к первым входам третьего и четвертого элементов И, шестой - к первым входам первого и второго элементов И, пятый - к вторым входам четырех элементов И и первому входу первого триггера, первым и вторым выходами подключенного соответственно к третьим входам первого и второго элементов И, выходы которых соединены с четвертыми пятым входами блока комбинационных схем, выход третьего элемента И подключен к первым входам четвертого элемента ИЛИ, сборки схем И и четвертого счетчика, выходы которого подключены к информационным входам блока дешифраторов, а выход переполнения четвертого счетчика - к первому входу второго элемента ИЛИ, подсоединенного выходом к первому входу счетчика-дешифратора, выходы которого подключены соответственно к вторым входам сборки схем И, соединенных выходами с управляющими входами блока дешифраторов, выходы которого от первого до k-ro иск + т + 1до n-го подключены к входам блока комбинационных схем, n-й выход блока дешифраторов, кроме того,

подключен к первым входам второго триггера, первого и третьего элементов ИЛИ, соединенных выходами с вторыми входами четвертого счетчика и счетчика-дешифратора соответственно, a m + n-й выход блока

дешифраторов подключен к вторым входам первого и второго элементов ИЛИ, первый и второй выходы второго триггера соединены соответственно с третьими входами четвертого и третьего элементов И, выход

четвертого элемента И подключен к второму входу четвертого элемента ИЛИ, первому входу первого счетчика, выход которого соединен с вторым входом первого счетчика, третьим входом второго элемента ИЛИ и

первым входом второго счетчика, подключенного выходом к второму входу второго счетчика, первым входом пятого элемента ИЛИ и третьего счетчика, выходы которого соединены с вторыми входами третьего

счетчика, третьего и пятого элементов ИЛИ, и первому выходу распределителя, второй выход распределителя подключен к выходу четвертого элемента ИЛИ, первый выход блока комбинационных схем соединен с

третьим выходом распределителя, а остальные выходы блока комбинационных схем объединены в выходную шину управления,

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Микропрограммный процессор | 1981 |

|

SU1037262A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для сопряжения | 1979 |

|

SU824185A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Тренажер оператора автоматизированной системы управления | 1981 |

|

SU983738A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Адаптивный коммутатор системы телеизмерения | 1990 |

|

SU1714641A2 |

Изобретение относится к медицинской технике и может быть использовано при автоматизированной оценке функционального состояния человека, в терапии, кардиологии и других областях медицины, в клиниках различного профиля. Анализатор расширяет функциональные возможности за счет увеличения количества каналов анализа, выделяемых и измеряемых параметров анализируемых электрофизиологических сигналов. Многоканальный анализатор электрофизиологических сигналов содержит датчик, аналоговый коммутатор, усилитель, аналого-цифровой преобразователь генератор импульсов, шифратор номера разложения, шифратор номера датчика, распределитель импульсов, таймер, блок выполнения переключений, два триггера, пульт управления, вычислитель, графический и цифровой регистраторы, 2 з.п. ф-лы, 6 ил., 2 табл.

П р и м е ч а ни е. Sij - текущая сумма амплитуд исходного сигнала;

Yoj-1 -амплитуда исходного сигнала X(t) в j-1 молмент Прон -признак сравнения Y0j-2 и YOJ-I; при Y0i-i Yoi-2 , при Y0j-i Y0i-2

К - код номера разложения и номера датчика; YIJ - амплитуда минимума первого разложения;

Т - время выделения минимума; Zij - амплитуда максимума первого разложения; Гц - текущая сумма временных дискрет измерения амплитуды сигнала;

Arij- текущая разность между интервалами от минимума до максимума и от максимума до последующего минимума.

Таблица 2

m-i

JTV

-С

/у

«f

Ј1

«

CO

ЈU

ЯГ

.r

Xli/P

f1

«

r/

л-..-

V

yiSAv Y-% : : .-;

,.; . , LT

irS1:;; :; . .- LT

.felMv... I ..

ITTTT . :

. -;;-v .

.I

.l: ,,- I--;.;.. -. ..----

Vvf 1 1 I . -. .

;,v.-.,-.;-...I Ml.

v ( l- ; M TT Г Г

-

----.. .--vti

JlJlTl nJ Lr -LTUI nnrg

et

OS

OS

i,. .№

ну

0

Л

9

t-ttiJtV

umj

M

1 r

Hit

/

ft т -К

-л

1 П П VJ--:-

ггии- - J

итг

f

Tr.tf .

t t. U Hi4

-У

I I I M I I I МП

-ж

----.. .--vti

at

v

t ,

fe

J

Hi

if

LFfc

ff

Sf

t

sr

e09908l

Фт.6.

39

ИЧг

43

1L

К

7g

-±L

45

| Авторское свидетельство СССР № 13606698, кл | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1993-04-07—Публикация

1991-02-11—Подача