соединен со стробирующим входом схемы сравнения, входом чтения блока памяти и третьим входом элемента 2И-ИЛИ, второй вход элемента И соединен через второй элемент НЕ с выходом элемента ИЛИ, входом записи блока памяти и управляющим входом коммутатора адреса, группа выходов которого соединена с группой адресных входов блока памяти и второй группой входов узла свертки, первая и вторая группы информационных входов коммутатора адре1.14 са соединены соответственно с второй группой входов внешнего адреса микрокоманд устройства и группой информационных выходов счетчика.микрокоманд, первый вход элемента ИЛИ соединен через элемент задержки с первым выходом i -го дешифратора, а второй - с входом записи устройства, группа информационных входов блока памяти является второй группой информационных входов устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

| Микропрограммное устройство управле-Ния | 1979 |

|

SU802963A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее генератор тактовых импульсов, вход запуска которого является управлякяцим входом устройства, блок памяти, -счетчик микрокоманд, m дешифраторов, регистр, счатчик тактов, узел свертки, схему сравнения, первый элемент НЕ и элемент 2И-Ш1И, выход которого соединен со счетным входом счетчика микрокоманд, первый, второй и третий входы записи которого соединены соответственно с первым выходомm-го дешифратора, первым выходом (m-l)-ro дешифратора и первым выходом первого дешифратора, первая и вторая группы информационных,входов счетчика микрокоманд соединены соответственно с первой группой входов внешнего адреса микрокоманд устройства и группой информационных выходов регистра, третья группа информационных входов счетчика микрокоманд соединена с группой информационных выходов устройства, группой выходов блока памяти, группами информационных входов дешифратбров, группой информационных входов счетчика тактов и первой группой информационных входов регистра, вторая и третья группы информационных входов которого соединены соответственно с группой информационных выходов счетчика микрокоманд и первой группой информационных входов устройства, первый, второй и третий входы записи регистра соединены соответственно с вторым выходом первого дешифратора, первым выходом второго дешифратора ипервым выходом третьего дешифратора, счетный вход счетчика тактов соединен с первым вьгходом

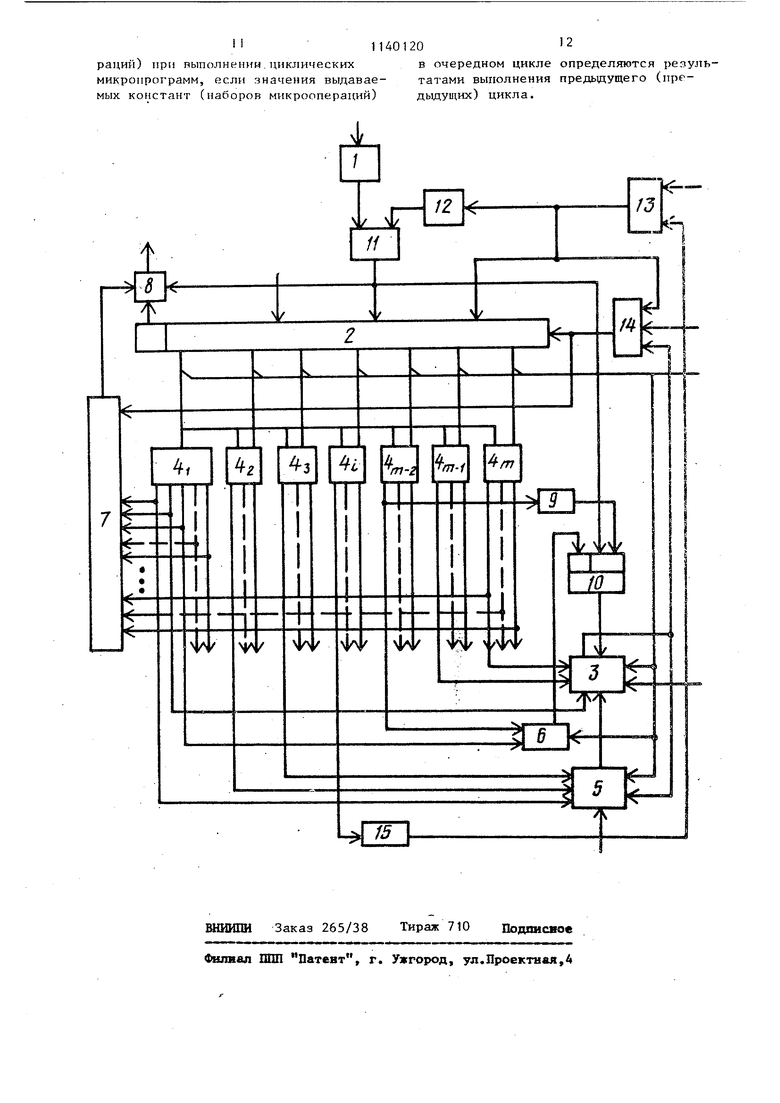

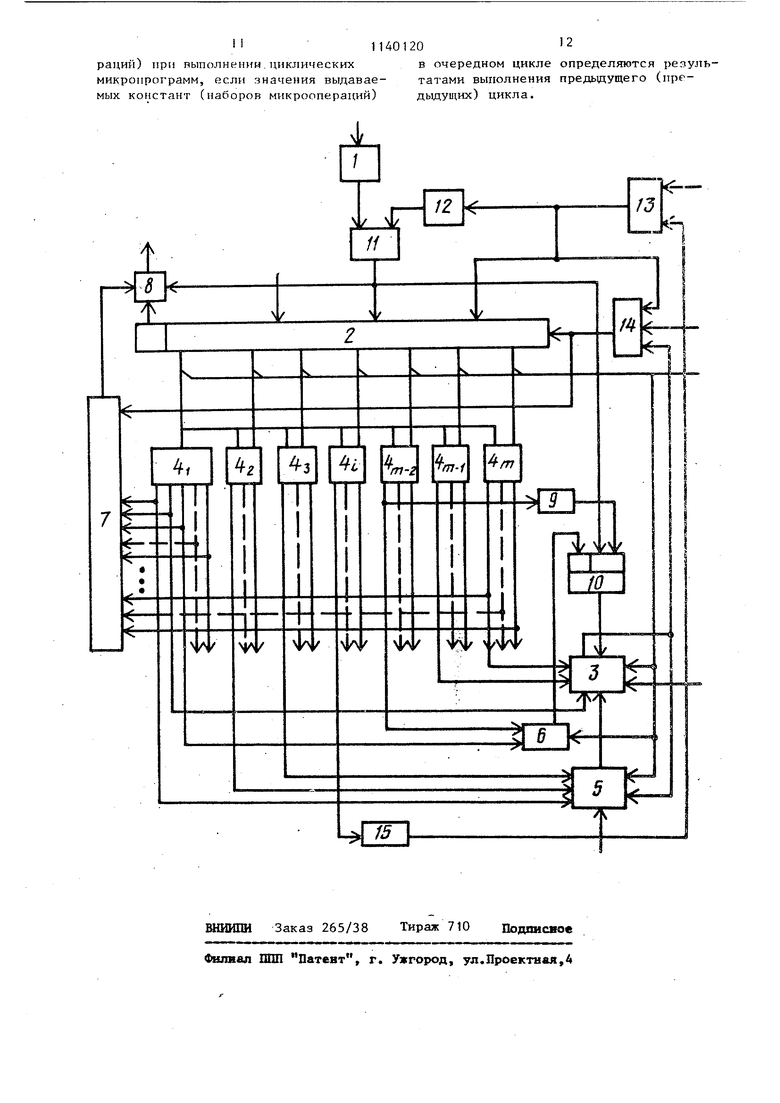

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления цифровых вычислительных машин. Известно микропрограммное устройство управления, содержащее генератор тактовых импульсов, блок памяти, счетчик микрокоманд, регистр и m дешифраторов m . Недостатком данного устройства яв ляется необходимост значительных затрат оборудования на его реализацию. Когда по ходу выполнения програм мы не tpeбyeтcя выдавать на выходы устройства никаких микроопераций в. течение определенного отрезка времени (тактов), необходимо оставлять в памяти микрокоманд зоны нулевых ячеек, число которых равно количеству режимов Трата в программе. Число нулевых ячеек в каждой зоне зависит от количества тактов, в течение которых необходимо произвести режим Трата. Все это приводит к значительному увеличению затрат памяти микрокоманд при реализации такого устройства управления. .Наиболее близким к предлагаемому потехнической сущности и достигаемому положительному результату явля ется микропрограммное устройство управления, содержащее генератор тактовых импульсов вход запуска ко торого является управляннцим входом устройства, блок памяти, счетчик ми рокоманд, rrt дешифратЬров, регистрД счетчик тактов, узел свертки, схему сравнения, первый элемент НЕ и элемент 2И-ИЛИ, выход которого соединен со счетным входом счетчика микрокоманд, первый, второй и третий входы записи которого соединены соответственно с первым выходом m-го дешифратора, первым выходом (т-1)го дешифратора и первым выходом первого дешифратора, первая и вторая группы информационных входов счетчика микрокоманд соединены соответственно с первой группой входов внешнего адреса микрокоманд устройства и группой информационных выходов регистра, третья группа информационных входов счетчика микрокоманд соединена с группой информационных вькодов устройства, группой выходов блока памяти, группами информационных входов дешифратора, группой информационных входов счетчика тактов и первой группой информационных входов регистра, вторая и третья группы информационных входов которого соединены соответственно с группой информационных выходов счетчика микрокоманд и первой группой информационных входов устройства, первьй, второй и третий входы записи регистра соединены соответственно с вторьв4 выходом первого дешифратора, первым выходом второго дешифратора и,первым выходом третьего дешифратора, счетный вход счетчика тактов соединен с первь м выходом (П1-2)-го дешифратора и через первый элемент НЕ с первым входом элемента 2И-ИЛИ, второй вход которого соединен с выходом счетчика тактов, вход записи которого соединен с третьим выходом первого дешифратора, четвертьш выход которого соединен со стробирующнми входами остальных дешифраторов, выходы дешифраторов подключены к соответствующим входам первой группы узла свертки, группа выходов i-ro (i 1,2,...,m) дешифратора соединена с i-й группой управляющих выходов устройства, выход узла свертки соединен с первым информаи,ионным входом схемы сравнения, второй информационный вход которой подключен к выходу контрольных разрядов блока памяти, выход -схемы сравнения является выхоДом индикации исправности устройства 2. Недостатком известного микропрограммного устройства управления является отсутствие возможности оперативного изменения содержимого любой ячейки блока памяти, а следовательно и набора микроопераций в ходе вьшолнения микропрограммы по результатам работы других устройств ЭВМ, что приводит к значительному расходу ячеек блока памяти при организации циклических микропрограмм с модификацией констант или наборов микроопераций внутри цикла.Так, например,для подготовки к выдаче в абоненты модифицированных констант в ходе выполнени циклических микропрограмм (значение констант меняется в каждом цикле) в известном микропрограммном устройстве требуется в общем случае (.Z. га,), п +3р ячеек (где п - числоЧ1иклов; р - число групп констант, выдаваемых в одном цикле (под группой подразумеваются подряд записанные константы в блоке памяти);m j - число констант в данной группе). Кроме того, в указанном микропрограмм,ном устройстве в принципе не возможна выдача модифицированных констант (наборов микроопераций) при вы полнении циклических микропрограмм, если значения -выдаваемых констант (наборов микроопераций) в очередном цикле определяются результатами выполнения предыдущего (предыдущих) цикла. . Указанный недостаток снижает функ циональные возможности, гибкость программирования известного микропрограммного устройства управления и приводит к значительному увеличению затрат оборудования (количества яче10 ек блока памяти) при. организации цикических микpoпpoгpa iм с модификацией констант или наборов микроопераций внутри цикла. Цель изобретения - сокращение оборудования микропрограммного устройства управления. Поставленная цель достигается тем, что в микропрограммное устройство управления-, содержащее генератор тактовых импульсов,вход которого является управляющим входом устройства, блок памяти,:счетчик микрокомандS m дешифраторов, регистр, счетчик тактов, узел свертки, схему сравнения, первый элемент НЕ и элемент 2И-Ш1И, выход которого соединен со счетным входом счетчика-микрокоманд, первый,второй и третий входы записи которого соединены соответственно с первым входом т-го дешифратора, первым выходом (m-l)-ro дешифратора и первым выходом первого дешифратора, первая и вторая группы информационных входов счетчика микрокоманд соединены соответственно с первой групт пой входов внешнего адреса микро-команд устройства и группой информа- . ционных выходов регистра, третья группа информационных входов счетчика микрокоманд соединена с группой информационных- выходов устройства, группой выходов блока памяти, группами информационных- входов дешифраторов, группой информационных входов счетчика тактов и тшрвой группой информационных входов регистра, вторая и третья группы .информационных входов которого соединены соответственно с группой информационных выходов счетчика микрокоманд и первой группой информационных.входов устройства, первый, второй и третий.входы записи регистра соединены соответственно с вторым выходом первфго дешифратора, первым выходом второго дешифратора и первым выходом третьего дешифратора, счетный вход счетчика тактов соединен с первым выходом (in-2) -го дешифратора и через первый элемент НЕ с первым входом элемента 2И-ИЛИ5 второй вход которого соединен с выходом счетчика тактов, вход записи.которого соединен с третьим выходом первого дешифратора,.четвертый выход которого соединен со стробирующими входами остальньпс дешифраторов, выходы дешифраторов подключены к соответствующим входам первой группы входов узла свертки, группа выходов i-го (i 1,2,...,m) . дешифратора соединен с i-й группой-управляющих выходов устройства, выход узла свертки соединен с первым информационным входом схемы сравнения, второй информационный вход которой подключен к выходу контрольных разрядов блока памяти, выход схемы сравнения является выхо дом индикации исправности устройства, дополнительно введены элемент И, второй элемент НЕ, элемент ИЛИ, коммутатор адреса и элемент задержки, причем, выход генератора тактовых . импульсов соединен с первым входом элемента И, выход которого соединен со стробирующим входом схемы сравнения, входом чтения блока.памяти и третьим входом элемента 2И-ИЛИ, второй вход элемента И соединен через второй элемент НЕ с выходом .элемента ИЛИ, входом записи блока памяти и управляющим входом коммутатора адреса, группа выходов которого соединена -с группой адресных входов блока памяти и второй группой входов узла свертки, первая и вторая группы нформационных входов коммутатора адреса соединены соответственно с второй группой входов внешнего адреса микрокоманд устройства и группой информационных выходов счетчика микрокоманд, первый вход элемента ИЛИ сое динен через элемент задержки с первым выходом i-ro дешифратора, а второй с- входом записи устройства, группа информационных входов блока памяти является второй группой информационных входов устройства. На чертеже представлена функциональная схема, устройства. Микропрограммное устройство управ ления содержит, генератор -1 тактовых импульсов, блок 2 памяти счетчик 3 микрокоманд, дешифраторы f-, гистр 5, счетчик 6 тактов, узел 7 свертки, схему 8 сравнения, первый, элемент НЕ 9, элемент.. 2И-ШШ 10, эле мент И 11, второй элемент НЕ 12, эле мент ИЛИ 13, коммутатор 14 адреса и элемент 15 задержки. Устройство работает следующим образом. Первоначально производится загру ка информации ,в блок 2 памяти следующим образом. Команда записис вхо да записи устройства- через второй 06 вход элемента ИЛИ 13 воздействует на вход записи блока 2 памяти, на управляющий вход коммутатора 14 адреса и через второй элемент НЕ 12 на второй вход элемента И 11, блокируя уровнем О прохождение импульсок с выхода генератора 1 на вход чтения блока 2 памяти, и стробирующий вход схемы 8 сравнения, а также прибавление единицы -в счетчик 3 микрокоманд. Уровень 1 с выхода элемента ИЛИ 13 разрешает прохождение информации с первой группы, информационных входов коммутатора 14 адреса, соединенных с второй группой входов внешнего адреса микрокоманд устройства, через коммутатор адреса 14 на группу адресных входов блока 2 памяти и соответствующие входы второй группы входов, узла 7 свертки. По сигналу, поступающему на вход записи блока 2 памяти , информация с группы информационных входов блока 2 памяти соединенных с второй группой инфорформационных входов устройства, записывается в ячейку, адрес которой соответствует информации, поступающей с второй группы входов внешнего адреса микрокоманд устройства. Генератор 1 тактовых импульсов вырабатывает сигналы, по которым при наличии уровня 1 на втором входе элемента И 11 производится считывание информации из блока 2 памяти и состояние счетчика 3 микрокоманд изменяется на единицу после каждого опроса памяти 2 блока. Сигнал с выхода генератора 1 тактовых импульсов поступает при наличии уровня 1 на втором входе элемента И 11 на счетный вход счетчика микрокоманд 3 через элемент 2И-ИЛИ 10 при условии, что на первьм вход элемента 2И-ИЛИ . 10 поступает разрешающий сигнал уровня 1 с выхода первого элемента НЕ 9. Уровень. на выходе первого элемента НЕ 9-соответствует уровню О первого выхода дешифратора (f.,n Микрокоманда, считанная из блока памяти 2, по адресу, указанному в счетчике 3 микрокоманд, поступает на группы информационных входов дешифраторов 4 S 1 и в соответствии с кодом, записанным в каждой группе, на выходах этих дешифраторов, вырабатываются микрооперации. 7 которые подаются к устройствам цифровой вычислительной машины (не показана) для выполнения соответствующих действий. Значение счетчика микрокоманд . увеличивается на единицу,, производится считывание микрокоманды из следующей ячейки блока памяти 2 и ее расшифровка, цикл работы устройства повторяется. Чтение констант из блoka 2 памяти и передача их в абоненты устро ства управления происходит следующим образом. I , Каждому выходу дешифратора 4| соответствует абонент устройства управления, которому записывается кон станта из блока 2 памяти. При возбуждении хотя бы одного из выходов дешифратора 4i, на его четвертом вы ходе, связанном со стробирующими входами остальных дешифраторов, появляется сигнал, запрещающий выработку микроопераций на выходах дешиф раторов 42, 4, 4,-,..., 4. Поэтому при считывании константы из блока 2 памяти и передачи ее абоненту дешиф ратора 4 дешифраторы 4, 4, 4,... 4 не работают и ложные микрооперации не вырабатываются. Изменение содержимого любой ячей ки блока 2 памяти происходит следую щим образом. При расшифровке соответствующей микрокоманды возбуждается первый вы ход i-ro дешифратора, соединенный с входом элемента 15 задержки. Элемент задержки 15 осуществляет задер ку входного сигнала на время, равно периоду следования импульсов генера тора 1. . Сигнал с выхода.элемента 15 задержки, проходя через первый вход элемента ИЛИ 13, воздействует на вход записи блока 2 памяти, на управляющий вход коммутатора 14 адреса и через второй элемент НЕ 12 на второй.вход элемента И 11, блокируя уровнем О с выхода второго элемен та НЕ 12 прохождение импульсов .с вы хода генератора 1 на вход чтения бл ка 2 памяти и стробирующий вход схе мы сравнения, а также прибавление единицы в счетчик 3 микрокоманд. Уровень 1 с вькода элемента ИЛ 13 разрешает прохождение информации 08 с первой группы информационных входов коммутатора -14 адреса, соединенных с второй группой-входов внешнего адреса микрокоманд.устройства, на группу выходов коммутатора 14 адреса и, следовательно, на группу адресных входов блока 2 памяти. Таким образом, по сигналу, поступающему на вход записи блока 2 памяти, информация с группы информационных входов блока 2 памяти записывается в ячейку, адрес которой соответствует информации, поступающей с второй группы входов внешнего адреса микрокоманд устройства. Режим Трата в микропрограмме производится следующим образом. На счетчик тактов 6 по группе информационных входов производится запись константы из блока памяти 2по микрооперации, вырабатываемой третьим выходом дешифратора 4 и появляющейся на входе записи счетчика 6 тактов. Значение константы, записываемой на счетчик 6 тактов, должно быть равно 2 -К (где п - число разрядов счетчика тактов 6; К - число тактов, в течение которых осуществляется режим Трата). Затем производится обращение за следующей микрокомандой, и на первом выходе дешифратора появляется микрооперация, которая воздействует на счетный вход счетчика тактов 6 н через первый элемент НЕ 9 блокирует прохождение сигналов с выхода генератора 1 тактовых импульсов через элемент 2И-ИЛИ 10 на счетный вход счетчика 3микрокоманд. При этом с выхода генератора 1 тактовых импульсов на вход чтения блока 2 памяти продолжают поступать сигналы считывания информации, и на первом выходе дешифратора 4,2 каждый раз вырабатывается микрооперация, воздействующая на счетный вход счетчика 6 тактов и блокирующая изменение значения счетчика 3 микрокоманд. Состояние счетчика тактов 6 изменяется на единицу после прихода каждого импульса на его счетный вход с первого выхода дешифратора 4.2 Когда состояние счетчика 6 тактов характеризуется числом (), т.е. все п разрядов счетчика тактов 6 находятся в единичном состоянии, то по приходу очередного импульса на счетный вход.счетчика 6 тактов на его выходе вьфабатывается- сигнал переполнения которьм через схему 2И-Ш1И 10 воздействует иа счетный вход счет чика 3 микрокоманд. Счетчик 3 микрокоманд, к следующему такту -изменяет свое состояние, на единицу из следую щей ячейки .блока 2 -памяти проиэводит -ся считыв.ание информации. Для осуществления безусловных переходов .в микропрограмме.производитс обращения к блоку 2 памяти за константой и запись считанной константы по третьей группе:информационных входов на счетчик 3 микрокоманд по микрооперации,.вырабатываемой первым выходом дешифратора 4 и появляющейся на третьем входе записи счетчика 3 микрокоманд. Условные переходы-в микропрограмме осуществляются следующим образом. Если по ХОДУ программы необходимо проанализировать состояние первой группы входов внешнего адреса микрокоманд устройства-, связанных с первой группой информационных входов счетчика 3 микрокоманд, или группы информационных выходов регистра 5, связанных со второй-группой информационных входов счетгчика 3 - микрокоман то на первый и второй входы записи счетчика 3. микрокоманд, связанные с первыми выходами- соответственно т-го и (m-l)-ro дешифраторов, поступают микрооперации,- по которым информация с первой группы входов внеш него адреса микрокоманд устройства или .с группы информационных выходов регистра 5 записывается-на счетчик 3 микрокоманд-и управление передается той ячейке блока 2памяти, адрее которой соответствует состоянию первой группы входов внешнего адреса микрокоманд-устройства, связанных с первой группой информационных входов счетчика-микрокоманд 3, или. состоянию группы информационных выходов регистра 5.Запись константы на регистр 5 производится из блока 2 памяти по первой группе информационных входов и микрооперации, вырабатываемой вторым выходом дешифратора 4| и появляющейся на первом 6ходе записи регистра 5. С целью расширения функциональных возможностей при организации условных переходов информация.на- регистр. 5 может записываться также с первой- группы- информационных входов устройства, связанных с третьей группой информационных входов регистра 5, и с группы информационных БЬУХОДОВ счетчика 3 микрокоманд, связанных с второй группой информационных входов регистра 5,.по микрооперациям, вырабатываемьм первыми, выходами дешифраторов 4 и 4/5 и поступающим соответственно на второй и третий входы записи регистра 5. Контроль правильности работы микропрограммного ус тройства управления в ходе выполнения микропр-ограммы осуществляется следуюащм образом. В каждой ячейке блока 2 памяти записаны контрольные -разряды по модулю :1 (modi) когда адреса данной ячейки , блока 2 памяти и кода выходов дешифраторов 4, 4, 4 ,..., 4, fcoответствующих информации в данной ячейке блокапамяти 2. Выход контрольных разрядов блока 2 памяти подключен к второму информационному входу схемы 8 сравнения. Узел 7 свертки осуществляет свертку кода адреса и кода выходов дешифраторов 4i, 4, 4, 4j, ..., 4f по modi. Выход узла 7 свертки подключен к первому информационному входу схемы 8 сравнения. В каждом такте работы устройства уцравления-сравнивается, выход контрольных разрядов блока 2 памяти с выходом узла 7 свертки. В случае формирования ложных микроопераций (или невыработки необходимых микроопераций) из-за искажения информации в блоке 2 памяти-.или кода-ад-реса вы- ход,контрьльных разрядов блока 2 памяти не совпадает с выходом узла 7 свертки-и схема В сравнения вырабатывает сигнал несравнения, сигнализирующий о сбое или неисправности устройства управления, В предлагаемом микропрограммном устройстве.управления для -подготовки вьщачи, например, модифицированных констант в ходе выполнения циклических, микропрограмм (значения констант меняются в каждом,дикле) требуется в общем случае (.Ё ) п ячеек блока. 2 памяти, т.е. Зр ячеек меньше, чем в известном устройстве. Кроме того, в предлагаемом микропрограммном устройстве-в отличие от известного возможна выдача модифицированных- констант.(наборов микроопеч114012012

раций) при пыполнеиин.циклических в очередном цикле определяются резульмикропрограмм, если значения выдаваемых констант (наборов микроопераций)

татами выполнения предыдущего (предыдущих ) ЦИКл а.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управле-Ния | 1979 |

|

SU802963A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1983-02-28—Подача