Изобретение относится к автоматике и вычислительной технике, может применяться в АСУ ТП и группами идентичных объектов, работающих с временным запаздыванием друг относительно друга (например, группами станков с ЧПУ и др.), а также в системах обработки данных с конвейерным выполнением микропрограмм.

Цель изобретения - расширение области применения и повышение производительностимикропрограммнойуправляющей конвейерной системы.

Сущность изобретения состоит в расширении области применения системы реализации программ с различными типами параллелизма и повышении производительности микропрограммной управляющей

конвейерной системы при реализации программ с двойным параллелизмом путем разделения ее на п независимо функционирующих подсистем. Программа обладает двойным параллелизмом в том случае, если наряду с параллелизмом множества объектов решаемая задача позволяет выделить параллелизм независимых операций. Рассмотрим пример вычисления интеграла. Лри этом задана функция f(x) и интервал интегрирования . Требуется

О Os СЛ СО

&

вычислить / f(x)dx. Задача сводится к выа

числению интегральной суммы. Интервал интегрирования разбивается на R элементарных участков. Величина R зависит от необходимой точности вычислений,,В

середине каждого К-го участка вычисляется значение функции f(xi), которое умножается на длину участка I. Сложив результаты, полученные на каждом участке, в итоге мы будем иметь значение интегральной суммы функции f(x) на интервале , Ь, которое с определенной степенью точности будет соьответствовать значению /f(x)dx.

Теперь разобьем интервал a, b на N участков. На каждом из участков будет работать один блок микропрограммного управления, причем каждый К-й блок организует вычисления по алгоритму

Fk F (хк1) + Fk-iM

где F(x k)fk(xi)l - значение элементарного слагаемого интегральной суммы на К-м участке К-1 N, b i-й точке..

Воспользовавшись тем, что

ЬсМЬ

J f(x)dx / f(x)dx + / f(x)dx + J f(x)dx,

aac-f-1м + 1

можно разбить все число блоков микропрограммного управления на п групп блоков N/n в каждой. Теперь задача сводится к вычислению суммы интервалов. Таким образом, внутри 1-п групп блоков используется параллелизм множества объектов, а наличие п групп блоков возможно благодаря тому, что задача обладает параллелизмом независимых операций.

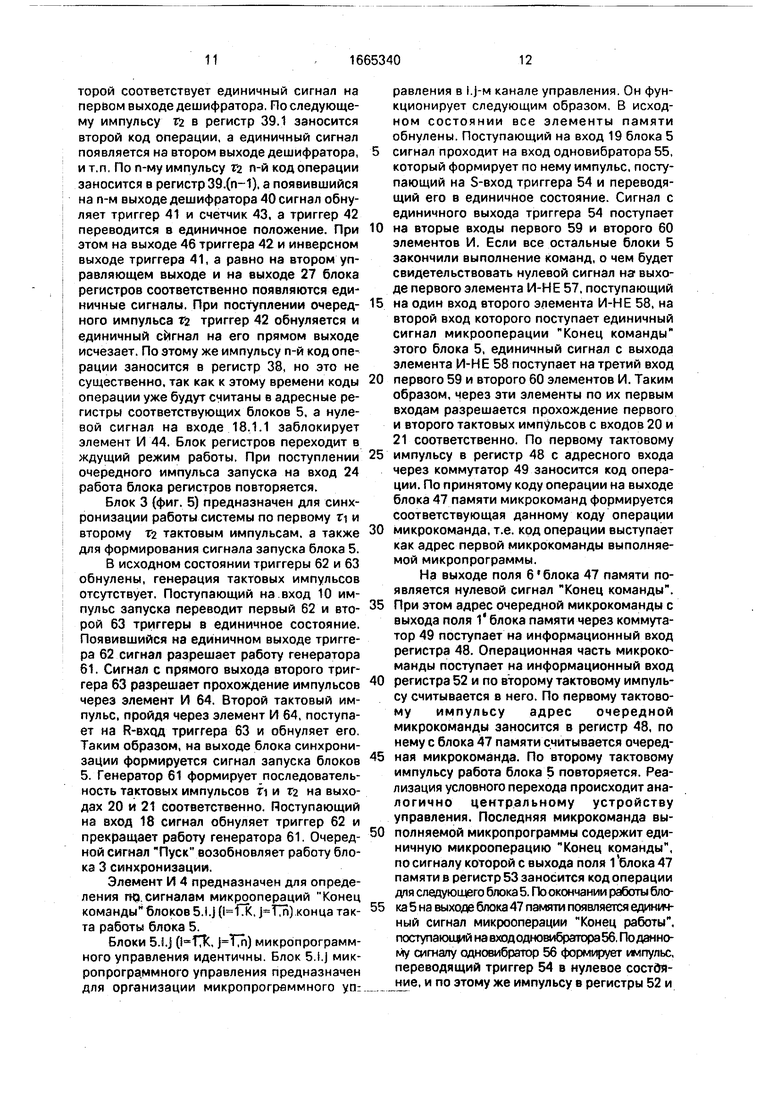

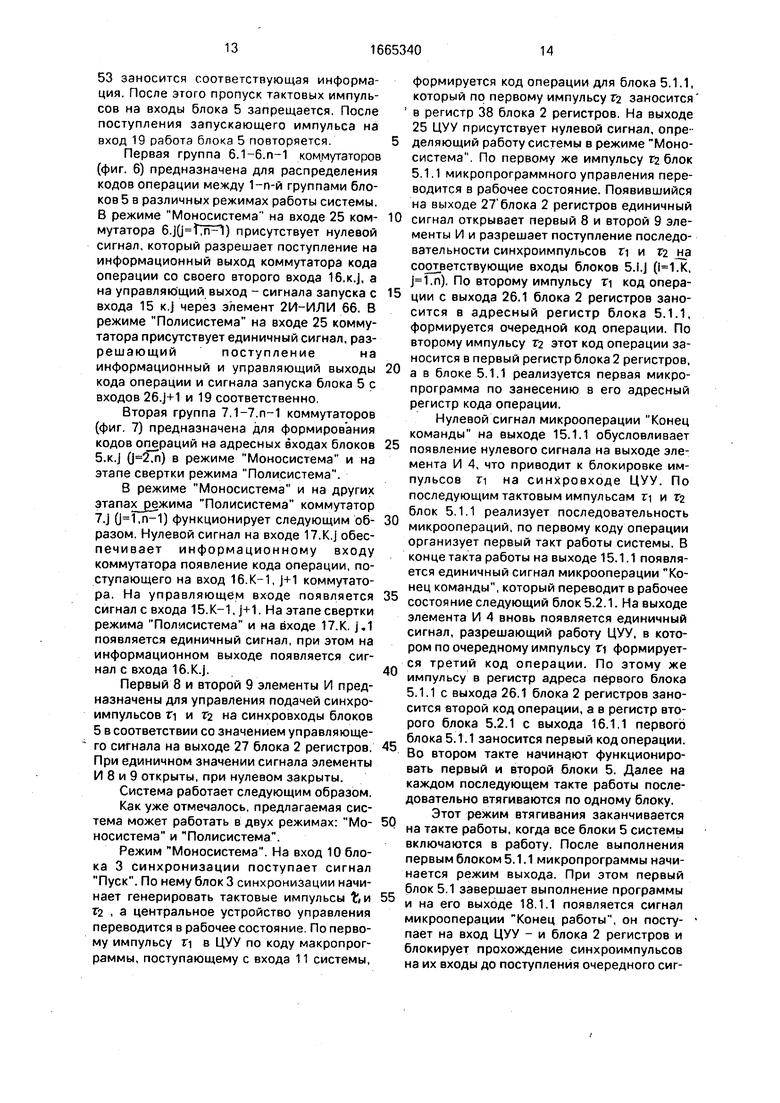

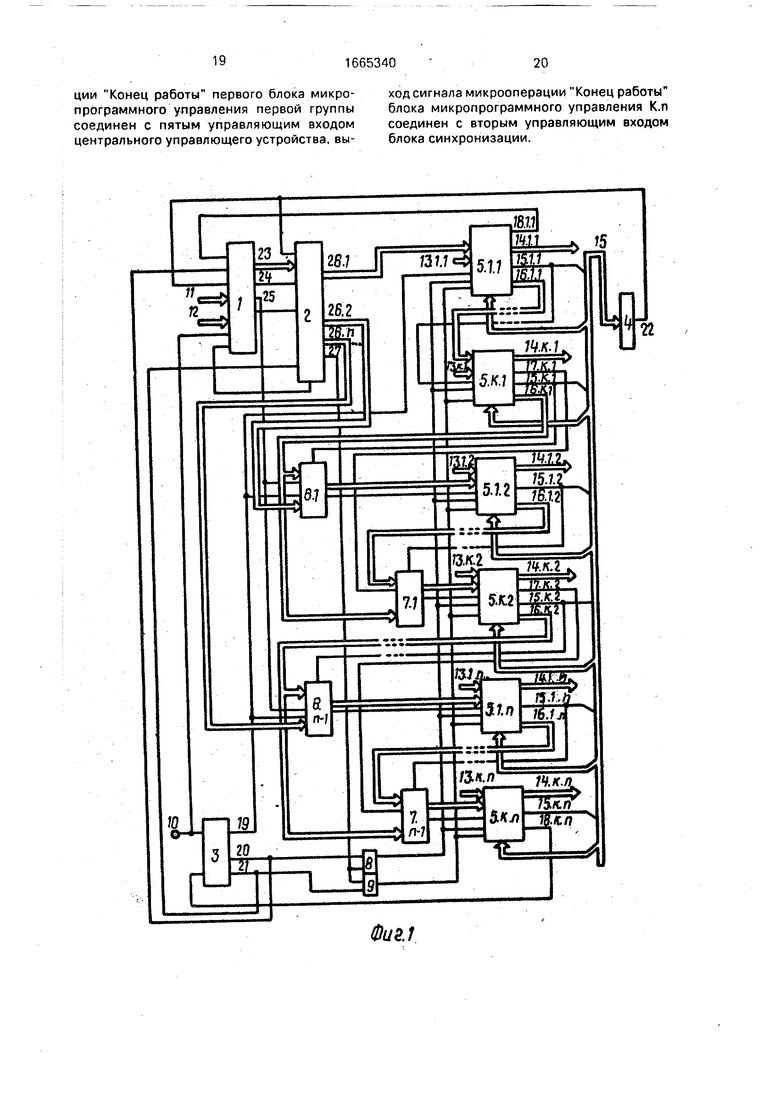

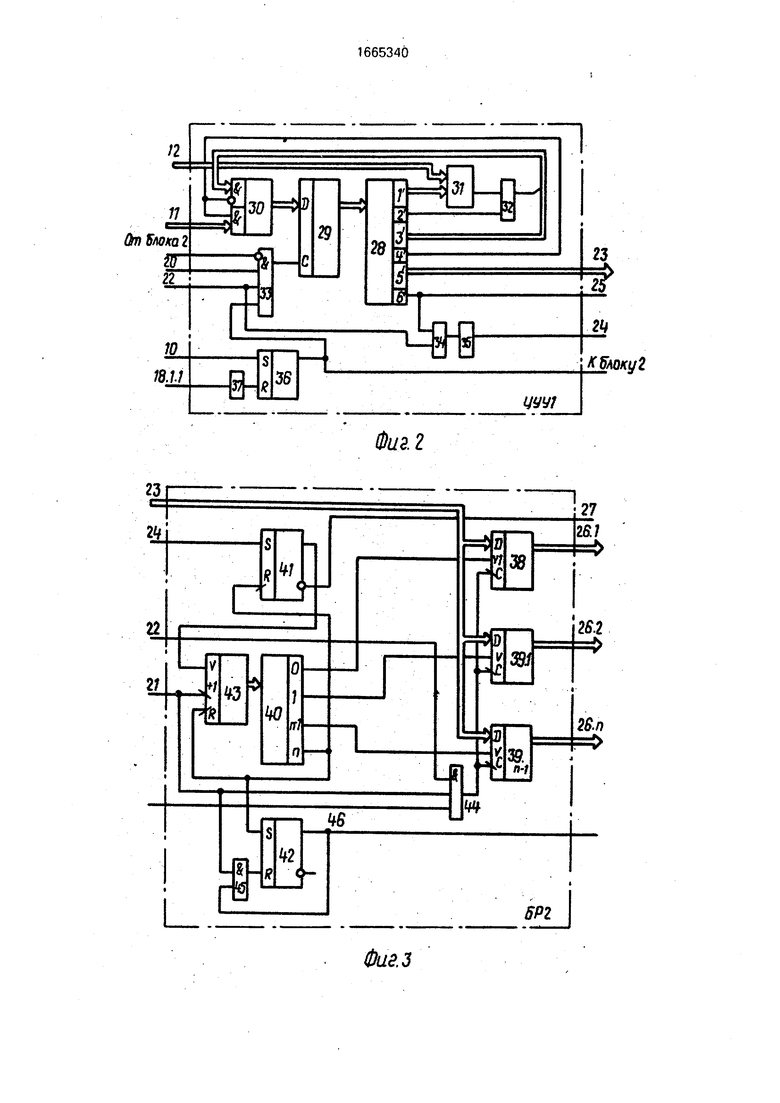

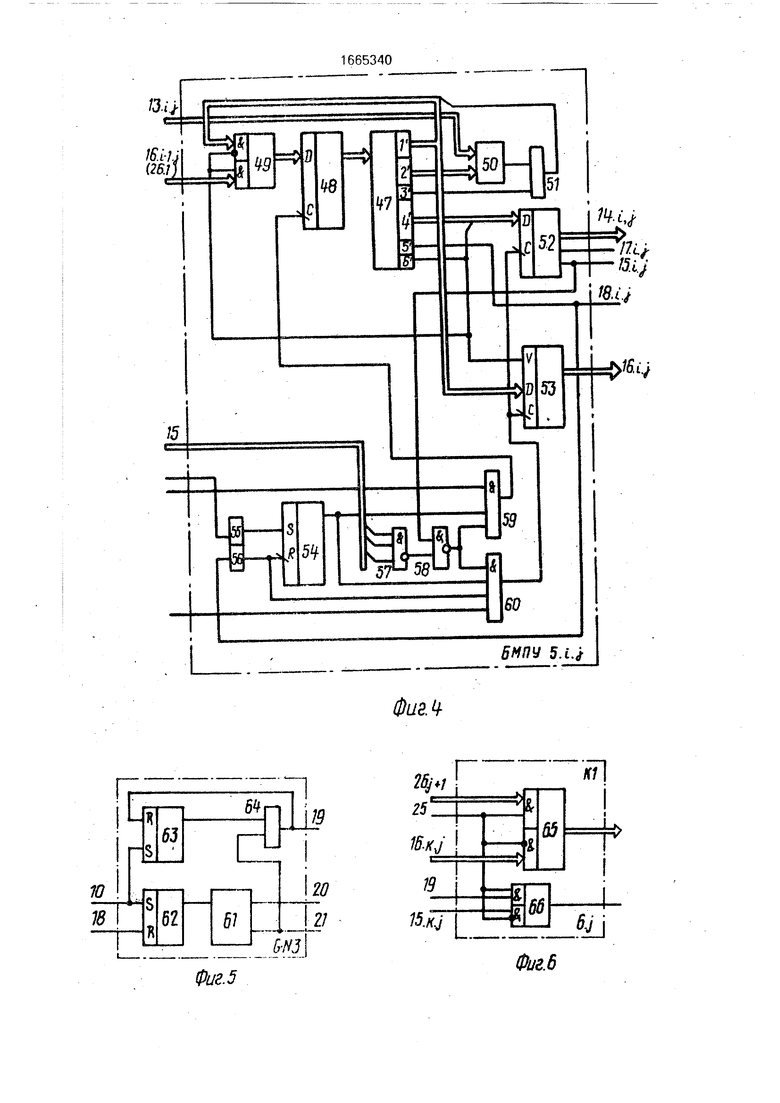

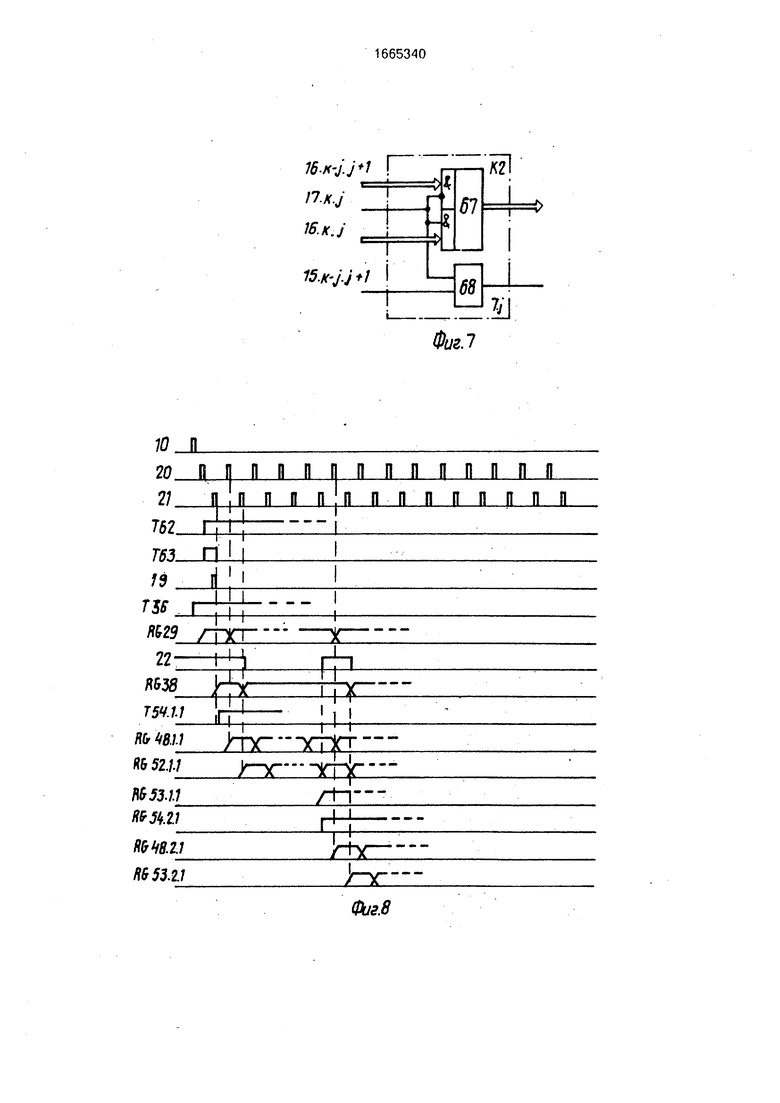

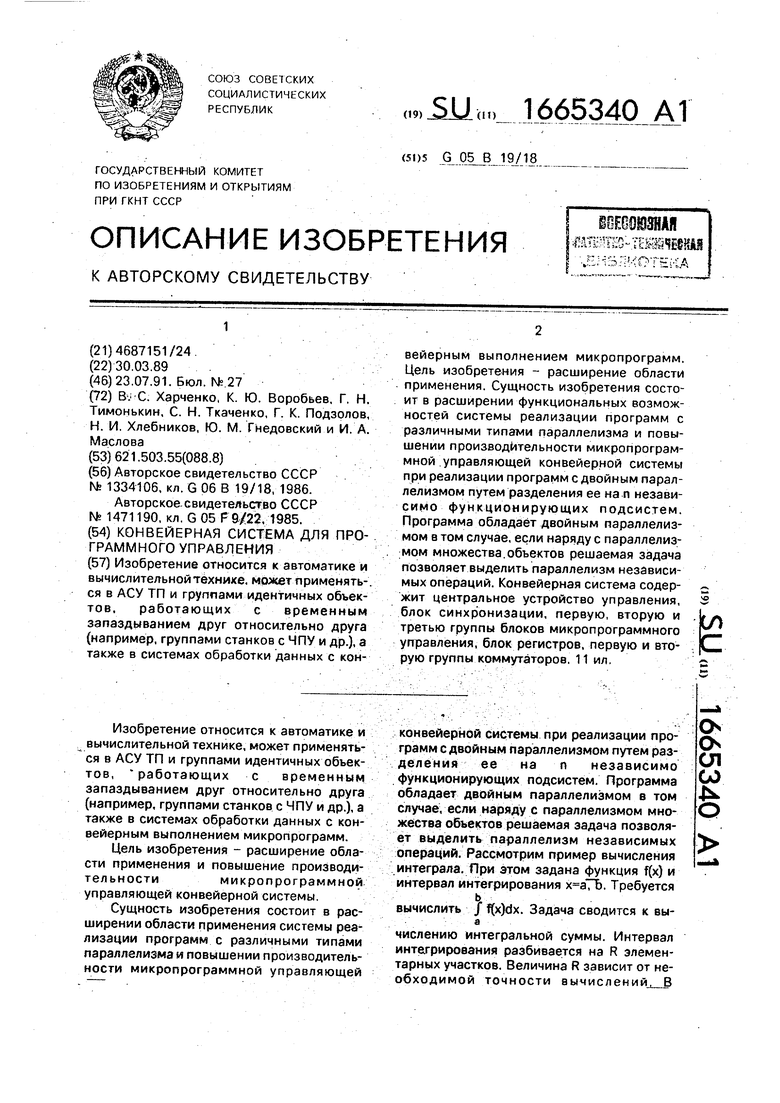

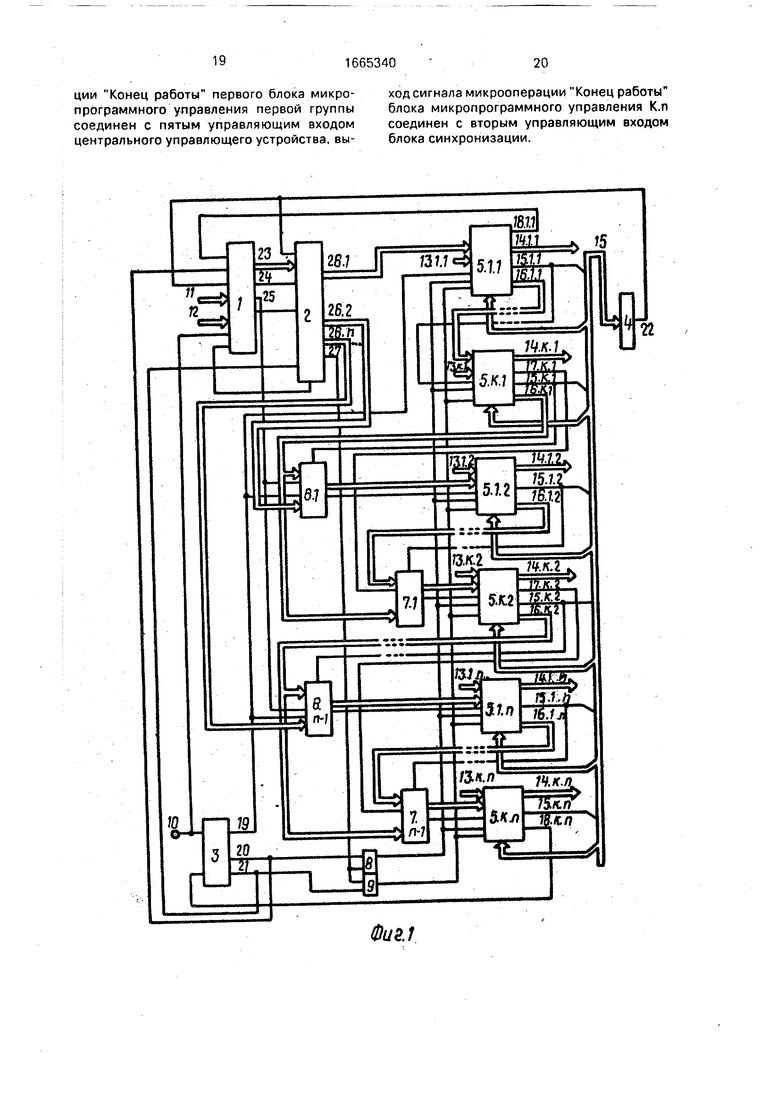

На фиг. 1 представлена функциональная схема системы; на фиг. 2 - функциональ- ная схема центрального устройства управления; на фиг. 3 - схема блока регистров; на фиг. 4 - схема блока микропрограммного управления; на фиг. 5 - схема блока синхронизации; на фиг. 6 и 7 - схемы первых и вторых коммутаторов соответственно; на фиг. 8 и 9 - временная диаграмма функцио- нирования N-ro блока микропрограммного управления элементов системы в режиме Моносистема ; на фиг. 10 и 11 - то же, в режиме Полисистема.

Конвейерная система для программного управления (фиг. 1) содержит центральное устройство 1 управления (ЦУУ), блок 2 регистров, блок 3 синхронизации первый элемент И 4, группу 5.I.J ( Ж, ,n) блоков микропрограммного управления, первую 6.1-6.П-1 и вторую 7.1 -7.п-1 группы коммутаторов соответственно, второй 8 и третий 9 элементы И, вход 10 пуска системы, вход 11 кода микрооперации, вход 12 логических условий устройства, группу входов 13, i, j (,К. ) логических условий блоков 5, группу выходов конвейерных микроопераций 14.I.J, сигналов микроопераций Конец команды 15.I.J, кода операций 16.1.J, второго управляющего сигнала 17..K.J ().

0

0

5

0

5

0

5

5

0

5

микроопераций Конец работы 18 и блоков 5.К.П соответственно На фиг. 1 также обозначены выходы блока 3 синхронизации: 19

-сигнала запуска блока 5, 20 и 21 - первого и второго тактовых импульсов соответственно; выход 22 элемента И 4; выходы ЦУУ 1: 23

-кодов операции, 24 - сигнала запуска блока 2 регистров, 25 - первого управляющего сигнала; группа 26.1-26.п выходов кодов операции блока 2 регистров и выход 27 третьего управляющего сигнала блока 2 регистров.

Вход 10 системы соединен с четвертым управляющим входом блока 1 и с первым управляющим входом блока 3 синхронизации, выход 19 сигнала запуска которого соединен с первыми управляющими входами блока5.1.1.ипервойгруппы6.1-6.п-1 коммутаторов соответственно, выход 20 первого тактового импульса блока 3 синхронизации соединен с первым входом второго элемента И 8 и синхровходом блока 1, выход 21 второго тактового импульса блока 3 синхронизации соединен с первым входом третьего элемента И 9 и синхровходом блока 2 регистров, вход системы соединен с первым, а вход 12

-с вторым информационными входами блока 1 соответственно, выход 22 элемента И 4 соединен с вторым управляющим входом блока регистров и с управляющим входом блока 1, информационный выход 23 которого соединен с информационным входом блока 2 регистров, выход 24 блока 1 соединен с первым управляющим входом блока 2 регистров, выход 25 блока 1 соединен с вторыми управляющими входами первой группы 6.1-б.п коммутаторов, третий управляющий выход блока 1 соединен с третьим управляющим входом блока 2 регистров, информационные выходы 26.1-26.п блока 2 регистров соединены с адресным входом первого блока 5.1.1 и первыми информационными входами группы 6.1-6.П-1 первых коммутаторов соответственно, выход 27 блока 2 регистров соединен с вторыми входами второго 8 и третьего 9 элементов И, выходы которых соединены с первыми и вторыми синхровходами группы блока 5.I.J (иТТк ), второй управляющий выход блока 2 регистров соединен с вторым управляющим входом блока 1, группа входов 13.I.J (.К, .n) соединена с вторыми информационными входами групп соответствующих блоков 5.1.J, группа выходов 14.I.J (, ) соответствующих блокоь 5 является группой выходов конвейерного управления системы, выходы 15.1.J и 16.I.J, где .K-2, .n, соответствующих блоков 5 соединены с управляющими и первыми управляющими входами блоков 5.1+1.j, выходы

17.K-1.J и 16.K-1J, .п соединены с первыми управляющими и информационными входами второй группы 7.J-1 коммутаторов, выходы 15.К-1.1 и 16.К-1.1 соответствующего блока 5 соединены с управляющими и информационными входам блока5.К.1, выходы 15.K.J и 17.KJ, 1, соответствующих блоков соединены с третьими управляющими входами первой группы 6.J коммутаторов и вторыми управляющими входами второй группы 17.J ком- -.мутатсшов соответственно, выходы 16.K.J .п-1) соответствующих блоков соединены с вторыми информационными входами первых 6.J и вторых 7.J коммутаторов, выходы 15.К-1.1 и 16.К-1.1 блока 5.К-1.1 соединены с управляющим и первыми информационными входами блоков 5.К.1, информационные, и управляющие выходы первых 6.J .п-1) коммутаторов соединены с первыми информационными и управляющими входами блоков 5.1. j + 1, информационные и управляющие выходы вторых 7.j ) коммутаторов соединены с первыми информационными и управляющими входами блоков 5.K.J+1, выходы 15 сигналов микроопераций Конец команды каждого блока 5.а.Ь из группы блоков 5.I.J, где , .n, соединены с группой входов сигналов микроопераций Конец команды всех блоков 5.I.J, для которых I т а, j b, выходы сигналов микроопераций Конец команды всех 5.LJ блоков , .n) соединены с входами элемента И 4, выход 18.1.1 блока 5.1.1 соединен с пятым управляющим входом блока 1, выход 18.К п блока 5.К.П соединен с вторым управляющим входом блока 3 синхронизации.

Центральное устройство 1 управления (фиг. 2) содержит блок 28 памяти с полями: 1 - кода логических условий, 2 - модифицируемого разряда адреса, 3 - немодифицируемого разряда адреса микрокоманды, 4 -микрооперации Конец команды, кода операции, 6 - первого управляющего сигнала, регистр 29 адреса, коммутатор 30 адреса, мультиплексор 31, элемент ИЛИ 32, первый 33 и второй 34 элементы И, первый одновибратор 35, RS-триггер 36 и второй одновибратор 37.

Вход 11 кода операции соединен с первым информационным входом коммутатора 30 адреса, выход поля 4 блока 28 памяти - с первым прямым и вторым инверсным управляющими входами коммутатора 30, выход поля 1 блока 28 памяти - с управляющим входом мультиплексора 31, вход 12 - с информационным входом мультиплексора 31, выход которого соединен с первым входом

элемента ИЛИ 32, выход поля 3 блока 28 памяти соединен с вторым входом элемента ИЛИ 32, выход которого соединен с входом модифицируемого разряда адреса второго

информационного входа коммутатора 30, выход поля 3 блока 28 памяти - с входом немодифицируемых разрядов адреса второго информационного входа коммутатора 30, выход которого соединен с информацион0 ным входом регистра 29, вход 20 соединен с первым входом элемента И 33, вход 22 - с вторыми входами элементов И 33 и И 34, третий управляющий вход ЦУУ соединен с третьим инверсным входом элемента И 33,

5 вход 10-с S-входом триггера 36, вход 18.1.1

-с входом второго одновибратора 37, выход которого соединен с R-входом триггера 36, единичный выход которого соединен с четвертым входом элемента И 33, выход кото0 рого соединен с синхровходом регистра 29, выход которого соединен с информационным входом блока 28 памяти, выход поля 6 которого является выходом 25 ЦУУ 1 и соединен с первым входом элемента И 34, вы5 ход которого соединен с входом первого одновибратора 35, выход последнего является выходом 24 сигнала запуска блока 2 регистров, выход поля 5 блока 28 памяти является выходом 23 кодов операций ЦУУ 1.

0Блок 2 регистров (фиг. 3) содержит регистр 38, группу 39.1-39.п-1 регистров, дешифратор 40, первый 41 и второй 42 RS-триггеры, счетчик 43, первый 44 и второй 45 элементы И, прямой выход 46 триггера

5 42.

Информационный вход 23 блока регистров соединен с информационными входами регистра 38 и группы 39.1-39.п-1 регистров, вход 21 соединен с первым входом второго

0 45 и вторым входом первого 44 элементов И, а также со счетным входом счетчика 43, вход 22 соединен с первым входом первого элемента И 44, вход 24 соединен с S-входом триггера 41, третий управляющий вход бло5 ка 2 регистров соединен с вторым входом элемента И 44, выход которого соединен с входом синхронизации регистра 38 и rpyrf- пы 39.1-39.n-1 регистров, выходы дешифратора 40 соединены: нулевой - с

0 управляющим входом регистра 38.1 (п-1)-й

-с управляющими входами группы 39.1- ЗЭ.п-1 регистров соответственно, n-й выход дешифратора 40 соединен с R-входом счетчика 43, S-входом триггера 42 и R-входом

5 триггера 41, прямой выход которого соединен с управляющим входом счетчика 43, а инверсный - с выходом 27 блока 2 регистров, выход счетчика 43 соединен с информа- цитонным входом дешифратора 40, прямой выход 46 триггера 42 соединен с управляющим выходом блока 2 регистров и вторым входом элемента И 45, выход которого соединен с R-входом триггера 42, выходы 26.1- 26.п регистра 38 и группы регистров 39.1-39.n-1 соответственно являются выхо- дами кодов операций.

Каждый блок 5.IJ (фиг. 4) содержит блок 47 памяти с полями: V- немодифицируемых разрядов адреса очередной микрокоманды, 2 - кода логических условий. 3 - модифициру- емого разряда адреса, 4 - кода микроопераций, 5 - сигнала микрооперации Конец работы, сигнала микрооперации Конец команды ; регистр 48, коммутатор 49, мультиплексор 50, элемент ИЛИ 51, регистры 52 и 53, триггер 54, первый и второй 56 одновиб- раторы, первый 57 и второй 58 элементы И- НЕ, первый 59 и второй 60 элементы И.

Первый информационный вход блока 5 соединен с первым информационным вхо- дом коммутатора 49, второй вход 13.I.J .n) блока 5 соединен с информационным входом мультиплексора 50, вход 15 сигналов микрокоманд Конец команды соединен с группой 1-(К, N) входов элемента И-НЕ 57, вход 19 - с входом первого одно- вибратора 55, выход которого соединен с S-входом триггера 54, вход 20 - с первым входом первого элемента И 59, вход 21 - с первым входом второго элемента И 60, вы- ход поля 1 блока 47 памяти соединен с входами немодифицируемых разрядов адреса второго информационного входа коммутатора 49 и информационным входом регистра 53, выход поля 2 - с управляющим входом мультиплексора 50, выход которого соединен с входом элемента ИЛИ 51, выход поля 3- с вторым входом элемента ИЛИ 51, выход которого соединен с входом модифицируемого разряда первого информацией- ного входа коммутатора 49, выход поля 4- с информационным входом регистра 52, выход поля 5 является выходом 18 блока 5 и соединен с входом одновибратора 56, выход которого соединен с R-входом триггера 54 и четвертым входом элемента И 60, выход поля 6 соединен с информационным входом регистра 52, управляющим входом регистра 53, групповым выходом 15 блока 5, первым прямым и вторым инверсным входа- ми коммутатора 49, выход которого соединен с информационным входом регистра 48, единичный выход триггера 54 соединен с вторыми входами первого 59 и второго 60 элементов И соответственно,, выход элемен- та И-НЕ 57 соединен с первым входом элемента И-НЕ 58, выход которого соединен с третьими входами первого 59 и второго 60 элементов И, выход первого элемента И 59 соединен с синхровходом регистра 48, выход которого соединен с информационным входом блока 47 памяти, выход второго элемента И 60 соединен с синхровходами регистров 52 и 53, первый управляющий выход регистра 52 соединен с вторым входом и является выходом 15.I.J блока 5. информационный и второй управляющие выходы первого регистра 52 являются выходами 14.I.J и 17.I.J блока 5 соответственно, выход второго регистра 53 является выходом 16.I.J блока.

Блок 3 синхронизации (фиг. 5) содержит генератор 61 тактовых импульсов, первый 62 и второй 63 RS-триггеры и элемент И 64. Вход 10 пуска системы соединен с R-входом первого 62 и S-входом второго 63 триггеров, вход 18 соединен с S-входом первого триггера 62, единичный выход которого соединен с управляющим входом генератора 61 тактовых импульсов, первый выход которого соединен с вторым входом элемента И 64 и является выходом 20 первого импульса синхронизации, второй выход генератора является выходом 21 второго импульса синхронизации, единичный выход триггера 63 соединен с первым входом элемента И 64, выход которого соединен с R-входом триггера 63 и выходом 19 блока 3 синхронизации.

Каждый коммутатор 6.J из первой группы 6.1-6.П-1 коммутаторов (фиг.6) содержит элементы 2 И-ИЛИ 65 и 66. Вход 26.J+1 соединен с первым информационным входом элемента 2И-ИЛИ 65, вход 16.K.J - с вторым информационным входом элемента 2И- ИЛИ 65, вход 25 - с первым прямым и вторым инверсным входами элемента 2И-ИЛИ 65, выход которого является информационным выходом коммутатора, вход 15.K.J соединен с первым прямым входом элемента 2 И-ИЛИ 66, вход 19 - с первым входом элемента 2 И-ИЛИ 66, выход которого является управляющим выходом коммутатора.

Каждый коммутатор 7.J из второй группы 7.1-7.П-1 коммутаторов (фиг. 7) содержит элемент 2 И-ИЛИ 67 и элемент ИЛИ 68, вход 16.К-1, J+1 соединен с первым, а вход 16.K.J - с вторым информационными входами элемента 2 И-ИЛИ 67 соотвественно, вход 17.K.J соединен с первым входом элемента ИЛИ 68, первым инверсным и вторым прямым входами элемента 2 И-ИЛИ 67, выход которого является информационным выходом коммутатора, вход 15.K-1.j-H соединен с вторым входом элемента ИЛИ 68, выход которого является выходом управляющего сигнала коммутатора 7.J.

Центральное устройство 1 управления предназначено для организации работы всех блоков системы в соответствии с макропрограммой посредством выдачи последовательности кодов операции.

ЦУУ 1 работает следующим образом.

Импульс команды Пуск с входа 10 переводит триггер 36 в единичное состояние. При наличии на втором и четвертом прямых и третьем инверсном входам элемента И 33 соответствующих разрешающих сигналов через него разрешается поступление на синхровход регистра 29 первого тактового импульса. По этому тактовому импульсу при наличии разрешающего сигнала на управляющих входах коммутатора 30 с входа 11 ЦУУ 1 в регистр 29 заносится код операции макропрограммы. По принятому коду операции на выходе блока 28 памяти формируется соответствующая данному коду операции микрокоманда, т.е. код операции выступает как адрес первой микрокоманды выполняемой макропрограммы. Если выполняемая программа предусматривает функционирование системы в режиме Полисистема, то на выходе поля 6 блока 28 памяти появляется единичный управляющий сигнал. Этот сигнал поступает на выход 25 ЦУУ 1 и на один из входов элемента И 34, на второй его вход поступает управляющий сигнал, свидетельствующий об исходном состоянии всех блоков 5. При этом на выходе элемента И 34 появляется единичный сигнал, по которому одновибратор 35-формирует импульс, поступающий на выход 24 ЦУУ 1. Если выполняемая программа предусматривает режим работы Моносистема, то на выходе проля б единичный сигнал отсутствует и формирование импульса не происходит.

Адрес очередной микрокоманды поступает на второй информационный вход коммутатора 30, при этом на выходе поля 4% блока 28 памяти присутствует нулевой сигнал микрооперации Конец команды, который разрешает его прохождение на выход коммутатора. По очередному первому тактовому импульсу в регистр 29 заносится адрес очередной микрокоманды. Код операции блоков 5 поступает с выхода поля 51 блока 28 памяти на выход 23 ЦУУ 1.

По очередному тактовому импульсу при наличии соответствующих разрешающих сигналов работа устройства повторяется. Исключение составляет режим реализации микрокоманды условного перехода. В этой ситуации адрес следующей микрокоманды формируется с учетом значений логических условий, поступающих на вход 12. Это происходит следующим образом. С выхода поля 1 блока 28 памяти на второй вход мультиплексора 31 поступает код логического условия, а на первый его вход поступает значение проверяемого логического условия.

Мультиплексор 31 реализует логическую функцию

...KsXi+KiK2K3...K3X|+KiK2K3...KsXs, где конъюнкции KiKzKs.-.Ks задают код про- веряемого логического условия KI { KjCKi} SHogad

d - число логических условий; Xj - значения логических условий на входе 12,,d.

В зависимости от значения функции Y

на выходе мультиплексора 31 на элементе ИЛИ 32 i модифицируется: младший нулевой разряд адреса микрокоманд. При следующей реализуется микрокоманда по адресу

А, поступившему с выхода поля З1 адреса блока 28 памяти, а при реализуется микрокоманда по адресу А+1. Таким образом, осуществляется реализация условного перехода. При появлении на входе 18.1.1 единичного сигнала одновибратор 37 формирует импульс, переводящий триггер 36 в нулевое состояние, при этом блокируется прохождение импульсов через элемент И 33.

Блок2 регистров предназначендля приема, хранения и одновременной выдачи кодов операций 1-п группам блоков 5. Одновременно блок 2 регистров может хранить п кодов операций. Он может работать

в двух режимах: приема и выдачи-кода операции лишь по одному, первому каналу, что соответствует режиму Моносистема. и распределения кодов операций по п каналам одновременно - режим Полисистема.

В режиме Моносистема триггеры 41 и 42 обнулены, работа счетчика 43 запрещена, на нулевом выходе дешифратора 40 присутствует единичный сигнал, разрешающий занесение информации с входа 23 в регистр

38. Тактовый импульс TI - может попасть на синхровход регистра только при условии наличия на входе 22 и третьем управляющем входе блока регистров единичных сигналов, открывающих элемент И 44, т.е. при

условии, что все блоки 5 системы завершили выполнение команды, а блок 1 включен в работу. При нарушении этого условия, тактовый импульс Г2 с входа 22 через заблоки- рованный элемент И 44 пройти не сможет,

и в регистр 38 информация занесена нз будет.

В режим Полисистема блок 2 регистров переходит при поступлении на вход 24 импульса запуска. Он поступает на S-вход

триггера 41 и переводит его в единичное состояние, после чего разрешается работа счетчика 43. По импульсу Тг в регистр 38 заносится первый код операции, а на выходе счетчика 43 появляется комбинация, которой соответствует единичный сигнал на первом выходе дешифратора. Последующему импульсу Тг в регистр 39.1 заносится второй код операции, а единичный сигнал появляется на втором выходе дешифратора, и т.п. По n-му импульсу Г2 n-й код операции заносится в регистр 39.(п-1), а появившийся на n-м выходе дешифратора 40 сигнал обнуляет триггер 41 и счетчик 43, а триггер 42 переводится в единичное положение. При этом на выходе 46 триггера 42 и инверсном выходе триггера 41, а равно на втором управляющем выходе и на выходе 27 блока регистров соответственно появляются единичные сигналы. При поступлении очередного импульса Т2 триггер 42 обнуляется и единичный сигнал на его прямом выходе исчезает. По этому же импульсу n-й код операции заносится в регистр 38, но это не существенно, так как к этому времени коды операции уже будут считаны в адресные регистры соответствующих блоков 5, а нулевой сигнал на входе 18.1.1 заблокирует элемент И 44. Блок регистров переходит в ждущий режим работы. При поступлении очередного импульса запуска на вход 24 работа блока регистров повторяется.

Блок 3 (фиг. 5) предназначен для синхронизации работы системы по первому ri и второму Т2 тактовым импульсам, а также для формирования сигнала запуска блока 5.

В исходном состоянии триггеры 62 и 63 обнулены, генерация тактовых импульсов отсутствует. Поступающий на вход 10 импульс запуска переводит первый 62 и второй 63 триггеры в единичное состояние. Появившийся на единичном выходе триггера 62 сигнал разрешает работу генератора 61. Сигнал с прямого выхода второго триггера 63 разрешает прохождение импульсов через элемент И 64. Второй тактовый импульс, пройдя через элемент И 64, поступает на R-BXOJI триггера 63 и обнуляет его. Таким образом, на выходе блока синхронизации формируется сигнал запуска блоков 5. Генератор 61 формирует последовательность тактовых импульсов ri и тг на выходах 20 и 21 соответственно. Поступающий на вход 18 сигнал обнуляет триггер 62 и прекращает работу генератора 61. Очередной сигнал Пуск возобновляет работу блока 3 синхронизации.

Элемент И 4 предназначен для определения гю.сигналам микроопераций Конец команды блоков 5.I.J (, ) конца такта работы блока 5.

Блоки 5J.J (НГХ ) микропрограммного управления идентичны. Блок 5.IJ микропрограммного управления предназначен для организации микропрограммного упг

равления в i.j-м канале управления. Он функционирует следующим образом. В исходном состоянии все элементы памяти обнулены. Поступающий на вход 19 блока 5

сигнал проходит на вход одновибратора 55, который формирует по нему импульс, поступающий на S-вход триггера 54 и переводящий его в единичное состояние. Сигнал с единичного выхода триггера 54 поступает

0 на вторые входы первого 59 и второго 60 элементов И. Если все остальные блоки 5 закончили выполнение команд, о чем будет свидетельствовать нулевой сигнал на выходе первого элемента И-НЕ 57, поступающий

5 на один вход второго элемента И-НЕ 58, на второй вход которого поступает единичный сигнал микрооперации Конец команды этого блока 5, единичный сигнал с выхода элемента И-НЕ 58 поступает на третий вход

0 первого 59 и второго 60 элементов И. Таким образом, через эти элементы по их первым входам разрешается прохождение первого и второго тактовых импульсов с входов 20 и 21 соответственно. По первому тактовому

5 импульсу в регистр 48 с адресного входа через коммутатор 49 заносится код операции. По принятому коду операции на выходе блока 47 памяти микрокоманд формируется соответствующая данному коду операции

0 микрокоманда, т.е. код операции выступает как адрес первой микрокоманды выполняемой микропрограммы.

На выходе поля 6 блока 47 памяти появляется нулевой сигнал Конец команды.

5 При этом адрес очередной микрокоманды с выхода поля 1 блока памяти через коммутатор 49 поступает на информационный вход регистра 48. Операционная часть микрокоманды поступает на информационный вход

0 регистра 52 и по второму тактовому импульсу считывается в него. По первому тактовому импульсу адрес очередной микрокоманды заносится в регистр 48, по нему с блока 47 памяти считывается очеред5 ная микрокоманда. По второму тактовому импульсу работа блока 5 повторяется. Реализация условного перехода происходит ана- логично центральному устройству управления. Последняя микрокоманда вы0 полняемой микропрограммы содержит единичную микрооперацию Конец команды, по сигналу которой с выхода поля 1 блока 47 памяти в регистр 53 заносится код операции для следующего блока 5. По окончании работы бло5 ка 5 на выходе блока 47 памяти появляется единичный сигнал микрооперации Конец работы, поступающий на вход одновибратора 56, Поданному сигналу одновибратор 56 формирует импульс, переводящий триггер 54 в нулевое состояние, и по этому же импульсу в регистры 52 и

53 заносится соответствующая информация. После этого пропуск тактовых импульсов на входы блока 5 запрещается. После поступления запускающего импульса на вход 19 работа блока 5 повторяется.

Первая группа 6.1-6.П-1 коммутаторов (фиг. 6) предназначена для распределения кодов операции между 1-п-й группами блоков 5 в различных режимах работы системы. В режиме Моносистема на входе 25 ком- мутатора e..n-1) присутствует нулевой сигнал, который разрешает поступление на информационный выход коммутатора кода операции со своего второго входа 16.K.J, а на управляющий выход - сигнала запуска с входа 15 K.J через элемент 2И-ИЛИ 66. В режиме Полисистема на входе 25 коммутатора присутствует единичный сигнал, разрешающийпоступлениенаинформационный и управляющий выходы кода операции и сигнала запуска блока 5 с входов 26.J+1 и 19 соответственно.

Вторая группа 7.1-7.П-1 коммутаторов (фиг. 7) предназначена для формирования кодов операций на адресных входах блоков 5.K.J ,п) в режиме Моносистема и на этапе свертки режима Полисистема.

В режиме Моносистема и на других этапах |эежима Полисистема коммутатор 7J (.n-1) функционирует следующим об- разом. Нулевой сигнал на входе 17.K.J обеспечивает информационному входу коммутатора появление кода операции, поступающего на вход 16.К-1, j+1 коммутатора. На управляющем входе появляется сигнал с входа 15.К-1, j+1. На этапе свертки режима Полисистема и на входе 17.К. j,1 появляется единичный сигнал, при этом на информационном выходе появляется сигнал с входа 16.K.J.

Первый 8 и второй 9 элементы И предназначены для управления подачей синхроимпульсов Г| и Г2 на синхровходы блоков 5 в соответствии со значением управляющего сигнала на выходе 27 блока 2 регистров, При единичном значении сигнала элементы И 8 и 9 открыты, при нулевом закрыты.

Система работает следующим образом,

Как уже отмечалось, предлагаемая система может работать в двух режимах: Мо- носистема и Полисистема.

Режим Моносистема. На вход 10 блока 3 синхронизации поступает сигнал Пуск. По нему блок 3 синхронизации начинает генерировать тактовые импульсы t,n TZ , а центральное устройство управления переводится в рабочее состояние. По первому импульсу т в ЦУУ по коду макропрограммы, поступающему с входа 11 системы,

формируется код операции для блока 5.1.1, который по первому импульсу TI заносится в регистр 38 блока 2 регистров. На выходе 25 ЦУУ присутствует нулевой сигнал, определяющий работу системы в режиме Моносистема. По первому же импульсу тг блок 5.1.1 микропрограммного управления переводится в рабочее состояние. Появившийся на выходе 27 блока 2 регистров единичный сигнал открывает первый 8 и второй 9 элементы И и разрешает поступление последовательности синхроимпульсов ri и Т2 на соответствующие входы блоков 5.I.J (.К. .n). По второму импульсу TI код операции с выхода 26.1 блока 2 регистров заносится в адресный регистр блока 5.1.1, формируется очередной код операции. По второму импульсу Г2 этот код операции заносится в первый регистр блока 2 регистров, а в блоке 5.1.1 реализуется первая микропрограмма по занесению в его адресный регистр кода операции.

Нулевой сигнал микрооперации Конец команды на выходе 15.1.1 обусловливает появление нулевого сигнала на выходе элемента И 4, что приводит к блокировке импульсов ti на синхровходе ЦУУ. По последующим тактовым импульсам п и Тг блок 5.1.1 реализует последовательность микроопераций, по первому коду операции организует первый такт работы системы, В конце такта работы на выходе 15.1.1 появляется единичный сигнал микрооперации Конец команды, который переводит в рабочее состояние следующий блок 5.2.1. На выходе элемента И 4 вновь появляется единичный сигнал, разрешающий работу ЦУУ, в котором по очередному импульсу п формируется третий код операции. По этому же импульсу в регистр адреса первого блока 5.1.1 с выхода 26.1 блока 2 регистров заносится второй код операции, а в регистр второго блока 5.2.1 с выхода 16.1.1 первого блока 5.1.1 заносится первый код операции. Во втором такте начинают функционировать первый и второй блоки 5. Далее на каждом последующем такте работы последовательно втягиваются по одному блоку.

Этот режим втягивания заканчивается на такте работы, когда все блоки 5 системы включаются в работу. После выполнения первым блоком 5.1.1 микропрограммы начинается режим выхода. При этом первый блок 5.1 завершает выполнение программы и на его выходе 18.1.1 появляется сигнал микрооперации Конец работы, он поступает на вход ЦУУ - и блока 2 регистров и блокирует прохождение синхроимпульсов на их входы до поступления очередного сигнала Пуск системы. На втором такте завершает работу второй блок 5.2.1, на третьем - блок 5.3.1 и т.п., на К n-м такте режима Выход завершает работу последний блок 5.К.П, сигнал на его выходе 18.К.п останавливает блок 3 синхронизации. Система переходит в ждущий режим работы. При поступлении на вход 10 импульса Пуск ее работа в режиме Моносистема повторяется.

Режим Полисистема. На вход 10 поступает сигнал Пуск. По нему блок 3 синх- ронизации начинает генерировать последовательность тактовых импульсов TI и Та , а на синхровход ЦУУ разрешается поступление импульсов ri. По первому импульсу г-| в адресный регистр ЦУУ заносится код макропрограммы, в блоке памяти формируется первый код операции. На выходе 25 появляется единичный управляющий сигнал, переводящий систему в режим Полисистема. Формируемый на выходе 19 блока 3 синхронизации импульс запуска поступает на управляющий вход блока 5.1.1, а через первую группу 6.1-6.П-1 коммутаторов на управляющие входы первых блоков 5.1.J (,п) 2.п-й групп. Таким образом, в работу сразу включается п групп блоков 5, начинающих одновременно реализовать п участков программы. По импульсу с выхода 24 блок 2 регистров переводится в режим Полисистема. На выходе 27 блока 2 регистров появляется нулевой сигнал, запрещающий прохождение импульсов синхронизации на входы блоков 5. По первым п импульсам TI в ЦУУ формируются по п кодов операций, которые заносятся в блок 2 регистров по п импульсам тг . на его выходах 26.1-26.п появляются п кодов операций для первой - n-й групп блоков 5 соответственно. После поступления на вход 21 блока 2 регистра n-го импульса Г2 на его первом 27 и втором управляющих выходах появляются единичные сигналы.

Первый блокирует прохождение (п+1}-го импульса т на вход ЦУУ и исчезает после появления на входе 21 блока 2 регистров (п+1)-го импульса Г2 . Второй открывает элементы И 8 и 9, чем разрешает поступлдение (п+1)-х и последующих импульсов п и TI на соответствующие синхровходы блоков 5.1.J (.п). По n-му импульсу г в адресные регистры блоков 5.1.J считываются соответствующие коды операций, по (п + 1)-му импульсу Т2 сформированные по ним коды конвейерных микроопераций появляются на выходах 14.1.j блока 5.1.J )- На их выходах 15.1.J исчезает сигнал микроопераций Конец команды, что приводит к появлению нулевого сигнала на выходе 22 элемента И 4, который блокирует синхровходы ЦУУ и блока 2 регистров на время выполнения группой блоков 5.1 J ) соответствующих команд. Когда на выходе 22 элемента И 4 вновь появится единичный сигнал, что свидетельствуем о завершении каждым из блоков 5.1 .j .п) соответствующих команд, на синхровход ЦУУ вновь поступает импульс п , импульс на выходе 24 ЦУУ заводит блок 2 регистров, и повторяется процесс формирования п кодов макроопераций, как описано. В следующем такте работы системы в работу включаются блоки 5.I.J

.n). Каждая группа блоков 5 функционирует как система в режиме Моносистема. При выполнении программ, ориентированных на параллелизм независимых ветвей, работа системы заканчивается после

выполнения блоками 5.K.J ) последних микрокоманд.

Рассмотрим режим выхода системы из режима Полисистема для программ с параллелизмом смежных операций - этап

свертки. Он начинается в момент реализации блоками 5.K.j() последних микрокоманд (1-п)-го участков макропрограммы. По импульсу ri на выходах 18.K.J блоков 5.K.J , п-1) появляются сигналы микроопераций Конец работы, по которым блокируется устройство 1 и блоки 5.KJ. По импульсу Т2 на выходе 17.К.1 блоков 5.К. 1 появляется единичный управляющий сигнал, поступающий на второй управляющий вход коммутатора 7.1. После этого на управляющем выходе коммутатора 7.1 появляется сигнал, запускающий блок 5.К.2. Адрес очередной микрокоманды поступает с выхода 16.К.1 через коммутатор 7.1 на вход блока 5.К.2. По

импульсу Г| адрес заносится в блок 5.К.2 , где формируется микрокоманда. После выполнения блоками 5.К.2 команды на выходе 18.К.2 появляется сигнал микрооперации Конец работы, который блокирует синхровходы блоков 5.К.2, а на выходе 17.К.2 появляется управляющий сигнал, поступающий на управляющий вход коммутатора 7.2. При этом включается в работу блок 5.К.З, он реализует команду по коду операции с выхода 16.К.2 соответствующего блока 5, т.е. в режиме свертки последние k-e блоки 5(1-п}- х групп с помощью коммутаторов 7.1-7.п-1 организуются в конвейерную систему, в которой в каждом такте работает только один

блок; на первом - блок 5.К.1, на втором блок 5.К.2, на n-м - блок 5.К.П. После того,

как на выходе 18.К.П блока б.К.п появится

сигнал микрооперации Конец работы,

этот блок выключается из работы. По этому

же сигналу прекращается работа блока 3 синхронизации. Система переходит в исходное состояние. При поступлении сигнала Пуск на вход 10 системы она начнет функционировать в одном из двух описанных режимов.

Ф о р м у л а и з о б р е т е н и я Конвейерная система для программного управления, содержащая центральное устройство управления, блок синхронизации, группу блоков микропрограммного управления, первый элемент И, причем вход пуска системы соединен с первым управляющим входом блока синхронизации, выход первого тактового импульса которого соединен с входом синхронизации центрального устройства управления, входы операций и логических условий системы соединены с первым и вторым информационными входами центрального устройства управления соответственно, входы логических условий конвейерных микропрограмм системы соединены с входами логических условий блоков микропрограммного управления, выходы микроопераций Конец команды которых соединены с соответствующим входом первого элемента И, выход которого соединен с первым управляющим входом центрального устройства управления, отличающаяся тем, что, с целью расширения области применения, система содержит блок регистров, первую и вторую группы коммутаторов, второй и третий элементы И, вход пуска системы соединен с вторым управляющим входом центрального устройства управления, выход сигнала запуска блока синхронизации соединен с первыми управляющими входами первого блока микропрограммного управления и с входами коммутаторов первой группы, выход первого тактового импульса блока синхронизации соединен с первым входом второго элемента И, второй выход тактового импульса блока синхронизации соединен с первым входом третьего элемента И и Синхровходом блока регистров, выход первого элемента И соединен с первым управляющим режимом входом блока регистров, информационный выход центрального устройства управления соединен с . информационным входом блока регистров, первый управляющий выход центрального устройства управления соединен с вторым управляющим режимом входом блока регистров, второй управляющий выход центрального устройства управления соединен с вторыми управляющими входами коммутаторов первой группы, третий управляющий выход центрального устройства управления

соединен с третьим управляющим режимом входом блока регистров, с первой по n-е группы информационных выходов блока регистров соединены с группой адресных входов первого блока микропрограммного управления и с группой первых информационных входов коммутаторов первой группы соответственно, первый управляющий выход блока регистров соединен с вторыми входа0 ми второго и третьего элементов И, выходы которых соединены соответственно с первыми и вторыми синхровходами всех блоков микропрограммного управления, второй управляющий выход блока регистров соеди5 нен с вторым управляющим входом центрального устройства управления, первая группа информационных выходов блока микропрограммного управления является группой выходов конвейерного управления

0 системы, вторая группа информационных и первая группа управляющих выходов блока микропрограммного управления i.j(, КЧ К - число блоков микропрограммного управления в группе, п - число групп)соеди5 нены с группой адресных и с первой группой управляющих входов блоков микропрограммного управления соответственно, первая группа управляющих и первая группа информационных выходов блока микропрог0 раммного управления K-1.J (,ri) соединены с первыми группами управляющих и информационных входов коммутаторов второй группы J-1, вторые группы управляющих и информационных выходов

5 блоков микропрограммного управления К- 1.1 соединены с группами управляющих и информационных входов блоков микропрограммного управления К. 1, первый и второй управляющие выходы блоков K.J

0 .п-1) соединены с третьими управляющими входами коммутаторов первой группы и с вторыми управляющими входами коммутаторов второй группы соответственно, первый информационный выход блока программного управления K.J (,n-1) соединен с вторыми информационными входами коммутаторов первой и второй групп, информационные и управляющие вы- ходы коммутаторов первой группы0 1 .п- О

0 соединены с первыми группами информационных и управляющих входов блока микропрограммного управления K.j+1, выходы сигналов микроопераций Конец команды каждого блока микропрограммного управ5 ления ab из группы блока микропрограммного управления . где ,К, .n, соединены с группой входов сигналов микроопераций Конец команды всех блоков микропрограммного управления i.j, для ко- торых . , выход сигнала микрооперации Конец работы первого блока микропрограммного управления первой группы соединен с пятым управляющим входом центрального управлющего устройства, выход сигнала микрооперации Конец работы блока микропрограммного управления К.п соединен с вторым управляющим входом блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142834A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1120326A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1133595A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1280629A1 |

Изобретение относится к автоматике и вычислительной технике, может применяться в АСУ ТП и группами идентичных объектов, работающих с временным запаздыванием друг относительно друга /например, группами станков с ЧПУ и др./, а также в системах обработки данных с конвейерным выполнением микропрограмм. Цель изобретения - расширение области применения. Сущность изобретения состоит в расширении функциональных возможностей системы реализации программ с различными типами параллелизма и повышении производительности микропрограммной управляющей конвейерной системы при реализации программ с двойным параллелизмом путем разделения ее на N независимо функционирующих подсистем. Программа обладает "двойным параллелизмом" в том случае, если наряду с параллелизмом множества объектов решаемая задача позволяет выделить параллелизм независимых операций. Конвейерная система содержит центральное устройство управления, блок синхронизации, первую, вторую и третью группы блоков микропрограммного управления, блок регистров, первую и вторую группы коммутаторов. 11 ил.

ФиМ

1 глф

OfrCS99t

«Э

t«i

СХ

t

J

.

n.K.J

10 JL

20t| П И Я П П П П П П П И П П

21П П П П П j П П П П П П П П П

762I

I

ТбЗО191

W-JC

-L

АРС

22 I

Я&38

f

Г5././|

Я& Ш /fy

Я652Л/-У

flfJJ././

№5k.U

№М.и

М 53.2.1

-

Фуг. 7

5Г1ПУ

Фиг. 9

w П

бппу

к.п

ч

ч

к.г

А

12 R (R+K-1)(R+K-2+%)

Фиг. ю

| Устройство программного управления | 1986 |

|

SU1334106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1471190A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-07-23—Публикация

1989-03-30—Подача