Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве многотактного устройства микропрограммно-, го управления при построении вычислительных машин и систем, а также АСУ технологическими процессами.

Известно микропрограммное устройство управления,содержащее регистр адреса, блок памяти микропрограмм, регистр микрокоманд, дешифраторы, блок управления длительностью микропрограммного такта (I .

Недостатком данного устройства является его низкая надежность, обусловленная формированием окончания микротакта на секционных линиях задержки.

Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство, содержащее регистр адреса, последовательно соединенные генератор тактовых импульсов, блок вь еления тактовых сигналов, последовательно соединенные первый дешифратор адреса, первый запоминающий блок, первый регистр микрокоманд, разделенный на п операционных полей и одно адресное поле,а каждое из опер шионцы

полей содержит управляющую и информационные части,последовательно соединенные второй дешифратор адреса,второй запоминающий блок,второй регистр микрокоманд, содержащий гшреснбе поле и п операционных полей, п управлякйдих дешифраторов, первую группу блоков элементов И, первый блок элементов ИЛИ, вторую группу блоков эле10ментов И, первую группу блоков элементов ИЛИ, блок элементов 2 И - ИЛИ, п дешифраторов кодов операций, триг- , гер управления 2 . .

Недостатком этого устройства явля15ется низкое быстродействие, обусловленное использованием при многотактных микрокомандах микротактов постоянной длины независимо от тактов выдачи последней микрооперации.

20

Время выполнения микропрогрёшмы, состоящей из NQ однотактных микрокоманд и N многотактных микрокоманд равно

Т,NoTo М„Т„. тТо N,,

25

где Tjj - дhитeльнocть нанотакта)

m - количество нанотактов в мвкротакте. Таким образом, прототип обладает

30 большой временной избыточностью, которая обусловлена тем, что независимо от того, в каком нанотакте вьщается последняя микрооперация в многотактной микрокоманде, время ее выполнения равно Т,

Цель изобретения - повышение быст родействия устройства.

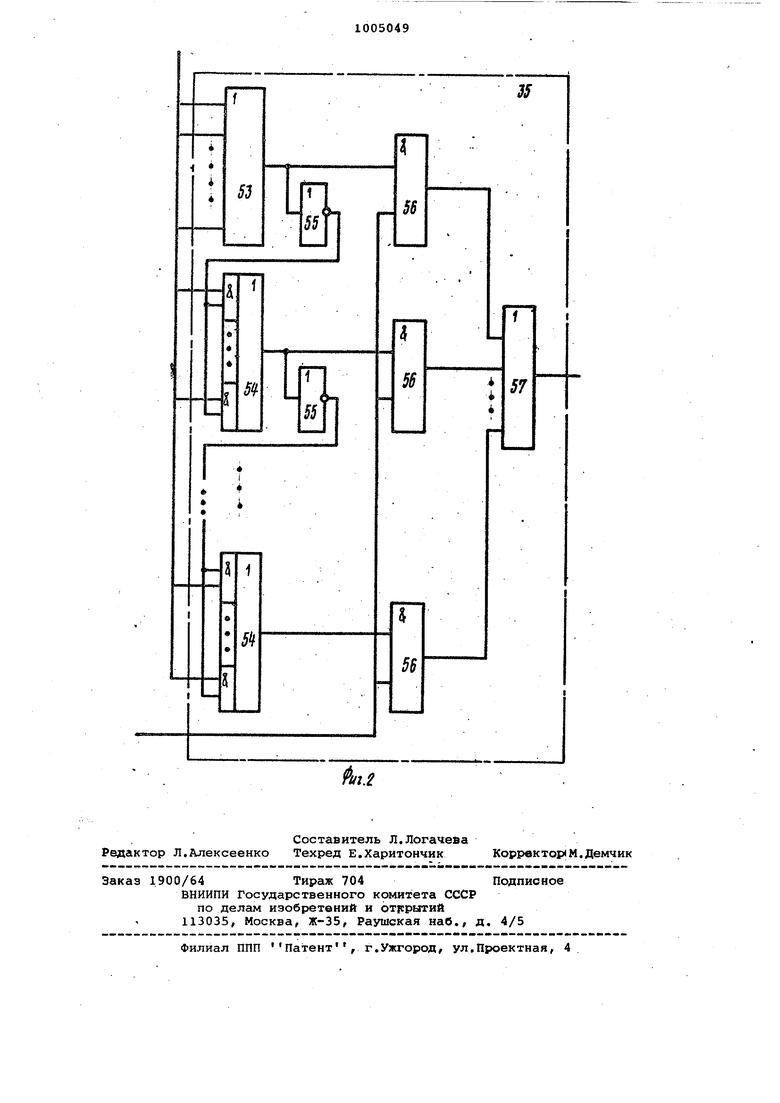

Поставленная цель достигается тем что в устройство,, содержащее регистр адреса, генератор тактовых импульсов учетчик, дешифратор, последовательно соединенные первый дешифратор адреса, первый блок памяти, первый регистр микрокоманд, последовательно соединенные второй дешифратор адреса, второй блок памяти, второй регистр микрокоманд управляющих де- , шифраторов, первую группу блоков элементов И, первый блок элементов ИЛИ, вторую г.руппу блоков элементов И, первую группу блоков элементов ИЛИ, блок элементов 2И-ИЛИ, п дешифраторов кодов операций, триггер управления, причем выход регистра адреса соединен с информационными вхорами управляющих дешифраторов соответственно, выходы которых соединены с первыми входами блоков элементов И первой группы, вторые входы . которых соединены с выходом дешифратора, информационный вход которого соединен свыходом счетчика, счетный вход которого Подключен к выходу генератора тактовых импульсов и управляющему входу дешифратора, выходы блоков элементов И первой группы через блок элементов ИЛИ соединены с синхронизирующими входами дешифраторов кодов операций соответственно, операционные выходы второго регистра микрокоманд соединены с первыми входами блоков элементов И второй группы, вторые входы которых соединены с нулевым выходом триггера управле-iния, выходы блоков элементов И второй группы соединены с первыми входами блоков элементов ИЛИ первой группы, выходы которых соединены соответственно с информационными входами дешифраторов- кодов операций, выходы которых подключены к выходу микроопераций устройства, дополнительно введены третья группа блоков элементов И, первый, второй, третий и четвертый элементы И, первый, второй, третий, четвертый и -пятый элементы ИЛИ, первый, второй и третий элементы задержки, первый, второй, третий, четвертый, пятый, шестой и седьмой одновибраторы, блок выделения максимального нанотакта, триггер формирования микротакта, причем первый вход первого элемента И соединен с единичным выходом триггера управления, первый вход второго элемента И соединен с нулевым выходом триггера управления, вторые входы первого и второго элементов И соединеньа с единичным входом триггера формирования микротакта и через первый одновибратор соединены с входом обнуления управляющих разрядов первого регистра микрокоманд адресный выход которого соединен с первым входом первой, группы входов блока элементов 2И-ИЛИ, второй вход первой группы входов которого соединен с единичным выходом триггера управления/ нулевой выход которого соединен ,с первым входом второй группы входов блока элементов 2И-ИЛИ, второй вход второй группы входов которого соединен с адресным выходом второго регистра микрокоманд, выход блока элементов 2И-ИЛИ соединен с первым инфор 1ационн лм входом регистра адреса, -второй информационный вход которого соединен с входом начального адреса устройства, треты входы первого и второго элементов И соединены с выходом дешифратора,- выходы первого и второго элементов И соединены с сйнхронизирующими входами соответственно первого и второго дешифраторов адреса и с первым и вторым входами первого элемента ИЛИ, выход которого через первый элемент згщержки соединен с нулевым входом триггера формирования микротакта, единичный вход которого соединен с выходом второго- элемента ИЛИ, первый вход которого соединен с выходами блоков элементов И второй группы, второй вход - с выходом блока выделения максимального нанотакта, первый вход которого соединен с выходами дешифраторов управления, второй вход - с выходом дешифратора, третий вход второго элемента ИЛИ соединен с входом начального адреса устройства, выход метки типа микрокоманды второго регистра микрокоманд соединен с входами второго и третьего одновибраторов, выход второго одновибратора соединен с первым входом третьего элемента ИЛИ, выход третьего одновибратора соединен с первым входом четвертого элемента ИЛИ, выход метки типа микрокоманды первого регистра микрокоманд соединен с входами четвертого и пятого одновибраторов, выход четвертого одновибратора соединен с вторым входом четвертого элемента ИЛИ, выход пятого одновибратора соединен с вторым входо м третьего элемента . ИЛИ, выходы меткИ ветвления первого и второго регистров микрокоманд соединены с входами пятого элемента ИЛИ, выход которого соединен с первыми входами третьего и четвертого элементов И, второй вход третьего элемента И соединен с инверсным входом четвёртого элемента И и подключен к входу логических условий устройства, выход третьего элемента И через шестой одновибратор соединен с третьим входом третьего элемента ИЛИ, выход которого через второй элемент эгщержки соединен с единичным входом триггера управления, нулевой вход которого соединен с выходом третьего эле мента задержки, вход которого соединен с выходом третьего элемента ИЛИ, Информационные выходы первого регист ра микрокоманд соединены с первыми входами.блоков элементов И третьей труппы,вторые входы которых соединен с единичным выходом триггера управле ния, а выходы - с вторыми входами блоков элементов ИЛИ группы. Кроме того, блок выделения максиглального нанотакта содержит первый .и второй элементы ИЛИ, группу (m-l) элементов И-ИЛИ (т - число нанотактов в микротакте), группу (т-1) элементов НЕ, группу m элементов И, при чем входы первого элемента ИЛИ и пер вые входы (m-l) элементов И-ИЛИ Труп пы соединены с первым входом блока, вторые входы (т-1) элементов И-ИЛИ группы соединены с выходами (т-1) элементов НЕ группы/соответственно, выход первого.элемента ИЛИ и выходы (m-l) элементов группы соединены с первыми входами соответствующих m элементов И группы, вторые входы которых соединены с вторым вхо дом блока, выходы первого элемента ИЛИ и (ш-1) элементов И-ИЛИ группы, кроме последнего, соединены с входами соответствукхадх (т-1) элементов НЕ группы, выходы m элементов И группы соединень с входами второго элемента ИЛИ, выход которого подключен к выходу блока. На фиг.1 изображена схема предлагаемого микропрограммного устройст ва управления; на фиг. 2 - функциональная схема блока выделения максимального нанотакта. Предлагаемое устройство содержит (фиг. 1) генератор 1 тактовьрс импуль сов, счетчик 2, блок 3 элементов . 2И-ИЛИ, вход 4 начального адреса, уст ройства, регистр 5 адреса, первый элемент И б, первый дешифратор) 7 адреса, первый блок 8 памяти, первый регистр 9. микрокоманд/ дешифратор 10 управлякицие поля-11 информационные поля 12,-адресное поле 13, поле 14 метки типа микрокоманды и поле 15 метки ветвления, первый одновибратор 16,.управляющие дешифраторы 17, первую группу блоков 18 элементов И, первый блок 19 элементов ИЛИ, третью группу блоков 20 элементов И, первую группу блоков 21 элементов ИЛИ, дешифраторы 22 кодов операции, выходы 23 микроопераций устройства, второй элемент И 24, второй дешифратор 25 сщреса,. второй блок 26 памяти, второй регистр 27 микрокоманд, содержащий информационные поля 28, адресное поле 29, поле 30 метки типа микрокоманды, поле 31 метки ветвления, первь й элемент ИЛИ 32, первый элемент 33 задержки, вторую группу бло ков 34 элементов И, блок 35 выделения максимального нанотакта, второй элемент ИЛИ 36, триггер 37 формирования микротакта, пятый элемент ИЛИ 38, второй одновибратор 39, третий одновибратор 40, четвертый одновибратор. 4 Г, пятый одновибратор 42,. вход Ч3 логических условий устройства, третий элемент И 44, четвертый элемент И 45, шестой одновибратор 46, седьмой одновибратор47,четвертый элемент ИЛИ 48, третий элемент ИЛИ 49, второй элемент 50 эгщержки, третий элемент 51 задержки, триггер 52 управления. Блок 35 выделения максимального нанотакта (фиг. 2) содержит первый элемент ИЛИ 53, группу 54 (m-I) элементов И-ИЛИ (т - число нанотактов в микротакте), группу элементов НЕ 55, группу 56 элементов И, второй элемент ИЛИ 57. Микропрограммное устройство управления работает следующим образом. Каждый микротакт устройства состоит из нанотактов, . В исходном состоянии все элементы памяти находятся в нулевом состоянии, в рёгис р 5 адреса записан адрес начальной однотактной микрокоманды микропрограммы через вход 4 устройства. Одновременно с записью адреса первой микрокоманды сигнал с входа 4 устройства через второй элемент ИЛИ 36 устанавливает триггер формирования такта в единичное состояние и подготавливает второй элемент И 24 для разрешения считывания через второй дешифратор 25 адреса однотактную микроко-. манду, записанную во втором блоке 26, Первый тактовый, импульс, поступающий с выхода дешифратора 10 через второй элемент И 24 на синхровход второго дешифратора 25 адреса, разрешает считывание первой однотактной микрокоманды из второго блока 26 во второй рехистр 27 микрокоманд. В полях 28 записаны коды однотактной микрокома.нды, которые через вторую группу блоков 34 элементов И и через второй блок -21 элементов ИЛИ поступают -на входы соответствующих дешифраторов 22 кодов операций. Сигналом с единичного выхода триггера 37 формирования такта через первый -одновибратор 16 упргшляющие поля 11 первого регистра 9 микрокоманд обнуляются. Нулевые коды управляющих полей 11 поступают на входы управляющих дешифраторов 17, первые выходы которых возбуждаются и через первую группу блоков 18 элементов И и первый блок 19 элементов ИЛИ поступают на синхронизирующие входы дешифраторов 22 кодов операции, на входы которых поступают коды микрооперации первой микрокоманды. На выходах 23 дешифраторов 22 появляются сигналы соответствующих микроопераций. После выдачи однотактной микрокоманды сигналы с выходов блока 34 элементов И посту пают на входы второго элемента ИЛИ 36, сигнал с выхода которого устанав ливает триггер 37 формирования в еди ничное состояние, разрешая тем самым чтение очередной микрокоманды. Кроме операционных частей в полях 28 второго регистра 27 микрокоманд в поле 29 записывается адрес следующей микрокоманды (однотактной или многотактной). В поле 30 метки типа микро команды записывается признак М, причем . 1, если следующая микрокоман да является многота;:тной; О, если следующая микрокоман да является однотактной, В поле 31 метки ветвления записывается признак В, причем fl, если данная микрокоманда яв.шется микрокомандой ветвлиния о в противном случае. Предположим, Следующей микрокоман дой микропрограМ1 1ы является многотак ная микрокоманда. Р. этом случае единичный сигнал с выхода поля 30 метки типа микрокоманды через третий одновибратор 40, четвертый элемент ИЛИ 48 и второй элемент 50 задержки поступает на единичный вход триггера 52 управления и перебрасывает его в единично состояние. Второй элемент 50 задержки необхо дим для задержки переброса триггера 52 управления на время, необходимое для перезаписи адреса следующей микрокоманды из адресного, поля 29 второго регистра 27 микрокоманд через блок 3 элементов 2И-ИЛИ в регистр 5 адреса. Сигнал с единичного выхода триггера 52 управления через первый элемент И б поступает на синхронизирующий вход первого дешифратора 7, разрешая тем самым чтение I TOKрокоманды, записанной в первом запоминающем блоке 8, по адресу регистра 5, Одновременно с чтением многотактной микрокоманды сигнал с синхровхода первого дешифратора 7 адреса через первьай элемент ИЛИ 32 и первый элемент 33 задержки поступает на нулевой вход триггера 37 формирования такта и пе ребрасывает его в нулевое состояние. Первый элемент 33 задержки необходим для осуществления возможности перепи си информации из блоков 8 и 26 в регистры 9 и 27,Переброс триггера 37 формирования такта в нулевое состояние показывает,что начался очередной микротакт и запрещает считывание новой микрокоманды,записанной в.регист ре 5 ашреса. Считанная многотактная микрокоманда записывается в П€грвый регистр 9 микрокоманд, на информационных полях которого записаны управляющие и операционные части микрокоманды. При этом в управляющих полях 11 записаны коды номеров нанотактов, в которых должна быть выполнена соответствую- i щая микрооперация, коды которых записаны в операционных полях 12, Код такта, -в котором должна считываться операционная информация с поля 12, поступает с поля 11 первого регистра 9 микрокоманд на управляющий дешифратор 17. Один из выходов управляющего дешифратора 17, соответствующий коду выдачи микрооперации в данном: нанотакте возбуждается. Сигнал с выхода дешифратора 17 через элемент И первой группы блоков элементов И и элемент ИЛИ первого бло,ка 19 элементов ИЛИ поступает на синхровход дешифратора 22. Операци:онная часть микроопераций данного нанотакта поступает через блок 20 элементов И и блок 21 элементов ИЛИ на вход дешифратора 22 кода операции. На выходе дешифратора 22 появляется сигнал соответствующей микрооперации. Аналогично в соответствующем нанотакте производится считывание информации с каждого из выходов операционных полей 12 в регистры 9 микрокоманд. Адрес очередной микрокоманды с выхода поля 13 через блок 3 элементов 2И-ИЛИ поступает на регистр 5 адреса. Если очередная микрокоманда является многотактной, сигнал с выхода поля М метки типа микрокоманды через четвертый одновибратор 41, четвертый элемент ИЛИ 48 и второй элемент 50 задержки поступает на единичный вход триггера 52 управления.Если очередная микрокоманда является однотактной, сигнал с выхода поля М метки типа микрокоманды через пятый одновибратор 42, третий элемент ИЛИ 49 и третий элемент 51 задержки поступает на нулевой вход триггера 52 и перебрасывает его в нулевое состояние, подготавливая тем самым схему для работы с однотактной микрокомандой , При работе устройства с многотактной микрокомандой сигналы с выходов управляющих дешифраторов 17 поступают на вход блока 35 выделения максимального нанотакта. При этом на первый элемент ИЛИ 53 поступают сигналы с выходов дешифраторов 17, соответствующие кодам максимальньрс нанотактов, в которых вьщаются соответствующие микрооперации. Если в многотактной микрокоманде имеется хоть одна микрооперация, выполняемая в последнем нанотакте, на соответствующем выходе управляющего дешифратора 17 Чюявляется сигнал. Данный сигнал поступает на один из входов первого элемента ИЛИ 53 и после подачи тактового импульса, поступающего с дешифратора 10, проходит через элемент И 56, второй элемент ИЛИ 57 блока 35 и через второй элемент ИЛИ 36 на еди ничный вход триггера 37 формирования такта, перебрасывая его в единичное состояние. Появление сигнала на единичном выходе триггера 37 формирования такта указывает на окончание выполнения данного микротакта и разрешает через /первый элемент И 6 или второй элемент И 24 чтение очередной микрокоманды, адрес которой записан в регистре 5 адреса. Если в т-ом нанотакте нет управляющей информации, сигнал с выхода элемента НЕ 55 подготавливает для опроса первый элемент (т-1) И-ИЛИ 54 на который поступают сигналы с выходов управляющих дешифраторов, соответствующих (т-1) -у нанотакту. (го-1}-м тактовым импульсом производится опрос данного нанотакта. Если для данного нанотакта есть управляющая информация, формируется сигнал окончания микротакта на данном нанотакте. Если в (т-1)-м нанотакте нет управляющей информации, последов;ательно опрашиваются все оставшиеся нанотакты, в которых имеется управляющая информация. Таким образом, сигнал окончания микротакта формируется для максималь ного нанотакта, в котором имеется, уп равляющая информация, записанная в операционных полях 12 первого регист ра 9 микрокоманд. Если очередная микрокоманда (одно тактная или многотактная) является микрокомандой ветвления, на соответствукяцем .выходе поля ветвления 15 ил 31, появляется сигнал, который через пятый элемент ИЛИ.38 поступает на входы третьего и четвертого элементов И 44 и 45. В зависимости от при нака логических условий, поступающе го на вход 43 устройства, триггер 52 управления устанавливается в то или иное состояние. При этом призна логических условий формируется следующим образом ГI, если очередная микрокоман 1да является многотактной; |0, если очередная микрокоман ;а является однотактной. После этого с приходом очередног го сигнала первого нанотакта устрой ство функционирует аналогично описа ному. Применение предлагаемого микропрограммного устройства управления позволит повысить быстродействие по отношению к прототипу на 20%. Формула изобретения 1. Микропрограммное устройство упрайления, содержащее регистр адреса, генератор тактовых импульсов, счетчик, дешифратор, последовательно соединенные первый дешифратор адреса, первый блок памяти и первый регистр микрокоманд, последовательно соединенные второй дешифратор , второй блок, памяти и второй регистр микрокоманд, блок элементов ИЛИ, первую и вторую группы блоков элементов. И, группу блоков элементов ИЛИ, блок элементов 2И-ИЛИ, п дешифраторов кодов операций, триггер управления, причем выход регистра адреса соединен с информационными входами первого и второго дешифраторов адреса, управляющие выходы первого регистра микрокоманд соединены с информационными входами управляющих.дешифраторов, соответственно, выходы которых соединены с первыми входами блоков элементов И первой группы, вторые входы Которых соединены с выходом дешифратора, информационнь-; вход которого соединен с выходом счетчика, счетный вход которого подключен к выходу генератора тактовых импульсов и управлякядему входу дешифратора, выходы блоков элементов И первой группы через блок элементов ИЛИ подключены к синхронизирующим входам дешифраторов кодов операции соответственно, операционные выходы второго регистра Микрокоманд соединены с первыми входами блоков элементов И второй группы, вторые входы которых соединены с нулевым выходом триггера управления, выходы блоков . элементов И второй группы соединены с первыми входами блоков элементов ИЛИ группы, выходы которых подключены соответственно к информационным входам дешифраторов кодов операций, выходы которых подключены к выходу микроопераций устройства, о т л и ч U ю щ е е с я.тем, что, с целью повышения быстродействия, оно дополнительно содержит третью группу блоков элементов И, первый, второй, третий и четвертый элементы И, первый, второй, третий,.четвертый и пятый элементы ИЛИ, первый., второй и третий элементы задержки, первый, второй, третий, четвертый, пятый, шестой и седьмой одновибраторы, блок выделения максимального нанотакта, триггер формирования микротакта, причем первый вход первого элемента И соединен с единичным выходся4 триггера управления, первый вход второгоэлемента И соединен с нулевым выходом триггера управления, вторые входы первого и второго элементов И соединены с .единичным выходом триггера . формирования микротакта и через первый одновибратор соединены с входом обнуления управляющих разрй юв регистра микрокоманд, адресный выход которого соединен с первым вх дом первой группы входов блока элементов 2И-ИЛИ, второй вход первой группы входов которого соединен с единичным выходом триггера управления, нулевой выход которого соедине с первым входом второй группы входо блока элементов 2Й-ИЛИ, второй вход второй группы входов которого соеди нён с адресным выходом второго реги стра микрокоманд, а вькод - с первы информационным входом регистра адре са, второй информационный вход кото рого подключен к входу начального адреса устройства, третьи входы пер вого, и второго элементов И соединены с .выходом дешифратора, выходы пе вого и второго элементов И соединены с синхррнизирующими входами первого и второго дешифраторов адреса и с первым и вторым входами первого ..элемента ИЛИ соответственно, выход «ервого элемента ИЛИ через первый элемент задержки соединен с нулевым входом триггера формирования микротакта, едини.чный вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединён с -выходами блоков -элементов И второй группы, второй вход - с выходом бло ка выделения максимального нанотакта, первый вход которого соединен с выходами дешифраторов управления,. вт рой вход - с выходом дешифратора. третий вход второго элемента ИЛИ сое динен с входом начального адреса уст ройства,-, выход метки типа микрокоман ды второго регистра микрокоманд соединен с входами второго и третьего одновибраторов, выход второго одновибратора соединен с первым входом третьего элемента ИЛИ, выход третьего одновибратора соединен с первым входом четвертого элемента ИЛИ, выход метки типа микрокоманды первого регистра микрокоманд соединен с входами четвертого и пятого оцновибраторов, выход четвертого одновибратора соединен с вторым входом четверtore элемента ИЛИ, выход пятого одновибратора соединен с вторым входом третьего элемента ИЛИ, выходы метки ветвления первого и второго регистров микрокоманд соединены с первым и вторь. входами .пятого элемента ИЛИ выход которого соединен с первыми входами третьего и четвертого элементов И, второй вход третьего элемента Н соединен с инверсным входом четвертого элемента И и подключен к входу логических условий устройства, выход третьего элемента И через шестой одновибратор соединен с третьим входом третьего элемента ИЛИ, выход четвертого элемента И через седьмой одновибратор соедйлен с третьим входом четвертого элемента ИЛИ, выход которого через второй элемент задержки соединен с единичным входом триггера управления, нулевой вход которого соединен с выходом третьего элемента задерж1 и, вход которого соединен с выходом третьего элемента ИЛИ, ин.формационные выходы первого регистра микрокоманд соединены с первыми входами блоков элементов И третьей группы, вторые входы которьсс соединены с единичнЬ1м выходом триггера управления, а выходы - с вторыми входами блоков элементов ИЛИ группы, 2. Устройство по п. 1,отличаю щ е е с я тем, что блок вьщеления максимального нанотакта содержит первый и второй элементы ИЛИ, группу (пт-1) элементов И-ИЛИ (rrj- число нанотактов в микротакте), группу (Гп-1) элементов НЕ/ группу fri элементов И, причем входы первого элемента ИЛИ и первые входы (in-l) элементов И-ИЛИ группы соединены с первым входом блока, вторые входы (щ-) элементов И-ИЛИ соединены с выходами (т-1) элементов НЕ группы соответственно, выход первого элемента ИЛИ и выходы (т-1) элементов И-ИЛИ группы соединены соответственно с первыми входа- . ми m элементов И группы, вторые входи которых соединены с вторым входом блока, выходы первого элемента ИЛИ и (тт1-1) элементов И-ИЛИ группы, кроме последнего, соединены с входами (т-1) элементов НЕ группы соответственно, выходы элементов И группы соединены с входами второго элемента ИЛИ, выход которого подключен к выходу блока. Источники информации, принятые во внимание при экспертизе 1.-Авторское свидетельство СССР № 467351, кл. G 06 F 9/22, 1972. 2.Авторское свидетельство СССР по заявке 2765918/18-24, кл. G 06 F 9/22, 1970 (прототип).

k

| название | год | авторы | номер документа |

|---|---|---|---|

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Микропрограммное устройство управления | 1981 |

|

SU945866A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Пикопрограммное устройство управления | 1979 |

|

SU817714A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1168936A1 |

| Устройство для микропрограммного управления | 1983 |

|

SU1198520A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-14—Подача