го дополнительного двухвходового элемента ИЛИ и единичным входом второго триггера управления, единичньй выход которого соединен с входом второго дополнительного двухвходового элемента ИЛИ, второй вход которого п(1цключен череэ элемент задержки к второму входу двухвходового элемента И и единичному выходу первого триггера управления, нулевой выход которого соединен с входом первого трехвходового элемента И, второй вход которого соединен с нулевым выходом второго триггера управления, а третий вход - с управляющим входом организации цикла настройки и входом второго трехвходового элемета И, второй вход которого подключен к выходу второго дополнительного двухвходового элемента ИЛИ, а третий вход - к нулевому выходу триггера фиксации цикла настройки, единичньй вход которого соединен с выходом первого трехвходового элемента И, а нулевой вход - с выходом третьего дополнительного двухвходового элемента ИЛИ, первый вход которого соединен с нулевыми входами трех триггеров управления и входом сброса устройства, а второй вход - с первым тактирующим входом устройства, управляющими входами схем сравнения и синхронизирующими входами первого и второго блоков фиксации кодов настройки, вторые синхронизирующие входы которых подключены к второму . тактирующему входу устройства, третьему входу трехвходового элемента ИЛИ второму входу первого дополнительного двухвходового элемента ИЛИ, вторым синхронизирующим входам третьего и четвертого блоков фиксации кодов настройки и первому входу четвертого дополнительного двухвходового элемента ИЛИ, второй вход которого соединен с третьим тактирующим входом устройства и первыми синхронизирующими входами третьего и четвертого блоков фиксации кодов настройки., а выход - с входами третьего и четвертого трехвходовых элементов И, вторые входы которых соединены соответственно с выходами тревходового элемента ИЛИ и первого дополнительного двухвходового элемента ИЛИ, а третьи входы - с выходами третьего и четвертого блоков фиксации кодов настройки, входы которых соединены соответственно с вторыми информационными входами второй и первой схем сравнения и выходами первого и второго блоков фиксации кодов настройки, каждьй из которых содержит регистр настройки, элемент ИЛИ и два элемента И, причем вход первого элемента И подсоединен к выходу блока фиксации кодов настройки и выходу регистра настройки, второй его вход - к первому синхронизирующему входу блока, а выход первого элемента И - к входу элемента ИЖ, второй вход которого соединен с выходом второго элемента И, вход которого подключен к второму синхронизирующему входу, а второй вход - к входу блока фиксации кода настройки, выход элемента ИЛИ которого соединен с входом регистра настройки, при этом третий информационный полюс устройства соединен с входом первого блока фиксации кода настройки и выходом третьего трехвходового элемента И, четвертьй информационньй полюс - с входом второго блока фиксации кода настройки и выходом четвертого трехвходового элемента И, первьй управляющий выход окончания цикла настройки - с выходом второго трехвходового элемента И, второй управляющий выход окончания цикла настройки - с выходом двухвходового элемента И, а вход предварительной настройки- с единичным входом третье го триггера управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Соединитель многокаскадной коммутационной системы | 1984 |

|

SU1226643A1 |

| Матричный коммутатор | 1985 |

|

SU1309294A1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| Многоканальное устройство контроля температурных режимов инкубаторов | 1983 |

|

SU1157528A1 |

| Устройство для автоматического контроля качества перешлифовки листопрокатного валка на заданный профиль | 1985 |

|

SU1308413A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для измерения параметров многополюсников | 1986 |

|

SU1478147A1 |

ЭЛЕКТРОННЫЙ СОЕДИНИТЕЛЬ ДВОИЧНОЙ СИСТЕМЫ КОММУТАЦИИ, содержащий четыре информационных полюса, два двоичньск элемента коммутации, каждый из которых содержит четьфе ключа, три триггера управления и элемент ИЛИ, выход которого подсое-. динен к единичному входу первого триггера управления, нулевой выход которого соединен с информационными входами первых двух ключей первого двоичного элемента ког-мутадии, нулевой выход второго триггера управления подключен к информационньм входам третьего и четвертого ключей первого двоичного элемента коммутации, в котором .управляющие входы первого и четвертого ключей соединены с нулевым выходом третьего тр иг г ер а. упр а вл ения, единичный выход которого подключен к управляющим входам второго и третьего ключей, причем выход второго ключа соединен с выходом четвертого ключа и управляющими входами первого и четвертого ключей второго двоичного элемента коммутации, а выход третьего ключа - с выходом первого ключа и управляющими входами второго и третьего ключей второго двоичного элемента коммутации, в котором информационные входы первых двух ключей соединены с первым информационным полюсом устройства, а информационные входы остальных двух ключей. с вторым информационным полюсом устройства, третий информационный полюс которого соединен с выходами первого и третьего ключей второго двоичного элемента коммутации, а четвертьй информационный полюс с выходами второго и.четвертого ключей второго двоичного элемента коммутации, отличающийся f f.S2rara тем, что, с целью расширения функциональных возможностей, в него введены дополнительно четыре двухвходовых и один трехвходовый элеe a;sEi мент ИЛИ, четыре трехвходовых и один двухвходовый элемент И, четыре блока фиксации кодов настройки, две схемы сравнения, элемент задержки и триггер фиксации цикла настройки, единичный выход которого подключен к входу трехв-ходового элемента ИЛИ и входу основного двухвходового элемента ИЛИ, второй вход которого соединен-с первым входом двухвходово го элемента И, вторым входом трехвходового элемента ИЛИ и выходом первой схемы сравнения, первый информационньш вход которой подключен к четвертому информационному полюсу .устройства и первому информационному входу второй схемы сравнения, вг 1ход которой соединен с входом перво

1

Изобретение относится к вычислительной технике и может быть использовано для построения параллельных многокаскадных коммутационньк схем

2

в универсальных и проблемных ориентированных вычислительных устройствах высокой проиэводитель,ности. Известен модуль многоканальной коммутирующей системы, содержащий элементы И, элементы ИЛИ, вертикаль ные и горизонтальные входные сигнал ные шины, соединенные с триггерами, матрицу коммутационных узлов lj . Недостаток известного устройства заключается в низкой надежности и уз ких функциональных возможностях. Наиболее близким к предлагаемому по технической сущности, и достигаемому результату является электронный соединитель двоичной системы коммутации, содержащий четыре информацион ных полюса, два двоичных элемента коммутации, каждый из которых содержит четыре ключа, три триггера управ ления и элемент ИЛИ, выход которого подсоединен к единичному входу первого триггера управления, нулевой выход которого соединен с информационными входами первьк двух ключей первого двоичного элемента коммутации, нулевой выход второго триггера управления подключен к информационным входам третьего и четвертого ключей первого двоичного элемента коммутации-, в котором управляющие входы первого и четвертого ключей соединены с нулевым выходом третьего триггера управления, единичный выход которого подключен к управляющим вхо дам второго и третьего ключей,, причем выход второго ключа.соединен с выходом четвертого ключа и управляющими входами первого и четвертого ключей второго двоичного элемента коммутации, а выход третьего ключас выходом перЬого ключа и управляющими входами второго и третьего ключей второго двоичного элемента коммутации, в котором информационные входы первьк двух ключей соединены с первым информационным полюсом устройства, а информационные входы остальных двух ключей - с вторым информационным полюсом ycтpoйctвa, тре тий информационный полюс которого со единен с выходами первого и третьего ключей двоичного элемента коммутации, а четвертый информационный полюс - с выходами второго и четвертого ключей второго двоичного элемента коммутации Ш. Каждый двоичный элемент электрон ного соединителя управляется от ЭВМ которая собирает информацию с остал ных элементов двоичной системы коммутации. В этом случае ЭВМ определяет, в каком состоянии должен находиться каждый электронный соединитель двоичной системы, т.е. реализует алгоритм безблокировочных соединений для полного списка соединений, а после этого переключает каждый соединитель. Поэтому отсутствие в каждом электронном соединителе рассредоточенного децентрали зованного устройства управления, функционирование которого обеспечивает исключение блокировочньк состояний при реализации полного списка соединений, приводит к таким основным недостаткам в известных соединениях, как наличие блокировочных состояний; низкие функциональные возможности и низкий уровень автоматизации процесса поиска путей; дли тельный процесс анализа и настройки каждого электронного соединителя двоичной системы коммутацииJ уменьшение надежности в результате большого количества внешних связей между ЭВМ и электронными соединителями. Цепью изобретения является расширение функциональных возможностей. I Поставленная цель достигается тем, что в электронный соединитель, содержащий четыре информационных полюса, два двоичных элемента коммутации, каждый из которых содержит четыре ключа, три триггера управления и элемент ИЛИ, выход которого подсоединен к единичному входу пер-;, вого триггера управления, нулевой выход которого соединен с информационными входами первых двух ключей первого двоичного элемента ком- мутации, нулевой выход второ триггера управления подключен к информационным входам третьего и четвертого ключей первого двоичного элемента коммутации, в КоторЬм управляюш е входы первого и четвертого ключей соединены с нулевым выходом третьего триггера управления, единичный выход которого подключен к управляющим входам второго и третьего ключей, причем выход второго ключа соединен с выходом четвертого ключа и управляющими входами первого и четвертого ключей второго двоичного элемента коммутации, а выход третье го ключа - с выходом первого ключа

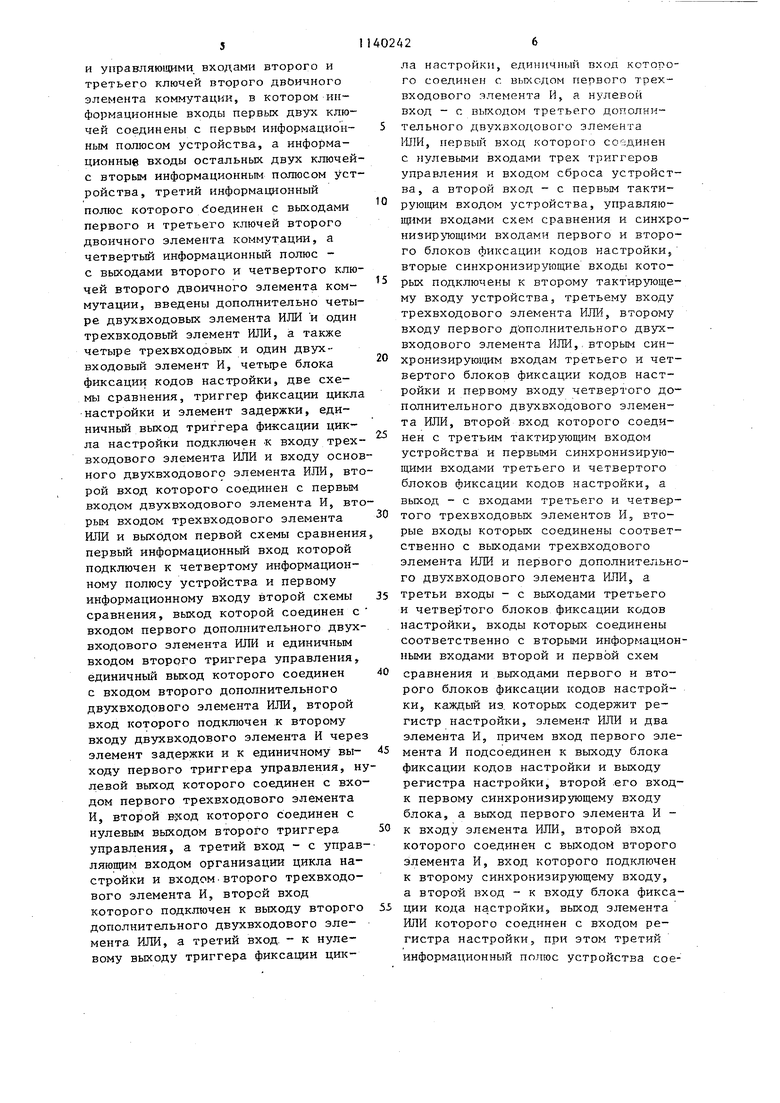

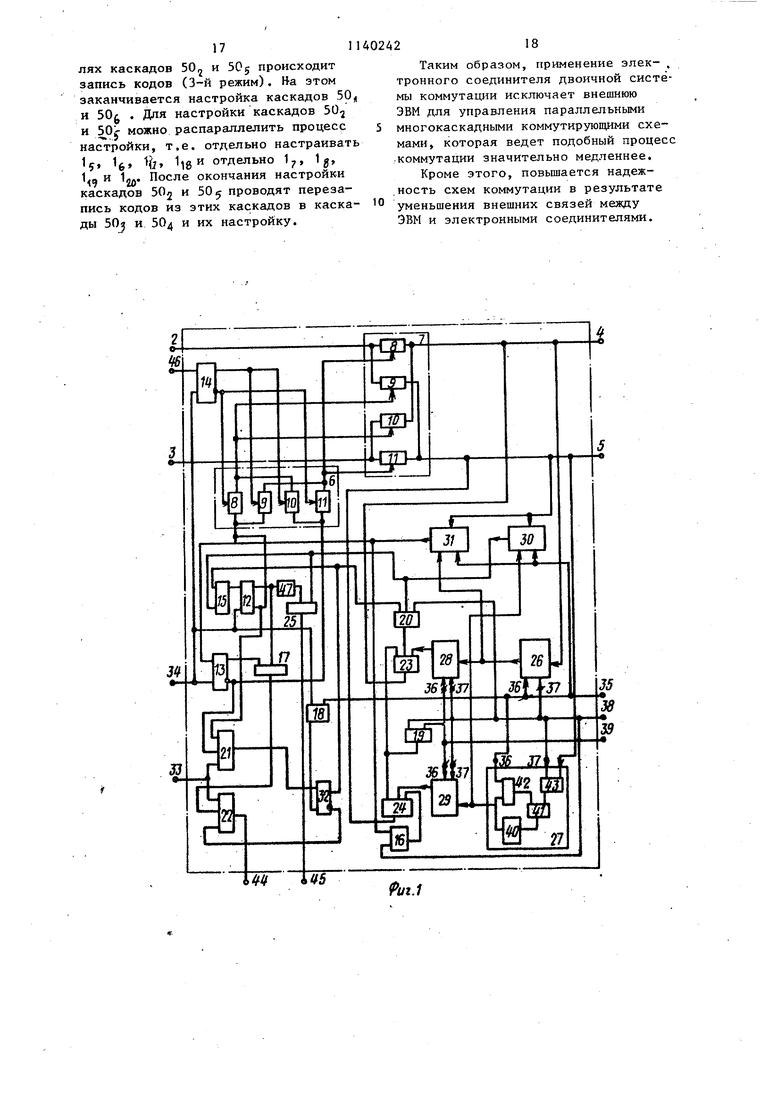

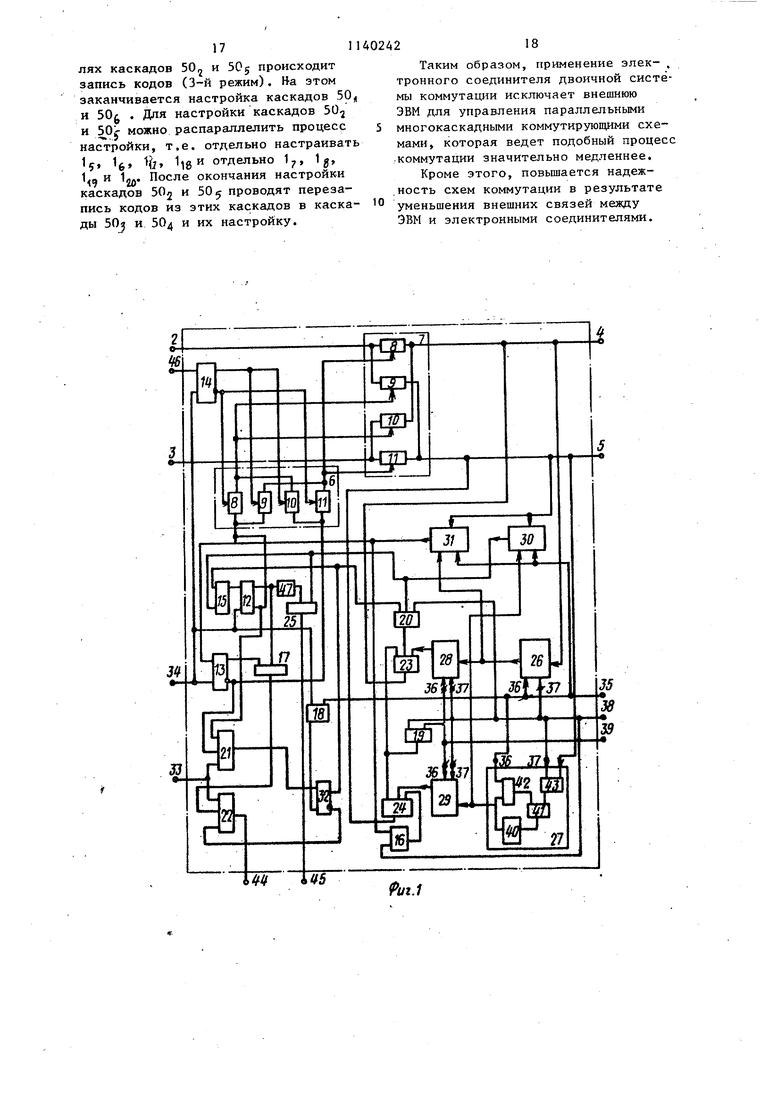

и управляющими входами второго и третьего ключей второго двЬичного элемента коммутации, в котором информационные входы первых двух ключей соединены с первым информационным полюсом устройства, а информационные входы остальных двух ключейс вторым информационным полюсом устройства, третий информационный полюс которого Соединен с выходами первого и третьего ключей второго двоичного элемента коммутации, а четвертьш информационньй полюс с выходами второго и четвертого ключей второго двоичного элемента коммутации, введены дополнительно четыре двухвходовых элемента ИЛИ и один трехвходовый элемент ИЛИ, а также четыре трехвходовых и один двухвходовый элемент И, четыре блока фиксации кодов настройки, две схемы сравнения, триггер фиксации цикла настройки и элемент задержки, единичный выход триггера фиксации цикла настройки подключен к входу трехвходового элемента ИЛИ и входу основного двухвходового элемента ИЛИ, второй вход которого соединен с первым входом двухвходового элемента И, вторым входом трехвходового элемента ИЛИ и выходом первой схемы сравнения первый информационный вход которой подключен к четвертому информационному полюсу устройства и первому информационному входу второй схемы сравнения, выход которой соединен с входом первого дополнительного двухвходового элемента ИЛИ и единичным входом второго триггера управления единичньй выход которого соединен с входом второго дополнительного двухвходового элемента ИЛИ, второй вход которого подключен к второму входу двухвх одового элемента И через элемент задержки и к единичному выходу первого триггера управления, нулевой выход которого соединен с входом первого трехвходового элемента И, второй вкод которого соединен с нулевым выходом второго триггера управления, а третий вход - с управляющим входом организации цикла настройки и входом-второго трехвходового элемента И, второй вход которого подключен к выходу второго дополнительного двухвходового элемента ИЛИ, а третий вход. - к нулевому выходу триггера фиксации цикла настройки, единичный вход которого соединен с выходом первого трехвходового элемента И, а нулевой вход - с выходом третьего дополнительного двухвходового элемента ШШ, первый вход которого соединен с нулевыми входами трех триггеров управления и входом сброса устройства, а второй вход - с первым тактиРУЮ1ЦИМ входом устройства, управляющими входами схем сравнения и синхрнизир тощими входами первого и второго блоков фиксации кодов настройки, вторые синхронизирующие входы которых подключены к второму тактирующему входу устройства, третьему входу трехвходового элемента ИЛИ, второму входу первого дополнительного двухвходового элемента ИЛИ,, вторым синхронизируювд1м входам третьего и четвертого блоков фиксации кодов настройки и первому входу четвертого дополнительного двухвходового элемента ИЛИ, второй вход которого соединен с третьим тактирующим входом устройства и первыми синхронизирующими входами третьего и четвертого блоков фиксации кодов настройки, а выход - с входами третьего и четвертого трехвходовых элементов И, вторые входы которых соединены соответственно с выходами трехвходового элемента ШШ и первого дополнитеошного двухвходового элемента ИЛИ, а третьи входы - с выходами третьего и четвертого блоков фиксации кодов настройки, входы которых соединены соответственно с вторыми информационными входами второй и первой схем сравнения и выходами первого и второго блоков фиксации кодов настройки, каждьй из. которых содержит регистр настройки, элемент ИЛИ и два элемента И, причем вход первого элемента И подсоединен к выходу блока фиксации кодов настройки и выходу регистра настройки, второй .его входк первому синхронизирующему входу блока, а выход первого элемента И к входу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, вход которого подключен к второму синхронизирующему входу, а второй вход - к входу блока фиксации кода настройки, выход элемента ИЛИ которого соединен с входом регистра настройки, при этом третий информационный no.inoc устройства соединен с входом первого блока фиксации кода настройки и выходом третьего трехвходового элемента И, четвертьй информационный полюс - с входом второго блока фиксации кода настройки и выходом четвертого трехвходового элемента И, первый управляющий выход окончания цикла настройки подключен к выходу второго трехвходового элемента И, второй управляющий выход окончания цикла настройки - к выходу двухвходового элемента И, а вход предварительной настройки - к единичному входу третьего триггера управления. На фиг.1 представлена функционал ная схема электронного соединителя двоичной системы коммутации; на фиг,2 - пример двоичной системы коммутации при восьми входах и выходах , вьшолненный на электронных соединителях. Функциональная схема (фиг.1) электронного соединителя 1 двоичной системы коммутации содержит четыре информационных полюса 2-5, два двоичных элемента 6 и 7 коммутации, каждый из которых содержит четьфе ключа 8-11. Устройство (фиг.1) содержит три триггера 12-14.управления и элемент ИЛИ 15, выход которого подсоединен к единичному входу первого Триггера 12 управления, нулевой Выход которого соединен с информационными входами первыхдвух ключей 8 и 9 первого двоичного элемента 6 коммутации, в котором управ ляющие входы первого 8 и четвертого 11 .ключей соединены с нулевым выходом третьего триггера 14 управления Единичный выход третьего триггера 14 управления подключен к управляющим входам второго 9 и третьего 10 ключей, первого /двоичного элемента коммутации, причем выход второго кл ча 9 соединен с выходом четвертого ключа 11 и управляющими входами пер вого 8 и четвертого 11 ключей , второго двоичного элемента 7 коммутаци а выход третьего ключа 10 и выход первого ключа 8 двоичного элемента коммутации соединены с управляющими входами второго 9 и третьего 10 клю чей второго двоичного элемента 7 коммутатдин. Входы первых двух ключе и 9 ДВОИЧН017О элемента 7 коммутац подсоединены к первому информационному полюсу 2 устройства, а двух др гих ключей 10 и 11 - к второму информационному полюсу 3,.Третий информационный полюс 4 подключен к выходам ключей 8 и 10 второго двоичного элемента 7 коммутации, а четвертый информационный полюс 5 - к выходам ключей 9 и 11. I Кроме того, функциональная схема (фиг.1) содержит четыре дополнительных двухвходовых элемента ИЛИ 16-19 один трехвходовый элемент ИЛИ 20, четыре трехвходовьк элемента И 21-24, . один двухвходовый элемент И 25, четыре блока 26-29 фиксации кодов настройки, две схемы 30 и 31 сравнения, триггер 32 фиксации цикла настройки. Единичный выход триггера 32 фиксации цикла настройки подключен к входу трехвходового элемента ИЛИ 20 и входу основного двухвходового элемента ИЛИ 15, второй вход которого соединен с первым входом двухвходового элемента И 25, вторым входом трехвходового элемента ИЛИ 20 и ыходом первой схемы 30 сравнения, информационный вход которой подключен к четвертому информационному полюсу 5 устройства и первому основному входу второй схемы 31 сравнения, вьосод которой соединен с входом первого дополнительного двухвходового элемента ИЛИ 16 и единичным входом второго триггера 13 управления. Единичный выход второго триггера 13 управления соединен с входом второго дополнительного двухвходового элемента ИЛИ 17, второй вход которо,го подключен к единичному выходу (первого триггера 12 управления, нулевой выход которого соединен с входом перво1:о трехвходового элемента И 21, второй вход которого соединен с нулевым выходом второго триггера 13 управления, а третийвход - с управляющим входом 33 организации цикла настройки и входом второго .трехвходового элемента И 22. Второй вход трехвходового элемента И 22 подключен к выходу второго дополнительного двухвходового элемента ИЛИ 17, а третий вход - к нулевому выходу триггера 32 фиксации цикла настройки. Единичньй вход триггера 32 фиксации цикла настройки подключен к выходу первого трехвходового элемента И 21, а нулевой вход - к выходу третьего дополнительного двухвходового элемента ИЛИ 18, первый вход которого соединен с нулевыми входами тре триггеров 12-14 управления и входом 34 сброса устройства, а второй входс первым тактирующим входом 35 устройства, управляющими входами схем 30 и 31;сравнений и синхронизирующими входамг 36 первого 26 и второго 27 блоков фиксации кодов настройки. Второй синхронизирующий вход 37 блоков 26-29 подключен к второму тактирующему входу 38 устройства, третьему входу трехвходового элемента ИЛИ 20, второму входу первого дополнительного двухвходового элемента ИЛИ 16 и первому входу четвертого дополнительного двухвходового элемента ИЛИ 19, второй вход которого соединен с третьим тактируюгцим входом 39 устройства и первыми синхронизирующими входами 36 третьего 28 и четвертого 29 блоков фиксации кодов настройки. Выход четвертого дополнительного элемента 1ШИ 19 подключен к входам третьего 23 и четвертого 24 трехвходовых элементов И, вторые входы которых соединены соответственно с выходами трехвходового элемента ИЛИ 20 и первого дополнительного двухвходового элемента ИЛИ 16, а третьи входы - с выхода-. ми третьего 28 и четвертого 29 блоков фиксации кодов настройки, входы которых подключены соответственно к вторым информационным входам второй 31 и первой 30 схем сравнения и выходам первой 26 и второй 27 схемфиксаций кодов настройки.

Каждьй из блоков фиксации кодов настройки содержит регистр 40 настройки, элемент 41 и два элемента И 42 и 43. Вход первого элемента И 42 подключен к выходу блока фиксации кода настройки и выходу регистра 40 настройки, второй его вход - к первому синхронизирующему входу 36 блока, а выход элемента И 42 - к входу элемента ИЛИ 41, второй вход которого соединен с выходом второго элемента И 43, вход которого подключен к второму синхронизирующему входу 37, а второй вход - к входу блока фиксации кода настройки. В схеме на фиг.1 третий информационный полюс 4 устройства .соединен с входом первого блока 26 фиксации кода настройки и выходом третьего трехвходового .элемента И 23, четвертый информационный полюс 5 - с входом второго блока 27

фиксации кода настройки и выходом четвертого терхвходового элемента И 24. Первый управляющий выход 44 окончания цикла настройки подключен к выходу второго трехвходового элемента li 22, а второй управляющий вькод 45 окончания цикла настройки к выходу двухвходового элемента И 25 Вход 46 предварительной настройки подсоединен к единичному входу триггера 14 управления. Устройство содержит также элемент задержки 47.

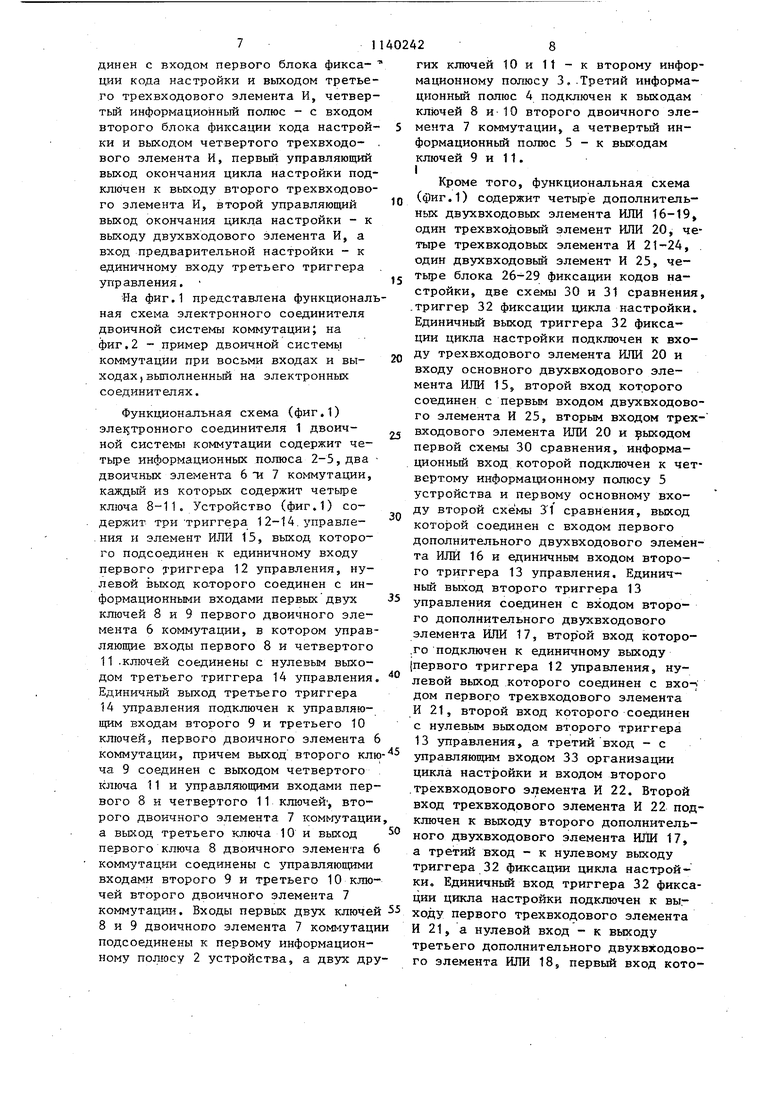

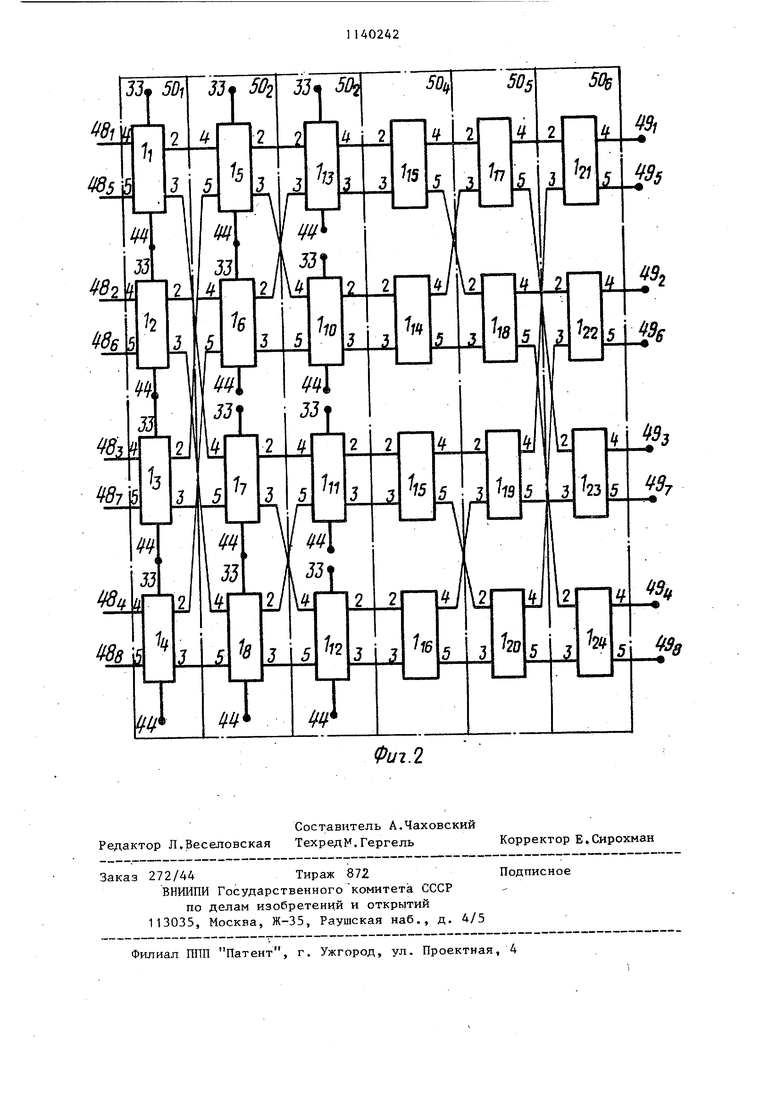

На фиг.2 приведен пример двоичной системы коммутации на 8 входов 48,48о и 8 выхоДов 49, -49g, построенный на электронных соединителях ,, которые объединены в шесть каскадов , каждый из которых содержит по четыре электронных соединителя. Вход с номером 48 соединяется при с информационным полюсом 4 электронного соединителя 1, а при i 4 с информационным полюсом 5 электронного соединителя 1. , где j 1-4. Выход с нЪмером 49, соединяется при и 4 с информационным полюсом 4 электронного соединителя 1: , где j 20-4-1 , а при i 4 - с информационным полюсом 5 электронного соединителя 1J , гдеj 16+f. Управляющие входы 33 организации цикла настройки электронных соединителей 1 , 1а 14 Ч IQ соединены с управляющими выходами 44 организации цикла настройки электронных соединителей 1 1 2 . V соответственно.

Рассмотрим работу электронного .соединителя в нескольких режимах, которые характеризуются подачей управляющих сигналов на входы 33, 34, 35, 38, 39 и 46 и на информационные полюса 2-5 (фиг.1).

Режим первый характеризуется подачей управляющего на третий триггер 14 управления через вход 46 предварительной настройки. По этому сигналу третий триггер 14 управления переходит в единичное состояние. Сигнал с единичного выхода открывает ключи 9 и 10 двоичного элемента 6. Отсутствие сигнала с нулевого выхода триггера 14 закрывает ключи 8 и 11 этого же двоичного элемента.

Режим второй характеризуется подачей сигнала на вход 34 сброса устройства. По этому сигналу триггеры 12-14 управления устанавливаются в нулевое состояние. Через третий

11

дополнительный двухвходовый элементИЛИ 18 в нулевое состояние устанавливается и триггер 32 фикса1Ц1и цикла настройки. Сигнал с нулевого выхода третьего триггера 14 управления открывает ключи 8 и 11 и закрывает ключи 9 и 10 первого двоичного элемента 6. Сигналы с нулевых выходов триггеров 12 и 13 через ключи 8 и 11 первого двоичного элемента 6 открывают ключи 8-11 второго двоичного элемента 7.

Режим третий характеризуется подачей на второй тактирующий вход 38 импульсов и на информационные полюса 4 и 5 двоичных кодов, которые состоят из двоичных чисел длины 22, при этом старшие S разрядов числа записываются в регистру 40 настройки блоков 28 и 29 фиксации кодов настройки, а младшие разрядов в регистры 40 настройки блоков 26 и 27 фиксации кодов настройки. По импульсам с второго тактирующего входа 38 через второй синхронизирующий вход 37 во всех блоках 26-29 открываются вторые элементы И 43. Коды с информационных полюсов 4 и 5 проходят через вторые элементы И 43 элементы ИЛИ 41 в регистры 40 настройки, сигнал с информационного полюса 4 проходит через блок 26 фиксации кодов настройки, а с 5 через блок 27 фиксации кодов настройки. Эти же сигналы через Е тактов появляются на вькоде блоков 26 и 27. Дальше старшие ° разрядов кодов записываются в регистры 40 настройки блоков 28 и 29, а мпадшиев регистры 40 настройки блоков 26 и 27.

Режим четвертый характеризуется подачей на второй.тактирующий вход 38 импульсов, по которым через второй синхронизирующий вход 37, как и в 3-м режиме открываются пути для считывания кодов длины 2 из регистров 40 настройки. Через дополнительный двухвходовый элемент ИЛИ 16 и четвертый дополнительный двухвходовый элемент ИЛИ 19 открьшается четвертый трехвходовой элемент И 24, и код длины 2В из регистров 40 настройки поступает на четвертый информационный полюс: 5. Импульсы с тактирующего входа 38 трехвх одовый элемент ИЛИ 20 и четвертыйдополнительный двухвхо024212

довый элемент ИЛИ 19 открывают третий трехвходовый элемент И 23, через который код длины 2Ё из регистров настройки блоков 28 и 26 фиксации настройки поступает на третий информационный полюс 4.

Режим пятьй характеризуется подачей импульсов на первый тактирующий вход 35. По этим импульсам запускаются схемы 30 и 31 сравнения. Через первые синхронизирующие входы 36 открываются элементы И 42 в блоках 26 и 27 фиксации кодов настройки,, благодаря чему происходит перезапись

15 кодов длины в из регистров 40 настройки через элемент И 42 в элемент ИЛИ 41. Код из регистра 40-настройки поступает, на его выход, откуда он поступает на выход из блока 26

20 и на информационный вход второй схемы сравнения 31. Код же из блока 27 фиксации кода настройки поступает на информационный вход первой схемы 30 сравнения. На вторые информационные входы схемы 30 и 31 сравнения поступает код длины В с четвертого информационного полюса 5. Триггер 32 устанавливается в О.

Режим шестой характеризуется тем,

30 что на третий тактирующий вход 39 поступают импульсы, в схеме 30 сравнения происходит сравнение двух кодов и триггер 12 управления находится в нулевом состоянии. Импульсы

- с третьего тактирующего.входа 39 через синхронизирующий вход 36 блоков 28 и 29 открывают путь для перезаписи кодов длины 8 из регистров 40 настройки, которые поступают на

Q входы трехвходовых элементов И 23 и 24. Элемент И 23 открыт, так как на его входы поступают сигналы от импульсов, подаваемых на входо39 через четвертый, дополнительный мент ИЛИ 19, и подаваемые первой

схемой сравнения 30 через трехвходовый элемент ИЛИ 20 о а четвертый трехвходовый элемент И 24 закрыт, так как на него не поступает сигнал чеJQ рез первый дополнительный элемент И 16. Кроме того, сигнал сравнения через элемент ИЛИ 15 перебрасывает триггер 12 управления в единичное состояние.

5 Режим седьмой характеризуется тем, что на третий тактирующий вход 39 поступают импульсы, в схеме 30 сравнения происходит сравнение двух

V13

кодов и триггер 12 управления находится в единичном состоянии. Работа устройства аналогична работе в 6-м режиме, только сигнал сравнения через двухвходовъй элемент И 25 поступает на выход 45 окончания цикла настройки.

Режим восьмой характеризуется тем, что на третий тактирующий вход 39 поступают импульсы, сравнение кодов длины о происходит в схеме 31 сравнения, Как и в шестом режиме на выходах блоков 28 и 29 фиксации кодов настройки появляются коды длины из регистров 40 настройки. Однако в этом случае открыт трехвходовый элемент И 24, на который поступают сигналы от третьего тактирующего входа 39 через четвертьй дополнительный элемент ИЛИ 19 и схемы сравнения 31 через.первый дополнительный элемент ИЛИ 16, а третий трёхвходовый элемент И 23 закрыт. Поэтому код из регистра 40 настройки блока 29 поступает на четвертый информационный полюс 5. Кроме того, сигнал из схемы 31 сравнения перебрасывает триггер 13 управления в единичное состояние.

Режим девятый характеризуется тем, что на третий тактирующий вход 39 подаются импульсы и триггер 32 фиксации кодов настройки находится в единичном состоянии. В этом режиме схема работает так же, как и в шестом режиме, только сигналы на трёхвходовый элемент ИЖ 20 поступают не от схемы 30 сравнения, а от единичного выхода тр иггера 32 фиксации цикла настройки.

Режим десятый характеризуется тем, что на вход 33 организации цикла настройки поступает сигнал, триггеры 12 и 13 управления находятся в нулевом состоянии. В этом режиме сигнал с входа 33 через первый трехвходовой элемент И 21 перебрасывает триггер 32 фиксации цикла настройки в единичное состояние. Сигнал с его единичного выхода проходит через элемент ИЛИ 15 и перебрасьюает триггер 12 управления в единичное состояние. Отсутствие сигнала с нулевого выхода триггера 32 открывает второй трехвходовьй элемент Л 22.

Режим одиннадцатый характеризуется тем, что на вход 33 организации цикла подается сигнал, один из триг4214

геров 12 или 13 управления находится в единичном состоянии, а триггер 32 находится в нулевом состоянии, Тогда первый трёхвходовый элемент И 21 закрыт, а второй 22 открыт, так как на него поступают сигналы от нулевого выхода триггера 32 фиксации цикла настройки и одного из единичных выходов триггеров 12 или 13 управления через второй дополнительный элемент ИЛИ 17. В результате этого сигнал от входа 33 проходит на выход 44 окончания цикла настройки.

Рассмотрим работу электронного

соединителя на примере образования соединительных путей согласно следующему списку соединений входов 48

с выходами 49

/48 48 48 48 48 48

2 4 6 8 5// реализуемому в двоичной системе коммутации (фиг.2) .

Вначале на все электронные соединители 1 двоичной системы коммз тации подают на вход 34 сброса устройства сигнал, в результате чего в каждом электронном соединителе 1 выполняется установка всех триггеров 12, 13,

14 и 32 в нулевое состояние (2 режим), Затем на все электронные соединители

1 каскадов 50, 50j, 50g подается сигнал на вход 46 и предварительной настройки, в результате чего в них

триггеры 14 управления устанавливаются в единичное состояние. Ключи 8 и 11 первого двоичного элемента 6 закрыты, а ключи 9 и 10 открыты. Электронный соединитель по этому

сигналу работает в первом режиме,

После чего подают на входы 48 двоичной системы коммутации (фиг.2) двоичные коды длины 28.-При этом старшие & разрядов на входах 48

производят двоичную запись чисел

соответственно: 482-1, 48g-7, а младшие разрядов образуют соответственно: 482-6S,

484-2; 48g-7i , .

Аналогично на выходы 49 также подают коды длины 26, при этом старшие ъ разрядов кодов образуют в двоичной записи числа: 492-1,

494-3; 495-4; , а младиме соответственно: 49,-6- , , , 49.-7, , i9g--5. В данных кодах,. подаваемых на входы 48 (выходы 49), первое число дает номер входа (выхода), а второе - номер выхода (входа) для соединения. При этом нумерация их начинается с О и заканчиваетс 7. Номера равны номеру индекса минус единица у входов 48 , у выходов 49 (фиг.2). В это же время на второй тактирующий вход 38 подаются импульсы, в результате чего коды настройки записываются в регистры 40 настройки блоков 28, 26, 27 и 29 фиксации кодов настройки электронных соединителей каскадов 50 и 50, (3-й режим). Затем подают сигнал на вход 33 организации цикла электронного со единителя 1., Он перебрасывает триггеры 12 управления и 32 фиксации цикла настройки в единичное состояние (10-й режим). После чего подают на третий тактирующий вход 39 электронных соединителей каскада 50 импульсы. В результате код из регистра 40 настройки блока 28 фиксации настройки блока 28 фиксации кода настройки поступает на третий информационный полюс 4 электронного соединителя 1 (9-й режим). Так как в этом электронном соединителе открыты ключи 8 и 11 второго двоичного элемента 7, то этот код проходит на первый информационный полюс 2 электронного соединителя 1, затем через электронные соединители К, I W 0 W U 18 информационные входы 2 электронных соедини телей 1 каскада 50, , откуда через открытые ключи 8-11 двоичных элементов 7 поступает на схемы 30 и 31 сравнения. В это же время на все электронные соединители каскада 50 подают тактирующие импульсы через вход 35. В рассматриваемом примере сравнение происходит с содержимым регистра 40 сравнения блока 26 фиксации кода настройки элекгронного .соединителя Ly, работа которого про текает так, как описано в 5- и 8-м режимах. После того, как заканчивается сравнение, подают импульсы на третий тактирующий вход 39. Физические процессы в электронном соединителе протекают так же, как описано в 8-м режиме, т.е. код из регистра 40 сравнения блока 29 фиксации кода настройки этого электронного соединителя поступает на его четвертый 1 216. информационный полюс 5. В этом электронном соединителе открыты ключи 8 и 11 второго двоичного элемента 7, так как триггеры управления 13 и 14 находятся в единичном состоянии. Поэтому код поступает на второй информационный полюс 3 электронного соединителя 122 дальше через электроннуе соединители каскадов на входы 3 электронных соединителей первого каскад. В это же время на все электронные соединители 1 первого каскада подают импульсы через первый тактирующий вход 35. Сравнение происходит в схеме 30 сравнения электронного соединителя 1 jpaбота которого протекает так, как описано в 7-м режиме. Это происходит из-за того, что триггер 12 управления находится в положении 1, сигнал из единичного выхода триггера 12 проходит через элемент задержки 47 и открывает двухвходовьй элемент И 25. В результате на выходе 45 окончания настройк появляется сигнал. По этому сигналу подают импульсы на вход 33 организации цикла электронного соединителя 1. Так как триггер 12 управления находится в единичном положении, то электронный соединитель 1 пропускает сигнал на выход 44 организации цикла (11-й режим), откуда сигнал поступает на вход 33 организации цикла электронного, соединителя Ь (см. фиг.2). Дальнейшая работа двоичной схемы коммутации аналогична описанной выше. Установление соединений продолжается до тех пор, пока не произойдет сравнение кодов в схеме сравнения 30 электронного соединителя 123, после чего получают сигнал на втором выходе 45 окончания цикла настройки этого электронного соединителя. Затем подают сигнал на вход 33 организации цикла настройки электронного соединителя If , Этот сигнал появляется на выходе 44 электронного соединителя 1 (11-й режим). Получив этот сигнал, подают на второй тактирующий вход 38 злектронных соединителей каскадов 50, 502, 5 6 импульсы. По этим импульсам электронные соединители каскадов 50 и 50 работают так, как описано в 4-м режиме, т.е. в них происходит считывание кодов, а в электронных соедините1711

лях каскадов 50 и 5С происходит запись кодов (3-й режим), fta этом заканчивается настройка каскадов 50, и 50 . Для настройки каскадов 50 и 50с можно распараллелить процесс настройки, т.е. отдельно настраивать

Ч Ч % 18 отдельно l, 1g, и 1л.. После окончания настройки каскадов 502 и 50 проводят перезапись кодов из этих каскадов в каскады 50j и 504 и их настройку.

024218

Таким образом, применение элек- , тронного соединителя двоичной системы коммутации исключает внешнюю ЭВМ для управления параллельными 5 многокаскадными коммутирующими схемами, которая ведет подобный процесс коммутации значительно медленнее.

Кроме этого, повышается надежность схем коммутации в результате уменьшения внешних связей между ЭВМ и электронными соединителями.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Модуль многокаскадной коммутационной системы | 1975 |

|

SU769741A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3638193, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1985-02-15—Публикация

1983-08-31—Подача