Изобретение относится к импульсной технике электронной коммутации и связи и может быть использовано в вычислительных и автоматических системах с перестраиваемой структурой.

Цель изобретения - повышение быстродействия, достоверности функционирования и расширение функциональных возможностей за счет одновременного параллельного поиска и фиксации произвольного числа каналов в многокаскадной коммутационной системе.

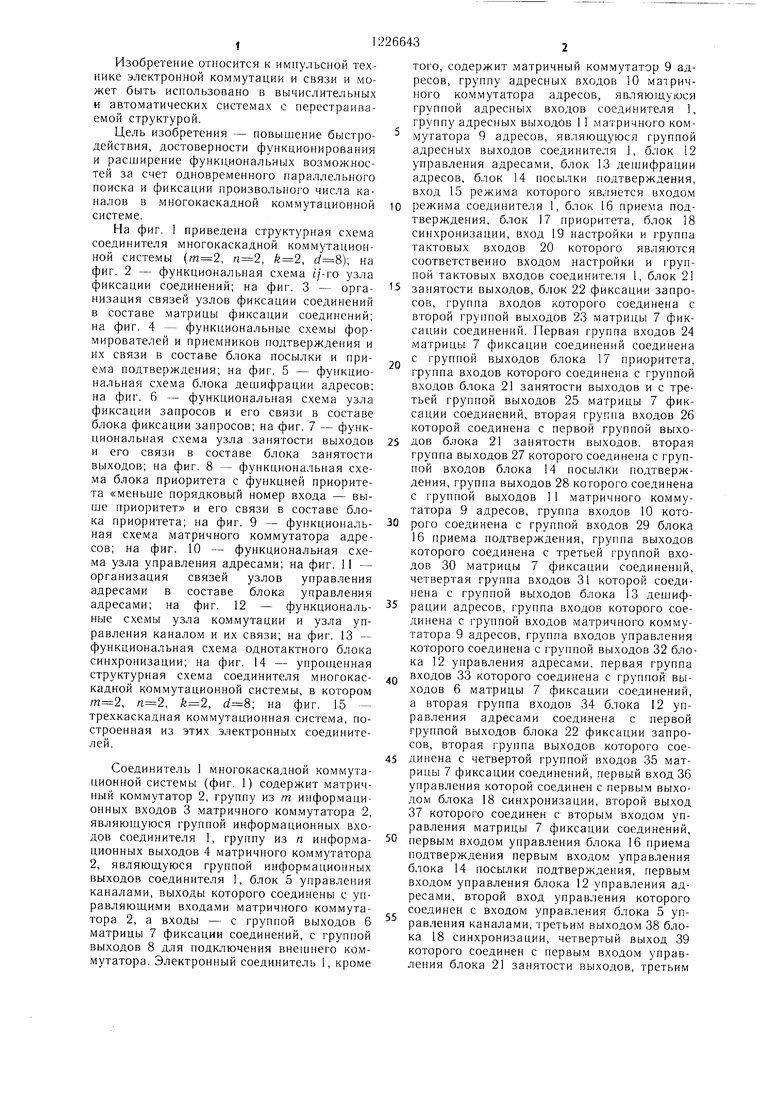

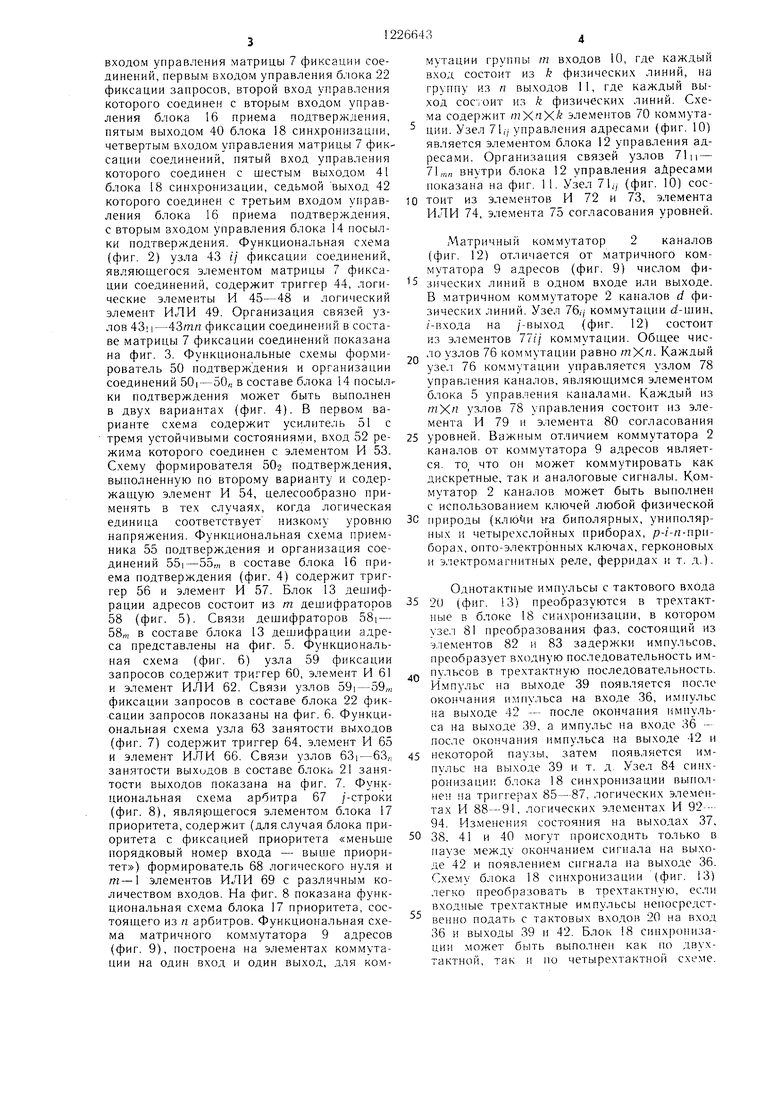

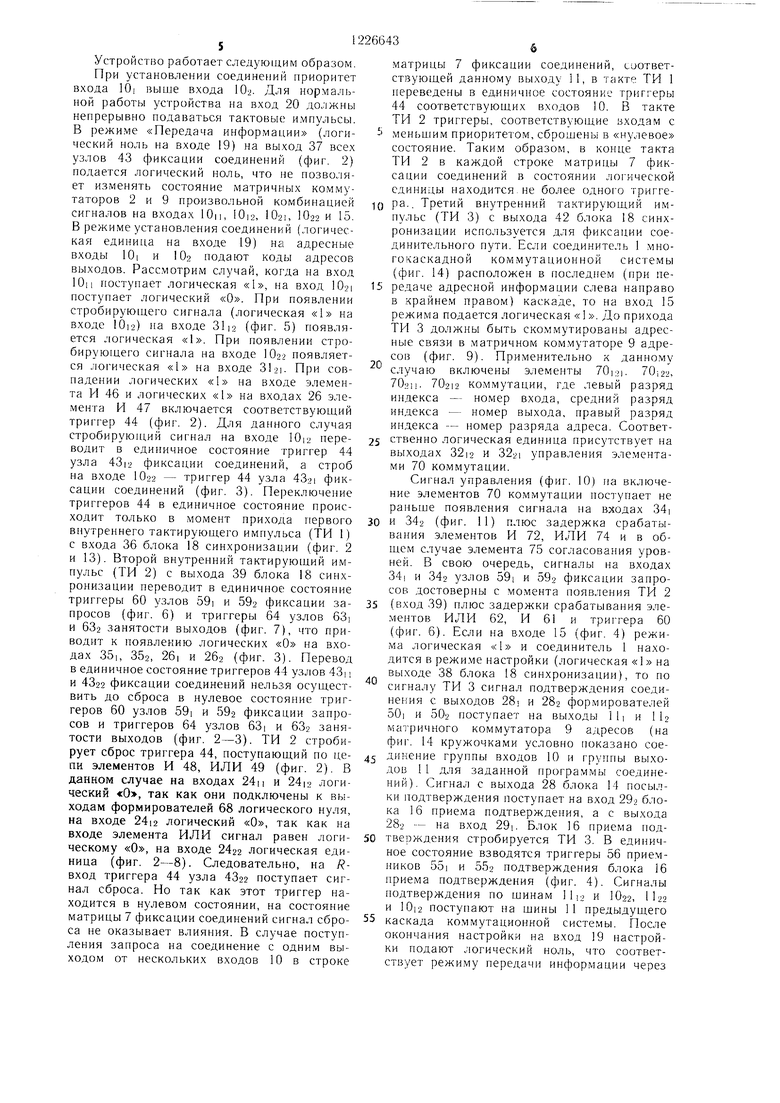

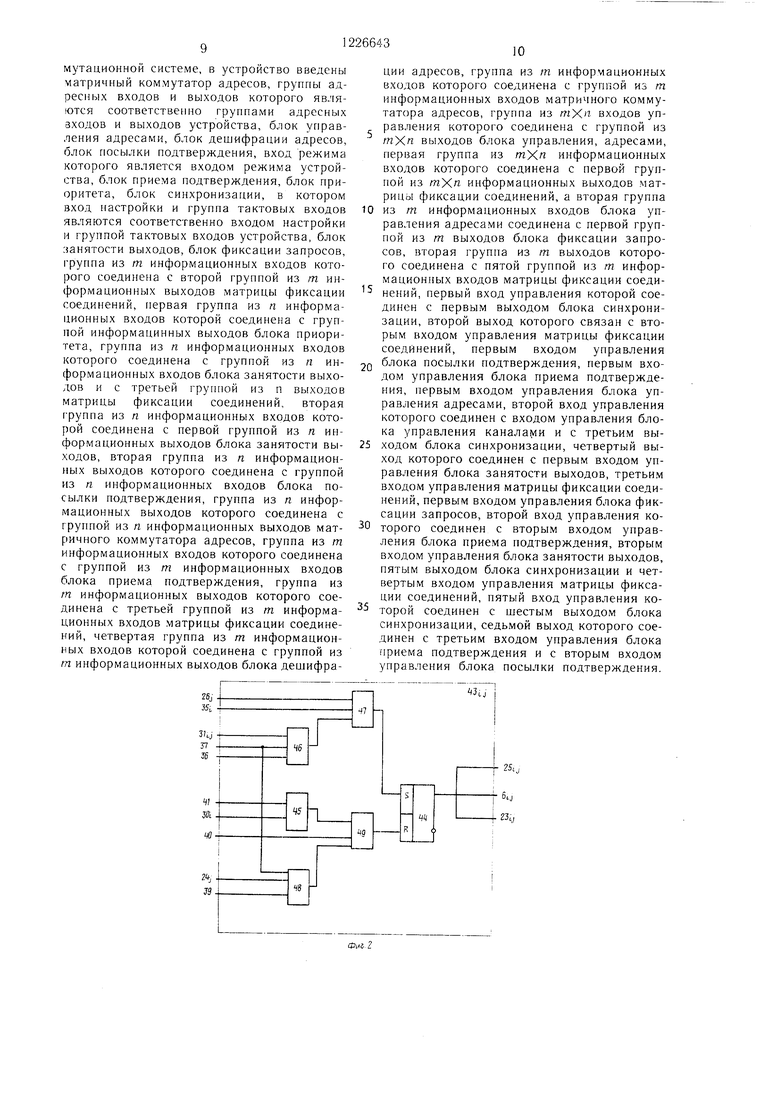

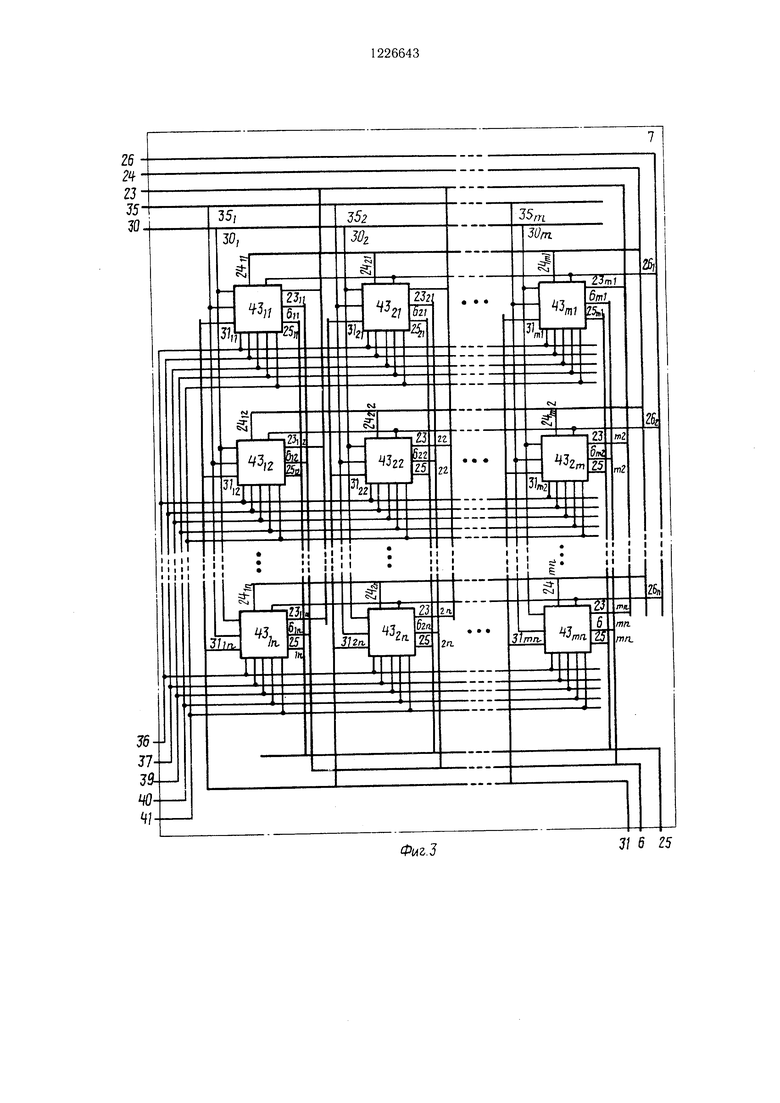

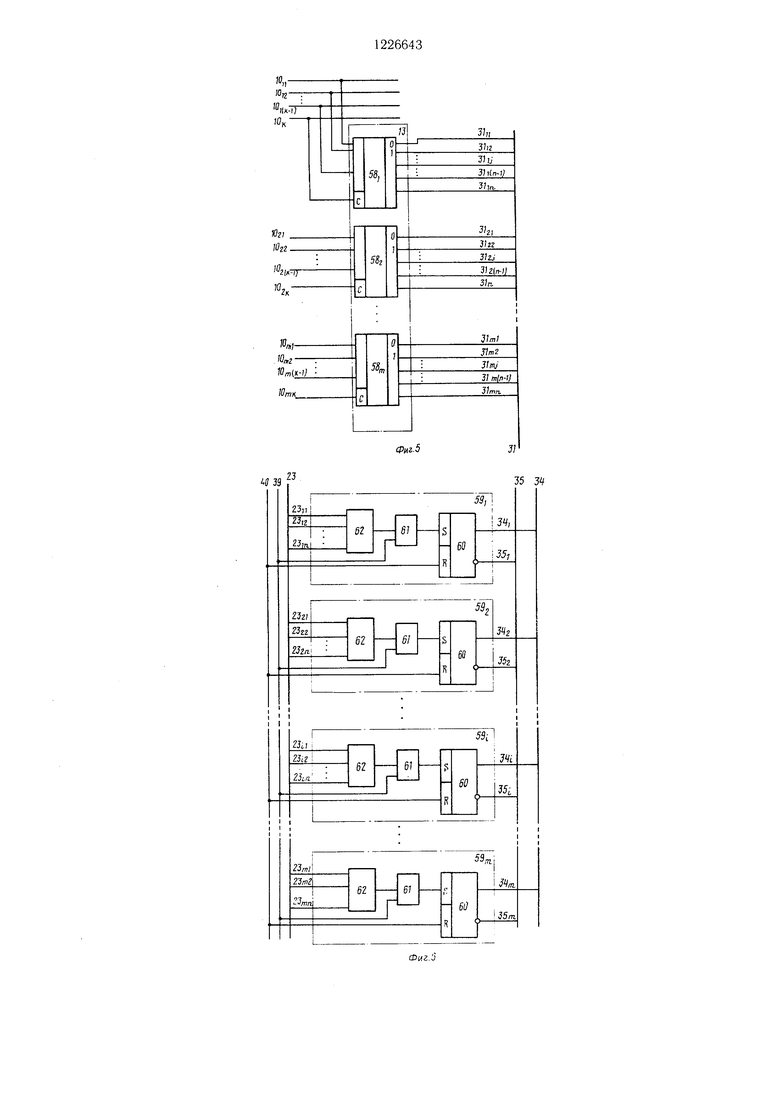

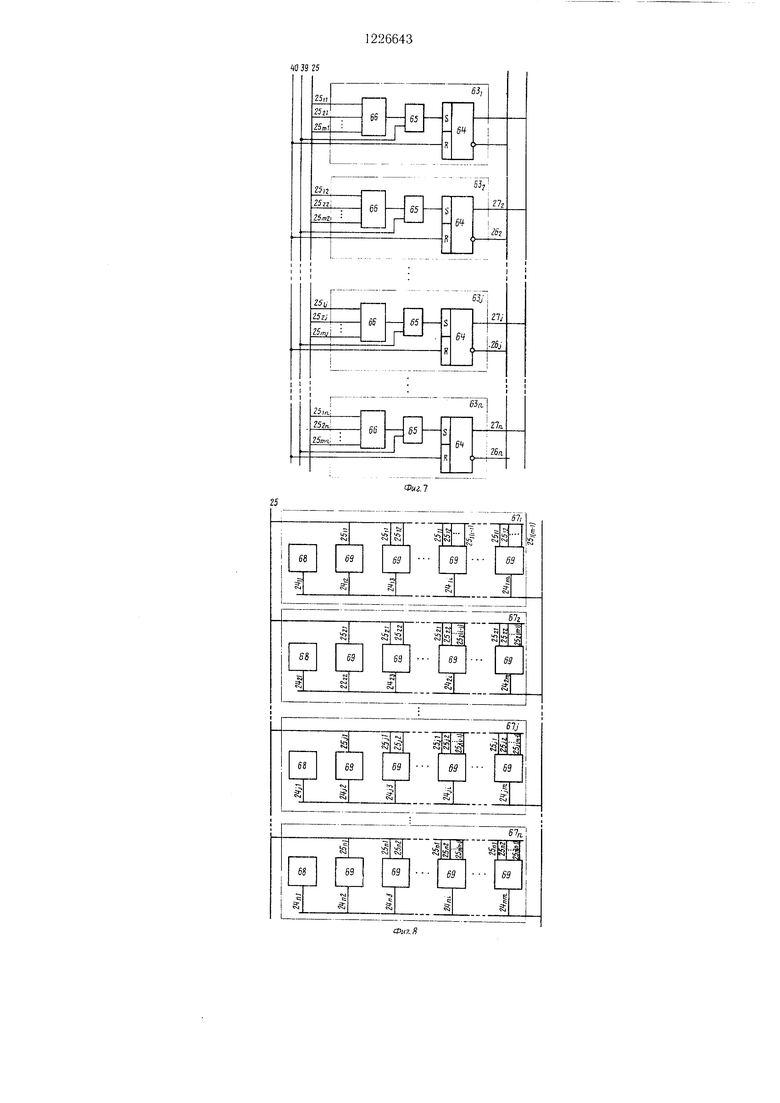

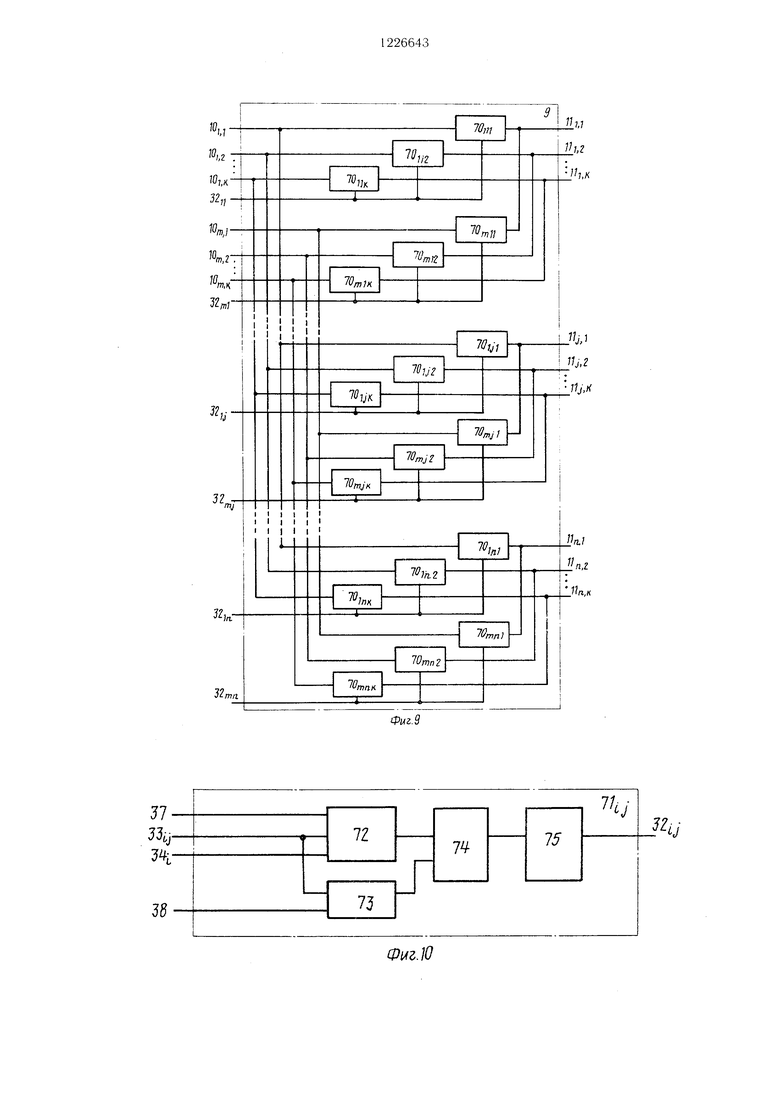

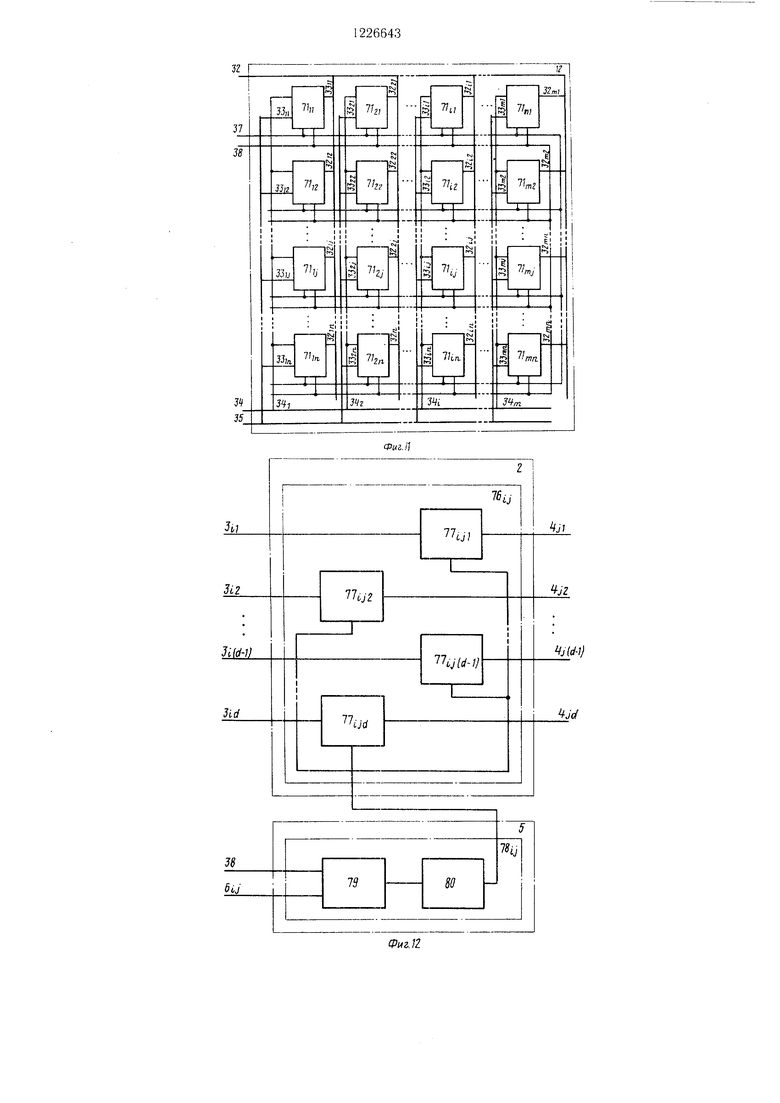

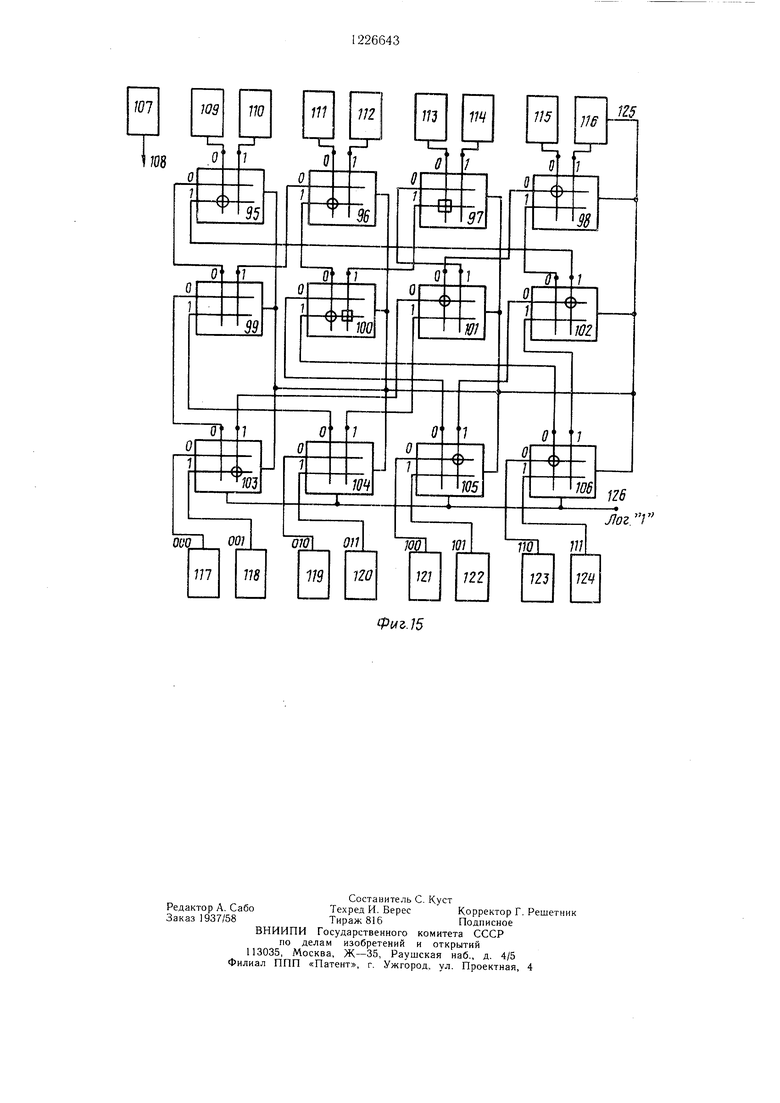

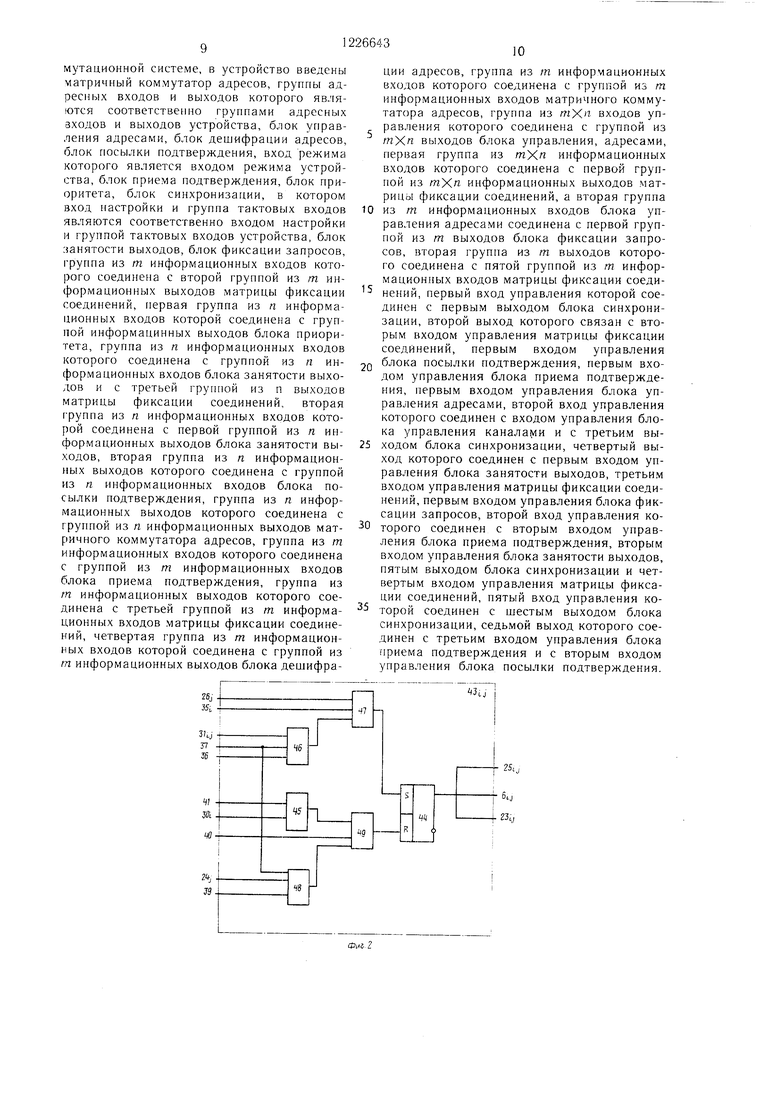

На фиг. 1 приведена структурная схема соединителя многокаскадной коммутационной системы (, , , ); на фиг. 2 - функциональная схема //-го узла фиксации соединений; на фиг. 3 - организация связей узлов фиксации соединений в составе матрицы фиксации соединений; на фиг. 4 - функциональные схемы формирователей и приемников подтверждения и их связи в составе блока посылки и приема подтверждения; на фиг. 5 - функциональная схема блока дешифрации адресов; на фиг. 6 - функциональная схема узла фиксации запросов и его связи в составе блока фиксации запросов; на фиг. 7 - функциональная схема узла занятости выходов и его связи в составе блока занятости выходов; на фиг. 8 - функциональная схема блока приоритета с функцией приоритета «меньше порядковый номер входа - выше приоритет и его связи в составе блока приоритета; на фиг. 9 - функциональная схема .матричного коммутатора адресов; на фиг. 10 - функциональная схема узла управления адресами; на фиг. И - организация связей узлов управления адресами в составе блока управления адресами; на фиг. 12 - функциональные схемы узла коммутации и узла управления каналом и их связи; на фиг. 3 - функциональная схема однотактного блока синхронизации; на фиг. 14 - упроп1.енная структурная схема соединителя многокаскадной коммутационной системы, в котором , , , на фиг. 15 - трехкаскадная коммутационная система, построенная из этих электронных соединителей.

Соединитель 1 многокаскадной коммутационной системы (фиг. 1) содержит матричный коммутатор 2, группу из т информационных входов 3 матричного коммутатора 2, являюш,уюся группой информационных вхо20

ТОГО, содержит матричный коммутатор 9 адресов, группу адресных входов 10 ма1рич- ного ком.мутатора адресов, являющуюся группой адресных входов соединителя 1, группу адресных выходов 11 матричного ком5 мутатора 9 адресов, являющуюся группой адресных выходов соединителя I, блок 12 управления адресами, блок 13 дешифрации адресов, блок 14 посылки подтверждения, вход 15 режима которого является входом

10 режима соединителя 1, блок 16 приема подтверждения, блок 17 приоритета, блок 18 синхронизации, вход 19 настройки и группа тактовых входов 20 которого являются соответственно входом настройки и группой тактовых входов соединителя 1, блок 21

15 занятости выходов, блок 22 фиксации запросов, группа входов которого соединена с второй выходов 23 матрицы 7 фиксации соединений. Первая группа входов 24 матрицы 7 фиксации соединений соединена с группой выходов блока 7 приоритета, группа входов которого соединена с группой входов блока 21 занятости выходов и с третьей группой выходов 25 матрицы 7 фиксации соединений, вторая группа входов 26 которой соединена с первой группой выходов блока 21 занятости выходов, вторая группа выходов 27 которого соединена с группой входов блока 14 посылки подтверждения, группа выходов 28 которого соединена с группой выходов 11 матричного коммутатора 9 адресов, группа входов 10 кото30 рого соединена с группой входов 29 блока 16 приема подтверждения, группа выходов которого соединена с третьей группой входов 30 матрицы 7 фиксации соединений, четвертая группа входов 31 которой соединена с группой выходов блока 13 дешифрации адресов, группа входов которого соединена с группой входов матричного коммутатора 9 адресов, группа входов управления которого соединена с группой выходов 32 блока 12 управления адресами, первая группа

Q входов 33 которого соединена с группой выходов 6 матрицы 7 фиксации соединений, а вторая группа входов 34 блока 12 управления адресами соединена с первой группой выходов блока 22 фиксации запросов, вторая группа выходов которого сое45 динена с четвертой группой входов 35 матрицы 7 фиксации соединений, первый вход 36 управления которой соединен с первым выходом блока 18 синхронизации, второй выход 37 которого соединен с вторым входом управления матрицы 7 фиксации соединений.

25

35

дов соединителя 1, группу из п информа- 50 первым входом управления блока 16 приема

ционных выходов 4 матричного коммутатора 2, являющуюся группой информационных выходов соединителя 1, блок 5 управления каналами, выходы которого соединены с управляющими входами матричного коммутатора 2, а входы - с группой выходов 6 матрицы 7 фиксации соединений, с группой выходов 8 для подключения коммутатора. Электронный соединитель 1, кроме

подтверждения первым входо.м управления блока 14 посылки подтверждения, первы.м входом управления блока 12 управления адресами, второй вход управления которого соединен с входом управления блока 5 управления каналами, 1 ретьим выходом 38 блока 18 синхронизации, четвертый выход 39 которого соединен с первым входом управления блока 21 занятости выходов, третьим

0

ТОГО, содержит матричный коммутатор 9 адресов, группу адресных входов 10 ма1рич- ного ком.мутатора адресов, являющуюся группой адресных входов соединителя 1, группу адресных выходов 11 матричного ком5 мутатора 9 адресов, являющуюся группой адресных выходов соединителя I, блок 12 управления адресами, блок 13 дешифрации адресов, блок 14 посылки подтверждения, вход 15 режима которого является входом

0 режима соединителя 1, блок 16 приема подтверждения, блок 17 приоритета, блок 18 синхронизации, вход 19 настройки и группа тактовых входов 20 которого являются соответственно входом настройки и группой тактовых входов соединителя 1, блок 21

5 занятости выходов, блок 22 фиксации запросов, группа входов которого соединена с второй выходов 23 матрицы 7 фиксации соединений. Первая группа входов 24 матрицы 7 фиксации соединений соединена с группой выходов блока 7 приоритета, группа входов которого соединена с группой входов блока 21 занятости выходов и с третьей группой выходов 25 матрицы 7 фиксации соединений, вторая группа входов 26 которой соединена с первой группой выходов блока 21 занятости выходов, вторая группа выходов 27 которого соединена с группой входов блока 14 посылки подтверждения, группа выходов 28 которого соединена с группой выходов 11 матричного коммутатора 9 адресов, группа входов 10 кото0 рого соединена с группой входов 29 блока 16 приема подтверждения, группа выходов которого соединена с третьей группой входов 30 матрицы 7 фиксации соединений, четвертая группа входов 31 которой соединена с группой выходов блока 13 дешифрации адресов, группа входов которого соединена с группой входов матричного коммутатора 9 адресов, группа входов управления которого соединена с группой выходов 32 блока 12 управления адресами, первая группа

Q входов 33 которого соединена с группой выходов 6 матрицы 7 фиксации соединений, а вторая группа входов 34 блока 12 управления адресами соединена с первой группой выходов блока 22 фиксации запросов, вторая группа выходов которого сое5 динена с четвертой группой входов 35 матрицы 7 фиксации соединений, первый вход 36 управления которой соединен с первым выходом блока 18 синхронизации, второй выход 37 которого соединен с вторым входом управления матрицы 7 фиксации соединений.

5

5

0 первым входом управления блока 16 приема

подтверждения первым входо.м управления блока 14 посылки подтверждения, первы.м входом управления блока 12 управления адресами, второй вход управления которого соединен с входом управления блока 5 управления каналами, 1 ретьим выходом 38 блока 18 синхронизации, четвертый выход 39 которого соединен с первым входом управления блока 21 занятости выходов, третьим

входом управления матрицы 7 фиксации соединений, первым входом управления блока 22 фиксации запросов, второй вход управления которого соединен с вторым входом управления блока 16 приема подтверждения, пятым выходом 40 блока 18 синхронизации, четвертым входом управления матрицы 7 фиксации соединений, пятый вход управления которого соединен с шестым выходом 41 блока 18 синхронизации, седьмой выход 42 которого соединен с третьим входом управления блока 16 приема подтверждения, с вторым входом управления блока 14 посылки подтверждения. Функциональная схема (фиг. 2) узла 43 г/ фиксации соединений, являющегося элементом матрицы 7 фиксации соединений, содержит триггер 44, логические элементы И 45-48 и логический элемент ИЛИ 49. Организация связей узлов 43м-43т« фиксации соединений в составе матрицы 7 фиксации соединений показана на фиг. 3. Функциональные схемы формирователь 50 подтверждения и организации соединений 50|-50„ в составе блока 14 посылки подтверждения может быть выполнен в двух вариантах (фиг. 4). В первом варианте схема содержит усилитель 51 с тремя устойчивыми состояниями, вход 52 режима которого соединен с элементом И 53. Схему формирователя 50-2 подтверждения, выполненную по второму варианту и содержащую элемент И 54, целесообразно применять в тех случаях, когда логическая единица соответствует низкому уровню напряжения. Функциональная схема приемника 55 подтверждения и организация соединений 55i-55,,, в составе блока 16 приема подтверждения (фиг. 4) содержит триггер 56 и элемент И 57. Блок 13 дешифрации адресов состоит из т дешифраторов 58 (фиг. 5). Связи дешифраторов 58i - 58„, в составе блока 13 дешифрации адреса представлены на фиг. 5. Функциональная схема (фиг. 6) узла 59 фиксации запросов содержит триггер 60, элемент И 61 и элемент ИЛИ 62. Связи узлов 59|-59,„ фиксации запросов в составе блока 22 фиксации запросов показаны на фиг. 6. Функциональная схема узла 63 занятости выходов (фиг. 7) содержит триггер 64, элемент И 65 и элемент ИЛИ 66. Связи узлов 63i-63,, занятости выходов в составе блока 21 занятости выходов показана на фиг. 7. Функциональная схема арбитра 67 /-строки (фиг. 8), являющегося элементом блока 17 приоритета, содержит (для случая блока приоритета с фиксацией приоритета «меньше порядковый номер входа - выше приоритет) формирователь 68 логического нуля и ш--1 элементов ИЛИ 69 с различным количеством входов. На фиг. 8 показана функциональная схема блока 17 приоритета, состоящего из п арбитров. Функциональная схема матричного коммутатора 9 адресов (фиг. 9), построена на элементах коммутации на один вход и один выход, для коммутации группы т входов 10, где каждый вход состоит из k физических линий, на группу из п выходов 11, где каждый выход состоит из k физических линий. Схема содержит mXnXk элементов 70 коммута ции. Узел 71,/ управления адресами (фиг. 10) является элементом блока 12 управления адресами. Организация связей узлов 71 ц - 71„,„ внутри блока 12 управления адресами показана на фиг. П. Узел 71,, (фиг. 10) сос0 тоит из элементов И 72 и 73, элемента ИЛИ 74, элемента 75 согласования уровней.

Матричный коммутатор 2 каналов (фиг. 12) отличается от матричного коммутатора 9 адресов (фиг. 9) числом фи5 зических линий в одном входе или выходе. В матричном ко.ммутаторе 2 каналов d физических линий. Узел 76,; коммутации й(-ц1ин, /-входа на /-выход (фиг. 12) состоит из элементов 77г/ коммутации. Общее чис- .10 узлов 76 коммутации равно . Каждый узел 76 коммутации управляется узлом 78 управления каналов, являющимся элементом блока 5 управления каналами. Каждый из тХ« узлов 78 управления состоит из элемента И 79 и элемента 80 согласования

5 уровней. Важным отличием коммутатора 2 каналов от коммутатора 9 адресов является, то, что он может коммутировать как дискретные, так и аналоговые сигналы. Коммутатор 2 каналов может быть выполнен с использованием ключей любой физической

С гфироды (клю1(и на биполярных, униполярных и четырехслойных приборах, /7-/-п-прп- борах, опто-электронных ключах, герконовых и э.чектромагнитных реле, ферридах и т. д.).

Однотактные импульсы с тактового входа

5 20 (фиг. 13) преобразуются в трехтактные в блоке 18 синхронизации, в котором узел 81 преобразования фаз, состоящий из э.лементов 82 и 83 задержки импульсов, преобразует входную последовательность им« пульсов в трехтактную последовательность. И мпульс на выходе 39 появляется после окончания импульса на входе 36, импульс на выходе 42 - после окончания импульса на выходе 39, а импульс на входе 36 -- после окончания импульса на выходе 42 и

5 некоторой паузы, затем появляется импульс на выходе 39 и т. д. Узел 84 синхронизации блока 18 синхронизации выполнен на триггерах 85-87, логических элементах И 88-91, логических элементах И 92 - 94. Изменения состояния на выходах 37,

0 38, 41 и 40 могут происходить только в паузе между окончанием сигнала на выходе 42 и появлением сигнала на выходе 36. Схему блока 18 синхронизации (фиг. 13) легко преобразовать в трехтактную, если входные трехтактные импульсы непосредст венно подать с тактовых входов 20 на вход 36 и выходы 39 и 42. Блок 18 С11нх)ониза- ции может быть выполнен как по двухтактной, так и по четырехтактно11 схеме.

5

Устройство работает следующим образом.

При установлении соединений приоритет входа 10| выше входа Юа. Для нормальной работы устройства на вход 20 должны ненрерывно подаваться тактовые импульсы. В режиме «Передача информации (логический ноль на в.ходе 19) на выход 37 всех узлов 43 фиксации соединений (фиг. 2) подается логический ноль, что не позволяет изменять состояние матричных коммутаторов 2 и 9 произвольной комбинацией сигналов на входах Юн, lOiz, lOai, 1022 и 15. В режиме установления соединений (логическая единица на входе 19) на адресные входы 101 и 102 подают коды адресов выходов. Расс.мотрим случай, когда на вход lOii поступает логическая «1, на вход 102i поступает логический «О. При появлении стробирующего сигнала (логическая «1 на входе 10:2) на входе 3112 (фиг. 5) появляется логическая «1. При появлении стробирующего сигнала на входе 1022 появляется логическая «1 на входе 3l2i. При совпадении логических «1 на входе элемента П 46 и логических «1 на входах 26 элемента И 47 включается соответствующий триггер 44 (фиг. 2). Для данного случая стробируюн1ий сигнал на входе 10i2 переводит в единичное состояние триггер 44 узла 43|2 фиксации соединений, а строб на входе 1022 - триггер 44 узла 432i фиксации соединений (фиг. 3). Переключение триггеров 44 в единичное состояние происходит только в момент прихода первого внутреннего тактирующего импульса (ТИ 1) с входа 36 блока 18 синхронизации (фиг. 2 и 13). Второй внутренний тактирующий импульс (ТП 2) с выхода 39 блока 18 синхронизации переводит в единичное состояние триггеры 60 узлов 59| н 592 фиксации запросов (фиг. 6) и триггеры 64 узлов 63) и 632 занятости выходов (фиг. 7), что приводит к появлению логических «О на входах 35|, 352, 26, и 2б2 (фиг. 3). Перевод в единичное состояние триггеров 44 узлов 43| и 4322 фиксации соединений нельзя осуществить до сброса в нулевое состояние триггеров 60 узлов 59i и 592 фиксации запросов и триггеров 64 узлов 63i и 632 занятости выходов (фиг. 2-3). ТИ 2 строби- рует сброс триггера 44, поступающий по цепи элементов И 48, ИЛИ 49 (фиг. 2). В данном случае на входах 24ц и 24ц логический 0, так как они подключены к выходам формирователей 68 логического нуля, на входе 24i2 логический «О, так как на входе элемента ИЛИ сигнал равен логическому «О, на входе 2422 логическая единица (фиг. 2-8). Следовательно, на R- вход триггера 44 узла 4322 поступает сигнал сброса. Но так как этот триггер находится в нулевом состоянии, на состояние матрицы 7 фиксации соединений сигнал сброса не оказывает влияния. В случае поступления запроса на соединение с одним выходом от нескольких входов 10 в строке

д

матрицы 7 фиксации соединений, соответствующей данному выходу 11, в такте ТИ 1 переведены в единичное состояние триггеры 44 соответствующих входов 10. В такте ТИ 2 триггеры, соответствующие входам с Ь приоритетом, сброщены в «нулевое состояние. Таким образом, в конце такта ТИ 2 в каждой строке матрицы 7 фиксации соединений в состоянии логической единицы находится,не более одного тригге) ра.. Третий внутренний тактирующий импульс (ТИ 3) с выхода 42 блока 18 синхронизации используется для фиксации соединительного пути. Если соединитель 1 многокаскадной коммутационной системы (фиг. 14) расположен в последнем (при пе5 редаче адресной информации слева направо в крайнем правом) каскаде, то на вход 15 режима подается логическая «Ь. До прихода ТИ 3 должны быть скоммутированы адресные связи в матричном коммутаторе 9 адресов (фиг. 9). Применительно к данному случаю включены элементы 70i2i. 70i22: 70211. 70212 коммутации, где левый разряд индекса - номер входа, средний разряд индекса - номер выхода, правый разряд индекса --- номер разряда адреса. Соответ5 ственно логическая единица присутствует на выходах 32|2 и управления элементами 70 коммутации.

Сигнал упраЕ ления (фиг. 10) па включение элементов 70 коммутации поступает не раньще появления сигнала на входах 34i

0 и 342 (фиг. 11) плюс задержка срабатывания элементов И 72, ИЛИ 74 и в общем случае элемента 75 согласования уровней. В свою очередь, сигналы на входах 34 и 342 узлов 59i и 592 фиксации запросов достоверны с момента появления ТИ 2

5 (вход 39) плюс задержки срабатывания элементов ИЛИ 62, И 61 и триггера 60 (фиг. 6). Если на входе 15 (фиг. 4) режима логическая «1 и соединитель 1 находится в режи.ме настройки (логическая «1 на выходе 38 блока 18 синхронизации), то по сигналу ТИ 3 сигнал подтверждения соединения с выходов 28 и 282 формирователей 50| и 502 поступает на выходы 11: и 1Ь матричного коммутатора 9 адресов (на фиг. 14 кружочками условно показано сое5 динение группы входов 10 и группы выходов 1 1 для заданной программы соединений). Сигнал с выхода 28 блока 14 посылки подтверждения поступает на вход 292 блока 16 приема подтверждения, а с выхода 282 - на вход 29:. Блок 16 приема под0 тверждения стробируется ТИ 3. В единичное состояние взводятся триггеры 56 приемников 55: и 552 подтверждения блока 16 приема подтверждения (фиг. 4). Сигналы подтверждения по щинам Ili2 и 1022, N22 и 10:2 поступают на щины 11 предыдунхего

5 каскада коммутационной системы. После окончания настройк.и на вход 19 настройки подают логический ноль, что соответствует режиму передачи информации через

соединитель 1. В момент изменения режима на выходе 41 блока 18 синхронизации вырабатывается одиночный импульс (фиг. 3), который сбрасывает в нулевое состояние триггеры 44 узлов 43 фиксации соединений (фиг. 2), на которые не поступает б.:1оки- рующий сигнал по входу 30. С выхода тех триггеров, сброс которых в нулевое состояние блокирован (в данном примере триггеры 44 узлов 4312 и фиксации соединений) сигналами с блока 16 приема под- тверждения, сишал логической единицы поступает на входы блока 5 управления каналами. В режиме передачи информации на выходе 38 блока 18 логическая единица (фиг. 12). Для заданной программы соединения логическая единица на выходах 6i2 и 621 (фиг. 12) и соответственно включены элементы 77 , . , 77„д и , 77218 ко.ммутации (на фиг. 14 кружочками условно показано соединение в матричном коммутаторе 2 каналов группы входов 3 и группы выходов 4). При переходе с режима передачи информации в режим настройки (на вход 19 настройки соединителя 1 вместо логического ноля подают логическую единицу) на выходе 40 блока 18 синхронизации (фиг. 13) вырабатывается единичный импульс (фиг. 2), который сбрасывает в нулевое состояние триггеры 44 матрицы 7 фиксации соединений. На фиг. 15 представлена трехкаскадная коммутационная система, имеющая восемь входов и восемь выходов, предназначенная для пере- дачи информации сверху вниз. В качестве коммутаторов используются соединители 1. в которых , , , . Соединители 95-98 образуют первый каскад, соединители 99-102 - второй каскад, соединители 103-106 - третий каскад. Для так- тирования коммутационной системы используется генератор 107 тактовых импульсов, с группы выходов 108 которого тактовые импульсы поступают на группу тактовых входов 20 (фиг. 1 -13) каждого электронно- го соединителя 95-106 (фиг. 15), входящего в систему. Активные абоненты 109- 116 коммутационной системы (к примеру, микропроцессоры) связаны с пассивными абонентами 117-124 (к при.меру. с запоминающими устройства.ми). На фиг. 15 пока- зан вариант управления входами 19 (настройки электронных соединителей 95-106 от одного) абонента 116 по выходу 125. На вход 15 режима электронных соединителей (фиг. 1) 103-106, образуюндий третий (последний) каскад, постоянно подается по тине 126 логическая единица. На вход 15 режима электронных соедигжтелей 95- 102 подается логический ноль (не показано). В качестве адресных входов электронных соединителей в данном случае используются вертикальные тины, а адресных выходов - горизонтальные ьмины. Пусть приоритет входа «О выше приоритета входа «. Пусть в коммутационной системе требуется осуществля1Ъ nonapiioe соединение абонентов 109 1 121, 115 и 1 18, III и 123, ИЗ и 124. Двоичные номера пассивных абонентов при заданной конфигурации коммутационной сети: 121--100о, 118--0012. ,., 124- 11L (фиг. 15). При переходе с режима передачи информации в режим настройки (на выходе 125 абонента 116 логический ноль переходит в логическую единицу) все коммутирующие элементы электронных соединителей 95--106 выключа.ются. В первом такте внещ него тактового генератора i07 происходит коммутация в первом каскаде и абоне 1ты 109, 111, 113, 115 выставляют на своих выходах соответственно логические сигналы «1, «1, «1, «О. Во втором такте па выходах абонентов 109. 111, 113, 115 «О, «1, «1, «О. В третьем такте на выходах абонентов 109, 111, i;3, 115 -- -:(Ь, «о, «1. «1. в конце третьего такта по внутреннему такту ТИ 3 производится фиксация соединительного пути и при переходе s режим передачи Илформащ и сбрасываются в нулевое состояние триггеры 44 (фиг. 2). на вход которых не пpинJЛO |;одтверждение организации соединительного пути с третьего каскада. Для заданно ; программы коммутации это триггер электронного соединителя 97, управляющий соединителем нулевого входа с единичным выходом (на фиг. 15 э,емент коммутации условно показан квадратом). Триггер электронного соединителя 100, управ- ЛЯЮП1ИЙ соединением единичного входа с едн- ничным выходом, сброшен в нулер)Ое состоя- пне б. юка приоритетов (нриоритот ну.певого входа выше). Таким образом, осуществлена попарная коммутация абонентов 09, 121, 115 и 118, 11 и 123. Абоненты 113 и 124 не соединяются вследствие блокировки в комму- тационно сети (информационные связи на фпг. 15) не ;юказаны, так как они ана- логичн адресным связям).

Формила изобретения

Соедиппте. ч- многокаскадной комму- auHOHnoii системы, содержании матричный коммутатор Kai-ia.TOB, группа информационных входов и группа информацио11ных выходов которого являются cooTBCTCTBeiiHO грчн- ггами информаци{)пных входов и кыхе.дов стройетва, матрицу фиксации соединений размером /пХ, I pynna из вь ходов которой соединена с группой выходов для подключения Biienjnei O коммутатора и с входами блока управления кана.:1амн, выход которого подчл1очег ы к управляющим входам матричного ком.утатора кана.моп. о .г- ли- иющийск тем, что, с целью повыщепия быстродейств:1я, достоверности фу1п циониро- вания и расширения .ональных возможностей за счет дновременно1Ч ) парал- ,лельно1 О поиска и фиксации произво, 1ьпо- го числа каналов в MHoroKacKa;iMoii ком9

мутационной системе, в устройство введены матричный коммутатор адресов, группы ад- рес}1ых входов и выходов которого являются соответственно грунпами адресных входов и выходов устройства, блок управления адресами, блок дешифрации адресов, блок посылки подтверждения, вход режима которого является входом режима устройства, блок приема подтверждения, блок приоритета, блок синхронизации, в котором вход настройки и групна тактовых входов являются соответственно входом настройки и группой тактовых входов устройства, блок гшнятости выходов, блок фиксации запросов, группа из m информационных входов которого соединена с второй группой из т информационных выходов матрицы фиксации соединений, первая группа из п информационных входов которой соединена с группой информацинных выходов блока приоритета, группа из п информационных входов которого соединена с группой из п информационных входов блока занятости выходов и с третьей гругиюй из п выходов матрицы фиксации соединений, вторая группа из п информационных входов которой соединена с первой группой из п информационных выходов блока занятости выходов, вторая группа из п информационных выходов которого соединена с группой из п информационных входов блока посылки подтверждения, группа из п информационных выходов которого соединена с группой из п информационных выходов матричного коммутатора адресов, группа из т информационных входов которого соединена с группой из т информационных входов блока приема подтверждения, группа из т информационных выходов которого соединена с третьей группой из m информационных входов матрицы фиксации соединений, четвертая группа из т информационных входов которой соединена с группой из т информационных выходов блока дешифра1

10

5

ции адресов, группа из m информационных входов которого соединена с группой из т информационных входов матричного коммутатора адресов, группа из mX« входов управления которого соединена с группой из mXrt выходов блока управления, адресами, первая группа из тХ информационных входов которого соединена с первой группой из тХ« информационных выходов мат- рицо фиксации соединений, а вторая группа

0 из m информационных входов блока управления адресами соединена с первой группой из m выходов блока фиксации запросов, вторая группа из m выходов которого соединена с пятой группой из т информационных входов матрицы фиксации соединений, первый вход управления которой соединен с первым выходом блока синхронизации, второй выход которого связан с вторым входом управления матрицы фиксации соединений, первым входом управления

Q блока посылки подтверждения, первым входом управления блока приема подтверждения, первым входом управления блока управления адресами, второй вход управления которого соединен с входом управления блока управления канала(1и и с третьим вы5 ходом блока синхронизации, четвертый выход которого соединен с первым входом управления блока занятости выходов, третьим входом управления матрицы фиксации соединений, первым входом управления блока фиксации запросов, второй вход управления ко0 торого соединен с вторым входом управления блока приема подтверждения, вторым входом управления блока занятости выходов, пятым выходом блока синхронизации и четвертым входом управления матрицы фиксации соединений, пятый вход управления которой соединен с шестым выходом блока синхронизации, седьмой выход которого соединен с третьим входом управления блока приема подтверждения и с вторым входом управления блока посылки подтверждения.

Фиг.З

J/ б 25

.Ю

го

г/

5

3

W

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2111532C1 |

| Устройство межмашинной связи | 1987 |

|

SU1474666A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Процессор | 1983 |

|

SU1213485A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Коммутационное устройство для мультипроцессорной системы | 1976 |

|

SU734697A1 |

Изобретение относится к импу.пьсной технике, электронной коммутации и связи и может быть использовано в вычислите.аьных и автоматических системах с перестраиваемой структурой. Цель изобретения - повышение быстродействия, достоверности функционированмя и расширение функциональных возможностей. Соединитель 1 содержит матричный коммутатор 2, блок 5 унрав.че- ния каналами, матрицы 7 фиксации соединений, коммутатор 9 адресов, блок 12 управления адресами, блок 13 дешифрации адресов, блок 14 посылки подтверждения, блок 16 приема подтверждения, блок 17 приоритета, блок 18 синхронизации, блок 21 занятости выходов, блок 22 фиксации запросов, группу из информационных входов и группу из т информационных выходов. Введение в устройство матричного коммутатора адресов, блоков уцравлепия адресами, их дешифрации, посылки и приема подтверждения, приоритета, синхронизации, занятости выходов, фиксации запросов позволило обесг1ечить од- новрсмеиный параллельный поиск и фиксацию произвольного числа каналО в многокаскадной коммутационной системе. 15 ил. СО

85

13

52

J7 да

«7

50

5/

г

. 15

| В П Т Б | 0 |

|

SU396831A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Модуль многокаскадной коммутационной системы | 1975 |

|

SU769741A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-23—Публикация

1984-11-01—Подача