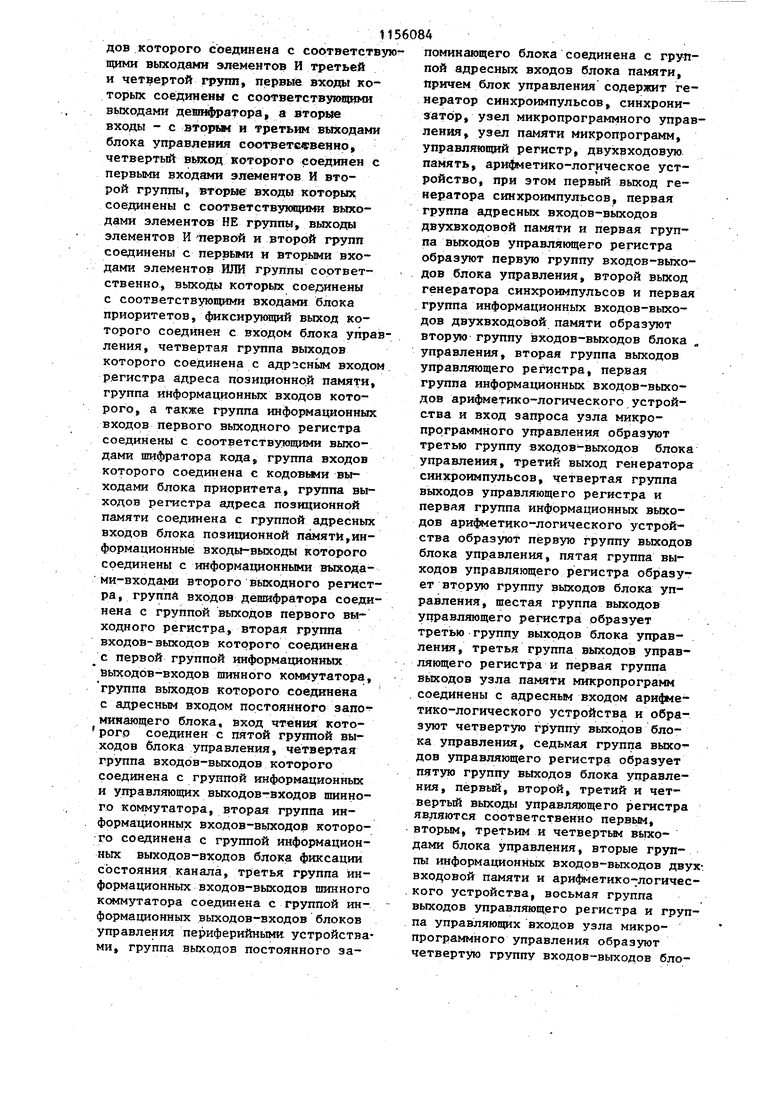

дов которого еоединема с соответству щими выходами элементов И третьей и четвертой групп, первые входь( которых соединены с соответствзпмцими выходами дешифратора f а вторые входы - с вторым и третьим выходами блока управления соответственно, четвертый вьчсод которого соединен с первыми входами элементов И второй группы, вторые входы которых соединены с соответствзпощими выходами элементов НЕ группы, выходы элементов И Первой и второй групп соединены с первьми и вторыми входами элементов ИЛИ группы соответственно, выходы которых соединены с соответствующими входами блока приоритетов, фиксирующий выход которого соединен с входом блока упраления, четвертая группа выходов которого соединена с адрггсным входо регистра адреса позищюнной памяти, группа информационных входов которого, а также группа информационных входов первого выходного регистра соединены с соответствующими выходами шифратора кода, группа входов которого соединена с кодовыми выходами блока приоритета, группа выходов регистра адреса позиционной памяти соединена с группой адресных входов блока позиционной памяти,информационные входы-выходы которого соединены с информационными выходами-входами второго выходного регистра , ГРУППА входов дешифратора соединена с группой выходов первого выходного регистра, вторая группа входов-выходов которого соединена с первой группой информационных выходов-входов пганного комму татора, группа вь1ходов которого соединена с адресным входом постоянного запомияающего блока, вход чтения которого соединен с пятой группой выходов блока управления, четвертая группа входов-выходов которого соединена с группой информационных и управляющих выходов-входов шинного коммутатора, вторая группа информационных входов-выходов которого соединена с группой информационных выходов-входов блока фиксации состояния канала, третья группа информационных входов-выходов шинного коммутатора соединена с группой информационных выходов-входов блоков управления периферийными устройствами, группа выходов постоянного запомина1рщего блока соединена с группой адресных входов блока памяти, причем блок управления содержит генератор синхроимпульсов, синхронизатор, узел микропрограммного управления, узел памяти микропрограмм, управляющий регистр, двухвходовую память, арифметико-логическое устройство, при этом первый выход генератора синхроимпульсов, первая группа адресных входов-выходов двухвходовой памяти и первая группа выходов управляющего регистра образуют первую группу входов-выходов блока управления, второй выход генератора синхроимпульсов и первая группа информационных входов-выходов двухвходовой памяти образуют вторую группу входов-выходов блока , управления, вторая группа выходов управляющего регистра, первая группа информационных входов-выходов арифметико-логического устройства и вход запроса узла микропрограммного управления образуют третью группу входов-выходов блока управления, третий выход генератора синхроимпульсов, четвертая группа выходов управляющего регистра и первая группа информационных выходов арифметико-логического устройства образуют первую группу выходов блока управления, пятая группа выходов управляющего регистра образует вторую группу выходов блока управления , шестая группа выходов управляющего регистра образует третью группу выходов блока управления, третья группа выходов управляющего регистра и первая группа выходов узла памяти микропрограмм . соединены с адресньм входом арифметико-логического устройства и образуют четвертую группу выходов блока управления, седьмая группа выходов управляющего регистра образует пятую группу выходов блока управления, первый, второй, третий и четвертый выходы управлжощего регистра являются соответственно первым, вторым, третьим и четвертьм выходами блока управления, вторые группы информационных входов-выходов двувходовой памяти и арифметико-логического устройства, восьмая группа выходов управляющего регистра и группа управляющих входов узла микропрограммного управления образуют четвертую группу входов-выходов блока управления, вход опроса узла микропрограммного управления образует вход блока управления, при этом в блоке управления первый выход генератора синхроимпульсов соединен с входом синхронизатора группа выходов которого соединена с соответствующими тактирующими входами управляющего регистра, узла памяти микропрограмм, узла микропрограммного управления и арифметико-логического устройства, вторая группа информационных выходов которого соединена с второй группой адресных входов двухвходовой памяти, группа входов режима работы которой соединена с

девятой группой выходов управляющего регистра, десятая группа выходов которого соединена с входом режима . работы арифметико-логического устройства, группа управляющих выходов которого соединена с входом признака операции узла микропрограммного управления, группа информационных входов-выходой которого соединена с однрименнь ш входами-выходами узла памяти микропрограмм, вторая группа выходов которого свединена с информационным входом заправляющего регистра одиннадцатая группа выходов которого соединена со входом режима работы синхронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Микропрограммный мультиплексный канал | 1985 |

|

SU1305693A2 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для распределения подканалов | 1981 |

|

SU1003065A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Селекторный канал | 1983 |

|

SU1226477A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Устройство для назначения подканалов | 1984 |

|

SU1264189A1 |

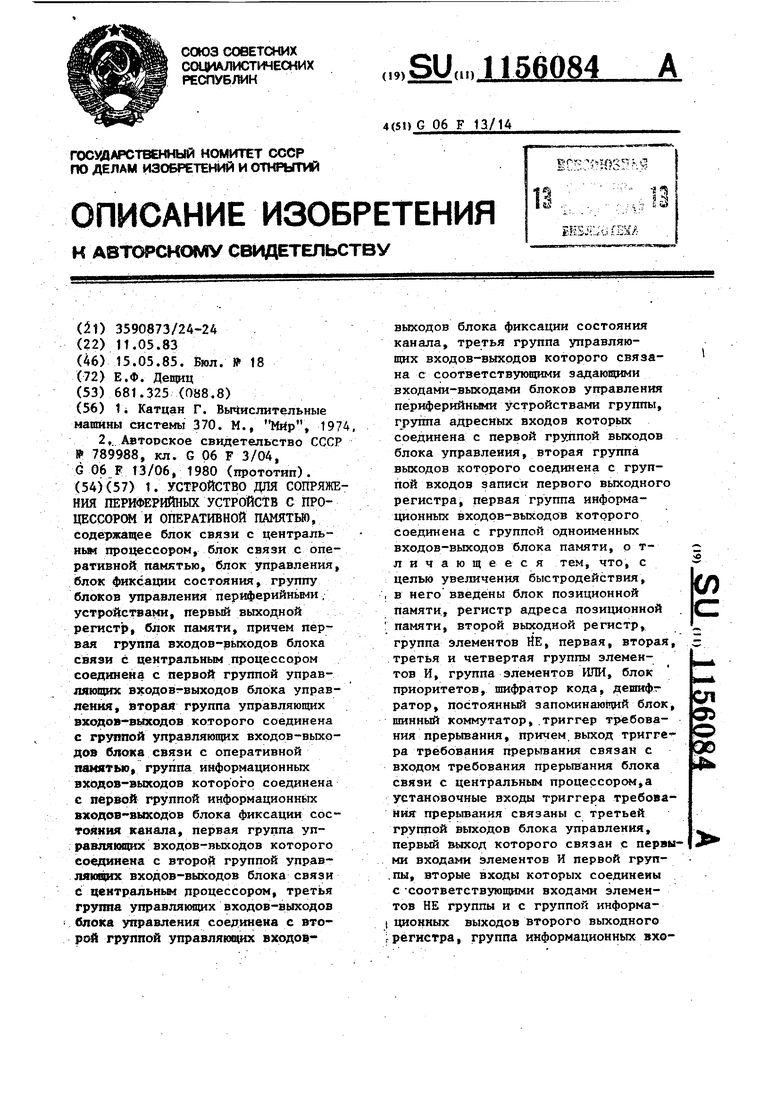

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПЕРИФЕРИЙНЫХ УСТРОЙСТВ С ПРОЦЕССОРС И ОПЕРАТИВНОЙ ПАМЯТЬЮ, содержащее блок связи с центральньм процессором, блок связи с оперативной памятью, блок управления, блок фиксации состояния, группу блоков управления периферийньми, устройстеами, первый выходной регистр, блок памяти, причем первая группа входов-выходов блока связи с центральньв 1 процессором соединена с первой группой управляющих входов-выходов блока управления, вторай группа управляющих входов-выходов которого соединена с группой управляющих входов-выходов блока связи с оперативной шмятью, группа информационных входов-выходов которого соединена с первой группой информационных входов-выходов блока фиксации состояния канала, первая группа управлягацих входов-выходов которого соединена с второй группой управляющих входов-выходов блока связи с центральньм процессором, третья группа управляющих входов-выходов блока управления соединена с второЛ группой управлякхщх входоввыходов блока фиксации состояния канала, третья группа управляющих входов-выходов которого связана с соответствующими задающими входами-выходами блоков управления периферийными Устройствами группы, группа адресных входов которых соединена с первой группой выходов блока управления, вторая группа выходов которого соединена с группой входов записи первого выходного регистра, первая группа информационных входов-выходов которого соединена с группой одноименных входов-выходов блока памяти, о тличающееся тем, что, с целью увеличения быстродействия, (Л , в него введены блок позиционной памяти, регистр адреса позиционной памяти, второй выходной регистр, группа элементов НЕ, первая, вторая, третья и четвертая группы элементов И, группа элементов ИЛИ, блок приоритетов, шифратор кода, дешифг СП ратор, постоянный запоминаюп ий блок, 3d шинный коммутатор,.триггер требоваО ния прерывания, причем, выход триггеро ра требования прерьтаания связан с входом требования прерьшания блока связи с центральным процессоре,а установочные входы триггера требования прерывания связаны с третьей группой выходов блока управления, первый выход которого связан с первы-I ми входами элементов И первой груп.пы, вторые входы которых соединены с Соответствующими входами элементов НЕ группы и с группой информационных выходов второго выходного г регистра, группа информационных вхо

Изобретение относится к-вычислительной технике и может быть использовано в вычислительных системах.

Известно устройство для управления обменом меязду оперативной памятью и периферийными устройствами, содержащее блок управления каналами, блок связи с оперативной памятью, блок микропрограммного управления, управляющую память микраграмм, каналы, в состав которых входи буфер прерывания, блок управления канала, входной и выходной регистры информации, память

подканалов СО«

Недостатком этого устройства является наличие достаточно большой по объему памяти подканалов, (по количеству периферийных устройств, .число которых в канале может достигать 256) .

Наиболее близким к предлагаемому является устройство, содержащее блок управления общего канала, общий канал, блок связи с оперативной памятыо, блок связи с центральным процессором, каналы, пер,иферийньй устройства, блок динамического распределения подканалов, которьй содержит блок памяти с выходным регистром блока памяти 23.

Недостатком данного устройства является нахождение подканала путем сканирования таблицы ключей, что

требует достаточно больщого вре.мени. При этом отсутствует конвейерная обработка инструкций ввода-вывода, заключающаяся в том, что подготовка следующей инструкции ввода-вывода для данного периферийного устройства (или группы периферийных устройств, объединенных одним управляющим устр ойством) производится во время выполнения текущей инструкции ввода-вьгоода для того же периферийного устройства при условии, что вычислительная система работает в мультипрограммном режиме, а периферийное устройство закреплено для выполнения операций ввода-вывода одновременно для нескольких программ. Подготовка инструкции ввода-вывода состоит из

следующих операций:. выборка самой инструкции, выборка адресного слова канала и командного слова канала, их обработка, формирование управляющего слова канала, выборка

информации из оперативной памяти в режиме вывода на периферийное устройство, достаточной для того, чтобы начать вывод.

Инструкция, которая подготовлена описанным способом, выполняется по получении указателя Устройство кончило. Окончание инструкщш ввода-вьгоода, которая осталась невыполненной - вьщача запроса на прерьгаание в центральный процессор и пересыпка в него слова состояния канала, должно выполняться независимо от выполнения новой инструкции ввода-вывода. Конвейерная обработка инструкций ввода-вывода позволяет эффективнее использовать периферийные устройства самого устройства и получить увеличение быстродействия вычислительной системы, работающей в мультипрограммном pejKiDte, Конвейерная обработка инструкций ввода-вывода позволяет увеличить быстродействие вычислительной системы при выполнении инст1:зкций , ввода-вывода, в управляющих словах канала которой .содержатся флажки цепочек данньрс и цепочек команд, для любых периферийных устройств. Цель изобретения - увеличение быстродействия за счет использования конвейерной обработки инструкций ввода-вьгаода. Поставленная цель достигается тем, что в устройство для сопряжения периферийных устройств с процес сором и оперативной памятью, содержащем блок связи с центральным процессором,блок связи с оперативной памятью,блок управления,блок фиксац состояния канала,группу блоков управления периферийными устройствами первый выходной регистр, блок памят причем первая группа входов-выходов блока связи с центральньм процессором соединена с первой группой упра ляющих входов-выходов блока управ гления, вторая группа управляющих входов-выходов которого соединена с группой управляющих входов-выходов блока связи с оперативной памятью, группа информационных входов-выходо которого соединена с первой группой информационных входов-вькодов блока фикса1ши состояния канала, первая группа управляющих входов-выходов которого соединена с второй группой упр авляющих входов-выходов блока св зи с центральным процессором, трет группа управляющих входов-выходов блока управления соединена с второ группой управляющих входов-выходов блока фиксации состояния канала, третья группа управляющих входов-в ходов которого связана с соответст вующими, задающими входами-выходами блоков управления периферийными устройствами группы, группа адресных входов которых соединена с первой группой выходов блока управления, вторая группа вькодов которого соединена с группой входов записи первого выходного регистра, первая группа информационных входов-выходов которого соединена с группой одноименный входов-выходов блока памяти, в него введены блок позиционной памяти, регистр адреса позиционной памяти, второй выходной регистр, группа элементов НЕ, первая, вторая, третья и четвертая группы элементов И, группа элементов ИЛИ, блок приоритетов, шифратор кода, дешифратор, постоянный запоминающий блок, шинный коммутатор, триггер требования прерывания, причем выход триггера требования прерывания связан с входом требования прерьГвания блока связи с центральным процессором, а установочные входы триггера требования прерывания связаны с третьей группой выходов блока управления, первьй выход которого связан с первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими входами элементов НЕ группы и с группой информационных выходов второго выходного регистра, группа информационных входов которого соединена с соответствующими выходами элементов И третьей и. четвертой групп, первые входы которых соединены с соответствующими выходами дешифратора, а вторые входы - с вторым и третьим выходами блока управления соответственно, четвертый выход которого соединен с первыми входами элементов И второй группы, вторые входы которых соединены с соответствующими вьпсодами элементов НЕ группы, выходы элементов И первой и второй групп соединены с первыми и вторьми входами элементов ИЛИ группы соответственно, выходы которых соеди- j нены с соответствующими входами блока приоритетов, фиксирующий выход которого соединен с входом блока управления, четвертая группа выходов которого соединена с адресным входом регистра адреса позиционной памяти, группа 1шформационных ВХОДОВ которого, а также группа информационных входов первого

выУодного регистра соединены с со ответствующями выходами шифратора кода, группа входов которого соединена с кодовьми выходами блока приоритета, группа выходов регистра адреса позиционной памяти соединена с группой адресных входов блока позиционной памяти, информационные входы-выходы которого соединены С информационными выходами-входами второго выходного регистра, группа входов девшфратора соединена с группой выходов первого выходного регистра, вторая группа входов-выходов которого соединена с первой группой информационных выходов-входов шинного коммутатора, группа выходов которого соединена с адресньм входом постоянного запоминающего блока, вход чтения которого соединен с пятой группой выходов блока управления, четвертая группа входов-выходов которого соединена с группой информационных и управляющих выходов-входов шинного коммутатора, вторая группа информационных входов-выходов которого соединена с группой информационных выходов-входов блока фиксации состояния канала, третья группа информационных входоввыходов шинного коммутатора соединена с группой информационных выходоввходов блоков управления периферийньми устройствами группы,группа выходов постоянного запоминающего блока соединена с группой адресных входов блока памяти, причем блок управления содержит генератор синхроимпульсов, синхронизатор, узел микропрограммного управления,узел памяти микропрограмм, управляющий регистр, двухвходовую память, арифметико-логическое устройство, при этом первый выход генератора синхроимпульсов, первая группа адресных входов-выходов двухвходовой памяти и первая группа выходов управляющего регистра образуют первую группу входов-выходов блока управления, второй выход генератора синхроимпульсов и первая группа информационных входов-выходов двухвходовой памяти образуют группу входов-выходов блрка управления, вторая группа выходов управляющего регистра, первая группа информациоч ных входов-выходов арифметико-логического устройства ивход запроса микропрограммного управления

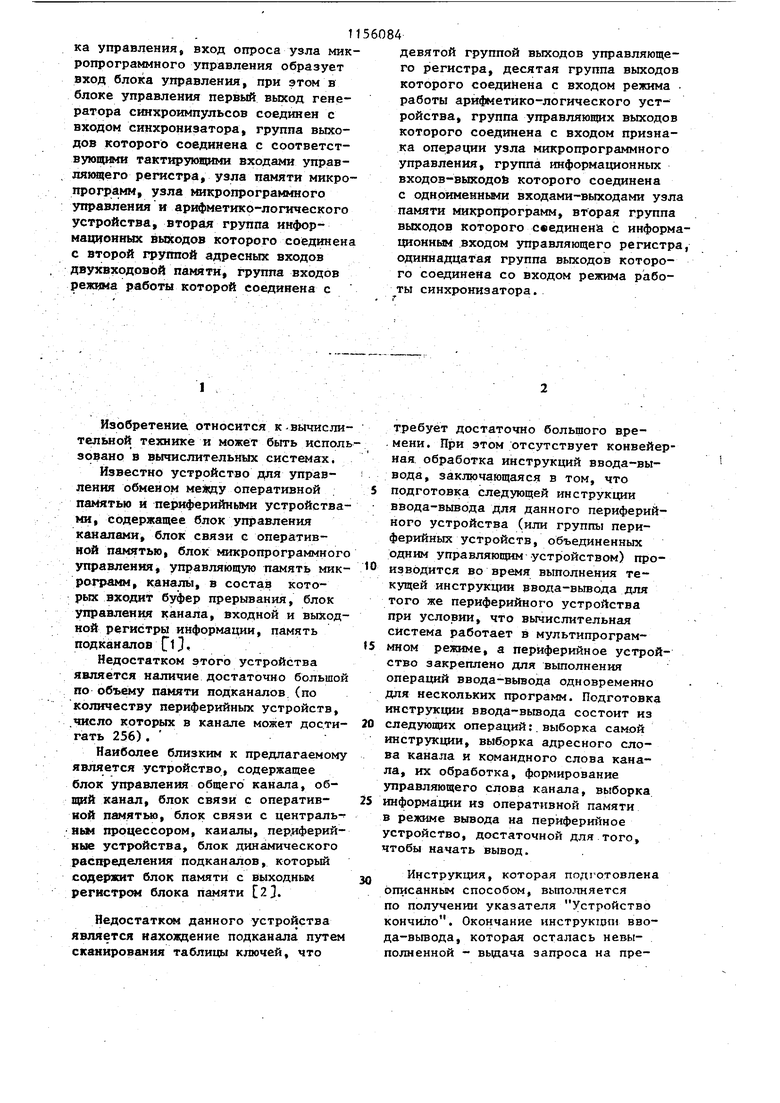

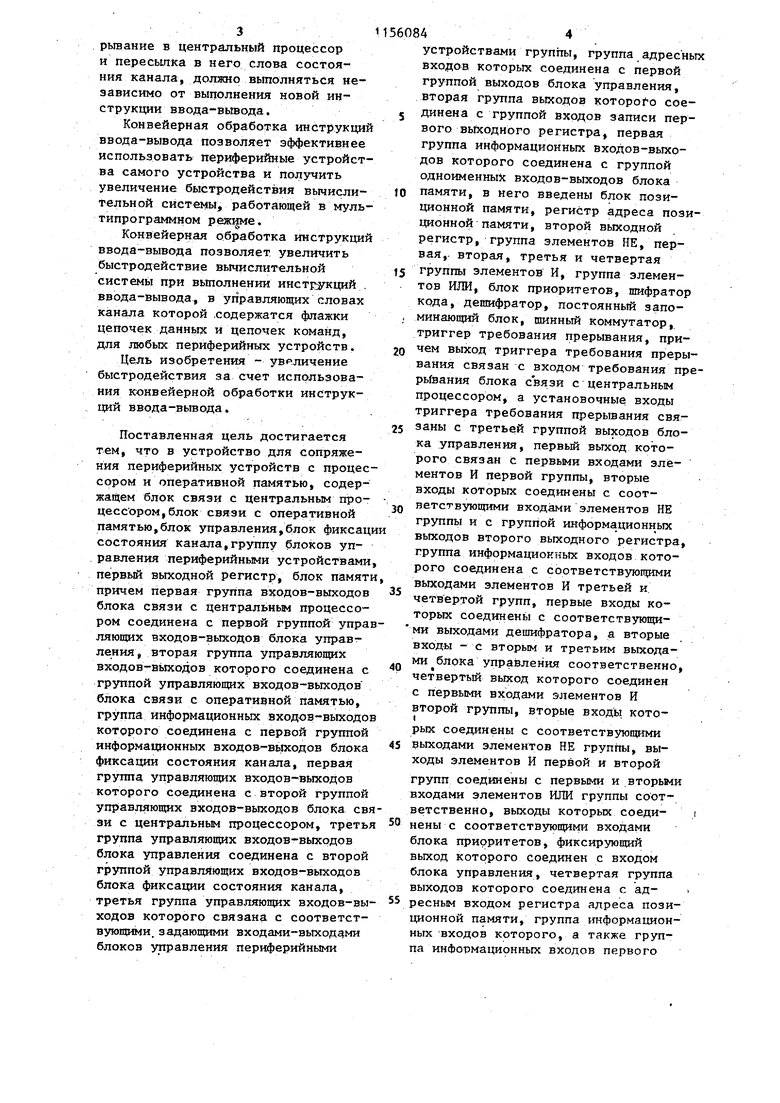

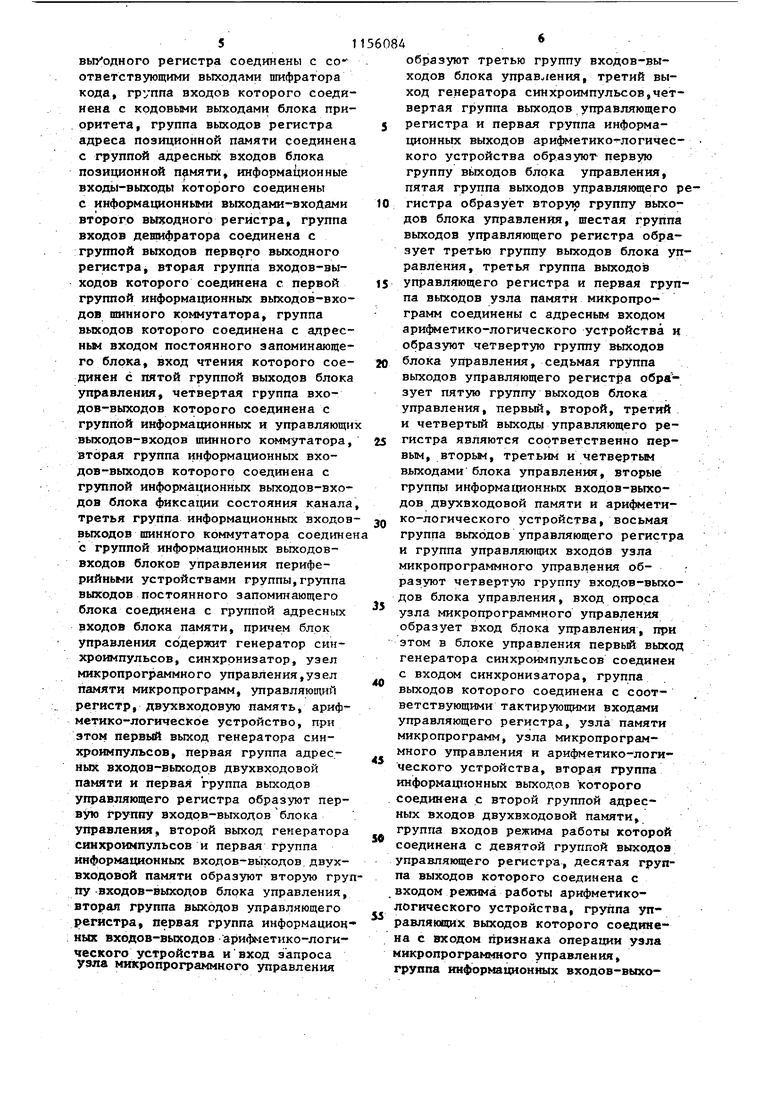

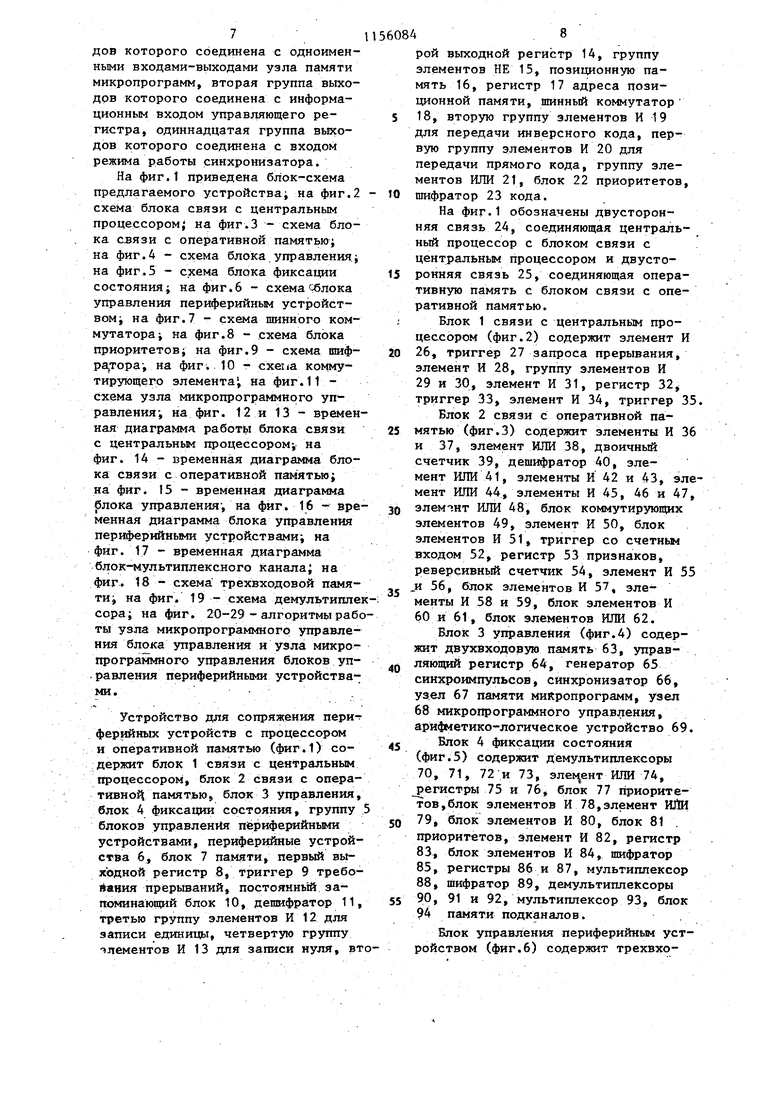

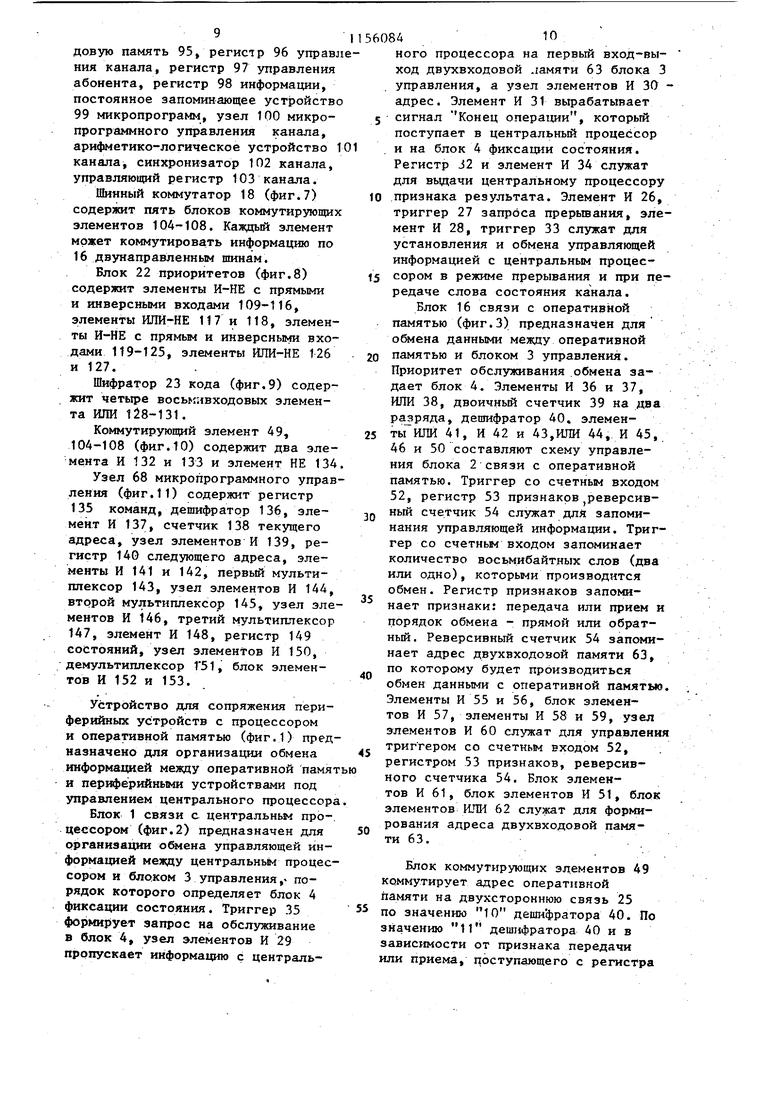

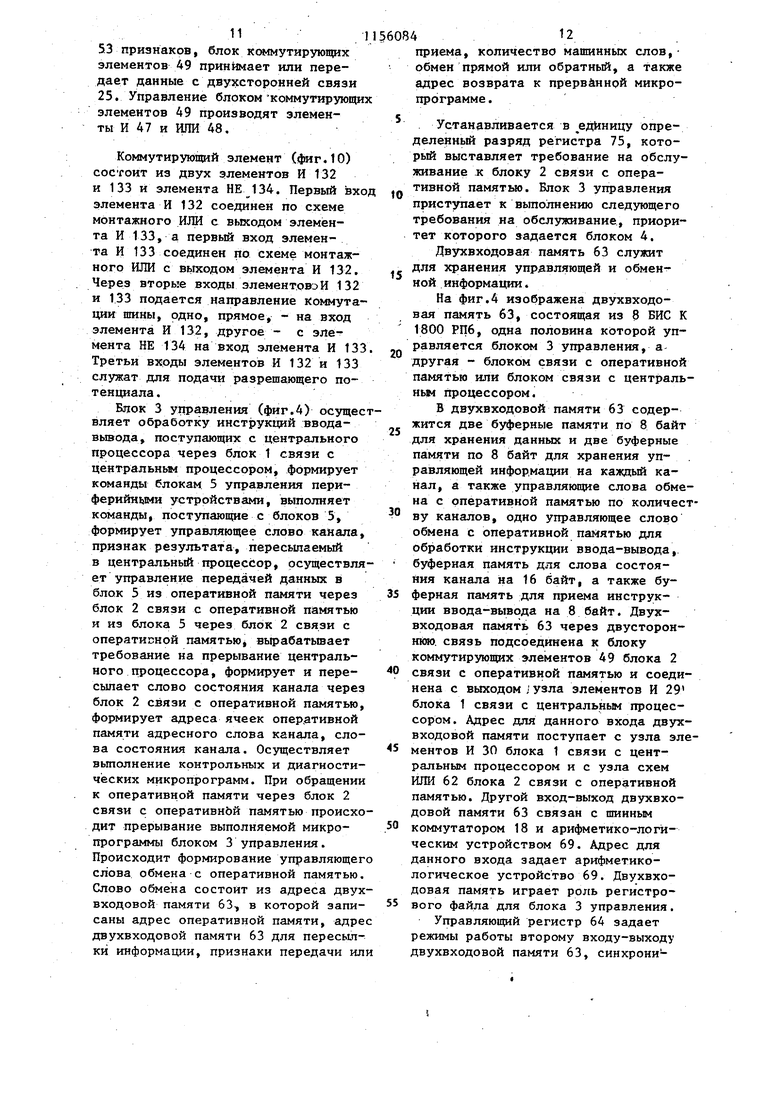

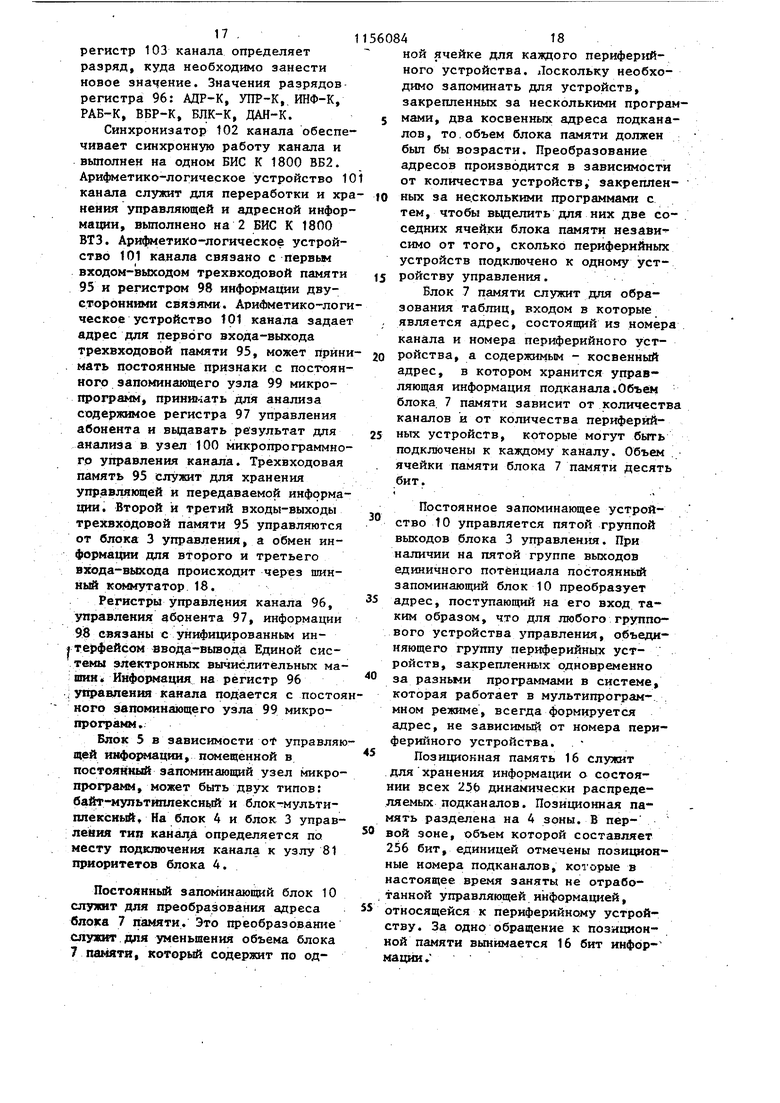

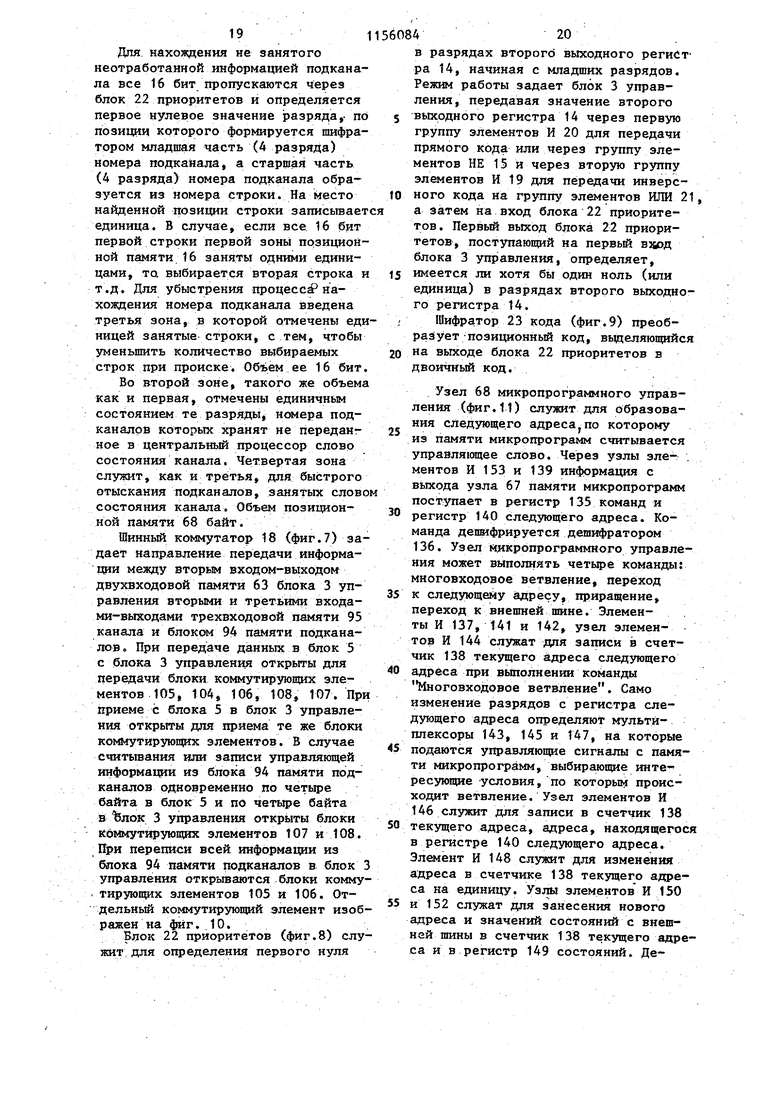

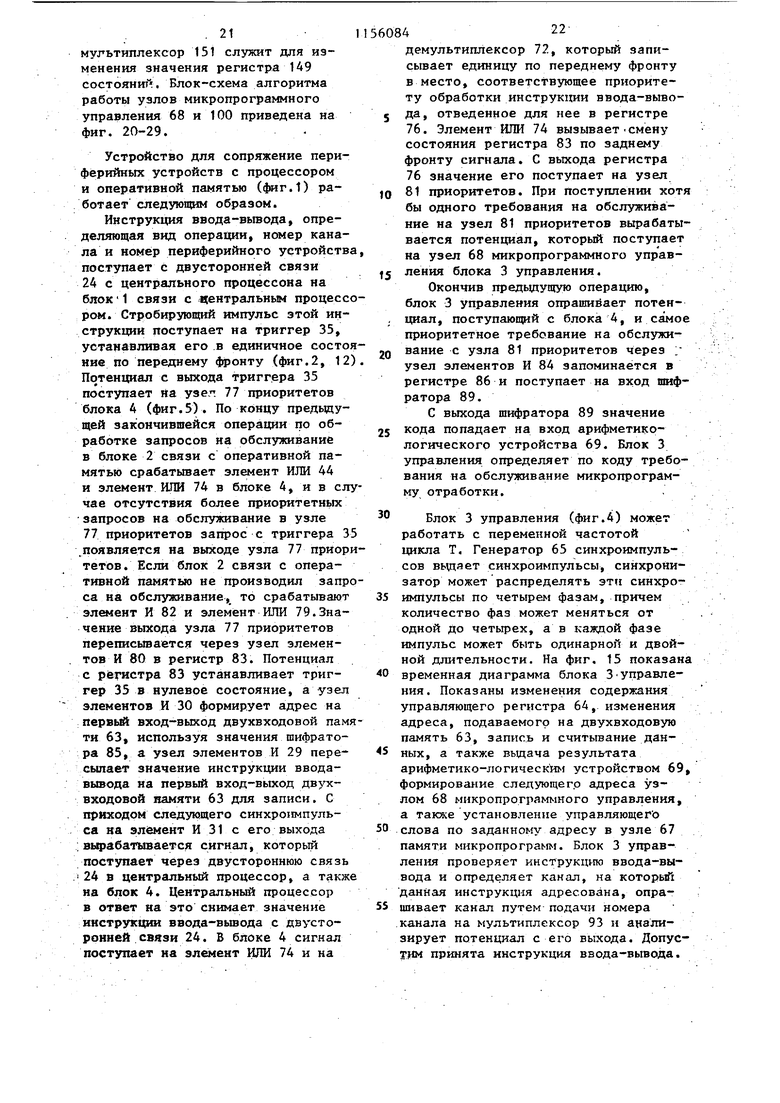

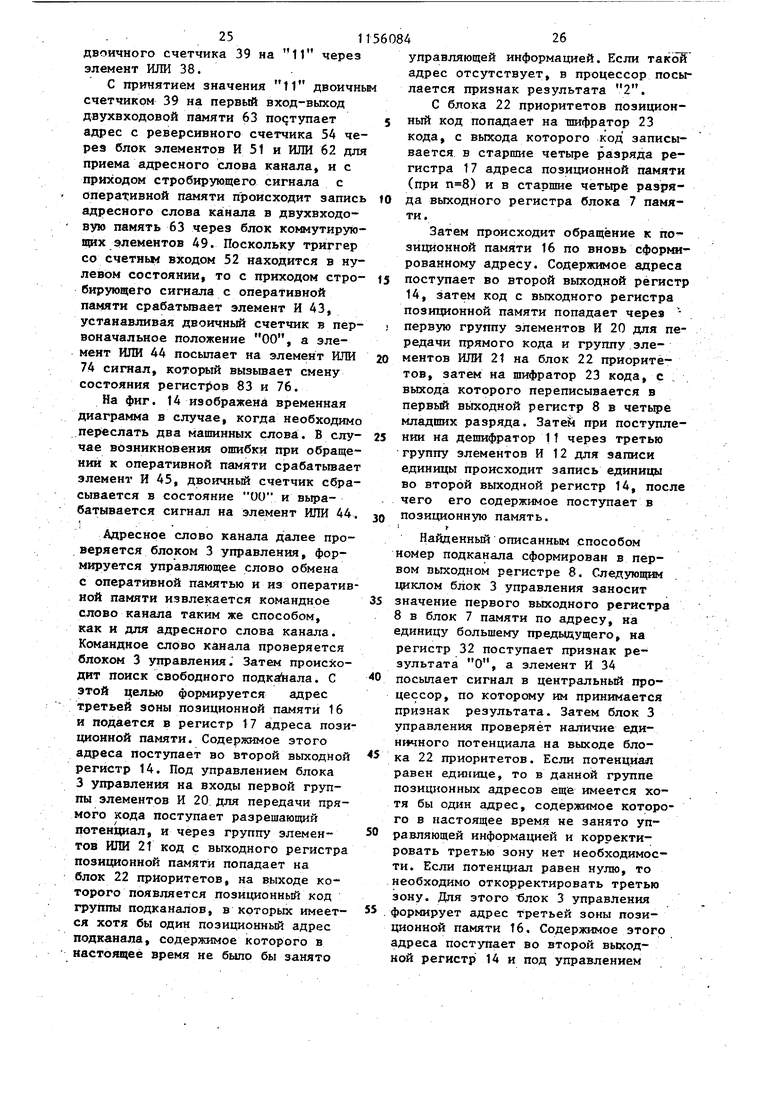

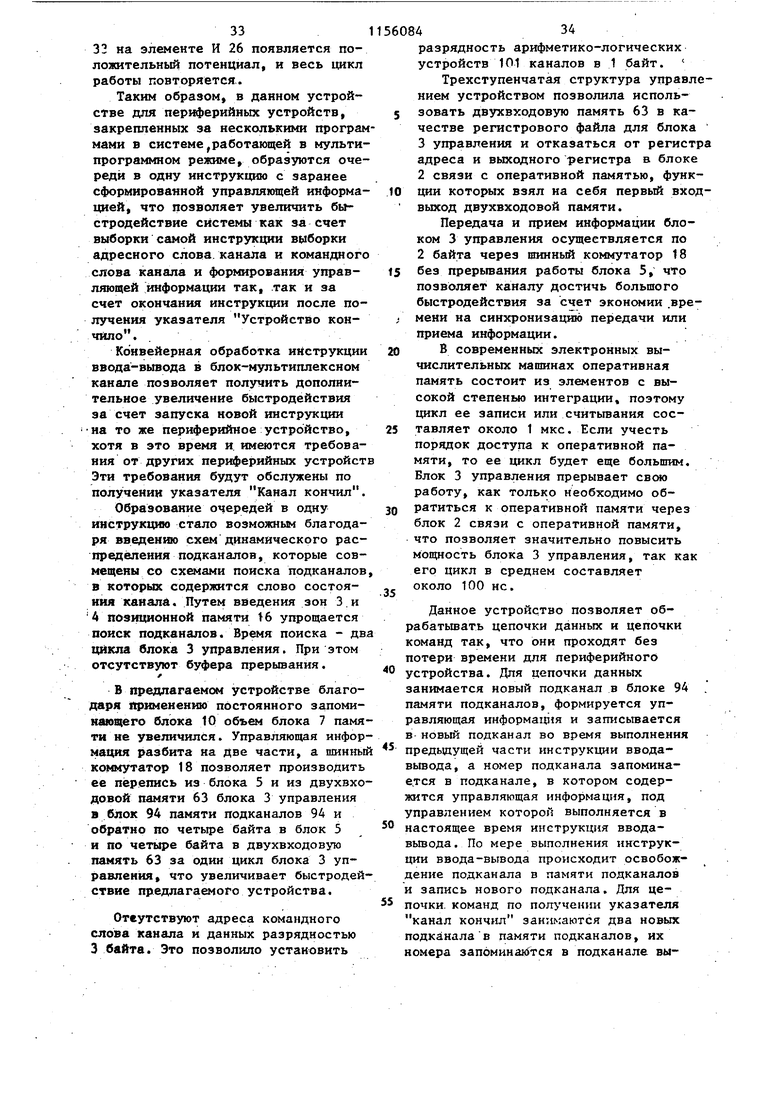

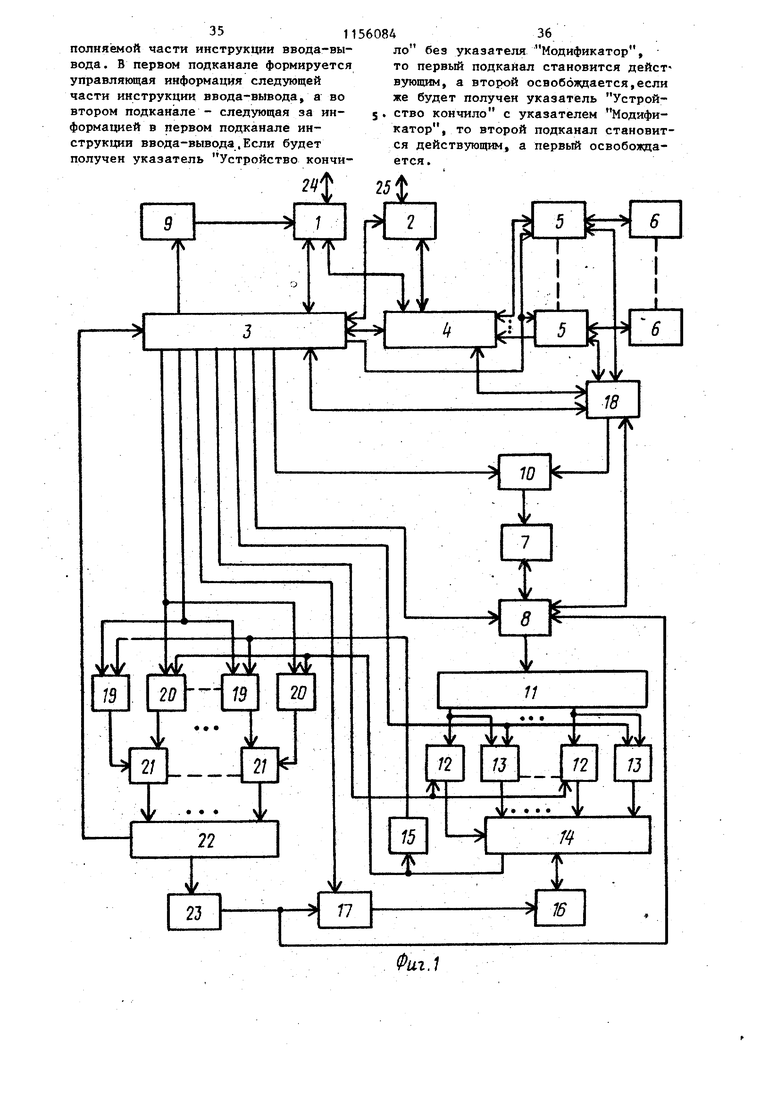

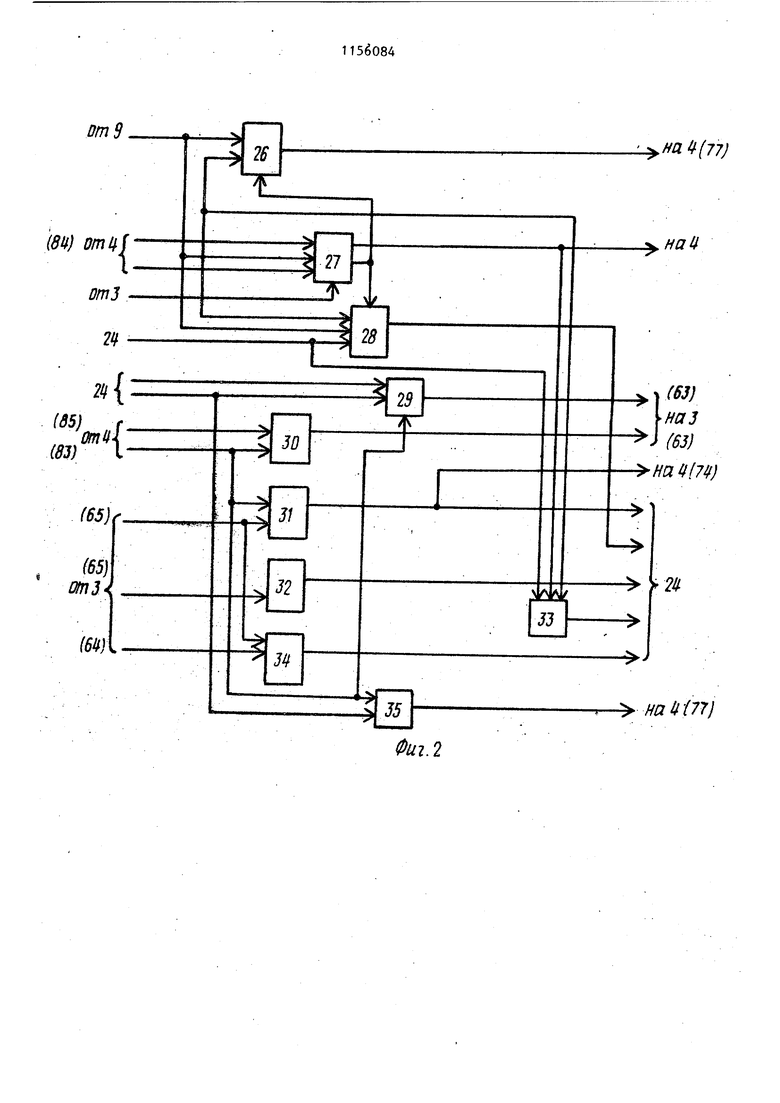

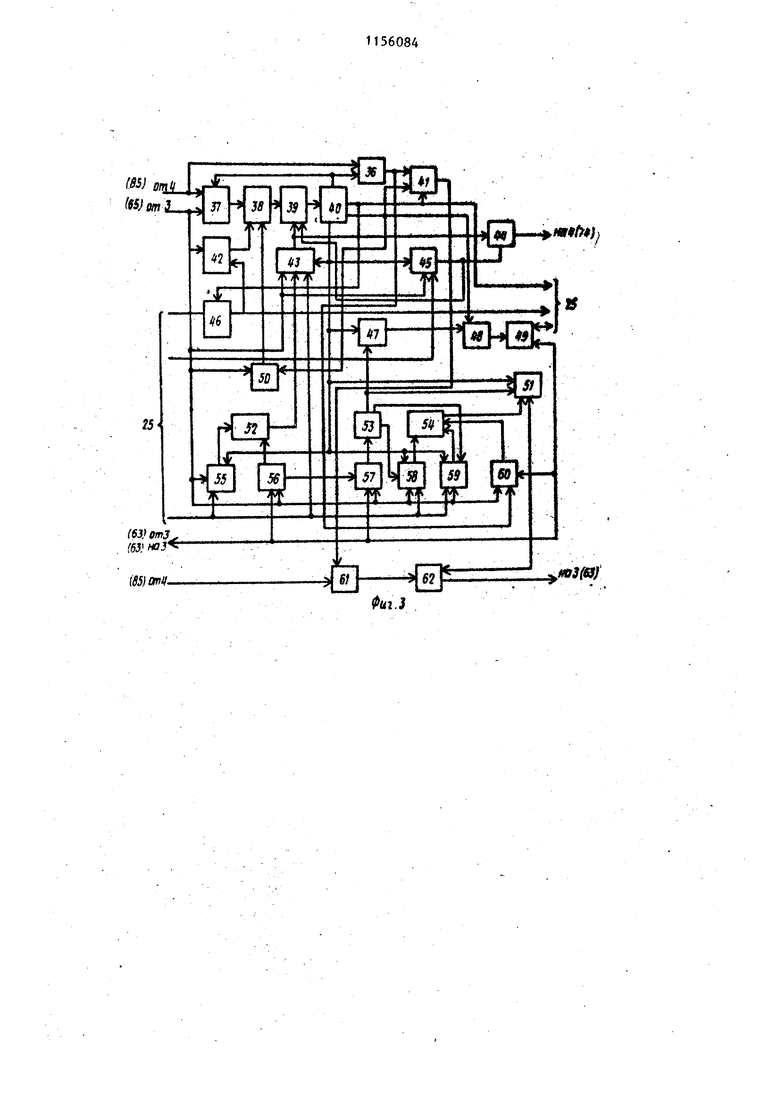

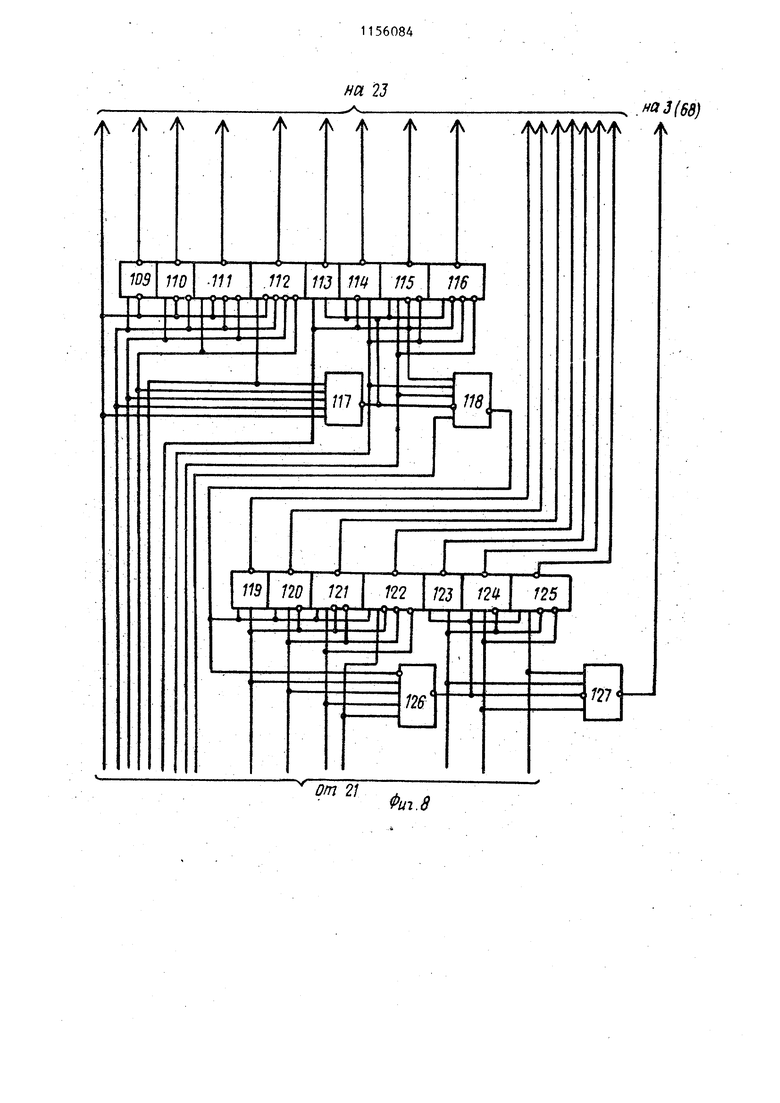

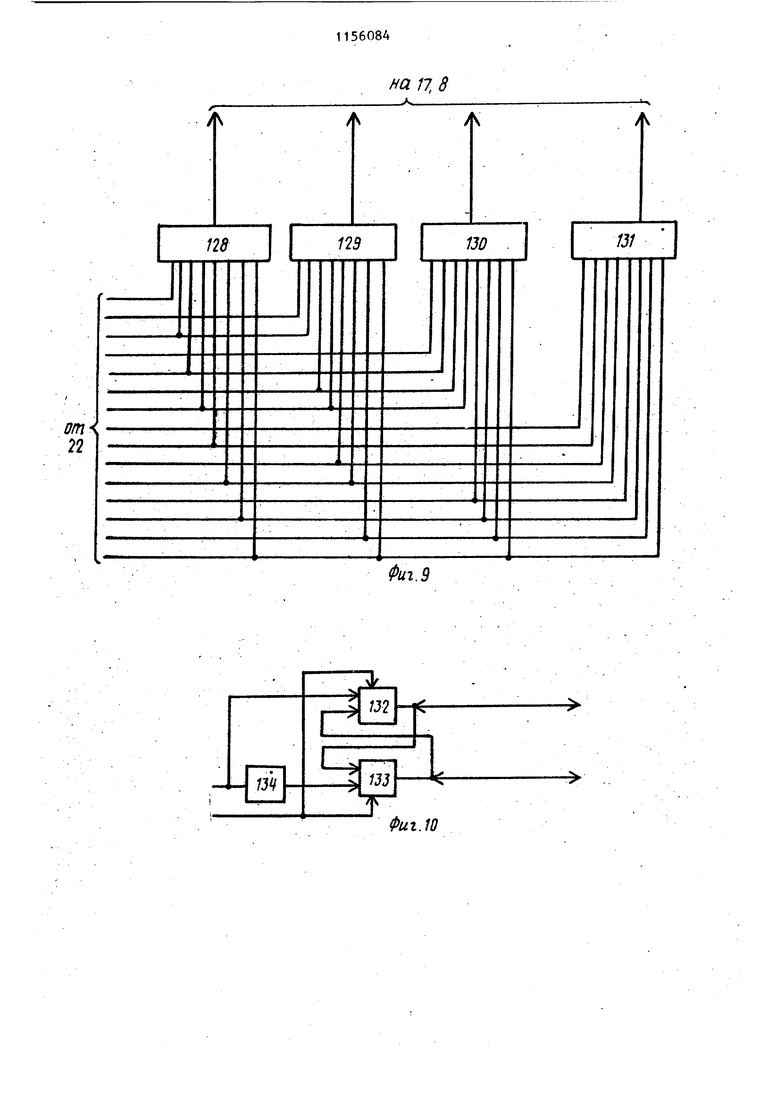

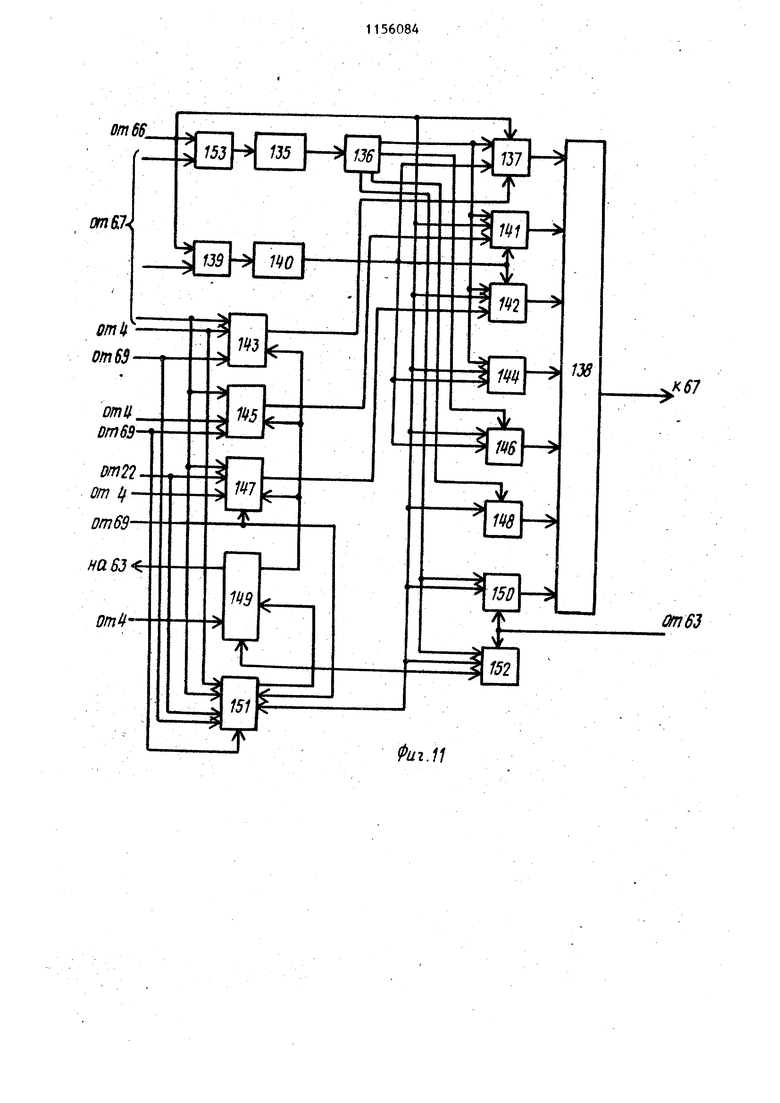

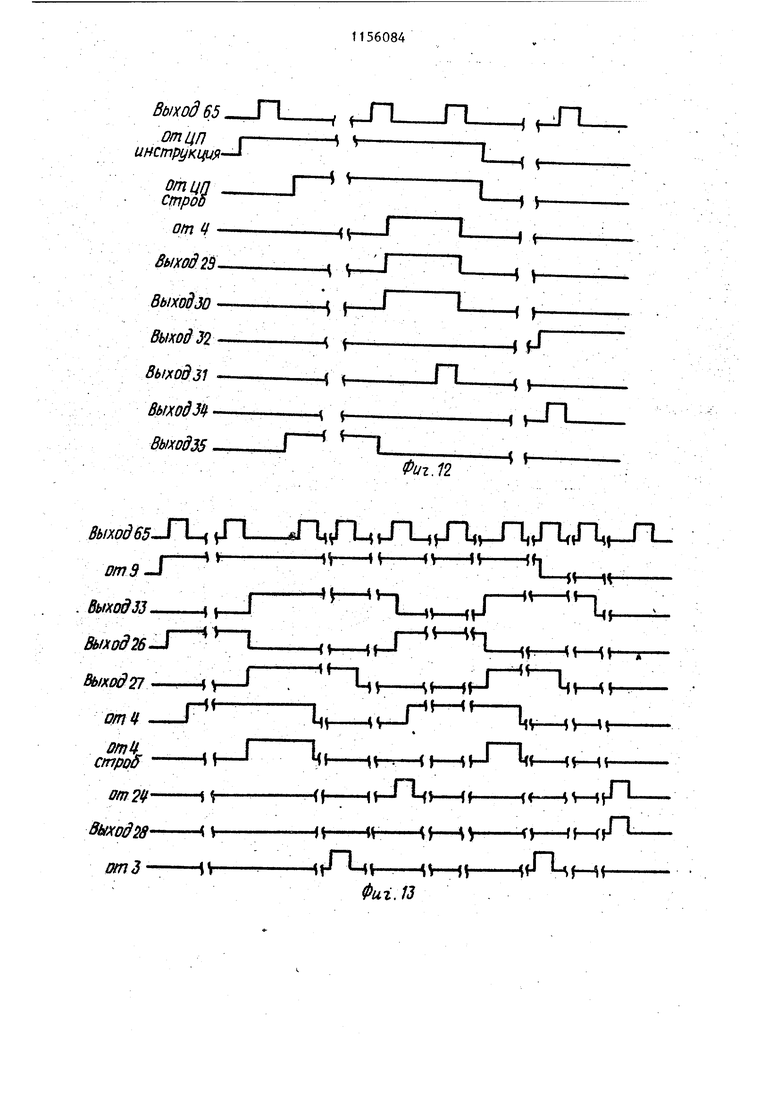

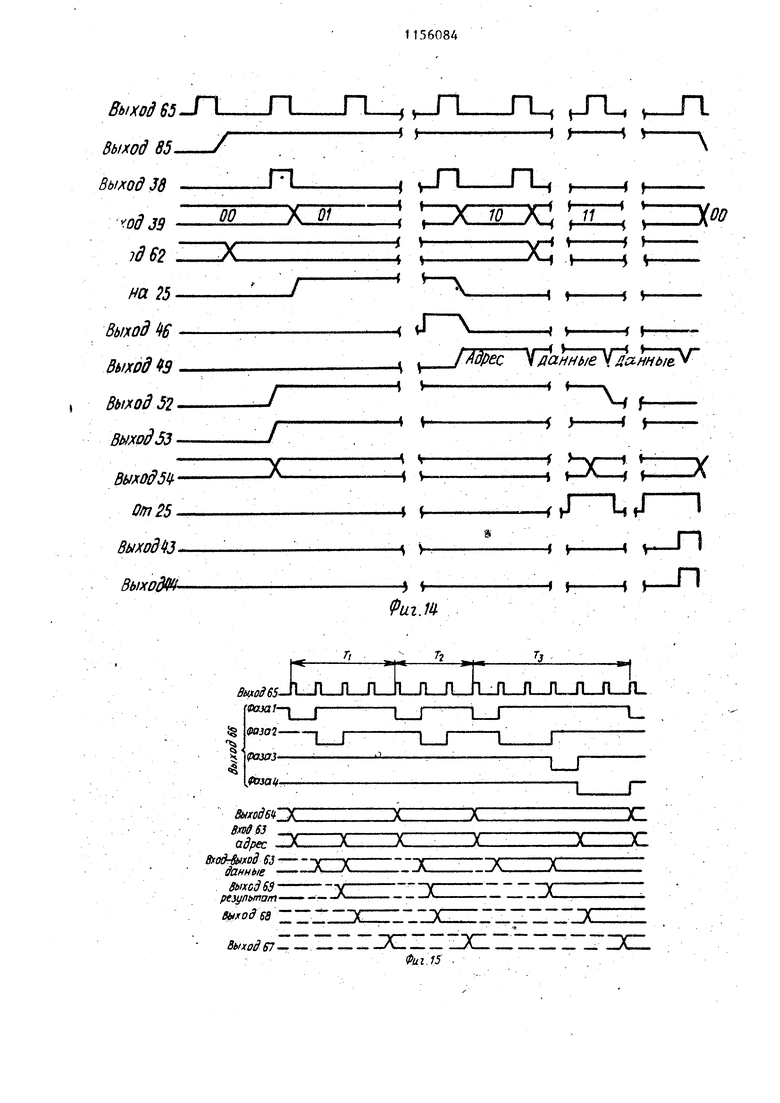

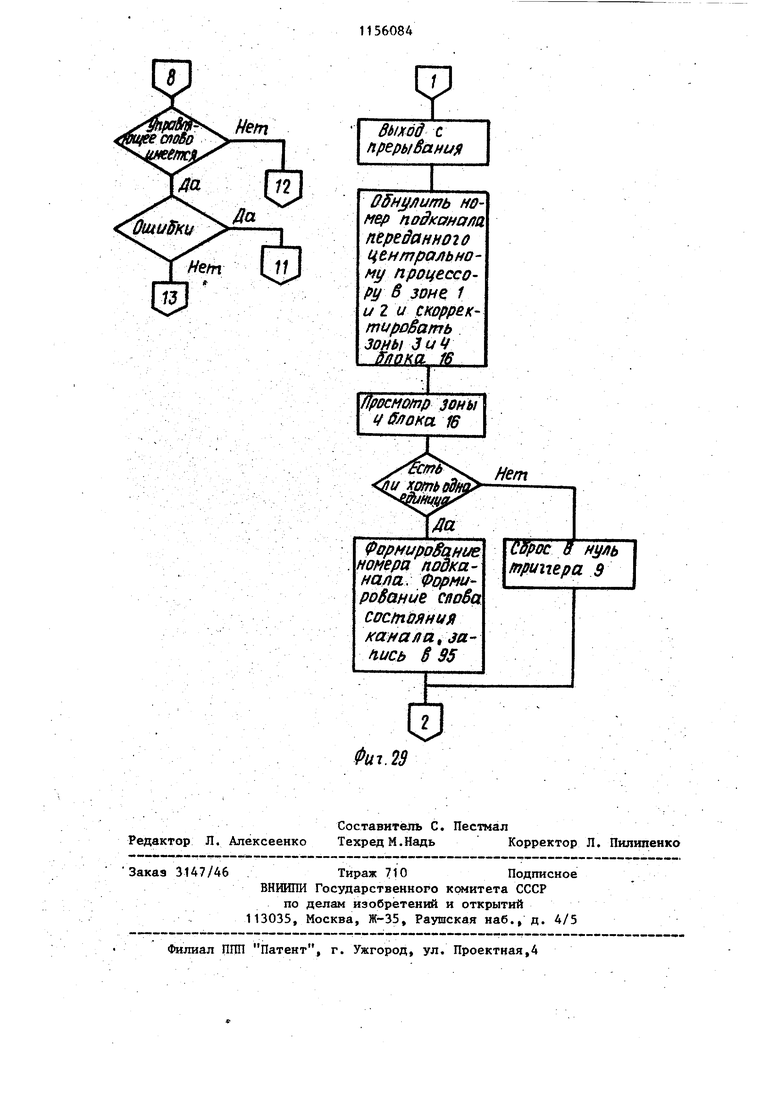

образуют третью группу входов-выходов блока управления, третий выход генератора синхроимпульсов,четвертая группа выходов управляющего регистра и первая группа информационных выходов арифметико- логического устройства образуют- первую группу вькодов блока управления, пятая группа выходов управляющего ргистра образует вторую группу выходов блока управления, шестая группа выходов управляющего регистра образует третью группу выходов блока управления, третья группа выходов управляющего регистра и первая группа выходов узла памяти микропрограмм соединены с адресным входом арифметико-логического устройства и образуют четвертую группу выходов блока управления, седьмая группа выходов управляющего регистра обра зует пятую группу выходов блока управления, первый, второй, третий и четвертый выходы управляющего регистра являются соответственно первым, вторьм, третьим и четвертьы выходами блока управления, вторые группы информационных входов-выходов двухвходовой памяти и арифметико-логического устройства, восьмая группа выходов управляющего регистра и группа управляюнщх входов узла микропрограммного управления образуют четвертую группу входов-выходов блока управления, вход опроса узла микропрограммного управления образует вход блока управления, при этом в блоке управления первый выход генератора синхроимпульсов соединен с входом синхронизатора, группа выходов которого соединена с соответствующими тактирующими входами управляющего регистра, узла памяти микропрограмм, узла микропрограммного управления и арифметико-логического устройства, вторая группа информационных выходов которого соединена с второй группой адресных входов двухвходовой памяти, группа входов режима работы которой соединена с девятой группой выходов управлякмдего регистра, десятая группа выходов которого соединена с входом режима работы арифметикологического устройства, группа управляющих выходов которого соединена с входом признака операции узла микропрограммного управления, группа информационных входов-выхо7дов которого соединена с одноименными входами-выходами узла памяти микропрограмм, вторая группа выходов которого соединена с информационным входом управляющего регистра, одиннадцатая группа выходов которого соединена с входом режима работы синхронизатора. На фиг.1 приведена блок-схема предлагаемого устройстваi на фиг.2 схема блока связи с центральным процессором на фиг.З - схема блока связи с оперативной памятью; на фиг.4 - схема блока управления; на фиг.5 - схема блока фиксации СОСТОЯНИЯ; на фиг.6 - схемасблока управления периферийньм устройством; на фиг.7 - схема шинного коммутатора; на фиг.8 - схема блока приоритетов; на фиг.9 - схема шифра,тора; на фиг. 10 - схеиа коммутирзтощего элемента , на фиг. 11 схема узла микропрограммного управления; на фиг. 12 и 13 - времен ная диаграмма работы блока связи с центральным процессором;- на фиг. 14 - временная диаграмма блока связи с оперативной памятью; на фиг. 15 - временная диаграмма блока управления; на фиг. 16 - вре менная диаграмма блока управления периферийньв и устройствами; на фиг. 17 - временная диаграмма блок-мультиплексного канала; на фиг. 18 - схема трехвходовой памяти; на фиг. 19 - схема демультипле сора; на фиг. 20-29 - алгоритмы раб ты узла микропрограммного управления блока управления и узла микропрограммного управления блоков уп,равления периферийными устройствами. . , Устройство для сопряжения периферийных устройств с процессором и оперативной памятью (фиг.1) содержит блок 1 связи с центральным процессором, блок 2 связи с оперативной; памятью, блок 3 управления блок 4 фиксации состояния, группу блоков управления периферийными устройствами, периферийные устрой ства 6, блок 7 памяти, первый выходной регистр 8, триггер 9 требо вания прерьюаний, постоянньй запоминающий блок 10, дешифратор 11 третью группу элементов И 12 для записи единицы, четвертую группу -элементов И 13 для записи нуля, в 8 рой выходной регистр 14, группу элементов НЕ 15, позиционную память 16, регистр 17 адреса позиционной памяти, шинный коммутатор 18, вторую группу элементов И 19 для передачи инверсного кода, первую группу элементов И 20 для передачи прямого кода, группу элементов ИЛИ 21, блок 22 приоритетов, шифратор 23 кода. На фиг.1 обозначены двусторонняя связь 24, соединяющая центральный процессор с блоком связи с центральным процессором и двусторонняя связь 25, соединяющая оперативную память с блоком связи с оперативной памятью. Блок 1 связи с центральным процессором (фиг.2) содержит элемент И 26, триггер 27 запроса прерывания, элемент И 28, группу элементов И 29 и 30, элемент И 31, регистр 32 триггер 33, элемент И 34, триггер 35. Блок 2 связи с оперативной памятью (фиг.З) содержит элементы И 36 и 37, элемент ИЛИ 38, двоичный счетчик 39, дешифратор 40, элемент ИЛИ 41, элементы И 42 и 43, элемент ИЛИ 44, элементы И 45, 46 и 47, элемент ИЛИ 48, блок коммутирующих элементов 49, элемент И 50, блок элементов И 51, триггер со счетным входом 52, регистр 53 признаков, реверсивный счетчик 54, элемент И 55 и 56, блок элементов И 57, элементы И 58 и 59, блок элементов И 60 и 61, блок элементов ШШ 62. Блок 3 управления (фиг.4) содержит двухВходовзто память 63, управляющий регистр 64, генератор 65 синхроимпульсов, синхронизатор 66, уз.ел 67 памяти микропрограмм, узел 68 микропрограммного управления, арифметико-логическое устройство 69. Блок 4 фиксации состояния (фиг.5) содержит демультиплексоры 70, 71, 72 и 73, ИЛИ 74, регистры 75 и 76, блок 77 приоритетов, блок элементов И 78,элемент ИЙИ 79, блок элементов И 80, блок 81 приоритетов, Элемент И 82, регистр 83, блок элементов И 84, шифратор 85, регистры 86 и 87, мультиплексор 88, шифратор 89, демультиплексоры 90, 91 и 92, мультиплексор 93, блок 94 памяти подканалов. Блок управления периферийным устройством (фиг.6) содерямт трехвходовую память 95, регистр 96 управ ния канала, регистр 97 управления абонента, регистр 98 информации, постоянное запоминающее устройств 99 микропрограмм, узел 100 микропрограммного управления канала, арифметико-логическое устройство канала, синхронизатор 102 канала, управляющий регистр 103 канала. Шинный коммутатор 18 (фиг.7) содержит пять блоков коммутирующи элементов 104-108. Казвдый элемент может коммутирова:ть информацию по 16 двунаправленным шинам. Блок 22 приоритетов (фиг.8) содержит элементы И-НЕ с прямыми и инверсными входами 109-116, элементы ИЛЙ-НЕ 117 и 118, элемен ты И-НЕ с прямьм и инверсными вхо дами 119-125, элементы ЙЛИ-НЕ 126 и 127. Шифратор 23 кода (фиг.9) содер жит четьфе восьмивходовых элемента ИЛИ 128-131. Коммутирующий элемент 49, 104-108 (фиг.10) содержит два эле мента И 132 и 133 и элемент НЕ 13 Узел 68 микропрограммного упра ления (фиг.11) содержит регистр 135 команд, дешифратор 136, элемент И 137, счетчик 138 текущего адреса, узел элементов И 139, регистр 140 следующего адреса, элементы И 141 и 142, первый мультиплексор 143, узел элементов И 144 второй мультиплексор 145, узел эл ментов И 146, третий мультиплексор 147, элемент И 148, регистр 149 состояний, узел элементов И 150, демультиплексор Г51, блок элементов И 152 и 153. Устройство для Сопряжения периферийных устройств с процессором и оперативной памятью (фиг.1) пред назначено для организации обмена информацией между оперативной памя и периферийными устройствами под управлением центрального процессор Блок 1 связи с центральные процессором (фиг.2) предназначен для организации оймена управляющей информацией между центральньм процес сором и блоком 3 управления , порядок которого определяет блок 4 фиксации состояния. Триггер 35 формирует запрос на обслуживание в блок 4, узел элементов И 29 пропускает информацию с центрального процессора на первый вход-выход двухвходовой ламяти 63 блока 3 управления, а узел элементов И 30 адрес. Элемент И 31 вырабатывает сигнал Конец операции, который поступает в центральный процессор и на блок 4 фиксации состояния. Регистр 32 и элемент И 34 служат для выдачи центральному процессору признака результата. Элемент И 26, триггер 27 запроса прерьшания, элемент И 28, триггер 33 служат для установления и обмена управляющей информацией с центральным процессором в режиме прерывания и при передаче слова состояния канала. Блок 16 связи с оперативной памятью (фиг.3) предназначен для обмена данными между оперативной памятью и блоком 3 управления. Приоритет обслуживания обмена задает блок 4. Элементы И 36 и 37, ИЛИ 38, двоичный счетчик 39 на два разряда, дешифратор 40. элементы ИЛИ 41, И 42 и 43,ИЛИ 44, И 45, 46 и 50 составляют схему управления блока 2 связи с оперативной памятью. Триггер со счетньм входом 52, регистр 53 признаков реверсивный счетчик 54 служат длА запоминания управляющей информации. Триггер со счетньм входом запоминает количество восьмибайтных слов (два или одно), которыми производится обмен. Регистр признаков запоминает признаки: передача или прием и порядок обмена - прямой или обратный. Реверсивный счетчик 54 запоминает адрес двухвходовой памяти 63, по которому будет производиться обмен данными с оперативной памятью. Элементы И 55 и 56, блок элементов И 57, элементы И 58 и 59, узел элементов И 60 служат для управления триггером со счетным входом 52, регистром 53 признаков, реверсивного счетчика 54. Блок элементов И 61, блок элементов И 51, блок элементов ИЛИ 62 служат для формирования адреса двухвходовой памяти 63. Блок коммутирующих элементов 49 оммутирует адрес оперативной амяти на двухстороннюю связь 25 о значению 10 дешифратора 40. По начению 11 дешифратора 40 и в ависимости от признака передачи ли приема, поступающего с регистра

53 признаков, блок коммутирующих элементов 49 принимает или передает данные с двухсторонней связи 25. Управление блоком коммутирующих элементов 49 производят элементы И 47 и ИЛИ 48.

Коммутирующий элемент (фиг.10) состоит из двух элементов И 132 и 133 и элемента НЕ J34. Первый Звход элемента И 132 соединен по схеме монтажного ИЛИ с выходом элемента И 133, а первый вход элемента И 133 соединен по схеме монтажного ИЛИ с вьгходом элемента И 132, Чере;з вторые входы элементрвэИ 132 и 133 подается направление коммута ции шины, одно, прямое, - на вход элемента И 132, другое - с элемента НЕ 134 на вход элемента И 133 Третьи входы элементов И 132 и 133 служат для подачи разрешающего потенциала .

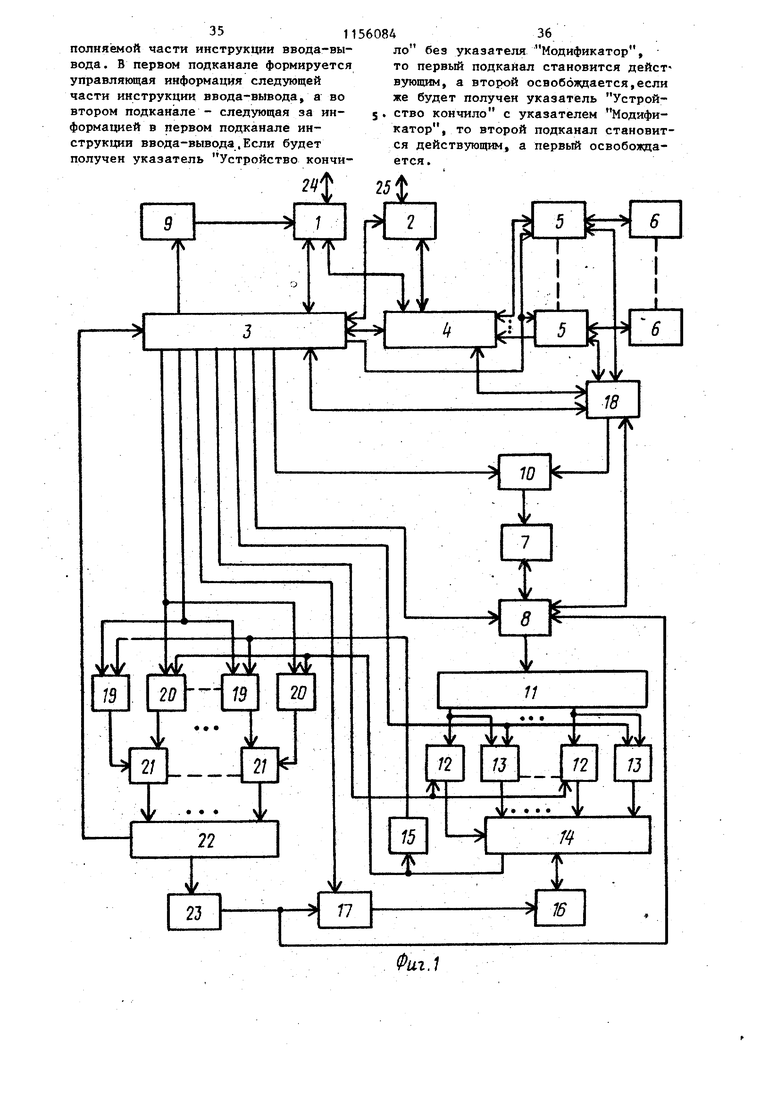

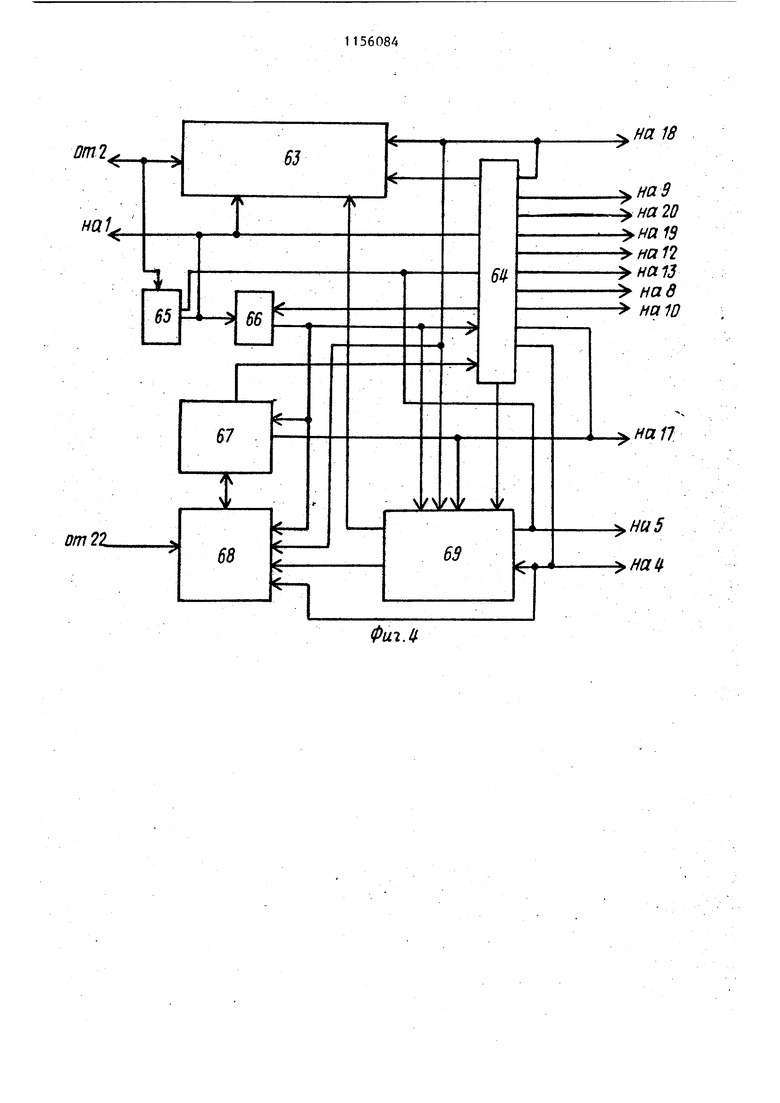

Блок 3 управления (фиг.4) осзпцествляет обработку инструкций вводавывода, поступающих с центрального процессора через блок 1 связи с центральным процессором, формирует команды блокам. 5 управления периферийными устройствами, выполняет команды, поступающие с блоков 5, формирует управляющее слово канала, признак результата, пересьшаемый в центральный процессор, осуществляет управление передачей данных в блок 5 из оперативной памяти через блок 2 связи с оперативной памятью и из блока 5 через блок 2 связи с оперативной памятью вырабатьтает требование на прерывание центрального процессора, формирует и пересылает слово состояния канала через блок 2 связи с оперативной памятью, формирует адреса ячеек оперативной памяти адресного слова канала, слова состояния канала. Осуществляет вьтолнение контрольных и диагностич еских микропрограмм. При обращении к оперативной памяти через блок 2 связи с оперативней памятью происходит прерывание выполняемой микропрограммы блоком 3 управления. Происходит формирование управляющег слова обмена с оперативной памятью. Слово обмена состоит из адреса двухвходовой памяти 63, в которой записаны адрес оперативной памяти, адре двухвходовой памяти 63 для пересылки информации, признаки передачи ил

Приема, количество машинных слов, обмен прямой или обратньй, а также адрес возврата к прерванной микропрограмме.

Устанавливается в единицу определенный разряд регистра 75, который выставляет требование на обслуживание к блоку 2 связи с оперативной памятью. Блок 3 управления приступает к выполнению следующего требования на обслуживание, приоритет которого задается блоком 4.

Двзгхвходовая память 63 служит для хранения упрдвляющей и обменной информации.

На фиг.4 изображена двухвходовая память 63, состоящая из 8 БИС К 1800 РПб, одна половина которой управляется блоке 3 управления, а другая - блоком связи с оперативной памятью или блоком связи с центральным процессором.

В двухвходовой памяти 63 содержится две буферные памяти по 8 байт для хранения данных и две буферные памяти по 8 байт для хранения управляющей информации на каждый канал, а также управляющие слова обмена с оперативной памятью по количесву каналов, одно управляющее слово обмена с оперативной памятью для обработки инструкции ввода-вывода, буферная память для слова состояния канала на 16 байт, а также буферная память для приема инструкции ввода-вывода на 8 байт. Двухвходовая память 63 через двустороннюю, связь подсоединена к блоку коммутирующих элементов 49 блока 2 связи с оперативной памятью и соединена с выходом узла элементов И 29 блока 1 связи с центральным процессором. Адрес для данного входа двухвходовой памяти поступает с узла элментов И 30 блока 1 связи с центральным процессором и с узла схем ИЛИ 62 блока 2 связи с оперативной памятью. Другой вход-выход двухвходовой памяти 63 связан с шинным коммутатором 18 и арифметико-логическим устройством 69. Адрес для данного входа задает арифметикологическое устройство 69. Двухвходовая память играет роль регистрового файла для блока 3 управления.

Управляющий регистр 64 задает режимы работы второму входу-выходу двухвходовой памяти 63, синхрони13

затору 66, арифметико- логическому устройству 69, шинному коммутатору 18, четвертой группе элементов И 1 для записи нуля, третьей группе элементов И 12 для записи единицы, первой группе элементов И 20 для передачи прямого кода, второй группе элементов И 19 для передачи инверсного кода, регистру 17 адреса позиционной памяти первому выходному регистру 8, блоку 4, постоянному запоминающему блоку 10, блоку 1 связи,с центральным процессором, группе блоков 5 управления периферийными устройствами, а также триггеру 9 требования прерьюания.

Управляющий регистр 64 слуямт для хранения кодов микрокоманды на время ее выполнения. Назначение разрядов микрокоманды: 0-3 - код микрокоманды; 4-12 - адрес следующей микрокоманды; 13-20 - поле постоянных признаков; 21-27 - поле управления узлом 68 микропрограммного управления; 28-32 - поле управления двухвходоврй памятью 63; 33-36 - поле управления синхронизатором 66; 37-54 - поле управления арифметико-логическим устройством 69; 55-60 - поле управления шинным коммутатором 18; 61-62 - поле управления триггером 9; 6365 - поле управления элементами И 1 13, 19 и 20; 66-69 - поле управления первьм выходные регистром 8; 70-73 - поле управления блоком 4; 74-76 - поле управления блоком 1 связи с центральным процессором; 77-78 - поле управления постоянным запоминающим блоком 10-, 79-83 - поле управления блоками 5; 84 - поле управления узлом 67 памяти микропрограмм; 85-87 - поле управления регистром 17 адреса позиционной памяти.

В управляющем регистре 64 хранятся разряды микрокоманды с 28 по 87,

Генератор 65 синхроимпульсов задает тактовую частоту. Синхронную работу блока 3 управления обеспечивает синхронизатор 66, «который выполнен на одной микросхеме К 1800ВБ2 - схеме синхронизации. В узле 67 памяти микропрограмм содержится управляющая информация блока 3 управления. Память микропрограмм соединена двусторонней связью с узлом 68 микропрограммного

56084

управления. Слово, поступающее с

узла 67 памяти микропрограмм, разделено на поля: поле команд, поле следующего адреса, поле состояний. 5 Поле команд и следующего адреса поступает на узел 68 микропрограммного управления. Поле состояний поступает на управляющий регистр 64 и узел 68 микропрограммного управления, которьА и вырабатывает

адрес следующего слова памяти микропрограмм.

Арифметико-логическое устройство 69 служит для переработки и хра15 нениЯ управляющей и адресной информации и вьтолнено на 6 БИС К 1800 ВТЗ - схеме управления оператив; ной памятью. Арифметико-логическое устройство 69 хранит и задает

20 адреса для второго входа-выхода

двухвходовой памяти 63, для второго и третьего входа-выхода трехвходовой памяти 95 каналов, принимает и выдает информацию в блок 4, связано

25 с двунаправленной шиной информации второго входа-выхода двухвходовой памяти 63, может принимать всевозможные признаки с узла 67 памяти микропрограмм.

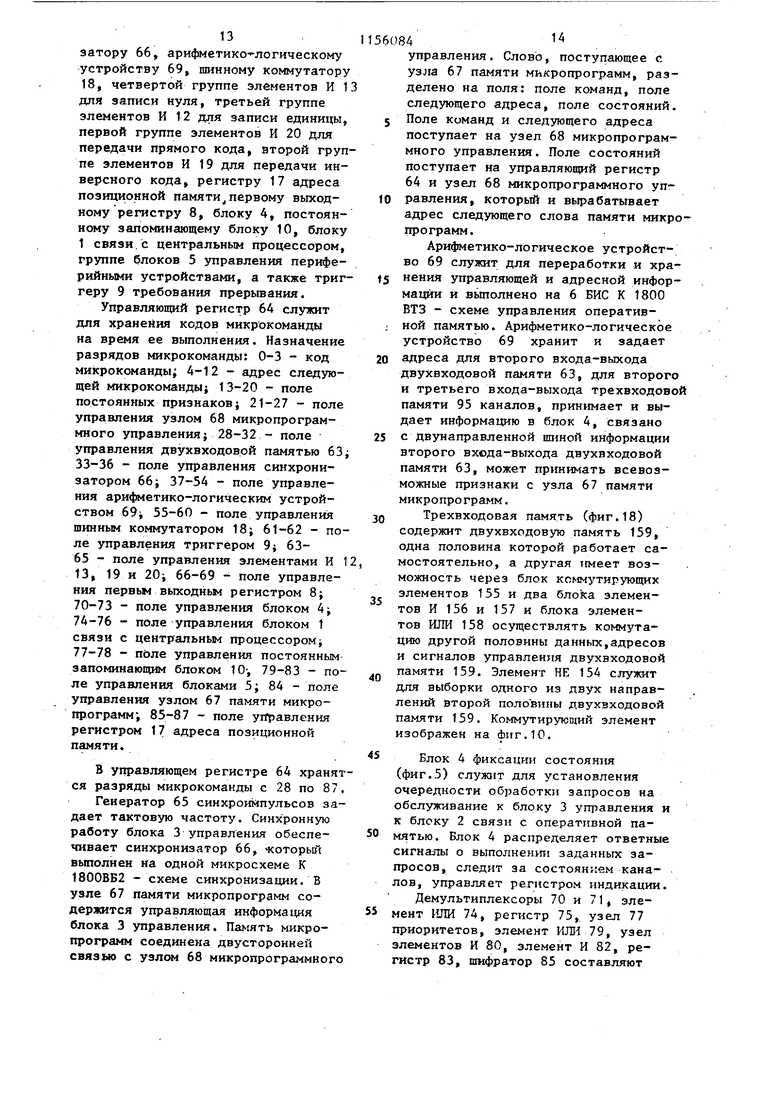

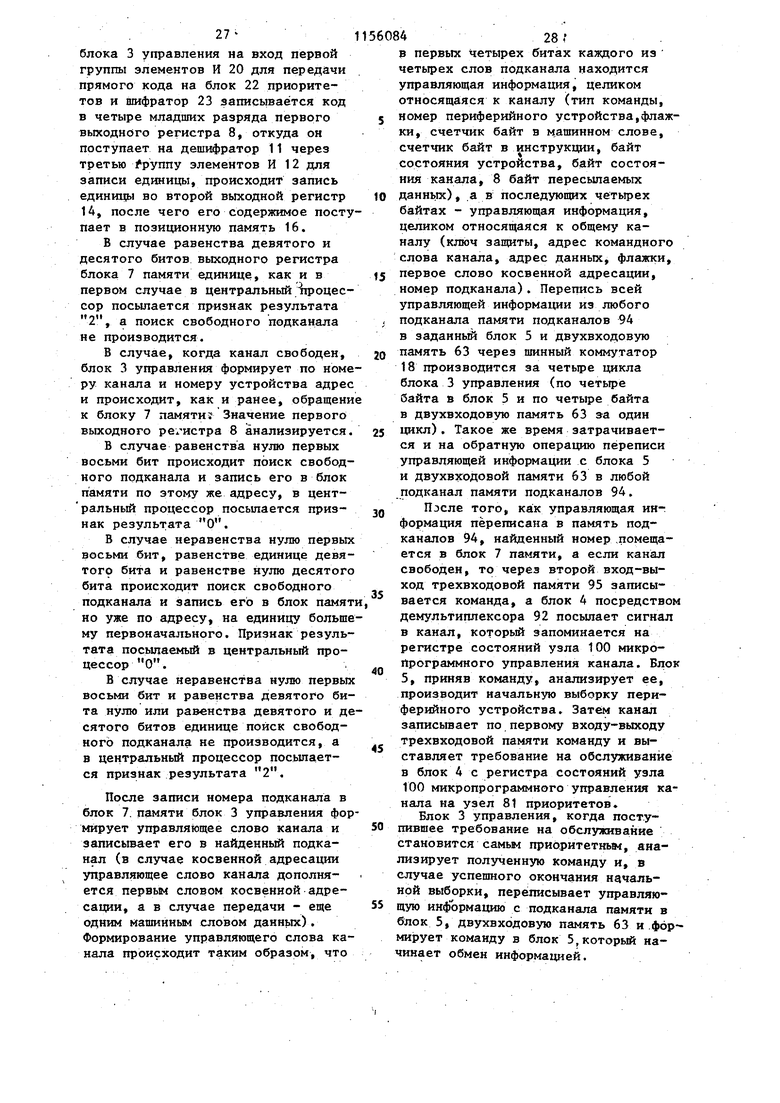

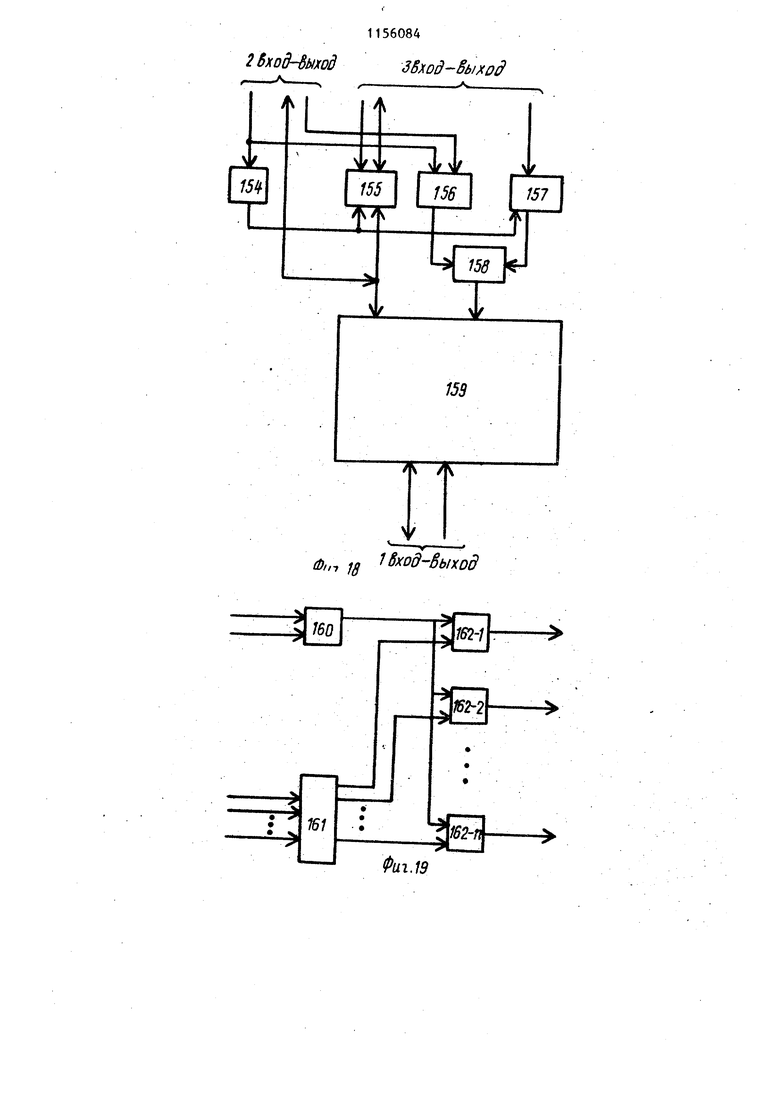

Трехвходовая память (фиг.18) содержит двухвходовую память 159, одна половина которой работает самостоятельно, а другая тгмеет возможность через блок коь{мутирующих элементов 155 и два блoka элементов И 156 и 157 и блока элементов ИЛИ 158 осуществлять коммутацию другой половины данных,адресов и сигналов управления двухвходовой памяти 159. Элемент НЕ 154 служит для выборки одного из двух направлений второй половины двухвходовой памяти 159. Коммутирующий элемент изображен на фиг.10.

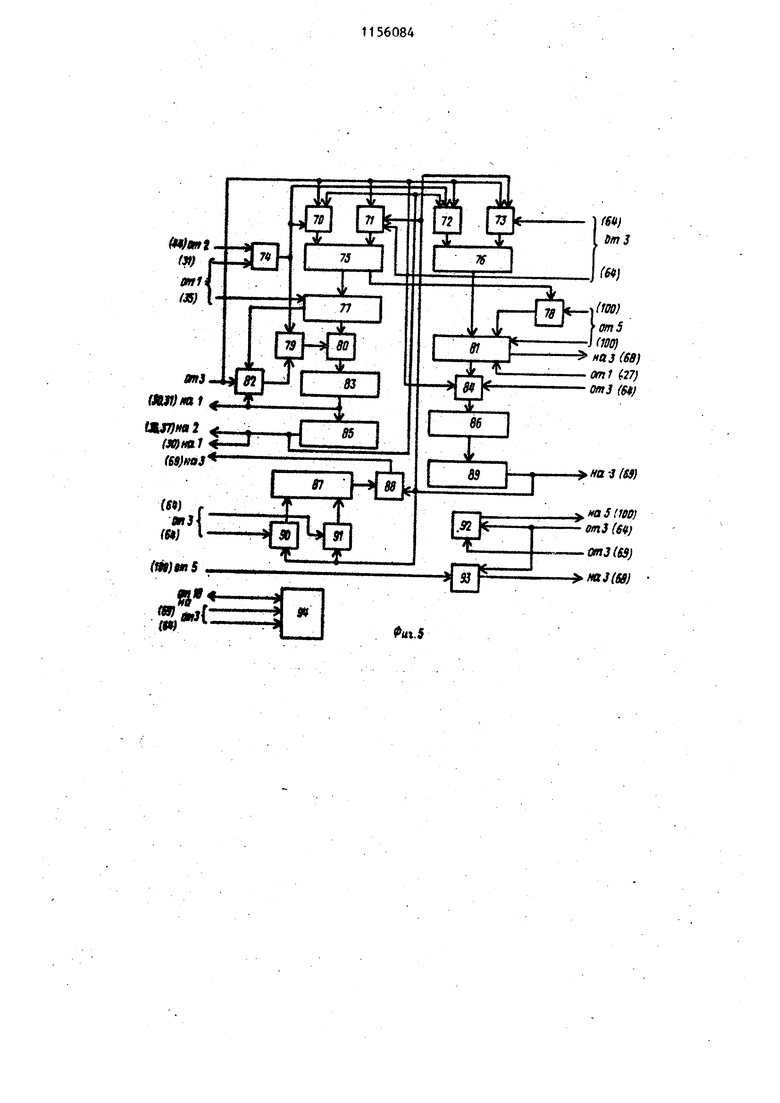

5 Блок 4 фиксации состояния

(фиг.5) служ1ст для установления очередности обработки запросов на обслуживание к блоку 3 управления и к блоку 2 связи с оперативной памятью. Блок 4 распределяет ответные сигналы о выполнении заданных запросов, следит за состоянием каналов, управляет регистром индикации. Демультиплексоры 70 и 71, элемент ИЛИ 74, регистр 75, узел 77 приоритетов, элемент Mnti 79, узел элементов И 80, элемент И 82, регистр 83, шифратор 85 составляют

схему установления порядка обслуживания к блоку 2 связи с оперативной памятью. Демультиплексоры 72 и 73, регистр 76, узел элементов И 78, узел 81 приоритетов, узел элементов И ЗА, регистр 96, шифратор 89 составляют схему установления порядка обслуживания к блоку 3 управления. Мультиплексор 88 и Демультиплексоры 90 и 91 служат для индикации и изменения значения регистра 87. Демультиплексор 92 служит для вьщачи ответных сигналов в блоки 5, а мультиплексор 93 шщици рует состояние блоков 5. Узел 94 памяти подканалов рй делен на 256 динамически распределяемых подканалов по 32 байта каждый, ширина слова 8 байт.

Демультиплексор 70 служит для установки в нулевое состояние разряда регистра 75, Демультиплексор 72 - для установки в единичное состояние разряда регистра 76. Над какими разрядами регистра 75 и 76 необходимо произвести действия определяет пшфратор 85. Демультиплексор 71 служит Для установки в единичное состояние регистра 75, а Демультиплексор 73 - для установки в нулевое состояние регистра 76. Над какими разрядами регистров 75 и 76 необходимо произвести действия определяет шифратор 89, а управляет работой демультиплексоров блок 3 управления.

Демультиппексоры 90 и 91 служат для записи нуля и единицы в регистр 87 под управлением блока 3. Разряды установки или сброса определяет шифратор 89.

Демультиплексор 92посьшает в узел 100 микропрограммного управления канала сигнал, по которому узел 100 микропрограммного управления канала сбрасывает требование на обслуживание, посылаемое им в блок фиксации без останова выполнения основной микропрограммы канала.

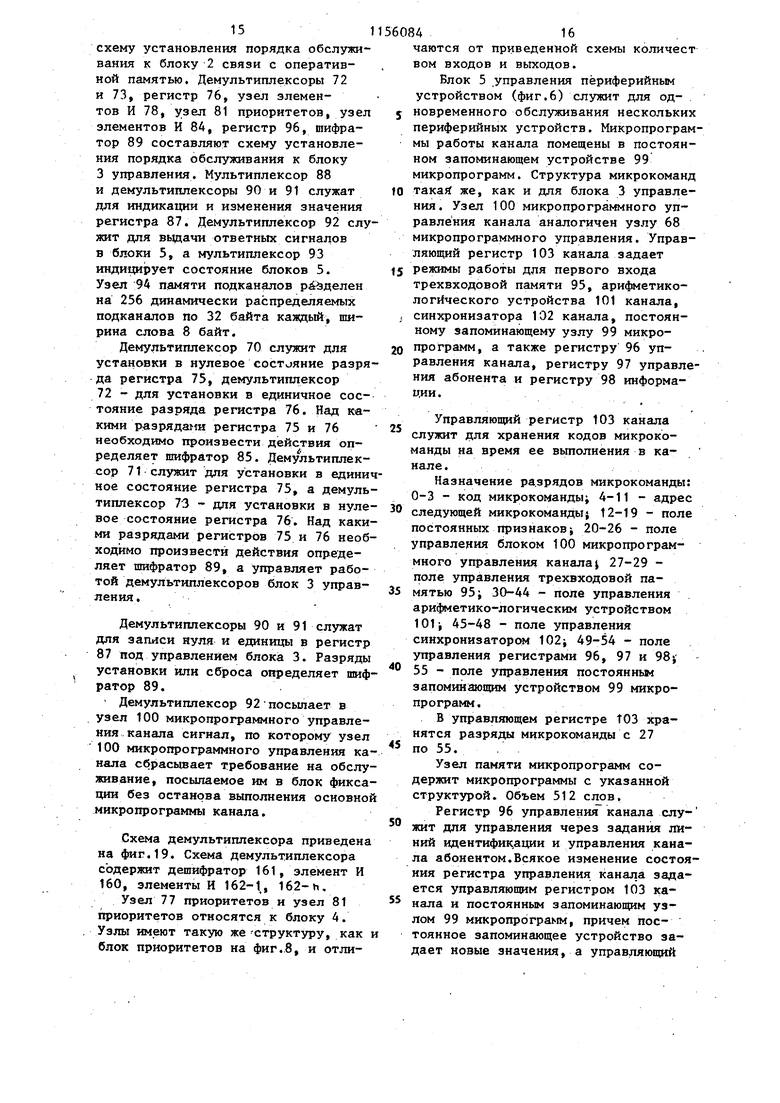

Схема демультиплексора приведена на фиг.19. Схема демультиплексора содержит дешифратор 161, элемент И 160, элементы И 162-1, 162-и.

Узел 77 приоритетов и узел 81 приоритетов относятся к блоку 4. Узлы имеют такую же структуру, как и блок приоритетов на фиг.8, и отличаются от приведенной схемы количест вом входов и выходов.

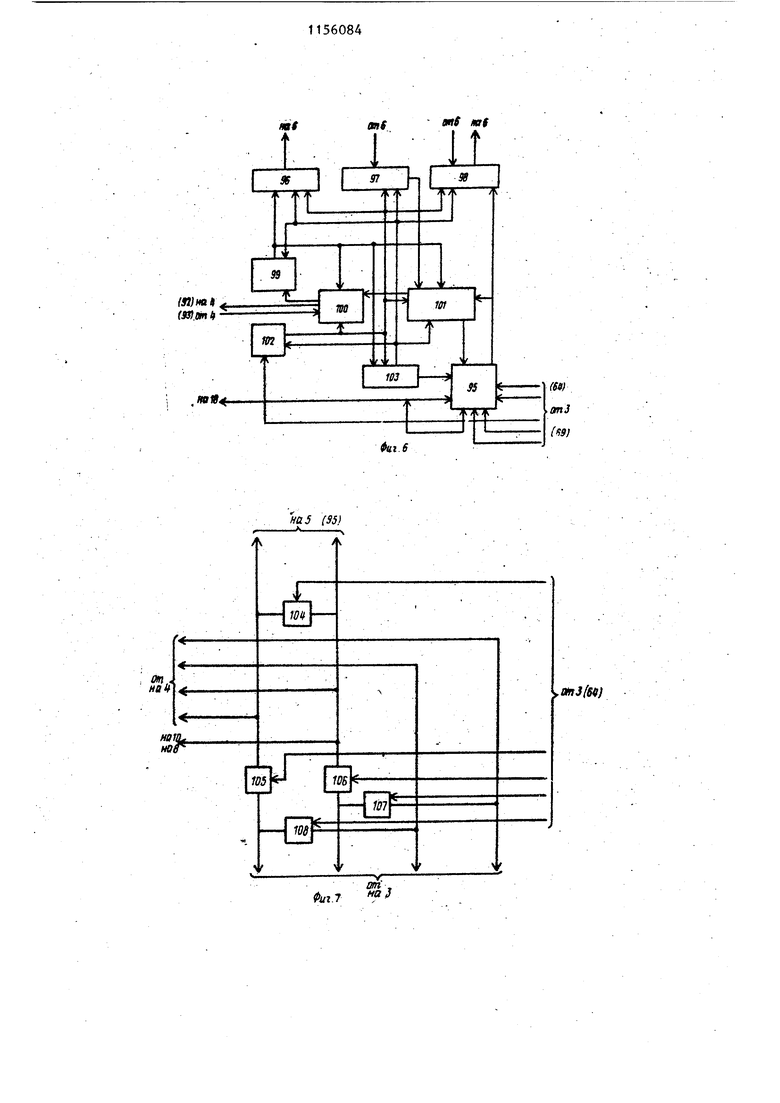

Блок 5 управления периферийным устройством (фиг.6) служит для одновременного обслуживания нескольких периферийных устройств. Микропрограммы работы канала помещены в постоянном запоминающем устройстве 99 микропрограмм. Структура микрокоманд

такай же, как и для блока 3 управления. Узел 100 микропрограммного управления канала аналогичен узлу 68 микропрограммного управления. Управляющий регистр 103 канала задает

режимы работы для первого входа

трехвходовой памяти 95, арифметикологического устройства 101 канала, синхронизатора 102 канала, постоянному запоминающему узлу 99 микропрограмм, а также регистру 96 управления канала, регистру 97 управления абонента и регистру 98 информации.

Управляющий регистр 103 канала служит для хранения кодов микрокоманды на время ее выполнения в канале .

Назначение ра.зрядов микрокоманды: 0-3 - код микрокоманды; 4-11 - адрес

следующей микрокоманды; 12-19 - поле постоянных признаков 20-26 - поле управления блоком 100 микропрограммного управления каналаj 27-29 поле управления трехвходовой памятью 95; 30-44 - поле управления арифметико-логическим устройством lOlj 45-48 - поле управления синхронизатором 102; 49-54 - поле управления регистрами 96, 97 и 98-,

55 - поле управления постоянньи запоминающим устройством 99 микропрограмм.

В управляющем регистре t03 хранятся разряды микрокоманды с 27

по 55.

Узел памяти микропрограмм содержит микропрограммы с указанной структурой. Объем 512 слов.

Регистр 96 управления канала служит для управления через задания линий идентификации и управления канала абонентом.Всякое изменение состояния регистра управления канала задается управляющим регистром 103 канала и постоянным запоминающим узлом 99 микропрограмм, причем постоянное запоминающее устройство задает новые значения, а управляющий

17 ,n

регистр 103 канала определяет разряд, куда необходимо занести новое значение. Значения разрядов регистра 96: АДР-К, УПР-К,, ИНФ-К, РАБ-К, ВБР-К, БЛК-К, ДАН-К.

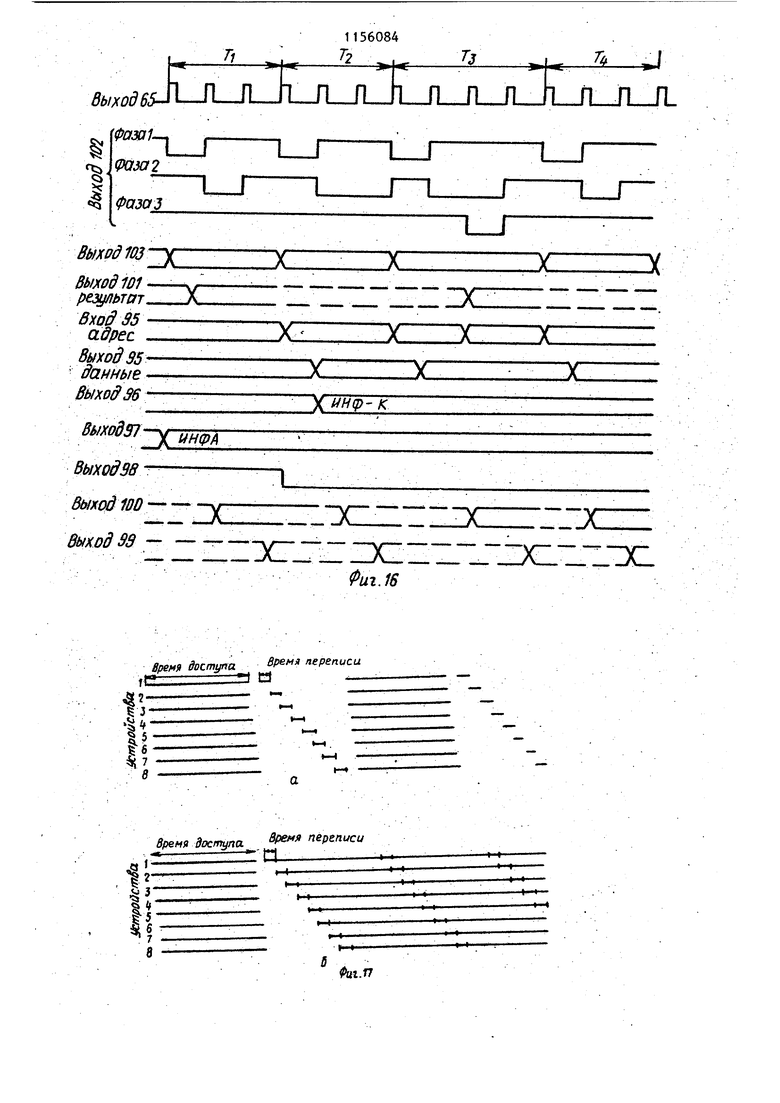

Синхронизатор 102 канала обеспечивает синхронную работу канала и выполнен на одном БИС К 1800 ВБ2. Арифметико-логическое устройство 101 канала служит для переработки и хранения управляющей и адресной информации, выполнено на 2 БИС К 1800 ВТЗ. Арифметико-логическое устройство 101 канала связано с первым входом-выходом трехвходовой памяти 95 и регистром 98 информации двусторонними связями. Арифметико-логическое устройство 101 канала задает адрес для первого входа-выхода трехвходовой памяти 95, может прйнимать постоянные признаки с постоянного запоминающего узла 99 микропрограмм, приншчать для анализа содержимое регистра 97 управления абонента и вьщавать результат для анализа в узел 100 микропрограммного управления канала. Трехвходовая память 95 служит для хранения управляющей и передаваемой информации . Второй и третий входы-выходы трехвходовой памяти 95 управляются от блока 3 управления, а обмен информации для второго и третьего входа-выхода происходит через шинный коммутатор 18.

Регистры управления канала 96, управления абонента 97, информации 98 связаны с унифицированньм интерфейсом ввода-вьгаода Единой систеьш электронных вычислительных машин. Йнфо{ мация на регистр 96 ytipHBneHiffl канала подается с постоянного запоминающего узла 99 микропрограмм..

Блок 5 в зависимости от управляющей инфо1Я4ации, помещенной в постоянный запоминающий узел микропрограмм, может быть двух типов: байт-мупьтиплексньй и блок-мультиппексиыЙ, На блок 4 и блок 3 управления тип каналу определяется по месту подключения канала к узлу 81 приоритетов блока 4.

Постоянный запоминающий блок 10 служит для преобразования адреса блока 7 памяти. Это преобразование служит для уменьшения объема блока 7 памяти, который содержит по од608418

ной ячейке для каждого периферийного устройства. Поскольку необходимо запоминать для устройств, закрепленных за несколькими программами, два косвенных адреса подканалов , то,объем блока памяти должен был бы возрасти. Преобразование адресов производится в зависимости от количества устройств, закрепленfО ных за несколькими программами с тем, чтобы вьщелить для них две соседних ячейки блока памяти незави симо от того, сколько периферийных устройств подключено к одному устройству управления.

Блок 7 памяти служит для образования таблиц, входом в которые ; является адрес, состоящий из номера канала и номера периферийного устройства, а содержимым - косвенный адрес, в котором хранится управляющая информация подканала.Объем блока 7 памяти зависит от количества каналов и от количества периферйй5 ных устройств, которые могут быть подключены к каждому каналу. Объем ячейки памяти блока 7 памяти десять бит.

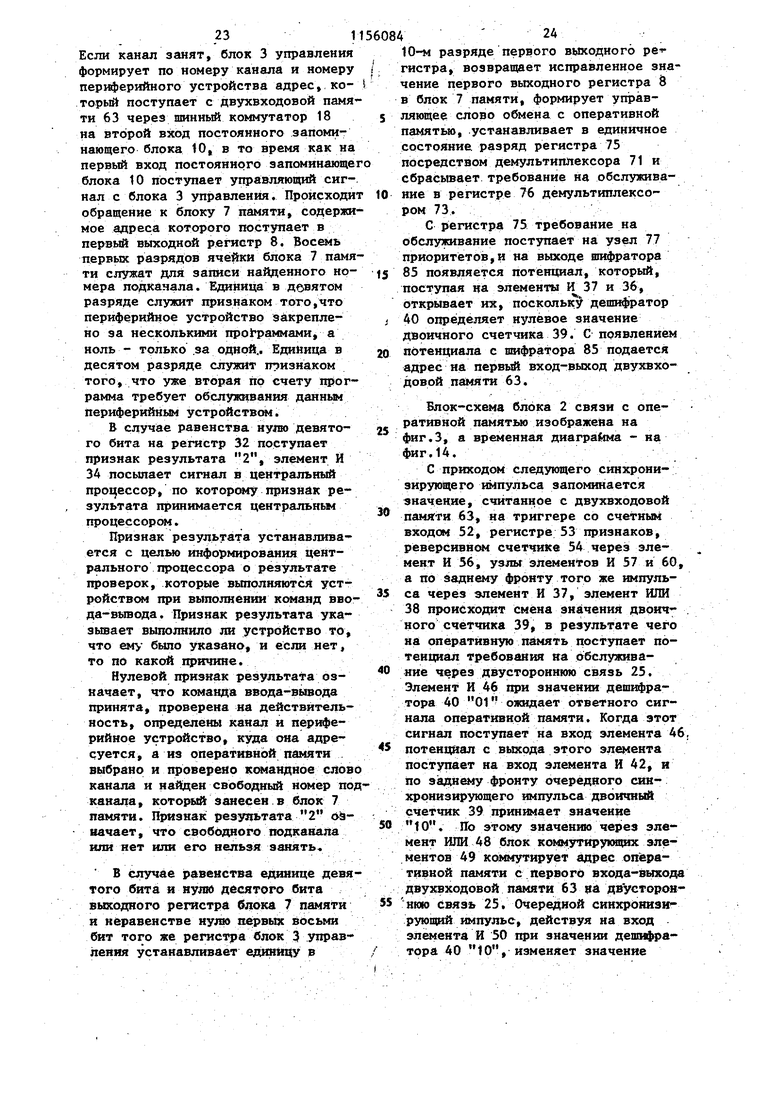

Постоянное запоминающее устрой ство 10 управляется пятой группой выходов блока 3 управления. При наличии на пятой группе выходов единичного потенциала постоянный запоминающий блок 10 преобразует 5 адрес, поступающий на его вход таким образом, что для любого группового устройства управления, объединяющего группу периферийных устройств, закрепленных одновременно за разньми программами в системе, которая работает в мультипрограммном режиме, всегда формируется адрес, не зависимый от номера периферийного устройства. Позиционная память 16 служит для хранения информации о состоянии всех 25Ь динамически распределяемых подканалов. Позиционная память разделена на 4 зоны. В первой зоне, объем которой составляет 256 бит, единицей отмечены позищюнные номера подканалов, ко1орые в настоящее время заняты не отрабо. тайной управляющей информацией, относящейся к периферийному устройству. За одно обращение к позиционной памяти вынимается 16 бит инфорMai9iH. Для нахождения не занятого неотработанной информацией подканала все 16 бит Пропускаются через блок 22 приоритетов и определяется первое нулевое значение разряда,- по позиции которого формируется шифратором младшая часть (А разряда) номера подканала, а старшая часть (4 разряда) номера подканала образуется из номера строки. На место найденной позиции строки записьшает единица. В случае, если все 16 бит первой строки первой зоны позиционной памяти 16 заняты одними единицами, та выбирается вторая строка и т.д. Для убыстрения процесс нахождения номера подканала введена третья зона, в которой отмечены еди ницей занятые строки, с тем, чтобы уменьшить количество выбираемых строк при происке. Объем ее 16 бит Во второй зоне, такого же объем как и первая, отмечены единичным состоянием те разряды, нсжера подканалов которых хранят не переданг ное в центральный процессор слово состояния канала. Четвертая зона служит, как и третья, для быстрого отыскания подканалов, занятых слов состояния канала. Объем позиционной памяти 68 байт. Шинный коммутатор 18 (фиг.7) за дает направление передачи информации между вторым входом-выходом двухвходовой памяти 63 блока 3 управления вторыми и третьими входами-выходами трехвходовой памяти 95 канала и блоком 94 памяти подканалов. При передаче данных в блок 5 с блока 3 управления открыты для передачи блоки коммутирзющих элементов 105, 104, 106, 108, 107. Пр приеме с блока 5 в блок 3 управления открыты для приема те же блоки ко1 {утирующих элементов. В случае считьгаания или записи управляющей информащга из блока 94 памяти подканалов одновременно по четыре байта в блок 5 и по четыре байта в %лок 3 управления открыты блоки коммутирующих элементов 107 и 108. При переписи всей информации из блока 94 памяти подканалов в блок управления открываются блоки комму тируюв их элементов 105 и 106, Отдельный коммутирующий элемент изоб ражен на фиг. 10, БЛОК 22 приоритетов (фиг.8) слу жит для определения первого нуля в разрядах второго выходного региСТ ра 14, начиная с младших разрядов. Режим работы задает блок 3 управления, передавая значение второго выходного регистра 14 через первую группу элементов И 20 для передачи прямого кода или через группу элементов НЕ 15 и через вторую группу элементов И 19 для передачи инверсного кода на группу элементов ИЛИ 21, а затем на вход блока 22 приоритетов. Первый выход блока 22 приоритетов, поступающий на первый вход блока 3 управления, определяет, имеется ли хотя бы один ноль (или единица) в разрядах второго выходного регистра 14. Шифратор 23 кода (фиг.9) преобразует позиционный код, вьщеляющийся на выходе блока 22 приоритетов в двоичный код. Узел 68 микропрограммного управления (фиг, 11) СЛ5ГЖИТ для образования след5тещего адреса,по которому из памяти микропрограмм считывается управляющее слово. Через узлы эле- . ментов И 153 и 139 информация с выхода узла 67 памяти микропрограмм поступает в регистр 135 команд и регистр 140 следующего адреса. Команда депйфрируется дешифратором 136, Уз ел микропрограммного управления может выполнять четьфе команды; многовходовое ветвление, переход к следующему адресу, приращение, переход к внешней шине. Элементы И 137, 141 и 142, узел элементов И 144 служат для записи в счетчик 138 текущего адреса следующего адреса при выполнении команды Многовходовое ветвление, Само изменение разрядов с регистра следующего адреса определяют мультиплексоры 143, 145 и 147, на которые подаются управляюпще сигналы с памяти микропрограмм, выбирающие инте-ресующие условия, по которым происходит ветвление, Уз ел элементов И 146 служит для записи в счетчик 138 текущего адреса, адреса, находящегося в регистре 140 следующего адреса. Элемент И 148 служит для изменения адреса в счетчике 138 текущего адреса на единицу. Узлы элементов И 150 и 152 служат для занесения нового адреса и значений состояний с внешней шины в счетчик 138 текущего адреса и в регистр 149 состояний. Де. 2t

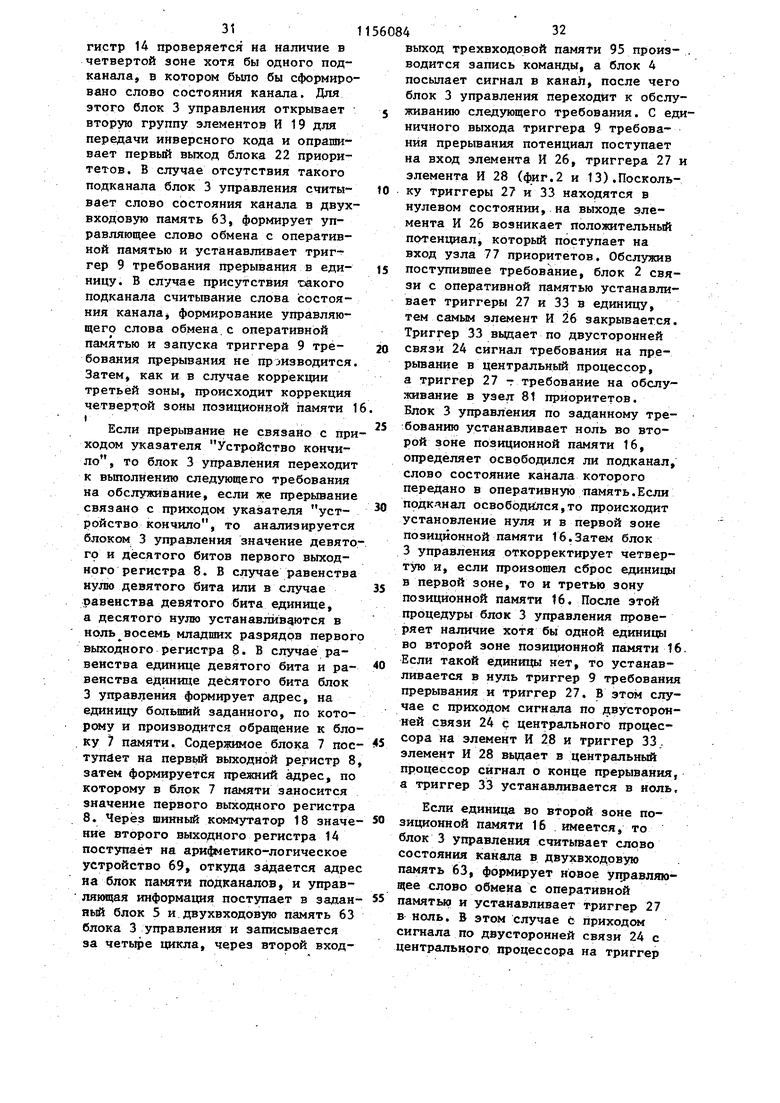

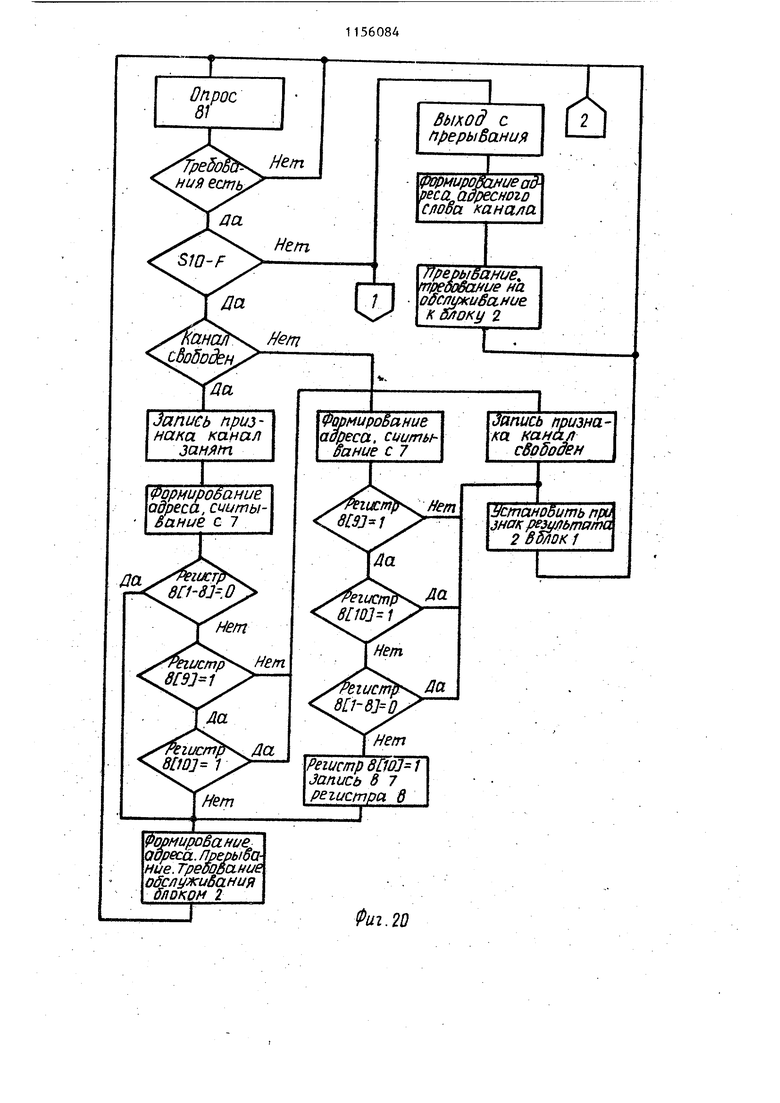

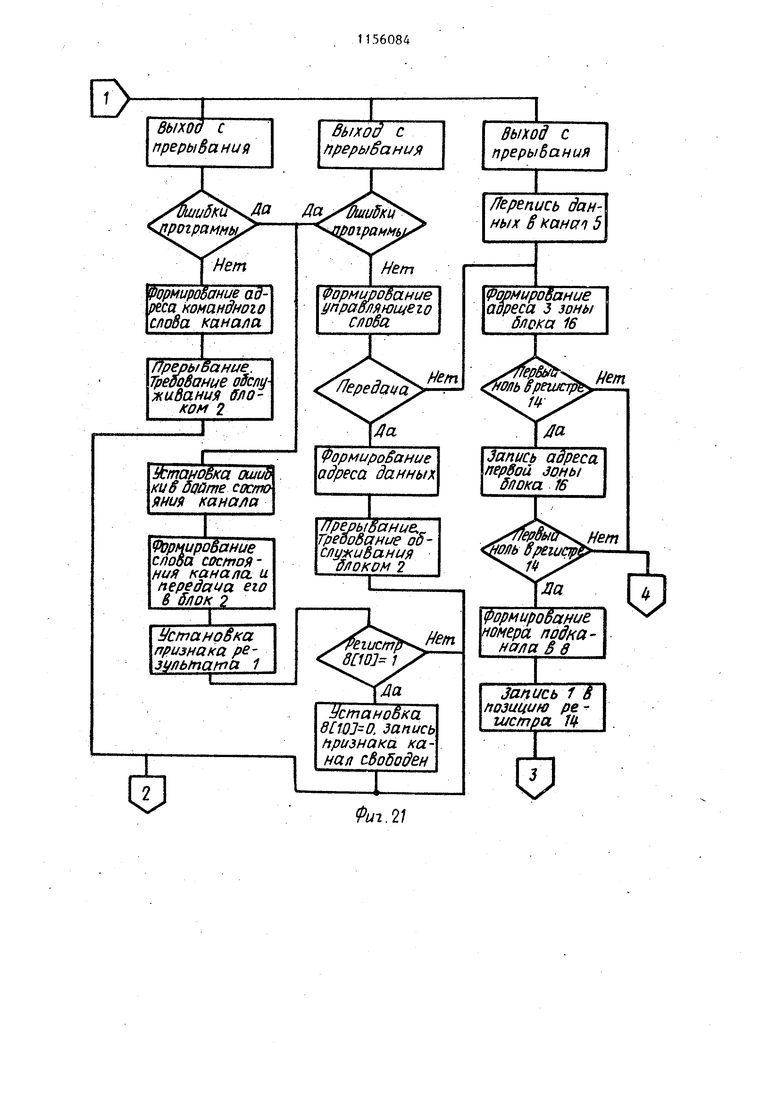

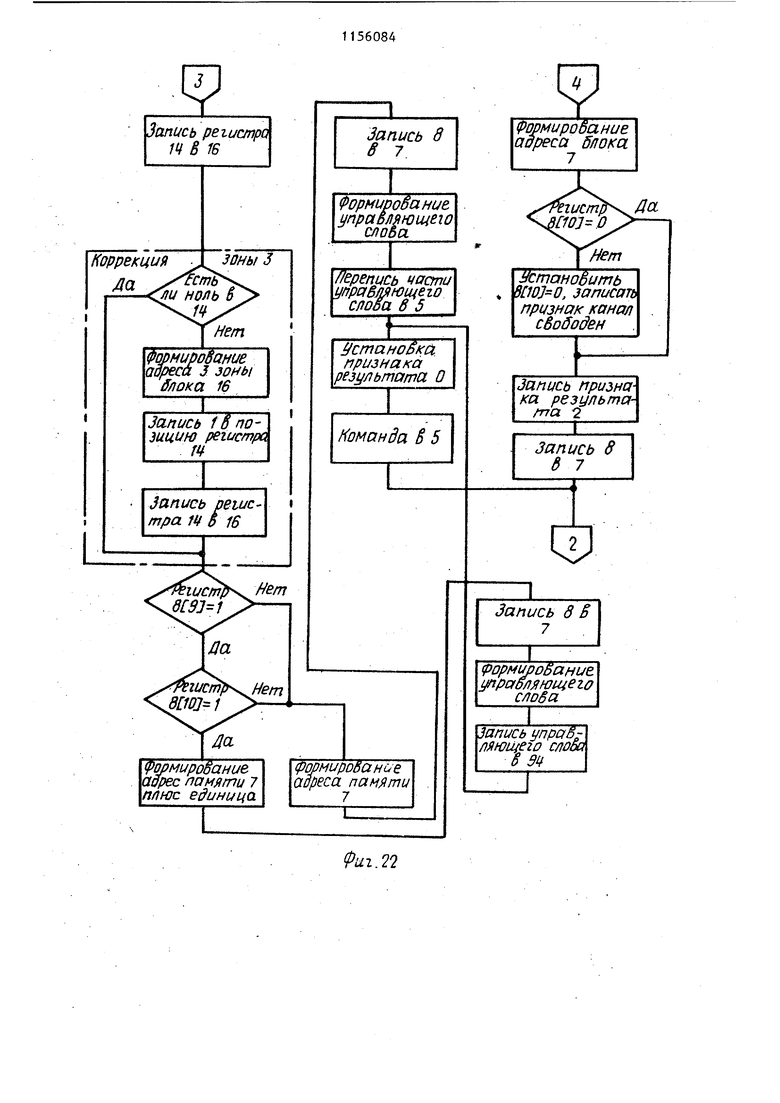

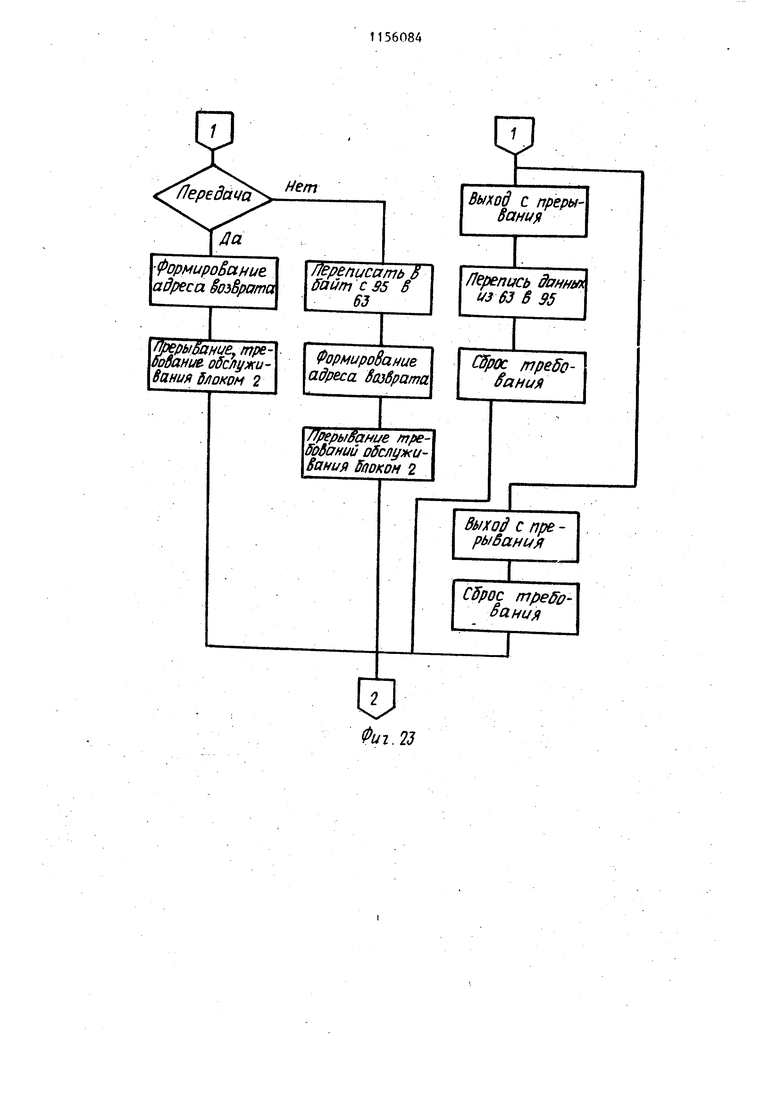

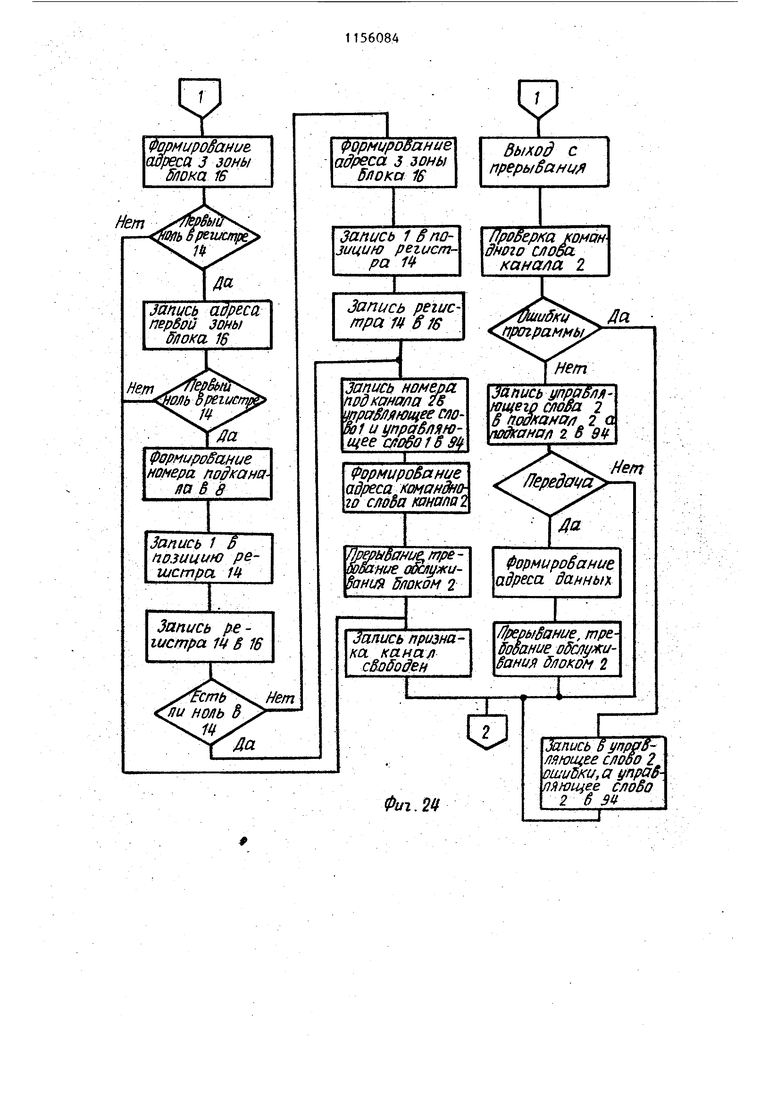

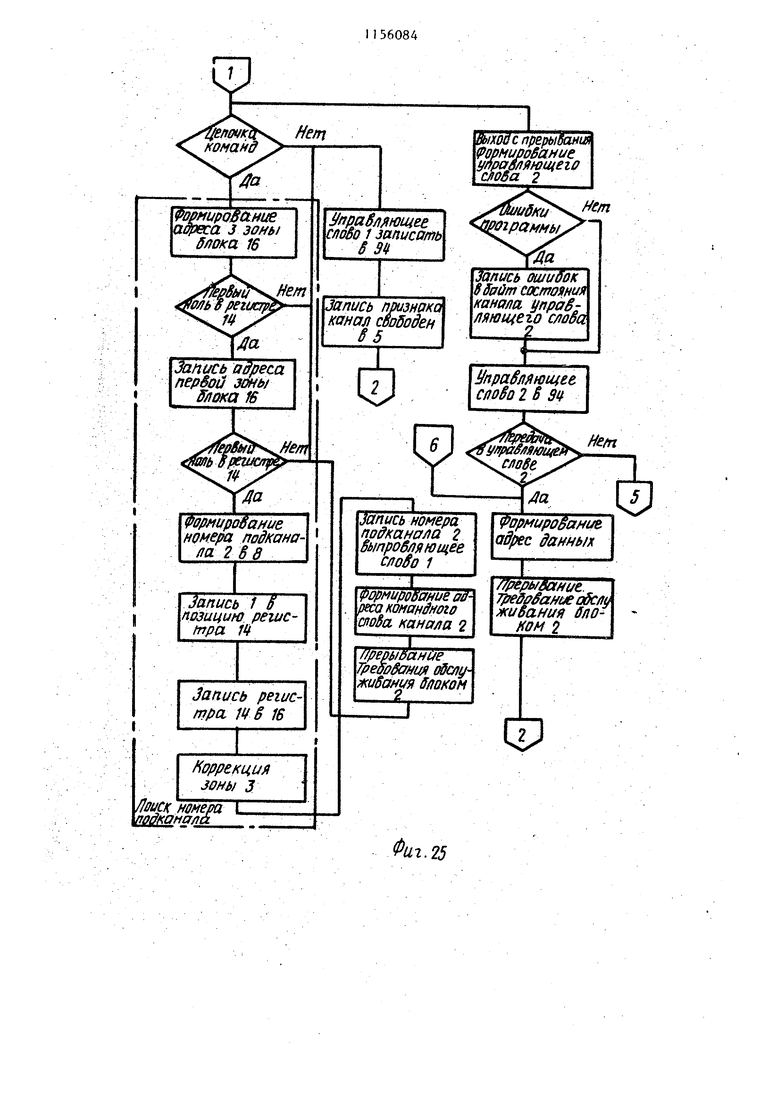

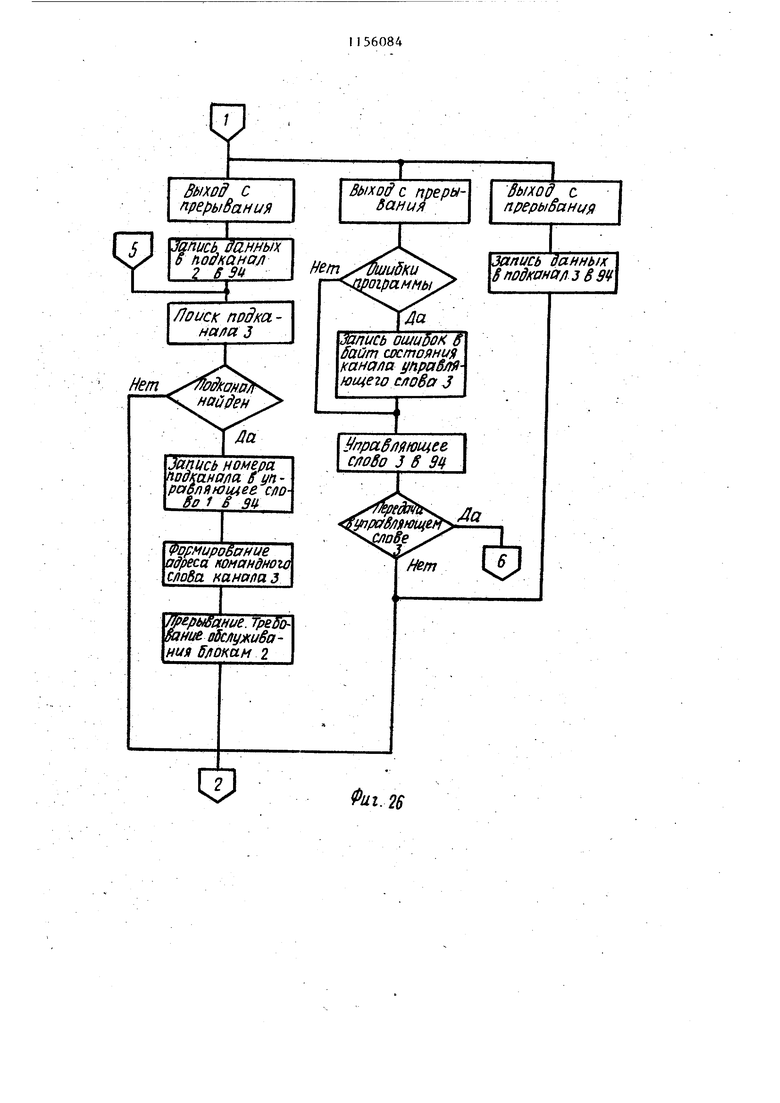

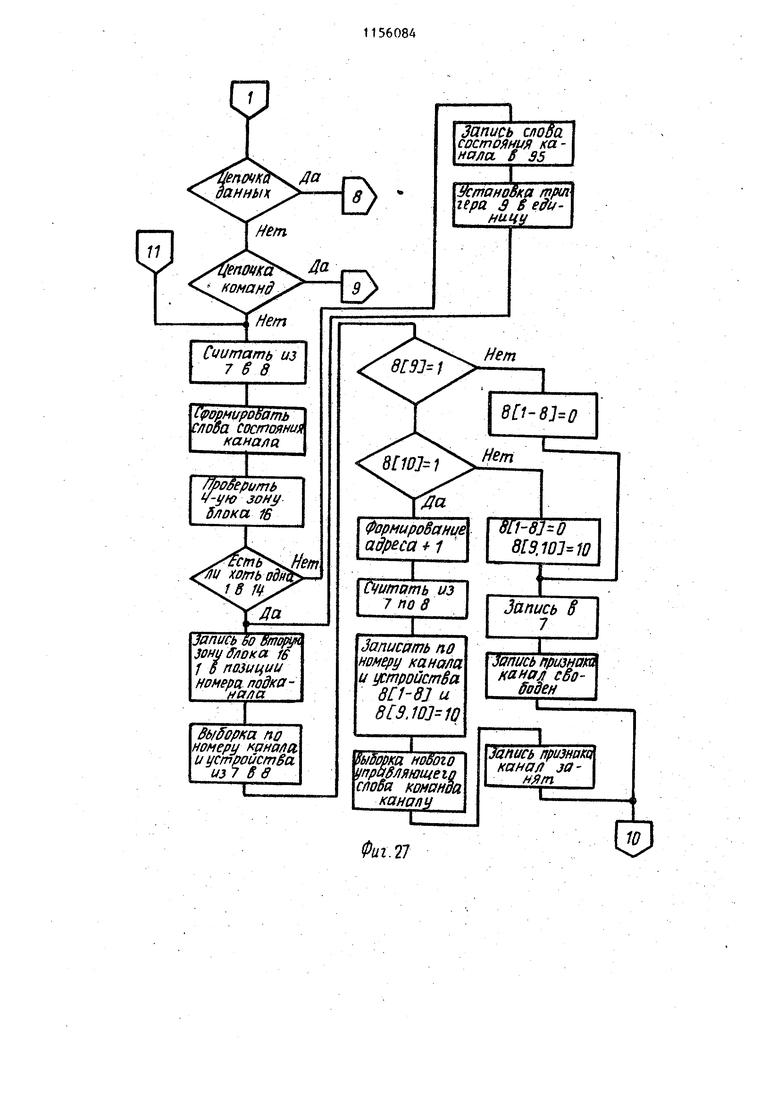

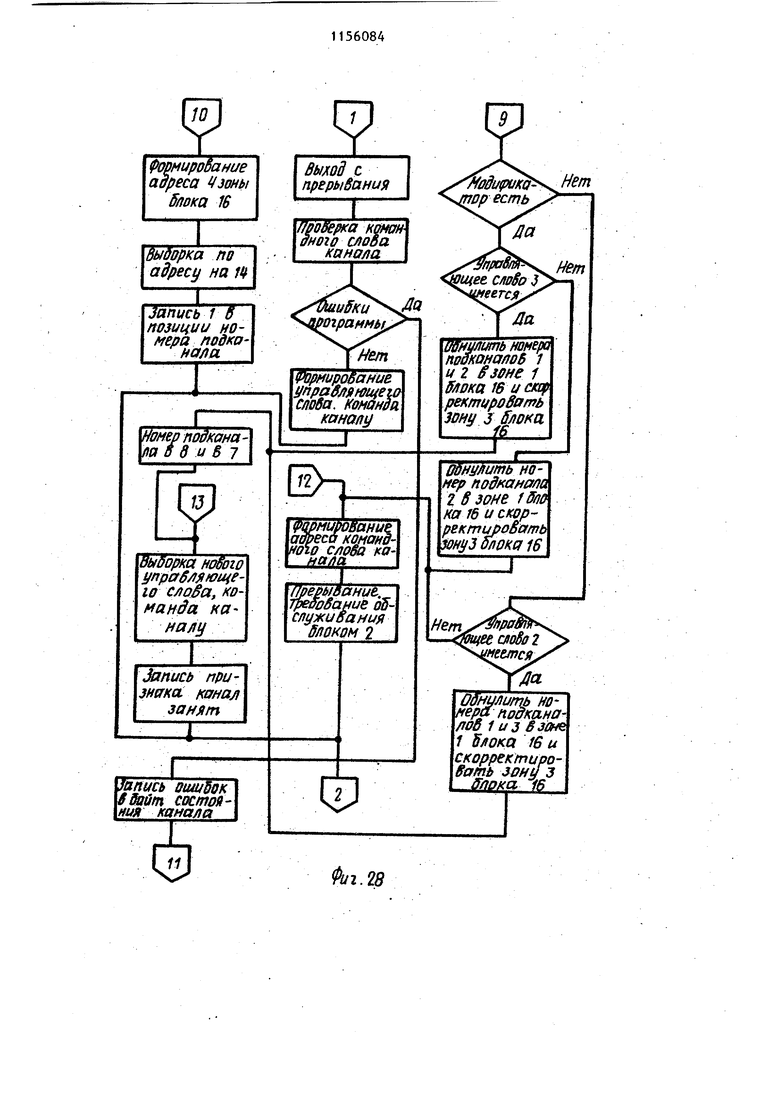

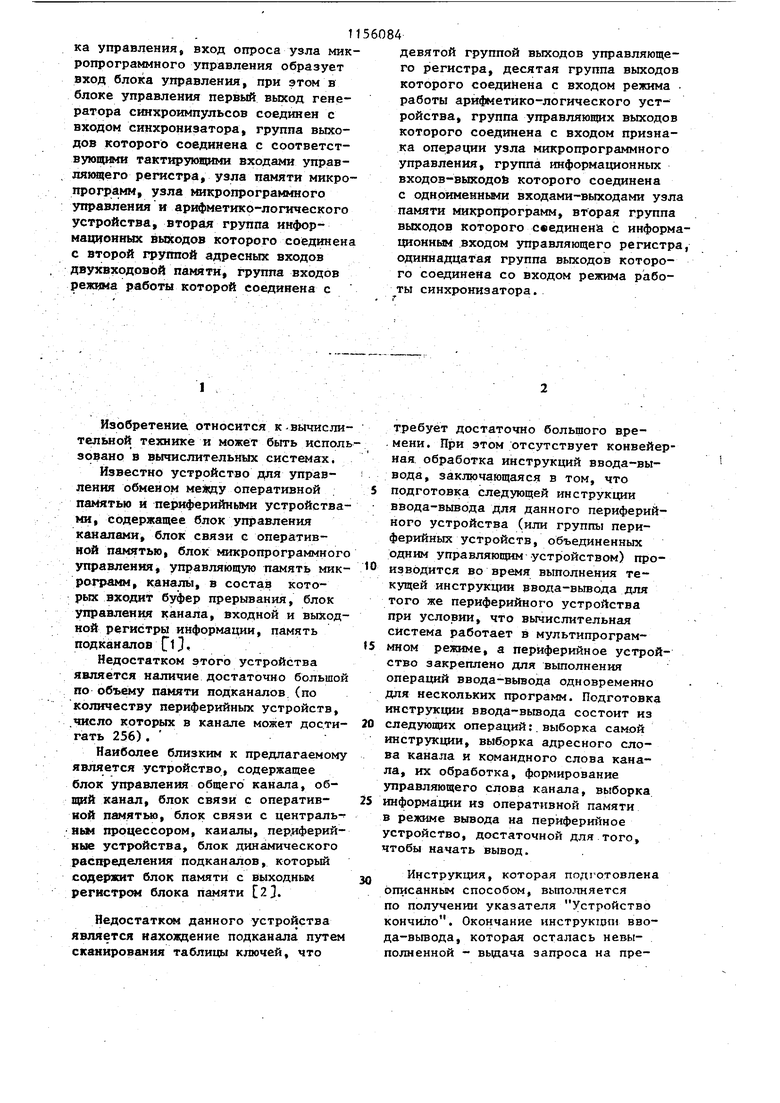

мультиплексор 151 служит для изменения значения регистра 1А9 состояний. Блок-схема алгоритма работы узлов микропрограммного управления 68 и 100 приведена на фиг. 20-29..

УстрЫ4ство для сопряжение периферийных устройств с процессором и оперативной памятью ((|мг.1) работает следующим образом.

Инструкция ввода-вьшода, определяющая вид операции, номер канала и номер периферийного устройства поступает с двусторонней связи 24 с центрального процессона на блок 1 связи с центральным процессором. Стробирующий импульс этой инструкции поступает на триггер 35, устанавливая его в единичное состояние по переднему фронту (фиг.2, 12) Потенциал с выхода триггера 35 поступает на узел 77 приоритетов блока 4 (фиг.5). По концу предьщущей закончившейся операции по обработке запросов на обслуживание в блоке 2 связи с оперативной памятью срабатывает элемент ИЛИ 44 и элемент ИЛИ 74 в блоке 4, и в случае отсутствия более приоритетньпс запросов на обслуживание в узле 77 приоритетов запрос с триггера 35

.появляется на выходе узла 77 приоритетов. Если блок 2 связи с оперативной памятью не производил запроса на обслуживание, то срабатывают И 82 и элемент ИЛИ 79.Значение выхода узла 77 приоритетов переписывается через узел элементов И 80 в регистр 83. Потенциал с р(вгистра 83 устанавливает триггер 35 в нулевое состояние, а узел элементов И 30 формирует адрес на первьй вход-выход двухвходовой памяти 63, используя значения шифратора 85, а узел элементов И 29 пересылает значение инструкции вводавывода на первый вход-выход двухвходовой памяти 63 для записи. С приходом следующего синхроимпульса на элемент И 31 с его выхода

.вьфабатывается сигнал, который поступает через двустороннюю связь

24 в центральный процессор, а также на блок 4. Центральный процессор в ответ на это снимает значение инструкции ввода-вывода с двусторонней связи 24. В блоке 4 сигнал поступает на элемент ИЛИ 74 и на

608422

демультиплексор 72, который записывает единицу по переднему фронту в место, соответствующее приоритету обработки инструкции ввода-выво5 Дз отведенное для нее в регистре 76. Элемент ШШ 74 вызывает-смену состояния регистра 83 по заднему фронту сигнала. С выхода регистра 76 значение его поступает на узел

JO 81 приоритетов. При Поступлении хотя бы одного требования на обслуживание на узел 81 приоритетов вырабатывается потенциал, который поступает на узел 68 микропрограммного управления блока 3 управления.

Окончив предьщущую операцию, блок 3 управления опрашивает потен, циал, поступающий с блока 4, и самое приоритетное требование на обслуживание с узла 81 приоритетов через . узел элементов И 84 запоминается в регистре 86 и поступает на вход шифратора 89.

С выхода шифратора 89 значение

25 кода попадает на вход арифметикологического устройства 69. Блок 3 управления определяет по коду требования на обслуживание микропрограмму отработки.

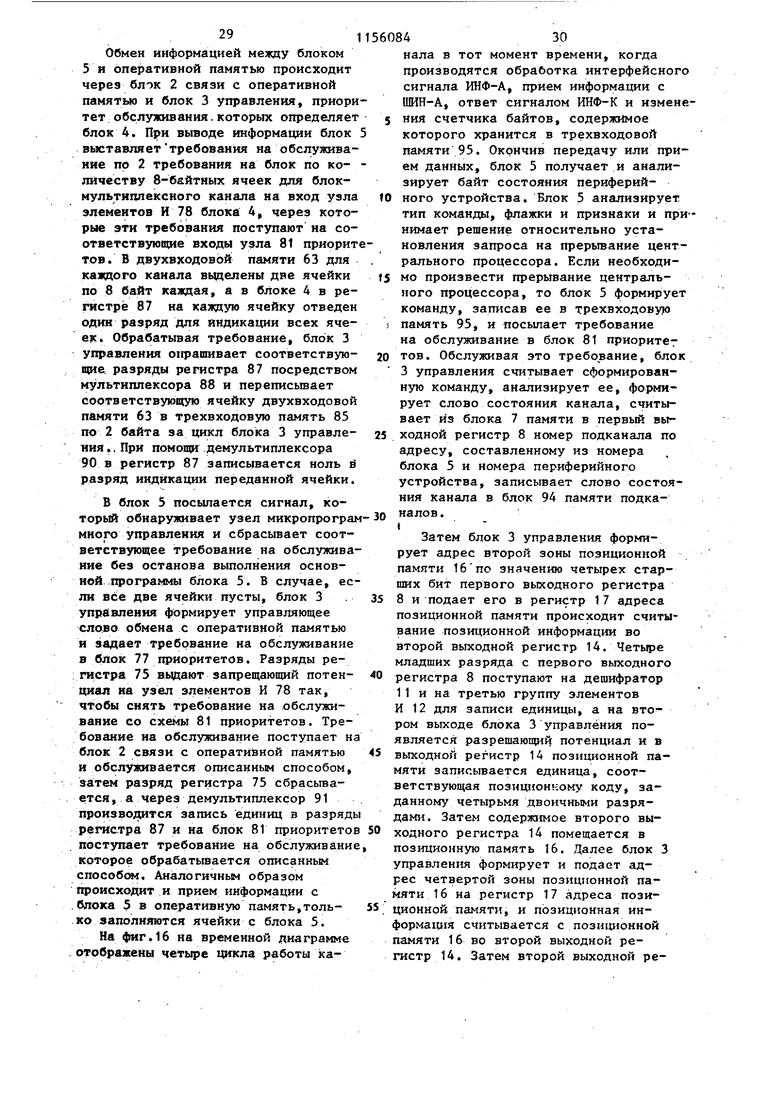

Блок 3 управления (фиг.4) может работать с переменной частотой цикла Т, Генератор 65 синхроимпульсов вьщяет синхроимпульсы, синхронизатор может распределять эти синхроимпульсы по четырем фазам, причем количество фаз может меняться от одной до четьфех, а в каждой фазе импульс может быть одинарной и двойной длительности. На фиг. 15 показана

0 временная диаграмма блока 3управления. Показаны изменения содержания управляющего регистра 64, изменения адреса, подаваемого на двухвходовую память 63, запись и считывание данных, а также вьодача результата

арифметико-логически устройством 69, формирование следующегр адреса узлом 68 микропрограммного управления, а также установление управляющего

0 слова по заданному адресу в узле 67 памяти микропрограмм. Блок 3 управления проверяет инструкцию ввода-вывода и определяет канал, на который данная инструкция адресована, опрашивает канал путем подачи номера .канала на мультиплексор 93 и анализирует потенциал с его выхода. Допустим принята инструкция ввода-вывода. Если канал занят, блок 3 управления формирует по номеру канала и номеру периферийного устройства адрес, который поступает с двухвходовой памя ти 63 через шинный коммутатор 18 на второй вход постоянного запоминающего блока 10, в то время как на первый вход постоянного запоминанще блока 1О поступает управляющий сигнал с блока 3 управления. Происходи обращение к блоку 7 памяти содержи мое адреса которого поступает в первый выходной регистр 8. Восемь первых разрядов ячейки блока 7 памя ти служат для записи найденного но мера подканала. Единица в девятом разряде служит признаком того,что периферийное устройство за1креплено за несколькими программами, а ноль - только за одной.. Единица в десятом разряде служит признаком того, что уже вторая по счету прог рамма требует обслуживания данным периферийным устройстве. В случае равенства нулю девятого бита на регистр 32 поступает признак результата 2, элемент Я 34 посьшает сигнал в центральный процессор, по которсму признак результата принимается центральньм процессором. Признак результата устанавливается с целью информирования центрального процессора о результате проверок, которые вьтолняются устройством при выполнении кся4анд вво да-вывода. Признак результата указывает выполнило ли устройство то, что ему было указано, и если нет, то по какой причине. Нулевой признак результата означает, что команда ввода-вывода принята, проверена на действительность, определены канал и периферийное устройство, куда она адресуется, а из оперативной памяти выбрано и проверено командное слов канала и найден свободный номер по канала, который занесен.в блок 7 памяти. Признак: результата 2 дёиачает, что свободного ш дкааала или нет или его нельзя занять В случае равенства единице девя того бита и нулю десятого бита выгодного регистра 7 памяти и неравенстве нулю первых восьми бит того же регистра блок 3 управления устанавливает единицу в 10-м разряде первого выходного ре гистра, возвращает исправленное значение первого выходного регистра 8 в блок 7 памяти, формирует управляющее слово обмена с оперативной памятью, .устанавливает в единичное состояние разряд регистра 75 посредством демультиплексора 71 и сбрасывает требование на обслуживание в регистре 76 демультиплексором 73. С р егистра 75 требование на обслуживание поступает на узел 77 приоритетов,и на выходе шифратора 85 появляется потенциал, который, поступая на элементы И 37 и 36, открывает их, посколыс дешифратор 40 определяет нулевое значение двоичного счетчика 39. С появлением потенциала с шифратора 85 подается адрес на nepBb i вход-выход двухвходовой памяти 63. Блок-схема блока 2 связи с оперативной памятью изображена на фиг.З, а временная диаграйма - на фиг.14. С приходом следующего синхронизирующего импульса запоминается значение, считанное с двухвходовой памяти 63, на триггере со счетным входом 52, регистре 5 3 признаков, реверсивнсж счетчике 54 через элемент И 56, узлы элементов И 57 и 60, а по заднему фронту того же импульса через элемент И 37, элемент ШШ 38 происходит смена значения двоичного счетчика 39, в результате чего на оперативную память поступает потенциал требования на (Обслуживание через двустороннюю связь 25. Элемент И 46 при значении дешифратора 40 01 ожидает ответного сигнала оперативной памяти. Когда этот сигнал поступает на вход элемента 46, потенциал с выхода этого элемента поступает на вход элемента И 42, и по задн&4у фронту очерёдного синхронизирующего импульса двоичный счетчик 39 принимает значение 10. По этому значению через элемент ИЛИ 48 блок комнутирукмцих элементов 49 коммутирует адрес оперативной памяти с первого входа-выхода двухвходовой памяти 63 iia двустороннюю Связь 25. Очередной синхронизм рующий импульс, действуя на вход элемента И 50 при значении дешифратора 40 10, изменяет значение двоичного счетчика 39 на 11 через элемент ИЛИ 38. С принятием значения t1 двоичн счетчиком 39 на первый вход-выход двухвходовой памяти 63 по9тупает адрес с реверсивного счетчика 54 че рез блок элементов И 51 и ИЛИ 62 дл приема адресного слова канала и с приходом стробирующего сигнала с оперативной памяти происходит запис адресного слова канала, в двухвходовую память 63 через блок коммутирую щих элементов 49. Поскольку триггер со счетньм входом 52 находится в ну левом состоянии, то с приходом стро бирующего сигнала с оперативной памяти срабатьшаёт элемент И 43, устанавливая двоичный счетчик в пер воначальное положение 00, а элемент ИЛИ 44 посылает на элемент ШТИ 74 сигнал, который вызывает смену состояния регист1 ов 83 и 76. На фиг. 14 изображена временная диаграмма в случае, когда необходим переслать два машинных слова. В слу чае возникновения ошибки при обраще нии к оперативной памяти срабатьгоает элемент И 45, двоичный счетчик сбра сывается в состояние 00 и вырабатывается сигнал на элемент ИЛИ 44 Адресное слово канала далее проверяется блоком 3 управления, формируется управляющее слово обмена с оперативной памятью и из оператив ной памяти извлекается командное слово канала таким же способом, как и для адресного слова канала. Командное слово канала проверяется блоком 3 управления. Затем происходит поиск свободного подка 1ала. С этой целью формируется адрес третьей зоны позиционной памяти 16 и подается в регистр 17 адреса пози ционной памяти. Содержимое этого адреса поступает во второй выходной регистр 14. Под управлением блока 3 управления на входы первой группы элементов И 20 для передачи прямого кода поступает разрешающий потенциал, и через группу элементов ИЛИ 21 код с выходного регистра позиционной памяти попадает на блок 22 приоритетов, на выходе которого появляется позиционный код группы подканалов, в крторьпс имеется хотя бы один позиционный адрес подканала, содержимое которого в настоящее время не бьшо бы занято управляющей информацией. Если такой адрес отсутствует, в процессор посылается признак результата 2. С блока 22 приоритетов позиционный код попадает на тпифратор 23 кода, с выхода которого код записывается в старшие четыре разряда регистра 17 адреса позиционной памяти (при ) и в старшие четыре разряда выходного регистра блока 7 памяти. Затем происходит обращение к по зиционной памяти 16 по вновь сфорюсрованному адресу. Содержимое адреса поступает во второй выходной регистр 14, затем код с выходного регистра позиционной памяти попадает через первую группу элементов И 20 для передачи прямого кода и группу элементов ИЛИ 21 на блок 22 приоритетов, затем на шифратор 23 кода, с , выхода которого переписывается в первый вьгходной регистр 8 в четыре младших разряда. Затем при поступдеНИИ на дешифратор 11 через третью группу элементов И 12 для записи единицы происходит запись единицы во второй выходной регистр 14, после чего его содержимое поступает в позиционную память. if. . Найденный описанным способом номер подканала сформирован в первом выходном регистре 8. Следующим циклом блок 3 управления заносит значение первого выходного регистра 8 в блок 7 памяти по адресу, на единицу большему предыцущего, на регистр 32 поступает признак результата О, а элемент И 34 посьшает сигнал в центральный процессор, по которому им принимается признак результата. Затем блок 3 управления проверяет наличие единичного потенциала на выходе блока 22 приоритетов. Если потенциал равен единице, то в данной группе позиционных адресов еще имеется хотя бы один адрес, содержимое которого в настоящее время не занято управляющей информацией и корректировать третью зону нет необходимости. Если потенциал равен нулю, то необходимо откорректировать третью зону. Для этого €лок 3 управления формирует адрес третьей зоны позиционной памяти 16, Содержимое этого адреса поступает во второй выходной регистр 14 и под управлением блока 3 управления на вход первой группы элементов И 20 для передачи прямого кода на блок 22 приоритетов и шифратор 23 записывается код в четыре младших разряда первого выходного регистра 8, откуда он поступает на дешифратор 11 через третью ifpynny элементов И 12 для записи единицы, происходит запись единицы во второй выходной регистр 1А, после чего его содержимое посту пает в позиционную память 16. В случае равенства девятого и десятого битов выходного регистра блока 7 памяти единице, как ив первом случае в центральный троцессор посылается признак результата 2, а поиск свободного подканала не производится. В случае, когда канал свободен, блок 3 управления формирует по номе ру канала и номеру устройства адрес и происходит, как и ранее, обращени к блоку 7 памяти Значение первого выходного ре истра 8 анализируется В случае равенства нулю первых восьми бит происходит поиск свободного подканала и запись его в блок памяти по этому же адресу, в центральный процессор посьшается признак результата О. В случае неравенства нулю первых восьми бит, равенстве единице девятого бита и равенстве нулю десятого бита происходит поиск свободного подканала и запись его в блок памят но уже по адресу, на единицу больше му первоначального. Признак результата посылаемый в центральный процессор О. В случае неравенства нулю первы восьми бит и равенства девятого бита нулю или равенства девятого и де сятого битов единице поиск свободного подканала не производится, а в центральный процессор посьшается признак результата После записи номера подканала в блок 7. памяти блок 3 управления фор мирует управляющее слово канала и записывает его в найденный подканал (в случае косвенной адресации управляющее слово канала дополняется первым словом косвенной адресации, а в случае передачи - еще одним машинным словом данных). Формирование управляющего слова канала происходит таким образом, что Э первых четырех битах каждого из четьфех слов подканала находится управляющая информация, целиком относящаяся к каналу (тип команды, номер периферийного устройства,флажки, счетчик байт в м,ашинном слове, счетчик байт в инструкции, байт состояния устройства, байт состояния канала, 8 байт пересылаемых данньпс), а в последующих четырех байтах - управляющая информация, целиком относящаяся к общему каналу (ключ защиты, адрес командного слова канала, адрес данных, флажки, первое слово косвенной адресации, номер подканала). Перепись всей управляющей информации из любого подканала памяти подканалов 94 в заданный блок 5 и двухвходовую память 63 через шинный коммутатор 18 производится за четыре цикла блока 3 управления (по четьфе байта в блок 5 и по четыре байта в двухвходовую память 63 за один цикл). Такое же время затрачивается и на обратную операцию переписи управляющей информации с блока 5 и двухвходоБой памяти 63 в любой подканал памяти подканалов 94. того, как управляющая информация переписана в память подканалов 94, найденный номер .помещается в блок 7 памяти, а если канал свободен, то через второй вход-выход трехвходовой памяти 95 записывается команда, а блок 4 посредством демультиплексора 92 посылает сигнал в канал, который запоминается на регистре состояний узла 100 микропрограммного управления канала. Блок 5, приняв команду, анализирует ее, производит начальную выборку периферийного устройства. Затем канал записывает по первому входу-выходу трехвходовой памяти команду и выставляет требование на обслуживание в блок 4 с регистра состояний узла 100 микропрограммного управления канала на узел 81 приоритетов. Блок 3 управления, когда поступившее требование на обслуживание становится самьм приЬритетнь, анализирует полученную команду и, в случае успешного окончания начальной выбJэpки, переписывает управляющую информацию с подканала памяти в блок 5, двухвходовую память 63 и .формирует команду в блок 5,который наинает обмен информацией. Обмен ииформацией между блоком 5 и оперативной памятью происходит через блок 2 связи с оперативной памятью и блок 3 управления, приори тет обслуживания, которых определяет блок 4. При выводе информации блок В111ставляет требования на обслуживание по 2 требования на блок по количеству 8-бгЙтных ячеек для блокмультиплексного канала на вход узла элементов И 78 блока: 4, через которые эти требования поступают на соответствующие входы узла 81 приорит тов. В двухвходовой памяти 63 для каясдого канала вьщелены две ячейки по 8 байт каждая, а в блоке 4 в регистре 87 на каяяую ячейку отведен один разряд для индикации всех ячеек. Обрабатьюая требование, блок 3 управления опрашивает соответствующие. разряды регистра 87 посредством мультиплексора 88 и переписьгаает соответствующую ячейку двухвходовой памяти 63 в трехвходовую память 85 по 2 байта за цикл блока 3 управления., При помощи демультиплексора 90 в регистр 87 записывается ноль и разряд индикации переданной ячейки. В блок 5 посылается сигнал, которь й обнаруживает узел микропрограм много управления и сбрасывает соответствующее требование на обслуживание без останова выполнения основной .программы блока 5. В случае, ес ли вбе две ячейки пусты, блок 3 . управления формирует управляющее слово обмена с оперативной памятью и задает требование на обслуживание в блок 77 приоритетов. Разряды регистра 75 вьщают запрещающий потенциал на узел элементов И 78 так, чтобы снять требование на обслуживание со схемы 81 приоритетов. Требование на обслуживание поступает на блок 2 связи с оперативной памятью и обслужива;ется описанным способом, зачтем разряд регистра 75 сбрасывается, а через демультиплексор 91 производится запись единиц в разряды регистра 87 и на блок 81 приоритетов поступает требование на обслуживание которое обрабатывается описанньм способам. Аналогичным образом происходит и прием информации с .блока 5 в оперативную память,только заполняются ячейки с блока 5. На фиг.16 на временной диаграмме .отображены четыре цикла работы ка84в тот момент времени, когда производятся обработка интерфейсного сигнала ИНФ-А, прием информации с ШИН-А, ответ сигналом ИНФ-К и изменения счетчика байтов, содержимое которого хранится в трехвходовой памяти 95. Окончив передачу или прием данных, блок 5 получает и анализирует байт состояния периферийного устройства. Блок 5 анализирует тип команды, флажки и признаки и при нимает решение относительно установления запроса на прерьгеание центрального процессора. Если необходимо произвести прерывание центрального процессора, то блок 5 формирует команду, записав ее в трехвходовую память 95, и посыпает требование на обслуживание в блок 81 приоритет тов. Обслуживая это требование, блок 3 управления считывает сформированную команду, анализирует ее, формирует слово состояния канала, считывает из блока 7 памяти в первый выходной регистр 8 номер подканала по адресу, составленному из номера блока 5 и номера периферийного устройства, записывает слово состояния канала в блок 94 памяти подканаловЗатем блок 3 управления формирует адрес второй зоны позиционной памяти 16по значению четырех старших бит первого выходного регистра 8 и подает его в регистр 17 адреса позиционной памяти происходит считывание позиционной информации во второй выходной регистр 14. Четыре младших разряда с первого выходного регистра 8 поступают на дешифратор 11 и на третью группу элементов И 12 для записи единицы, а на вто ром вьтходе блока 3 управления появляется разрешающий потенциал и в выходной регистр 14 позиционной памяти записывается единица, соответствующая позиционному коду, заданному четырьмя двоичными разрядами. Затем содерж1шое второго выходного регистра 14 помещается в позиционную память 16. Далее блок 3 управления формирует и подает адрес четвертой зоны позиционной паяти 16 на регистр 17 адреса позиционной памяти, и позиционная инормация считывается с позищюнной амяти 16 во второй выходной регистр 14. Затем второй выходной регистр 14 проверяется на наличие в четвертой зоне хотя бы одного подканала, в котором было бы сформировано слово состояния канала. Для этого блок 3 управления открывает вторую группу элементов И 19 для передачи инверсного кода и опрашивает первый выход блока 22 приоритетов. В случае отсутствия такого подканала блок 3 управления считывает слово состояния канала в двухвходовую память 63, формирует управляющее слово обмена с оперативной памятью и устанавливает триг гер 9 требования прерывания в единицу. В случае присутствия какого подканала считывание слова состояния каналаj формирование управляющего слова обмена,с оперативной памятью и запуска триггера 9 требования прерывания не производится. Затем, как ив случае коррекции третьей зоны, происходит коррекция четвертой зоны позиционной памяти 1 I Если прерьгааиие не связано с при ходом указателя Устройство кончило , то блок 3 управления переходит к выполнению следующего требования на обслуживание, если же прерывание связано с приходом указателя устройство кончило, то анализируется блоком 3 управления значение девято го и десятого битов первого выходного регистра 8. В случае равенства нулю девятого бита или в случае равенства девятого бита единице, а десятого нулю устанавливается в ноль восемь младших разрядов первог выходного регистра 8. В случае равенства единице девятого бита и равенства единице десятого бита блок 3 управления формирует адрес, на единицу больший заданного, по котороыу и производится обращение к бло ку памяти. Содержимое блока 7 пос тупает на первьй выходной регистр 8 затем формируется прежний адрес, по которому в блок 7 памяти заносится значение первого выходного регистра 8. Через шинный кижмутатор 18 значе ние второго выходного регистра 14 поступает на арифметико-логическое устройство 69, откуда задается адре на блок памяти подкакалав, и управляияцая информация поступает в задан ный блок 5 и двухвходовую память 63 блока 3 управления и записывается за четыре цикла, через второй входвыход трехвходовой памяти 95 произ- . водится запись команды, а блок 4 посьшает сигнал в канал, после чего блок 3 управления переходит к обслуживанию след5тощего требования. С единичного выхода триггера 9 требова- ния прерывания потенциал поступает на вход элемента И 26, триггера 27 и элемента И 28 (фиг.2 и 13).Поскольку триггеры 27 и 33 находятся в нулевом состоянии, на выходе элемента И 26 возникает положительный пoтeнIц aлj который поступает на вход узла 77 приоритетов. Обслужив поступившее требование, блок 2 связи с оперативной памятью устанавливает триггеры 27 и 33 в единицу, тем самым элемент И 26 закрывается. Триггер 33 вьщает по двусторонней связи 24 сигнал требования на пре рьтание в центральный процессор, а триггер 27 т требование на обслуживание в узел 81 приоритетов. Блок 3 управления по заданному тре:бованию устанавливает ноль во второй зоне позиционной памяти 16, определяет освободился ли подканал, слово состояние канала которого передано в оперативную память.Если подК-чнал освободился,то происходит установление нуля и в первой зоне позиционной памяти 16.Затем блок 3 управления откорректирует четвертую и, если произошел сброс единицы в первой зоне, то и третью зону позиционной памяти 16. После этой процедуры блок 3 управления проверяет наличие хотя бы одной единицы во второй зоне позиционной памяти 16. Если такой единицы нет, то устанавливается в нуль триггер 9 требования прерывания и триггер 27. В этом случае с приходом сигнала по двусторонней связи 24 с центрального процессора на элемент И 28 и триггер 33. элемент И 28 вьщает в центральный процессор сигнал о конце прерывания, а триггер 33 устанавливается в ноль. Если единица во второй зоне позиционной памяти 16 имеется, то блок 3 управления считьгеает слово состояния какала в двухвходовую память 63, формирует новое управляющее слово обмеиа с оперативной памятыо и устанавливает триггер 27 в ноль. В этом случае с приход сигнала по двусторонней связи 24 с центрального процессора на триггер 33 33 на элементе И 26 появляется положительный потенциал, и весь цикл работы повторяется,. Таким образом, в данном устройстве для периферийных устройств, закрепленных за несколькими програ мами в системе,работающей в мульти программном режиме, образуются оче реди в одну инструкцию с заранее сформированной управляющей информа цией, что позволяет увеличить быстродействие системы как за счет выборки самой инструкции выборки адресного слова, канала и командног слова канала и формирования управляющей информации так, .так и за счет окончания инструкции после получения указателя Устройство кончило . . Конвейерная обработка инструкции ввода-вывода в блок-мультиплексном канале позволяет получить дополнительное увеличение быстродействия за счет запуска новой инструкции на то же периферийное устройство, хотя в это время и. имеются требования от других периферийных устройст Эти требования будут обслужены по получении указателя Канал кончил Образование очередей в одну инструкцию стало возможным благодаря введению схем динамического распределения подканалов, которые совмещены со схемами поиска подканалов в которых содержится слово состояния канала. Путем введения зон З.и 4 позиционной памяти t6 упрощается поиск подканалов. Время поиска - дв цикла блока 3 управления. При этом отсутствуют буфера прерывания. В предлагаемом устройстве благодаря Применению постоянного запоминающего блока 10 объем блока 7 памя ти не увеличился. Управляющая инфор мация разбита на две части, а шинны коммутатор 18 позволяет производить ее перепись из блока 5 и из двухвхо довой памяти 63 блока 3 управления в блок 94 памяти подканалов 94 и обратно по четьфе байта в блок 5 и по четыре байта в двухвходовую память 63 за один цикл блока 3 управления, что увеличивает быстродей ствие предлагаемого устройства. Отсутствуют адреса командного слова канала и данных разрядностью 3 байта. Это позволило установить 8434 разрядность арифметико-логических устройств 101 каналов в 1 байт. Трехступенчатая структура управлением устройством позволила использовать двухвходовую память 63 в качестве регистрового файла для блока 3 управления и отказаться от регистра адреса и выходного регистра в блоке 2 связи с оперативной памятью, функции которых взял на себя первый входвыход двухвходовой памяти. Передача и прием информации блоком 3 управления осуществляется по 2 байта через шинный коммутатор 18 без прерьгаания работы блока 5, что позволяет каналу достичь большого быстродействия за счет экономии .времени на синхронизации) передачи или приема информации. В современных электронных вычислительных машинах оперативная память состоит из элементов с высокой степенью интеграции поэтому цикл ее записи или считьгеания составляет около 1 мкс. Если учесть порядок доступа к оперативной памяти, то ее цикл будет еще большим. Блок 3 управления прерывает свою работу, как только необходимо обратиться к оперативной памяти через блок 2 связи с оперативной памяти, что позволяет значительно повысить мощность блока 3 управления, так как его цикл в среднем составляет около 100 НС. Данное устройство позволяет обрабатьшать цепочки данных и цепочки команд так, что они проходят без потери времени для периферийного устройства. Для цепочки данных занимается новый подканал в блоке 94 . памяти подканалов, формируется управляющая информация и записывается в новый подканал во время выполнения предьщущей части инструкции вводавывода, а номер подканала запоминается в подканале, в котором содержится управляющая информация, под управлением которой выполняется в настоящее время инструкция вводавьгоода. По мере выполнения инструкции ввода-вывода происходит освобождение подканала в памяти подканалов и запись нового подканала. Для цепочки, команд по получении указателя канал кончил занимаются два новых подканала в памяти подканалов, их номера запоминаются в подканале выполня(амой части инструкции ввода-вывода. В первом подканале формируется управляющая информация следующей части инструкции ввода-вывода, а во втором подканале - следующая за информацией в первом подканале инструкции ввода-вывода,Если будет получен указатель Устройство кончиi t А

ло без указателя Модификатор, то первый подканал становится деиствзгющим, а второй освоб6яздается,если же будет получен указатель Устройство кончило с указателем Модификатор, то второй подканал становится действующим, а первый освобозвдается.

Фи.г.1

Фиг.Ч f-Si} Dtntl (fSJonL W9fft)) Mf3{&}

ami.

63

на1

il

i-

65

55

57

Ж

jj

2Z.

55

на 18

ri

на В

-

на 20

на 13

4

над - паю

на П

ни5

69

Фи1Л

от 2t

Фи-i.d

123

пд

от 22

с

нал, 8

л

л

131

130

фиг. 9

U

Фиг.11

&«Z./J

Выход S7 тл ,Lm -г--11 Lm , , ,,

ifui.fS fj ifljr - т BЫ)(Oд6 Фазо1. 0Ч7Л72 I Фаза ВшодЩ- )Г fje.vtahTarX.. МГ . Bwd 35 -----V,- X Выход 35------v данные-- л- 8ыхо&3бjkM

Выход98 : - . Выход 1DD - - v Вы)(од 93 - --у . . Л- i

Время доступа рвня переписи

.

4 2|j V

Is

|б

n

Sfimix ma.

|i g if

6: -

--t- il.n 1156084 j., Л Ц ГД ХТ ..- ----- .г vV- ,. Y - -л/- -V А Д А (.. .-...-У-- -XллHK Фиг.16

2Вход-ёшодЗВ)((од

Ф,, W од-ёыкод

(рормиробание адреса, сиитыВание с 7

Регистр Запись 8 7 регистра в

Нет

Жтанооить при jHffif решьтата 2 В Шок 1

Фиг. 20

1

Перепись данных S xaHffi 5

(рормироВание управляющего Прерывание. Требование оаспу живани GflOком 2 Формирование адреса данны хтаноВка ошио ки§ йиите света ЯИИ9 кана/ia , W -fi - -. требование ol Формирование слу иВания слаба состояSflOKOM 2 ния канала, и nepedcti a его В блок 2 УсгпанрБка признака резшьтата. 1 Установка . запис признака ка нал свободен

формирование адреса J зоны слова блока 16 fe.2/ апись адреса ервой JOHbi бпока 16 ормирование мера поднанала S 8 Запись 1 В озицию ре lucmpa, П

Запись регистре) 14 8 16

Рормиробание

Запись 8 адреса блока В 7

1 ормиро6ание. ynpaEflmuino

зоны 3

оррещи}

ffepenucb vaonu Да управляющего

ли ноль о

т,

нет

станоёка признака результата О

Номанда В 5

формирование ад/жа памяти

ДОС слоЬа

Нет

Мтаноёить . записать СП оба 6 5

признак канал свободен

Запись при2на ка результата 2

I

Запись 8 67

Ф

Запись 8 В

7

I

рормироБание.

1 раблян}щего

слова.

I

Запись управляющего СЛОдО В 3f

(риг.22

Нет

Выход с прерыSoHUfi

формирование

Переписать В

ffaum с S5 В адреса $о Врата

Формирование адреса StaSpama

Т/ рывдние т/ е5оданий обслу)ки$аний SaoKOH 2

перепись ннм из 63 6 95

Cifpoc mpeSo1 ания

Вь/ход с прерыбан //

тре5оёания

2 Ч/

Фиг. 73

.

(1 ормирование адреса j зоны

Выход с npepbfSaHij/i блока 16

ет SD

запись номера, подканала 2S тьорегисп рсгёляющее Cfloт1 и упраблянз Да

фврмиро аиие номера подшнат В 8

Запись 1 D позицию реwcmpa т

7(роБерка JKOMQHдного слова канапа 2

запись упроблЯ №щего cfloBa 2 В поакана 2 о m oHufl г 6 9tf щее с/ю6о1б Sif

Нет

Формирование адреса командаго споВа №напа1

формирование адреса даинык

Запись регистра т 6 16

I

//рермёание, третание одслужиёани SnoKOH 2

Нет

Wxoot прврыВан1 (рормироёание

jpaeflHtoufeio

йоба 2 Запись п зиака канал свободен MfttfCi) affoeca первой зоны д/11жа К Рортро6аиие нонера подканала. 26 д Запись 1 о позицию регистра fif Запись регисnjpa, 1V6 16

Коррекций зоны 3

/jBtiC номера L (10 «омала запись номера подканала 2 быпробляющее слово 1 рормпро банив 00 (кса командного сло8а канала 2 //рер 15ание Треообамця oiicfiyЖибСМиЯ ffflOKOM

Фаг.25 запись ошиоок Saum состояния анала упраёяющего слова ynpaeflfitou4et cnoSo 2 В 9ff Ч ормиробсгние одрес данных /ffKpb/вание. ком 2

с пре1)ы8ания

Выход с прерывания

fjpepi aHtie. вбслужиёаНиЯ BflOKCLM 2

Фиг. 26

ет

Bbfffopua по номеру канапл и устройства из7 В в

Запись слова состояния канала, S 35

I

гпаноВка гпрш гера 3 $ е иницу

формирование

1

Считать из 7 по 8

Запись 8 7

1

1

Записать по

запись признака номеру канат канал сбои устройства бооен и

L

.

1

Мпись п изнакс

канал jctнят.

U

.27

Фиг.28

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборное колесо | 1921 |

|

SU370A1 |

| М., Мир, 1974 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления обменом между оперативной памятью и внешними устройствами | 1978 |

|

SU789988A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-05-15—Публикация

1983-05-11—Подача