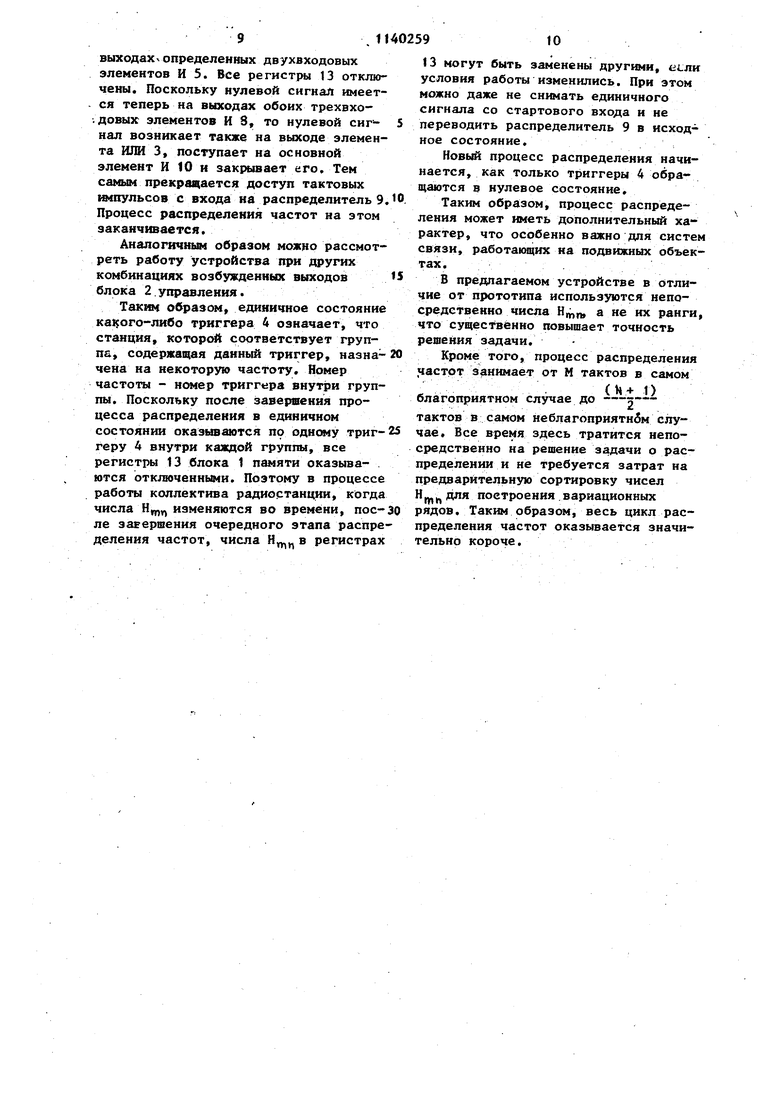

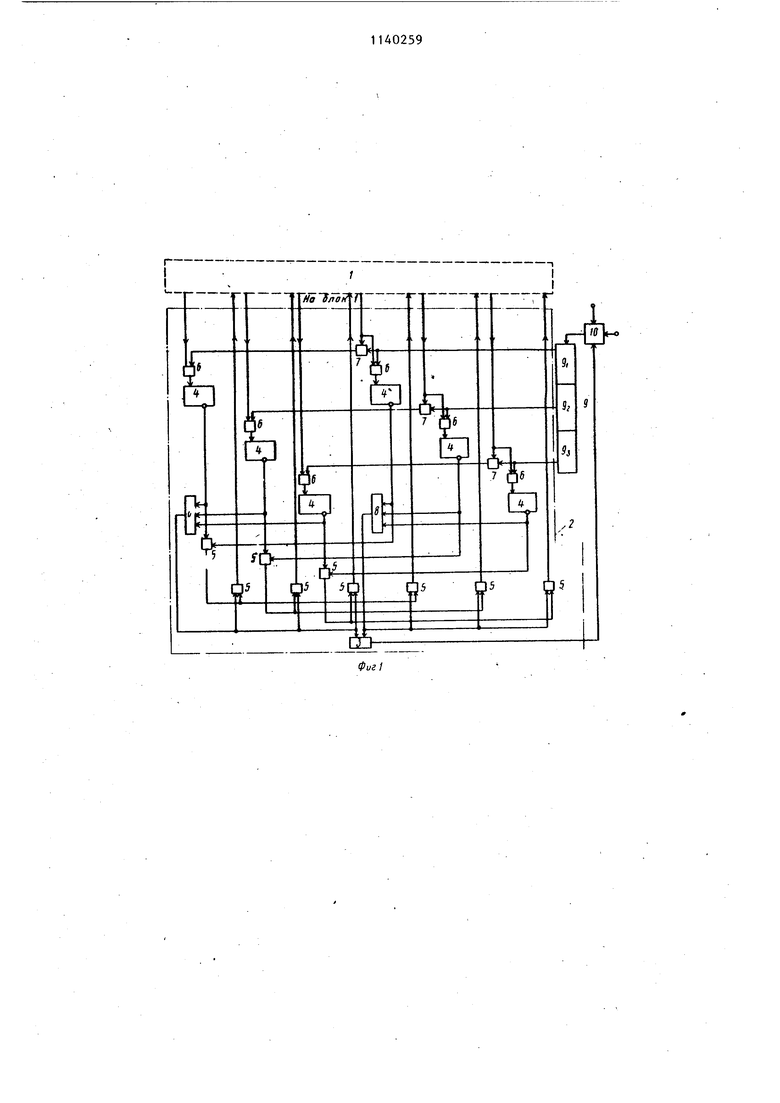

Изобретение относится к технике радиосвязи и может использоваться для распределения частот в сети ради останций при построении систем связи .с подвижными объектами. Известно устройство для назначения рабочих частот, содержащее блок памяти, выходы которого подключены к входам блока управления, выход которого соединен с первым входом блока памяти Л . Недостаток известного устройства заключается в низкой точности назначения частот при воздействии помех Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для распределения частот в сети радиостанций, содерж.ащв;е распределител выходы которого подулючены к входам блока управления,.который соединен с блоком памяти 21. Однако это устройство имеет низку точность. Цель, изобретения - повышение точности. Поставленная цель достигается тем, что в устройство для распределения частот в сети радиостанций, содержащее распределитель, выходы которого подключены к входам блока управления, который соединен с блокбм памяти, введен основной элемент И, выход которого подключен к йходу распределителя, при этом блок памяти содержит блоки элементов ИЛИ, блоки элементов И и регистры, Каждьй из которых состоит из элементов памяти элементов И и элементов РАВНОЗНАЧНОСТЬ, причем выходы элементов памяти подключены к первым входам одних элементов И, выходы которых соединены с входами соответствующих блоков элементов ИЛИ, выходы которых подключены к первым входам соответствующих элементов РАВНОЗНАЧНОСТЬ, BTopbie входы которых соединены с вьпсодами одних элементов И, вторые входы которых являются управляющими входами блока памяти, стартовым входом которого являются первые входы блоков элементов И, вторые входы которых соединены с выходами соответствующих элементов РАВНОЗНАЧНОСТЬ и с входами других элементов И при этом выходы блоков элементов И я ляются выходами блока памяти, а блок управления состоит из триггеров. двухвходовых элементов И, входных элементов И, элементов НЕТ, трехвходовых элементов И и элемента ИЛИ. входы которого соединены с выходами трехвходовых элементов И и с первьми входами одних двухвходовых элементов И, к вторьм входам которых подключены выходы двугих двухвходовых элементов И, входы которых соединены с входами соответствующих трехвходовых элементов И и с выходами соответствующих триггеров к входам которых подключены выходы входных элементов И, причем выходы распределителя соединены с первьми входами элементов НЕТ, выходы которых подключены к первым входам одних входных элементов И, и с первыми входами других входных элементов И,-вторые входы которых соединены с вторыми входами соответствующих элементов НЕТ, выход элемента ИЛИ плдключен к первому входу основного элемента И, второй и третий входы которого являются соответственно стартовым и тактовым входами устройства, при этом вторые входы элементЬв НЕТ и одних входных элементов И являются входами блока управления,, выходами которого являются выходы одних двухвходовых элементов И. На фиг. 1 изображена струкурная электрическая схема предлагаемого устройства; на фиг. 2 - то же, блока памяти. Устройство для распределения частот в сети радиостанций содержит блок 1 памяти, блок 2 управления, состоящий из элемента ИЛИ 3, триггеров 4, двухвходовых элементов И 5, входных элементов И 6, элементов НЕТ 7 и трехвходовых элементов И 8, распределитель 9, имеющий первый 9, второй 9л и третий 9 выходы, основной элемент И 10. При этом блок памяти содержит (фиг. 2) блоки 11 элементов ИЛИ, блоки 12 элементов И, регистры 13, каждый из которых состоит из элементов 14 памяти, элементов И 15 и элементов РАВНОЗНАЧНОСТЬ 16. Устройство работает следующим образом. Все регистры 13 блока 1 памяти (фиг. 2) разбиты на группы число которых равно числу радиостанций в коллективе (М станций). Число регистров 13 Б каждой группе равно числу частот, отведенных для работы 3 коллектива радиостанций (N частот). Работа .устройства рассматривается на примере коллектива, содержащего две станции (), для работы которого отведено три частоты (). Соответственно этому блок 1 памяти содержит две группы регистров 13 по три регистра в каждой группе. Перед началом работы устройства в регистры 13 записываются в двоичном коде значения чисел Н , опреде ляющих качество работы каждой станции, входящей в коллектив, на каждо частоте, В первый регистр 13 первой группы записывается двоичное выражение числа Н (качество, которое обеспечит первая станция, если оно будет работать на первой частоте). Во второй регистр 13 записано число (первая станция, вторая частота В третий регистр 13 первой группы число Н (первая станция, третья частота). В следующий регистр 13 (первый регистр второй группы) - число Н, (вторая станция, первая частота). Далее - число (вторая станция, вторая частота), и, наконец, в последний регистр 13 (третий регистр третьей группы) - число Н,. Запись осуществляется таким образом, что разряды по старшинству располагаются сверху вниз (старший разряд в самый верхний элемент 14 памяти). В исходном состоянии все, триггер 4 (фи1. 1) блока 2 находятся в нуле вом состоянии и, следовательно, на их инверсных (нулевых) выходах имеются единичные сигналы. Совпадение единичных сигналов от инверсных выходов триггеров 4 блбка 2 управле НИН вызывает единичные сигналы на выходах обоих трехвходовых элементов И 8, а тйкже на выходах соответствукицих двухвходовых элементов И 5. Поэтому.на выходах других двух входовых элементов И 5 также имеют место единичные сигналы. Эти единич ные сигналы поступают на управляющи входы регистров 13 блока 1 памяти и далее на элементы И 15 каждого регистра 13. Одновременно единичные сигналы с выходов трехвходовых элементов И 8 блока 2 управления поступают.на входы элемента ИЛИ 3, вызывая на его выходе единичный сигнал. Этот сигнал поступает на основной эле594мент И 10. Однако до тех пор, пока по стартовому входу не поступит единичный сигнал, основной элемент И 10 остается закрытым, не позволяя тактовым импульсам, поступающим на его тактовый вход, проникать на вход распределителя 9. Первый этап работы устройства заключается в сравнении всех чисел целью выбора максимального из них. Это сравнение начинается с отбора тех чисел, которые имеют единицу в старшем разряде. Очевидно, что искомое максимальное число должно находиться среди них. Числа снулем в старшем разряде заведомо меньше и, следовательно могут быть, отброшены, за исключением случая, когда нули записаны в старших разряДах всех регистров 13. В этом случае анализ переносится на более низкий уровень, в следующий, более младший разряд. ЕсЛи же в старших разрядах некоторых чисел имеются единицы, то дальнейшему анализу подвергаются только эти числа. Если некоторые из чисел Н, таковы, что в их.старших разрядах имеются единицы, то единичные сигналы имеют место на прямых выходах элементов 14 памяти старших (верхних по схеме) разрядов соответствующих регистров 13. Эти единичные сигналы, проходя через открытые элементы И 1-5, поступают на входы блока 11 элементов ИЛИ и элемент РАВНОЗНАЧНОСТЬ 16. Наличие единичного сигнала хотя бы на одном из входов блока 11 элементов ИЛИ вызывает появление единичного сигнала на его выходе. Этот единичный сигнал поступает на вторые входы элементов РАВНОЗНАЧНОСТЬ 16 старшего разряда всех регистров 13. Элемент РАВНОЗНАЧНОСТЬ 16 формирует на своем выходе единичный сигнал лишь тогда, когда сигналы на его входах имеют одинаковое значение ,(оба нули, либо оба единицы). Поэтому единичный сигнал имеет место на выходах только тех элементов РАВНОЗНАЧНОСТЬ 16, которые имеют единичные сигналы на своих первых входах, т.е. тех, на которые от элементов 14 памяти через элементы -И 15 поданы единичные сигналы. Нулевые сигналы, записанные в остальных элементах памяти 14, также через соответствукицие им элементы И 15 записываются в паузах на свои J. элементы РАВНОЗНАЧНОСТЬ 16. Посколь ку на вторые входы этих элемен гов РАВНОЗНАЧНОСТЬ 16 поступает единичн сигнал, то выходной сигнал указанны элементов РАВНОЗНАЧНОСТЬ 16 нулевой Сигналы (единичные либо нулевые) с выходов элементов РАВНОЗНАЧНОСТЬ 16 старшего разряда всех регистров 13 поступают на соответствующие каждом из этих регистров 13 блоки 12 элементов И. Одновременно нулевые сигналы с выходов тех элементов РАВНОЗНАЧНОСТЬ 16, где они имеют место, поступают на соответствующие элемен И 15 следующего более младшего разряда, тем самым блокируют эти эле.менты, и из. анализа исключается весь регистр 13 с нулем в старшем разряде. Если все числа Н таковы, что их двоичное изображение имеет в старшем разряде нуль, то элементы 14 памяти старшего разряда всех регистров 13 находятся в нулевом со стоянии и через открытые элементы И 15 на все входы блока 11 элементо ИЛИ старшего разряда, а также на входы элементов РАВНОЗНАЧНОСТЬ 16 старшего разряда всех регистров 13 поданы нулевые сигналы. Нулевой сигнал, который имеет место в этом случае на выходе блока 11 элементов ИЛИ, поступает на вторые входы всех элементов РАВНОЗНАЧНОСТЬ 16. Таким образом, сигнал):, на обоих входах каждого из этих элементов РАВНОЗНАЧ НОСТЬ 16 имеют одинаковое значение, и выходной сигнал у каждого из них оказывается единичным. Эти сигналы поступают на соответствующие элемен И 15 следующего более младшего разряда и на блок 12 элементов И, Анйлиз, таким образом, переносится в следующий младший разряд. На уровне этого более младшего разряда процес сы повторяются. I Если наибольшее значение имеет только одно из чисел, записанных в регистрах 13, то на всех входах бло ка 12 элементов И, соответствующего этому регистру 13, имеют место единичные сигналы. Если таких, чисел несколько, то возбуждены входы всех блоков 12 элементов И, соответствующих регистрам 13, содержащим эти числа. Наконец, если все числа один ковы (в том числе, когда все они равны нулю), то возбуждены все вход 59 блока 12 элементов И всех регистров 13. Процесс записи чисел Н является подготовительным, причем, как следует из описанного, непосредственно после записи чисел в регистры 13 блок 1 памяти подготовлен к реализации операции выбора максимального числа. Рабочий цикл предлагаемого устройства начинается в момент поступления запроса на частоты. Этот запрос реализуется подачей единичного сигнала на стартовый вход основного элемента И 10 и блока 1 памяти. Единичный сигнал со стартового входа проходит лишь через те блоки 12элементов И, у которых возбуждены все остальные входы. Поскольку это имеет место только для тех блоков 12 элементов И,-в чьих регистрах 13 записано наибольшее число, единичный сигнал проникает только через эти блоки 12 элементов И на соответствующие им управляющие выходы. образом, скорость протека|Ния процессавыбора наибольшего числа (чисел) определяется лишь временем распространения стартового сигнала от .входа к выходу. Единичные сигналы с тех выходов блока 1 памяти, которые соответствуют регистрам 13с максимальным числом, поступают на входные элементы И 6, триггеры 4 и на управляющие входы элементов НЕТ 7. Соответствующие входные элементы И 6 открываются, а элементы НЕТ 7 запираются. Триггеры 4, как и регистры 13, разбиты на группы. Каждому регистру 13и выходу в блоке 1 соответствует триггер 4. В исходном состоянии распределитель 9 находится в положении, при котором возбужден его первый выход 9 . Единичный сигнал с первого выхода 9. распределителя 9 поступает на входные элементы И 6 и элементы НЕТ 7 соответствующего триггера 4 (первого триггера второй группы). Если число Нл, , соответствующее указанному триггеру 4, оказывается наибольшим либо входит в число наибольших, входной элемент И 6, соответствующий этому триггеру 4, оказывается открытым, а элемент НЕТ 7 закрытым. Поэтому единичный сигнал с первого выхода 9( распределителя 9 через входной элемент И 6 проникает на соответствующий вход триггера 4 второй группы и переводит его в .единичное .состояние. При этом единичный сигнал на инверсном выходе триггера сменяется нулевым и поступает на соответствующий двухвходовой элемент И 5. Нулевые сигналы, которые, в сво очередь, появляются на выходах этих элементов И, поступают на другие двухвходовые элементы И 5, вызывая нулевые сигналы на выходах этих элементов. Следовательно, нулевой сигнал поступает на управляющий вход соответствующий определенному регист 13, и на управляющие входы всех других регистров 13, Нулевой сигнал с входа попадает ,на элементы И 15 и отключает все элементы 1А п-амяти от соответствующих им блоков 11 элементов ИЛИ, т.е. исключает весь регистр из анализа. Перевод соответствующего триггера 4 в- единичное сос тояние означает, что первая частота назначается второй станцией, т.е. на эту частоту назначается станция, которая может на ней работать наи- более эффективно. Отключение других регистров 13 соответствует тому, что вторая станция получила свое назначение и, следовательно, не може больше претендовать на частоты. Отключение соответствующего регистра 13 первой группы (в котором записано Качество, которое обеспечит первая станция, если она будет работать на первой частоте отвечает тому факту, что первая частота уже занята и претендовать на нее больше нельзя. Если число Нл, не оказалось максимальным (или в .числе максимальных то на управляющем выходе, который соответствует регистру 13, где запи сано это число, имеется нулевой сиг нал. Поэтому соответствующий указан ному выходу входной элемент И 6 оказывается закрытым, а элемент НЕТ 7 - открытым, и единичный сигна с выхода 9 распределителя 9 на триггер 4 не поступает, а проходит. через элемент НЕТ 7 и поступает на входной элемент И 6, соответствующи другому триггеру 4. Если число Н. , записанное в определенном регистре 13 максимальное, то на соответствующем этому регистру 13 управляющем выходе имее йесто единичный сигнал, открывающий входной элемент И 6. Поэтому единич ньй сигнал с выхода 9 распределите 9, прошедший элемент НЕТ 7, через открытый входной элемент И 15 поступает на соответствующий вход триггера 4 и переводит его в единичное состояние. Это означает, что первая частота отдается первой станции. Аналогично описанному в указанном случае нулевой сигнал появляетчя на инверсном выходе триггера 4, на выходе соответствующего трехвходового элемента И 8, на выходах определенных двухвходовых элементов ИЗ, на выходах всех других двухвходовых элементов И 5. Соответствующие двухвходовые элементы И 5 подают нулевые сигналы на соответствующие им управляющие входы и тем самым отключают все регистры 13. Таким образом, первая станция Получает первую частоту (определенный триггер 4 переведен в единичное состояние), вся первая станция исключается из дальнейшего анализа (все регистры 13 первой группы отключены), первая частота занята, и вторая станция уже не может претендовать на нее (первый регистр 13 второй группы отключен). Наконец, если оба числа Н, 2$ не входят в число максимальных, оба входных элемента И 6, соответствующие регистрам, где записаны эти числа, закрыты, и единичный сигнал с выхода 9, распределителя 9 не может перевести первые триггеры 4 в единичное состояние, то это означает, что первая частота остается незанятой ни той, ни другой станцией. Тактовый импульс, поступгиощий вслед за этим на тактовый вход через открытый основной элемент И 10, следует на распределитель 9 и переводит его в следующее состояние. При этом единичный сигнал с выхода перемещается на выход 92 распределителя .9. .Если максимальным было число Н , то, как описано, определенные регистры 13 отключены, а блок 1 памяти осуществляет выбор наибольшего из / оставшихся чисел Соответственно этому открытыми оказываются входные элементы И 6 (либо один, либо другой, либо оба вместе). Если наибольшим оказалось число Н , то триггер 4 переходит в единичное состояние (первой станцией назначена вторая частота), на инверсном выходе этого триггера 4 появляется нулевой сигнал. Нулевой сигнал возникает на

выходахX определенных двухвходовых элементов И 5. Все регистры 13 отключены. Поскольку нулевой сигнал имеется теперь на выходах обоих трехвхо.довых элементов И 8, то нулевой сигнал возникает также на выходе элемента ШШ 3, поступает на основной элемент И 10 и закрывает его. Тем самым прекращается доступ тактовых импульсов с входа на распределитель 9. Процесс распределения частот на этом заканчивается.

Аналогичньн образом можно рассмотреть работу устройства при других комбинациях возбужденных выходов блока 2.управления.

Такян образом единичное состояние какого-либо триггера 4 означает, что станция, котор Л соответствует группа, содержащая данный триггер, назначена на некоторую частоту. Номер частоты - номер триггера внутри группы. Поскольку после завершения процесса распределения в единичном состоянии оказываются по однсму триггеру 4 внутри каждой групгал, все регистры 13 блока 1 памяти оказыва- . ются отк;шченными. Поэтому в процессе работы коллектива радиостанции, когда числа Н,, изменяются во времени, после заеергаения очередного зтапа распределения частот, числа Н в регистрах

13 могут быть заменены другими, е1.ли условия работы изменились. При этом можно даже не снимать единичного сигнала со стартового входа и не переводить распределитель 9 в исходное состояние.

Новый процесс распределения начинается, как только триггеры 4 обращаются в нулевое состояние.

Таким образом, процесс распределения может иметь дополнительный характер, что особенно важно для систе связи, работакицих на подвижных объектах.

В предлагаемом устройстве в отличие от прототипа используются непосредственно числа э их ранги что существенно повышает точность решения задачи. Кроме того, процесс распределения tiacTOT занимает от М тактов в самом

(Н+ 1) благоприятном случае до j

тактов в самом неблагоприятнбм случае. Все время здесь тратится непосредственно на решение задачи о распределении и не требуется затрат на предварительную сортировку чисел построения .вариационных рядов. Таким образом, весь цикл распределения частот оказывается значительно короче.

На Sfleif

rfi

хГ

ю

гк

f

-Шг:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления подачей топлива в двигатель внутреннего сгорания | 1979 |

|

SU859665A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Цифровое измерительное устройство для обработки сигналов частотных датчиков | 1989 |

|

SU1659891A1 |

| СПОСОБ ДЕТЕКТИРОВАНИЯ СИГНАЛОВ С МАГНИТНОГО НОСИТЕЛЯ ИНФОРМАЦИИ, ЗАПИСАННЫХ RLL КОДАМИ, И ДЕТЕКТОР ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2015 |

|

RU2623660C2 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| Датчик случайных чисел | 1981 |

|

SU1007104A1 |

| Цифровой измеритель угловой скорости | 1982 |

|

SU1016741A1 |

| Аналого-цифровой преобразователь поразрядного кодирования | 1976 |

|

SU657607A1 |

УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЧАСТОТ- В СЕТИ РАДИОСТАНЦИЙ, содержащее распределитель, выходы которого подключены к входам блока управления, который соединен с блоком памяти, отличающееся тем, что, с целъ.о повьпиения точности, в него введен основной элемент И, выход которого подключен к входу распределителя, при этом .блок памяти содержит блоки элементов ИЛИ, блоки элементов И и регистры, каждый из которых состоит из элементов памяти, элементов И и элементов РАВНОЗНАЧНОСТЬ, причем выходы элементов памяти подключены к первым входам одних элементов И, выходы .которых соединены с входами соответствующих блоков элементов ИЛИ, выходы которых Лтодключены к первым входам соответствующих элементов РАВНОЗНАЧНОСТЬ, вторые входы которых соединены с выходами одних элементов И, вторые входы которых являются управляющими входами блока памяти, стартовым входом которого являются первые входы блоков элементов И, вторые входы которых соединены с выходами соответствующих элементов РАВНОЗНАЧНОСТЬ и с входами других элементов И, при этом выходы блоков элементов И являются выходами блока памяти, а блок управления состоит из триггеров, двухвходовых элементов И, входных элементов И, элементов НЕТ, трехвходовых элементов И и элемента ИЛИ, входы которого соединены с выходами трехвходовых элементов И и с первыми входами одних двухвходовых элементов И, к вторым входам которых подключены выходы других двухвходовых элементов И, входы которых соединены с входами соответствующих трехвходовых элементов И (Л и с выходами соответствукицих триггеров, к входам которых подключены выходы входных элементов И, причем выходы распределителя соединены с первыми входами элементов НЕТ, выходы которых подключены к первым входам одних входных элементов И, и с пер( выми входами других входных элементов И, вторые входы которых соединены с о ел вторыми входами соответствующих элементов НЕТ, выход элемента ИЛИ подключен к первому входу основного :о элемента И, второй и третий входы которого являются соответственно стартовым и тактовым входами устройства, при этом вторые входы элементов НЕТ и одних входных элементов И являются входами блока управления, выходами которого являются вы7:оды двухвходовых элементов И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Хлытчиев С.М | |||

| и др | |||

| Пути автоматизации радиоприемных центров | |||

| - Электросвязь, 1958, № 6, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для распределения частот в сети радиостанций | 1976 |

|

SU640443A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-02-15—Публикация

1981-04-22—Подача