логического блока, первый управляющий вход этого блока соединен с первым выходом блока сравнения, а другие входв - с выходными шинами распределителя импульсов, введен дополнительный преобразователь кода в напряжение и инвертор, причем выход дополнительного преобразователя кода в напряжение соединен с третьим входом блока сравнения, а входы - с шинами распределителя импульсов, второй : управляющий вход логического блока подключен к второму выходу блока сравнения, а третий вход логического блока подключен через инвертор к третьему выходу блока сравнения

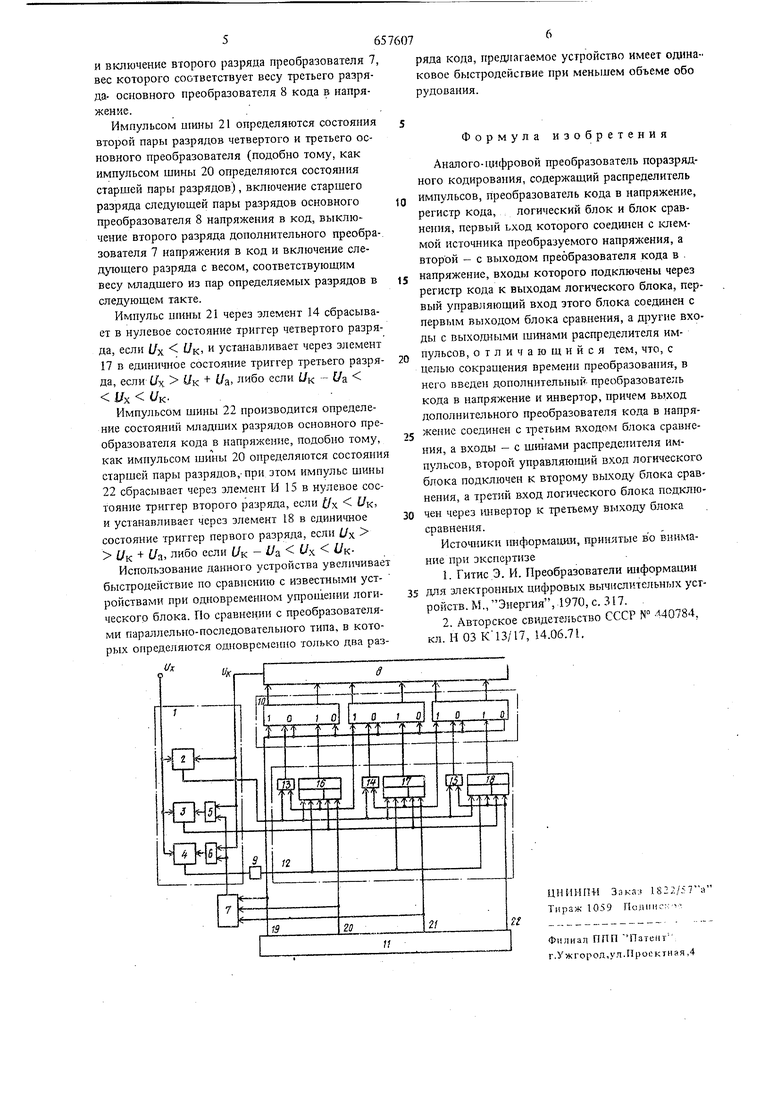

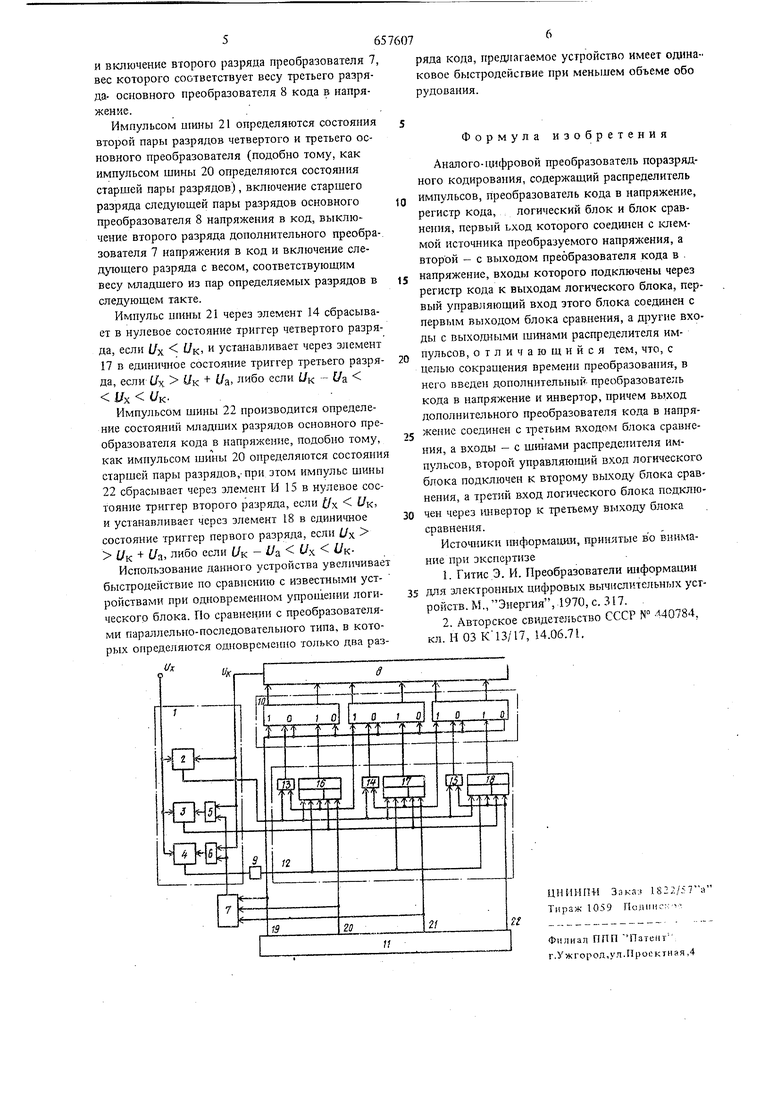

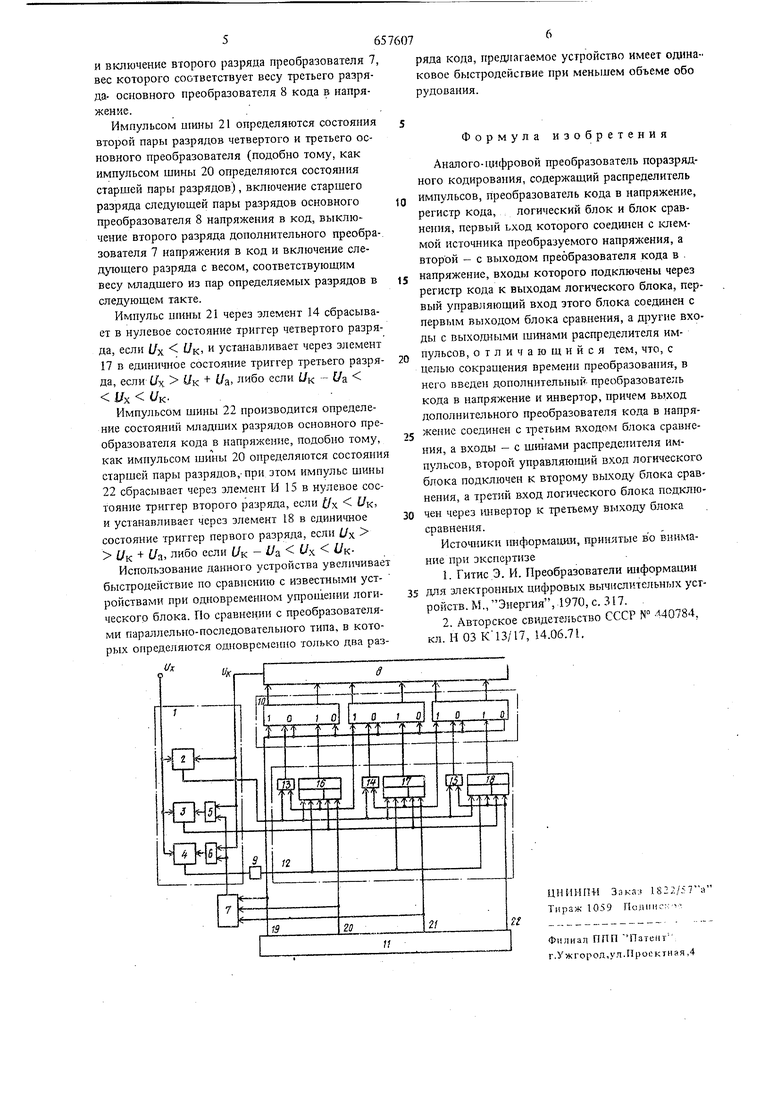

На чертеже изображена структурная схема предлагаемого устройства.

Для npHMispa взят шестиразрядный преобразователь, содержащий блок сравнения 1, состоящий ю нуль-органов 2-4 и аналоговых блоков сложния 5 и блока вычитания 6, дополнительный преобразователь 7 кода в напряжение, основной преобразователь 8 кода в напрян ение, инвертор 9, регистр 10, распределитель 11 импульсов логического блока 12, состоящего из элементов И 13 -15, элементов 2 И-И ЛИ 16-18, входные шины 19-22 распределителя импульсов.

Первый вход блока сравнения 1 соединен с источником преобразуемого напряжения, второй вход - с выходом преобразователя 8; вход последнего через регистр 10 кода соединен с выходом блока 12; первый управляющий вход бло ка 12 соединен с первым выходом блока сравнения 1, а другие входы - с выходами распределителя 11 импульсов; выход дополнительного преобразователя 7 соедижи с третьим входом блока сравнения 1, а входы этого преобразователя - с шинами распределителя И, второй управляющий вход блока 12 соединен с вторым выходом блока сравнения 1 измеряемого напряжения с суммой напряжения, а третий вход логического блока 12 через инвертор 9 подключен к третьему выходу блока 1 измеряемого напряжения с разностью найряжений преобразователей 8 и 7; выход аналогового блока сложения 5 соединен с входом нуль-органа 3, а выход аналогового блока вычитания 6 - с входом нуль-органа 4; шина 19 распределителя 11 соединена с установкой единицы старшего и установкой нулей остальных р;13рядов триггеров регистра кода, а шины 20-22 - с установочнымивходами групп по два разряда регистра 10 кодов через логический блок 12, причем шины 20-22 соединены с входом установки нуля старшего из группы триггера через двухвходовые элементы И 13-15, другие входы которых соед1шены с выходом блока сравнения 1 измеряемого напряжения с напряжением преобразователя 8, а с входами установки единицы младших из групп триггеров через элементы 2 И-ИЛИ 16-18; другие входы

элементов 2 И-ИЛИ 16--18 у двухвходовых элементов И соединены с вторым входом блока 12, у трехвходовых элементов И - один с первым, а другой -- с третьим входами логического блока 12; шины 20 и 21 соединены со входами установки единицы соответстве1шо триггеров четвертого и второго разрядов регистра 10 кодов.

На первом выходе блока сравнения 1 (выход нуль-органа 2) вырабатывается сигнал 1, если i/x С/к, и сигнал О, если U UK где

U- - измеряемое напряжение; UK - напр:яжение компенсации на выходе основного преобразователя 8.

На втором выходе блока сравнения 1 (выход нуль-органа 3) вырабатывается сигнал 1, если Ух //к + i/a, и сигнал О, если i/x UK + + {/а где Ua - напряжение на выходе преобразователя 7 кода в напряжение; - напряжение на выходе аналогового блока сложения 5. На третьем выходе блока сравнения 1 (выход нуль-органа 4) вырабатывается сигнал 1, если и &к - Ua, и сигнал О, если /х UK - - /а, где UK напряжение на выходе аналогового блока вычитания 6. Импульсом с шины 19 устанавливаются в регистре 10 все разряды, кроме старшего, в нулевое состояние, шестой разряд устанавливается в единичное состояние, в преобразователе 7 устанавливается в единичное состояние старший разряд, вес которого соответствует весу пятого разряда основного преобразователя кода в. напряжение, остальные два разряда устанавливаются в нулевое состояние. Импульсом с шины 20 производится установка шестого и пятого разрядов регистра 10 в состояние, определяемое соотношением напряжений на выходе блока сравнения 1.

Если УХ UK и УХ к а) то шестой разряд остается в единичном состоянрш, а пятый устанавливается в единичное состояние через двухвходовый элемент И элемента 2 И-ИЛИ 16.

Если /х i/K и i/x к + t/a то шестой разряд остается в единичном состоянии, а пятый в нулевом, так как на установовдые входы обоих триггеров импульс шины 20 не проходит.

Если (/X С/к и УХ С/к - i/a. то шестой разряд устанавливается в нулевое состояние че рез элемент 13, а пятый - в единшшое состояние через трехвходовьш элемент И элемента 2 И-ИЛИ 16.

Если i/x и i UK i/a то шестой разряд устанавливается в нулевое состояние через элемент И 13, а пятый остается в нулевом состоянии, поскольку импульс щины 20 через элемент 2 И-ИЛИ 16 не проходит.

Одновременно импульсом шины 20 производится установка в единичное положение четвертого разряда регистра 10 и выключение третьего

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1640818A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU744968A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1979 |

|

SU782147A2 |

| Устройство аналого-цифрового преобра-зОВАНия | 1979 |

|

SU809554A1 |

| Аналого-цифровой преобразователь с самоконтролем | 1980 |

|

SU886236A2 |

| Устройство для контроля монтажа | 1985 |

|

SU1352505A1 |

| Следящий аналого-цифровой преобразо-ВАТЕль | 1979 |

|

SU797064A1 |

| Аналого-цифровой преобразователь поразрядного уравновешивания | 1971 |

|

SU440784A1 |

| Преобразователь напряжения в код | 1987 |

|

SU1427568A1 |

Авторы

Даты

1979-04-15—Публикация

1976-04-26—Подача