Изобретение относится к вычислительной технике и может быть исполь- .зовано в спе1щализированных вычислительных системах.

Цель изобретения - повышение быстродействия.

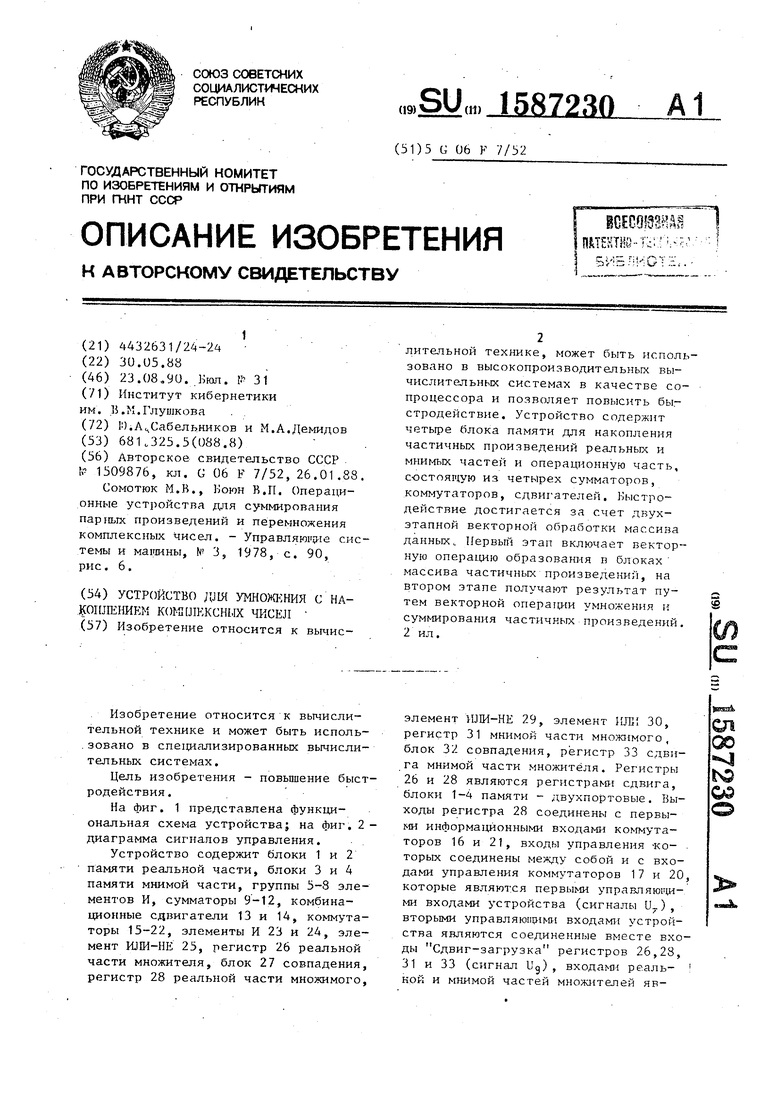

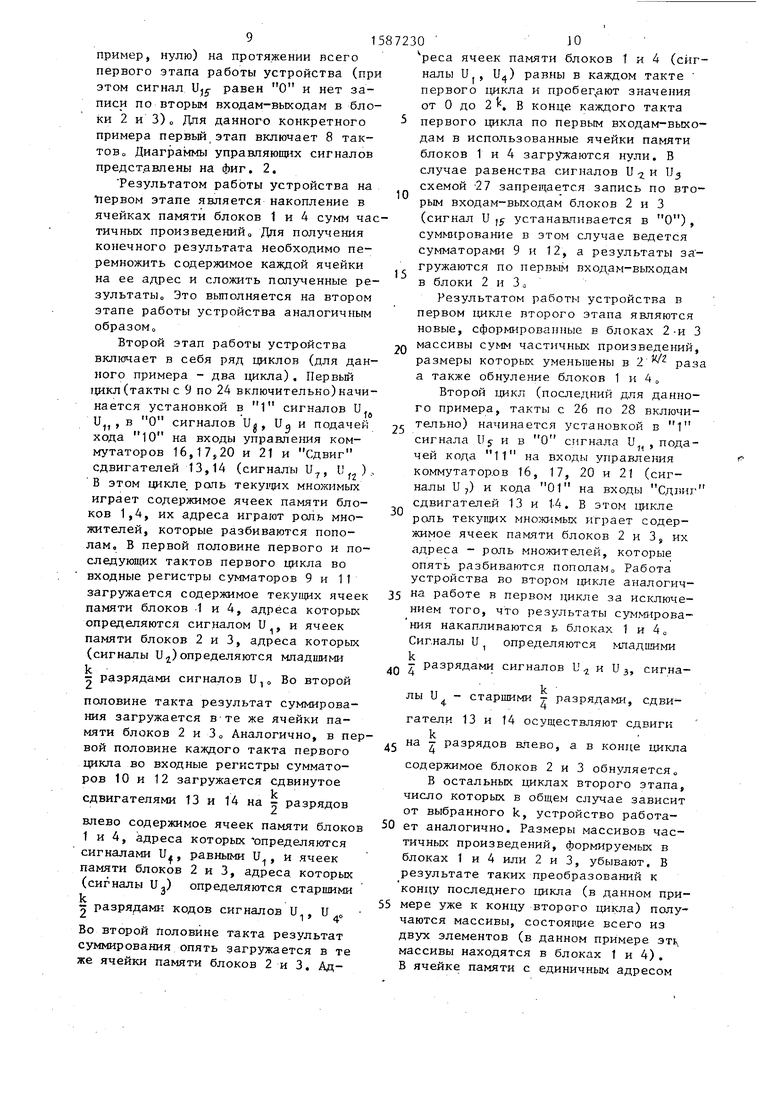

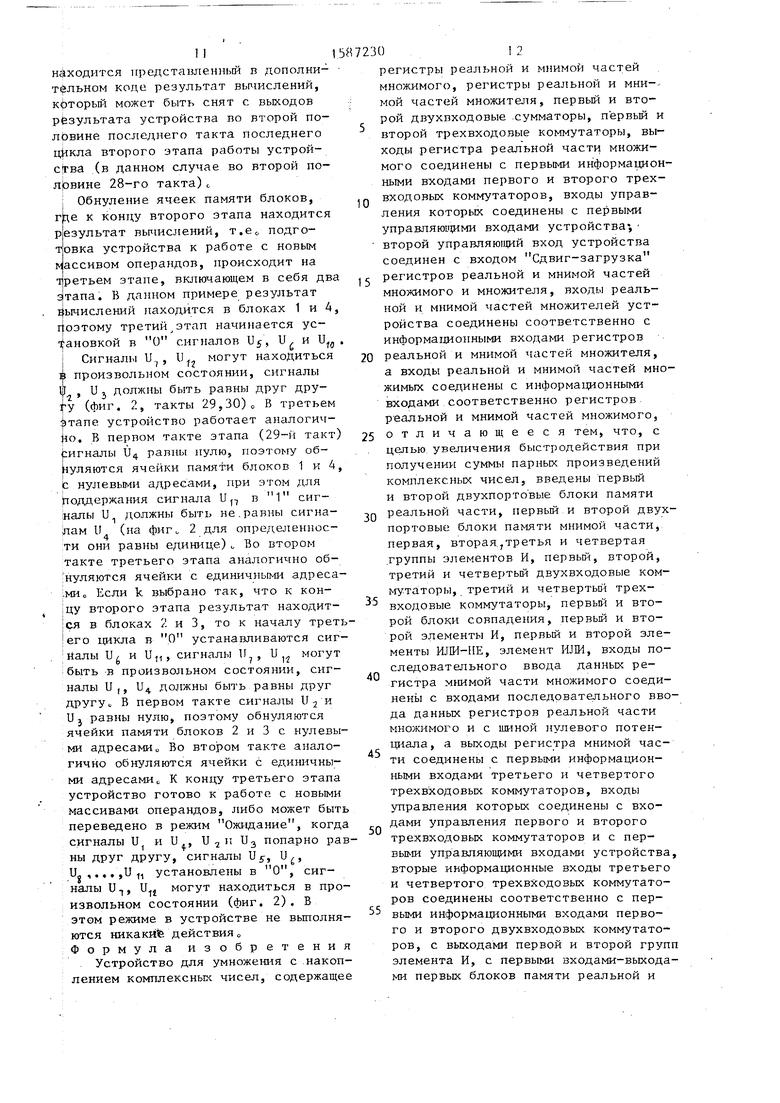

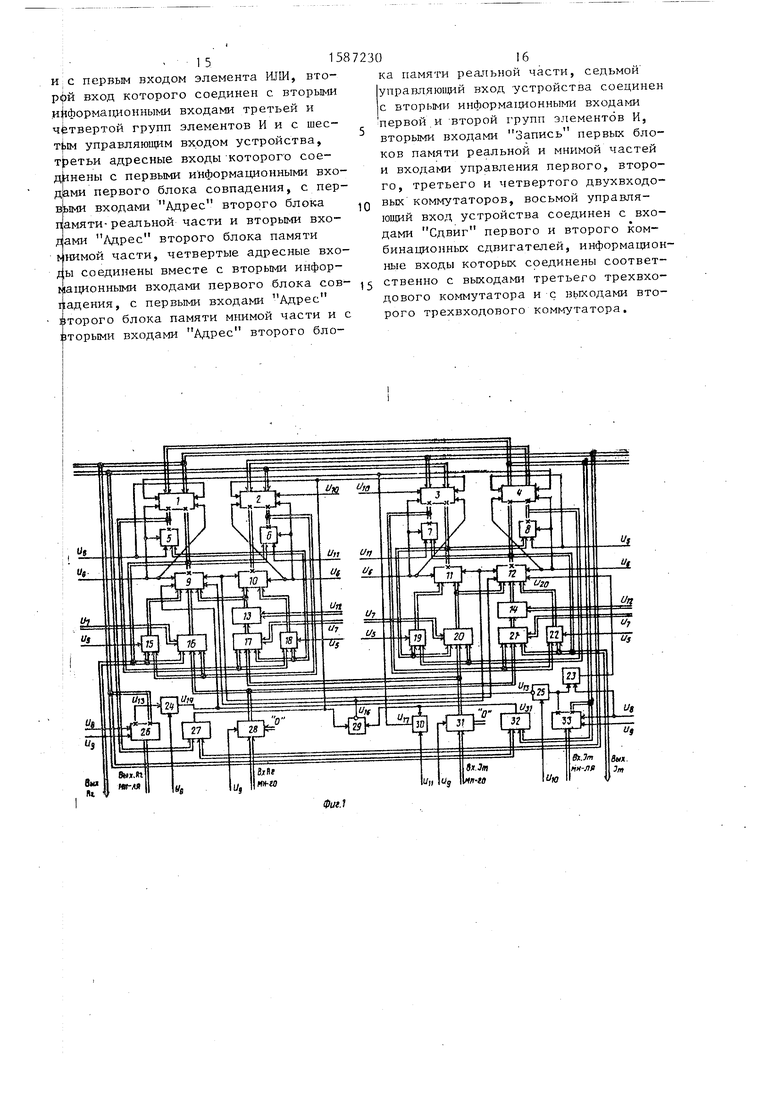

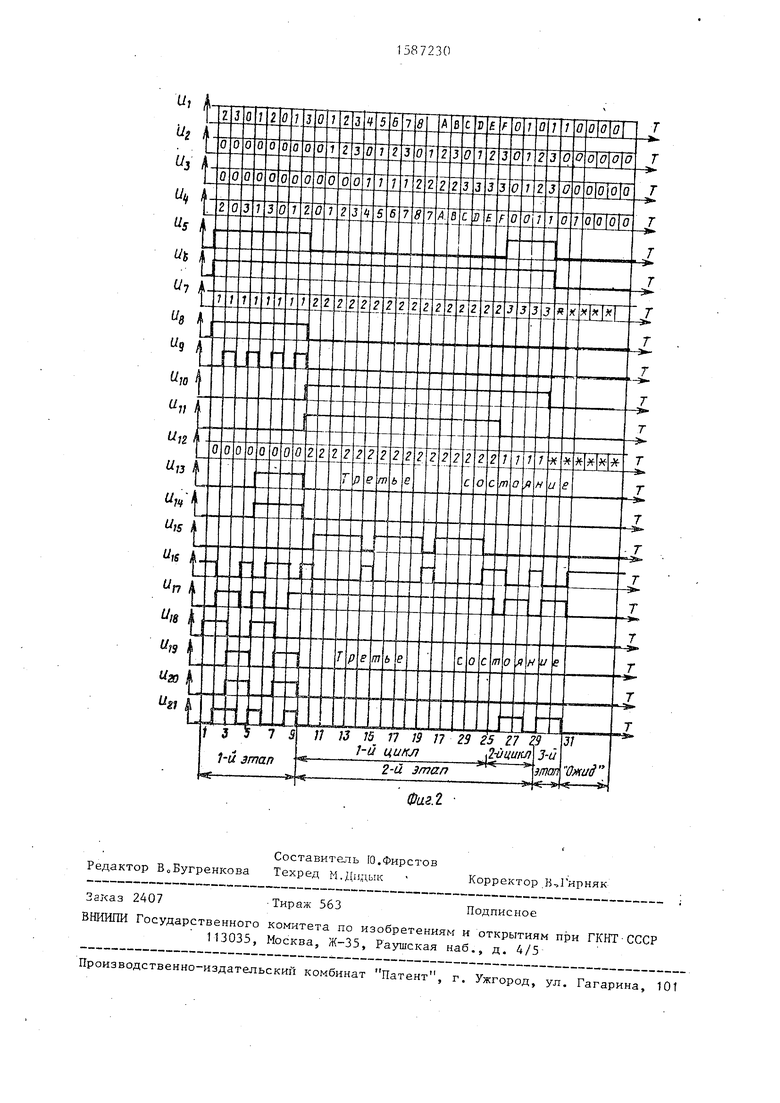

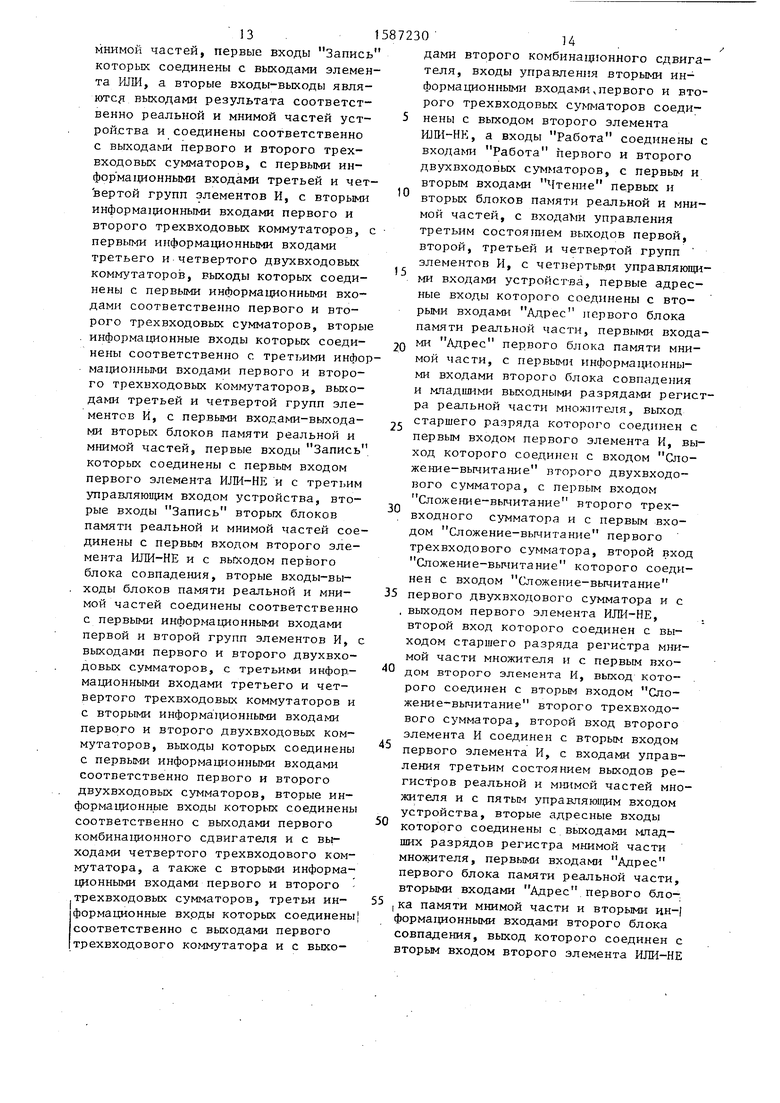

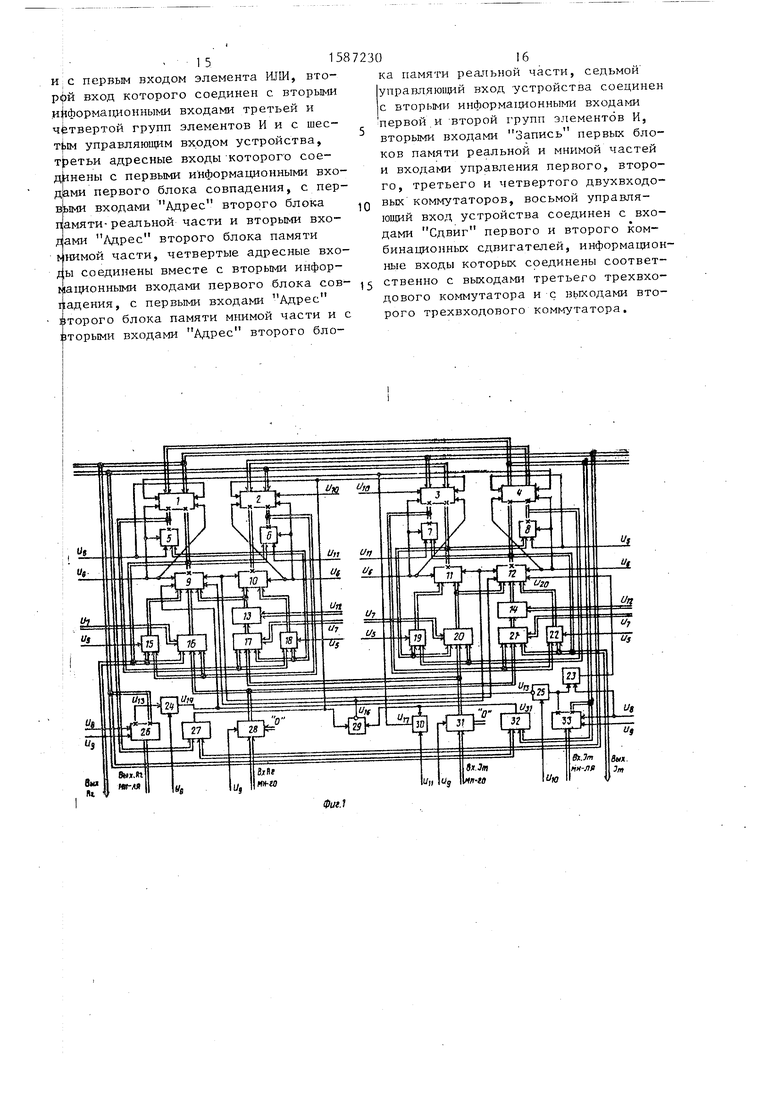

На фиг. 1 представлена функциональная схема устройства; на фиг. 2- диаграмма сигналов управления.

Устройство содержит блоки 1 и 2 памяти реальной части, блоки 3 и 4 памяти мнимой части, группы 5-8 элементов И, сумматоры 9-12, комбинационные сдвигатели 13 и 14, коммутаторы 15-22, элементы И 23 и 24, элемент ИЛИ-НЕ 25, регистр 26 реальной части множителя, блок 27 совпадения, регистр 28 реальной части множимого.

элемент У1ЛИ-НЕ 29, элемент ИЛИ 30, регистр 31 мнимой части множимого, блок 32 совпадения, регистр 33 сдви- .га мнимой части множителя. Регистры 26 и 28 являются регистрами сдвига, блоки 1-4 памяти - двухпортовые. Выходы регистра 28 соединены с первыми информа :1йонными входами коммутаторов 16 и 21, входы управления -ко- . торьк соединены между собой и с входами управления коммутаторов 17 и 20 которые являются первыми управляюищ- i-Di входами устройства (сигналы U) , вторыми yпpaвляюIци входами устройства являются соединенн 1е вместе входы Сдвиг-загрузка регистров 26,28, 31 и 33 (сигнал Ug), входами реаль- ной и мнимой частей множителей яв0100 tC

ляютсу информаи юниые входы соответственно регистров 26 и 33, а входами реальной и мнимой частей множимых являются информационные входы соот- ветственно регистров 28 и 31, входы последовательного ввода данных устройства соединены с входами последовательного ввода данных регистра 28 и с шиной нулевого потен1щала, а вы- |ходы соединены с первыми информационными входами коммутаторов 17 и 20, вторые информационные входы которых соединены соответственно с первыми ин |формационными входами коммутаторов 18 и 19, с выходами элементов И 5 и 8 |И с первыми входами-выходами блоков 1 и 4 памяти, первые входы Запись Которых соединены между собой и с вы- 1 ХОДОМ элемента 30 (сигнал U ,., ) , I вторые входы-выходы блоков 1 и 4 I являются выходами соответственно ре- альной и мнимой частей результата устройства и соединены соответствен- но с выходами сумматоров 9 и 12, с первьми информа щонными входами элементов 6 и 7, с вторыми информацио} - HiiiMH входами коммутаторов 16 и 21, а также с первыми инфopмaциoмны ш входами коммутаторов 15 и 22, выходы ко- торых соединены с первыми; информащюн ными входами соответственно суь5мато- ров 9 и 12,,вторые информащ-юнные входы которых соединены соответственно с третьими информационными входам-:

коммутаторов 16 и 21, с вьгходам г элементов И 6 и 7 и с первыми входа- ки-выходами блоков 2 и 3, первЕяе входы Запись которых соеди}шны между собой и с первым входом элемента 25, а также с третьим управляю1цим входом устройства (сигнал U), вторые входы Запись соединены между собой, с первым входом элемента HJO-l-HK 29 и с выходом блока 27 совпаде ия (сиг- нал и jg) J вторые входы-выходы блоков 2 и 3 памяти соединены соответственно с первыми информационными Входами элементов И 5 и 8, с выходами сумматоров 10 и 11, с третьими информационными входами коммутаторов 17 и 20, а также с вторыми ин- формахщонными входами коммутаторов 18 и 19, выходы которых соединены с первыми информационными входами соответственно сумматоров 10 и 11, вторые информационные входы которых .соединены соответственно с выходами сдвигателя 13 и с выходами коммутаQ

5

Q

тора 2.0, а также с вторыми информаи - онными входами сумматоров 9 и 12, третьи информационные входы которых соединены соответственно с выходами коммутатора 16 и с. выхода сдвигателя 14, входы управления вторыми информационными входами сумматоров соединены между собой и с выходом элемента И 29 (сигнал U.,), входы блоков памяти Работа соединены между собой и с входами Работа сумматоров 10 и 11, с первыми и вторыми входами Чтение блоков 1-4, с входами управления третьим .состоянием выходов элементов И 5-8 и являются четвертым управляюишм входом устройства, (сигнал и), первыми адресными входами которого являются соединенные вместе вторые входы Адрес блока 1, первые входы Адрес блока 4, первые информационные входы блока 32 сравнения и мпад1Ш1е вьгходных разрядов регистра 26 (сигнал U;,), старшей выходной разряд которого соединен с первым входом элемента 24 (сигнал Ь „) , выход которого соединен с входом Сложение/вычитание сумматора 11, с первым входом Сложение/вычитание сумматора 1.2, с первым входом Сложе- ние/вьиитание сумматора 9 (сигнал и ), второй вход Сложение/вычитание которого соединен с входом Сложение/вычитание сумматора 10 и с выходом элемента Ш1И-НЕ 25 (сигнал U,), второй вход которого соединен с выходом старшего разряда регистра 33 и с первым входом элемента И 23 (сигнал и ig) , выход которого соединен с вторым входом (Сложение/вычитание сумматора 12 (сигнал Vio), а второй вход соединен с вторым входом элемента К 24, с входом управления третьим состоя шем выходов регистров 26 и 33 и является пятым- упра.вляю1 1им входом устройства (сигнал Uj),вторыми адресными входам которого являются соединенные вместе младшие k выходных разрядов регистра 33, первые входы Адрес блока 1, BTopt.ie входы Адрес блоке 4 и вторые информационною входы блока 32 совпадений (сигнал и), выход блока 32 соединен с вторым входом элемента И-НЕ 29 и с первым входом элемента ИЛИ 30 (сигнал и), второй вход которого соединен с вторыми информаи 1он.ными входами элементов И 6 и 7 и является uiecTbiM управляю1 Д1м входом устройства

10

20

25

(сигнал и „), третьими адресными вхо- дами которого являются соединенные вместе первые информационные входы блока 27 совпадений, первые входы Адрес блока 2 и вторые входы Адрес блока 3 (сигналы U), четвертыми адреснь1ми входами являются соединенные вместе вторые информационные входы блока 27, первые входы Адрес блока 3 памяти и вторые входы Адрес блока 2 памяти (сигнал U), седьмым управляющим входом являются соединенные вместе вторые информационные входы элементов И 5 и 8, вторые входы Запись блоков 1 и 4 и входы управления коммутаторов 15,18,19 и 22 (сигнал U), а восьмыми управля- югцими входами являются соединенные вместе входы Сдвиг сдвигателей 13 и 14 (сигналы и,р , информационные входы которых соединены соответственно с выходами коммутатора 17 и с выходом коммутатора 21.

Двухпортовые блоки 1-4 памяти адресуются независимо по своим первым и вторым входам Адрес, причем первые входы Адрес, Запись и Чтение относятся к .первым входам-выходам, вторые - к вторым входам-выходам и могут быть построены на элементах 1802 ИР К Группы элементов И 5-8 могут быть построены на элементах 531 JIA 17, сумматоры 9-12 должны иметь входные регистры и могут быть построены на элементах 1802 ИМ К Комбинационные сдвигатели 13 и 14 могут быть построены на элементах 531 liP 21, регистры 26,28, 31 и 33 - на элементах 533 ИР 16, схемы 27 и 32 совпадения - на элементах 531 СП 1 (задействован вькод А-В).

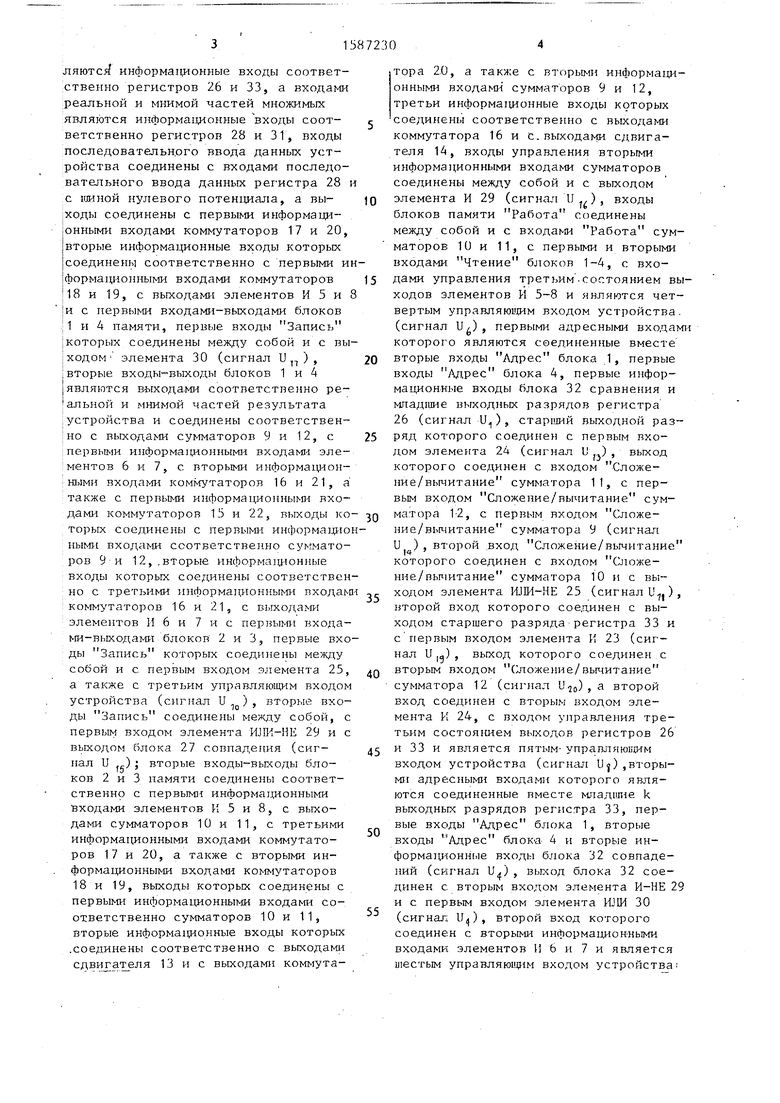

На фиг. 2 показаны диаграммы сигналов на соответствуюищх адресных и управляющих входах устройства, а же на входах управления блоков, входящих в состав устройства:

запись в блоки памяти 1,...,4 разрешается уровнем логической 1 (сигналы Uj, и,,,и,,,и„);

чтение их блоков 1, „. „,4 памяти разрешается уровнем логической 1 (сигнал и);

разрешение перевода в активное состояние выходов элементов 5,...,а и сумматоров 9,,12 осуществляется уровнем логической 1 (сигнал U);

разрешение загрузки информации во внутренние входные регистры сумматоров 9,.о.,12 осуществляется уровнем логической 1., (сигналы U, ,

и )

,

сложение числа на первых информа- щюнных Входах сумматоров 9 и 12 с числом на их третьих информационных входах осуществляется по уровню логического О сигнала U , вычитание из числа на первых {Информационных входах числа на третьих информационных входах - по уровню логичес- кой 1 сигнала U. Управление операцией на вторых информационных входах этих сумматоров, а также сумматоров 10 и 11 осущест вляется аналогич но сигналам U,j,U(,;

числа на вторых информационных входах сумматоров 9 и 12 загружайтся

в их входные регистры лишь в случае равенства сигнала 16 уровню логической 1, в противном случае числа на этих входах не оказьгоают влияния на работу сумматоров;

отсутствию сдвига входной информации сдвигателями 13 и 14 соответствует код 00 (сигналы U ,j) , сдвигу на один разряд влево - код 01, на два - 10, при этом освобождающиеся 30 разряды заполняются нулями;

подключение первых информационных входов коммутаторов 15, 18, 19 и 22 к их выходам осуществляется уровнем логической 1 сигнала Uj-, вторых информационных входов - уровнем логического О этого сигнала;

подключение первых информационных входов коммутаторов 16, 17, 20 и 21 к их выходам соответствует код 40 (сигналы U-,) , вторых информационных входов - код 10, третьих -

загрузка информации в регистры 26,28,31 и 33 разрешается уровнем 45 логического О сигнала Ug , сдвиг - уровнем логической

выходы регистров 26 и 33 переводятся в третье состояние уровнем

50

55

логического О сигнала U, и активны при равенстве логической 1 этого сигнала;

в случае равенства сигналов U и и, Из сигналы U ,,г и U равны уровню логического О, в противном случае - уровню логической 1.

Устройство умножения с накоплением комплексных чисел работает следующим образом.

158723U

- е0

маторов 9,.о.,12 осуществляется уровнем логической 1., (сигналы U, ,

и )

,

сложение числа на первых информа- щюнных Входах сумматоров 9 и 12 с числом на их третьих информационных входах осуществляется по уровню логического О сигнала U , вычитание из числа на первых {Информационных входах числа на третьих информационных входах - по уровню логичес- кой 1 сигнала U. Управление операцией на вторых информационных входах этих сумматоров, а также сумматоров 10 и 11 осущест вляется аналогично сигналам U,j,U(,;

числа на вторых информационных входах сумматоров 9 и 12 загружайтся

в их входные регистры лишь в случае равенства сигнала 16 уровню логической 1, в противном случае числа на этих входах не оказьгоают влияния на работу сумматоров;

25

30

выходы регистров 26 и 33 переводятся в третье состояние уровнем

логического О сигнала U, и активны при равенстве логической 1 этого сигнала;

в случае равенства сигналов U и и, Из сигналы U ,,г и U равны уровню логического О, в противном случае - уровню логической 1.

Устройство умножения с накоплением комплексных чисел работает следующим образом.

Реальная и мнимая части множимы::, Которые должны быть представлены в Дополнительном коде, загружаются Соответственно в регистры 28 и 31 в Нпадшие п разрядов, старшие п разрядов этих регистров заполняются зна- комо Регистры 28 и 31 выполняют сдвиг влево сразу на k разрядов, при этом через последовательные входы {данных этих регистров освободдающи- еся разряды заполняются нулями. Ре- |альная и мнимая части множителей, которые должны быть представлены в прямом коде, загружаются соответственно в регистры 26 и 33, причем в нпад1Ш е (п-1) разрядов этих регистров загружаются модули, в п-й раз- 1ряд загружается нуль, а в (п+1) раз- ряд загружается знаковьш разряд. Ре- 1гистры 26 и 33 в толняют сдвиг впра- |во сразу на k разрядов, при этом зна :ковьпЧ разряд в сдвигах не участвует. |Таким образом, модули реальной и мни мой частей множителей разбиваются на М k-разрядных груши Блоки 1 и 4 содержат 21 ячеек памяти, блоки 2,3-2 ячеек 1. Внешние устройства, подключаемые к первому и второму адресным - входам устройства, должны обладать третьим состоянием на своих выходах Для правильной работы перед первым (после включения ) обращением к устройству необходимо осу- -ществить обнуление блоков 1,...,4 : памяти. Эта операция выполняется посредством холостого пуска устройства хотя бы для пары сомножителей. Работа устройства в этом режиме ничем не отличается от обьмной его раб оты, поэтоьгу не рассматриваеся, однако в дальнейшем предполагается, что холостой пуск вштолнен.

Для пояснения функи -ю-лирования устройства на следУюпрх этапах рассмотрим работу устройства на конкретном примере. Пусть , , количество сомножителей , а массив операндов имеет вид:

Рсллмглп:-:i.jiM.:niPenjii.ii..l1

O.onoODDI1.1n11000.01I001Uff,0000010

1.111111 l.nilUll0.00100001.00IOOII

u .UOOOOno .OOOOOlO1.00000100.0000011

1.11П100U.0000001l.OnOOQI1.C100001

(точкой условно отделены знаковые разряды, реальная и мнимая части мно- шгмьпс представлены в допол1штельном коде,множителей - в прямом).

Работа устройства по вьгшслению суммы произведений пар комплексньпх

0

5

20

25 30

35

40

45

50

55

чисел проходит в три этапа. Пер вый этап начинается установкой в 1 сигналов и, и, Ug, подачей на входы Сдвиг сдвигателей 13 и 14 кода 00 (сигналы и,)., кода 01 на входы управления коммутаторов 16, 17, 20 и 21 (сигналы U-,) и одновременной загрузки первой пары сомножителей в регистры 26,28,31 и 33 В первой половине этого и каждого следующего такта первого этапа работы устройства во входные регистры сумматоров 9,..о,12 загружается содержимое регистров 28 и 31 и ячеек памяти блоков 1 и 4, адреса которых задаются мпадшими k выходными разрядами регистров 26 и 33, а во второй половине такта результат суммирования (вычитания) загружается в : те же ячейки блоков 1 и Чтение и запись в блоки 1 и 4 памяти (на втором этапе работы устройства - в блоки 1,0 и., 4, памяти), перевод в актив-, ное состояние выходов схем 5, о..,8 и сумматоров 9,.,. ,,12, загрузка информации во входные регистры сумматоров 9,...0,1 2 осу1цествляется в соответствующие моменты времени общим тактируюнщм сигРЕалом (не показан) с Во втором такте сигнал Uj устанашш- вается в 1 и в конце этого такта ячейки памяти 1,4 блоков с адресами, определяемыми сдвинутыми разрядами регистров 26. и 33, будет загружен результат суммирования (вычитания) сдвинутого содержимого, регистров 28 и 31 и чисел, хранившихся в этих ячейках до начала такта (сдвиг в регистрах 26,28,31 и 33 также осуществляется обищм тактируюиулм сигналом) . В поа1едую115-1х тактах первого этапа устройство работает аналогично, причем в случае равенства адресов ячеек памяти на первых и втор.ых входах Адрес блоков 1 и 4 сигнал U i, с выхода блока 32 устана вливается в О, что обеспечивает запрещение записи ин- формаци:и по первым портам блоков 1 и 4. Суммирование в этом случае ведется только сумматорами 9 и 12 (сигнал и., устанавливается в 1, разрешая загрузку информации по вторым входам сумматоров 9,12). Этим устраняется неопределенность, возникающая при записи различной информации в одну и ту же ячейку двухпортовых блоков 1,4 памяти о Кроме того, для правильной работы устройства сигналы и, и J должны быть равными (например, нулю) на протяжении всего первого этапа работы устройства (при этом сигнал и,- равен О и нет записи по вторым входам-выходам в блоки 2 и 3) Дпя данного конкретного примера первьй этап включает 8 тактов Диаграммы управляющих сигналов представлены на фиг. 2.

Результатом работы устройства на первом этапе является накопление в ячейках памяти блоков 1 и 4 сумм частичных произведений о Для получения конечного результата необходимо перемножить содержимое каждой ячейки на ее адрес и сложить полученные результаты Это выполняется на втором этапе работы устройства аналогичным образом

Второй этап работы устройства включает в себя ряд циклов (для данного примера - два ) . Первьй цикл (такты с 9 по 24 включительно)начи10

1 сигналов Uj сигналов Uj, UQ и подачей

нается установкой в

.- .

хода 10 на входы управления коммутаторов 16,17(20 и 21 и Сдвиг сдвкгател ей 13,14 (сигналы U, U ) В этом цикле, роль текугщх множимых играет содержимое ячеек памяти блоков 1,4, их адреса играют роль множителей, которые разбиваются пополам, В первой половине первого и последующих тактов первого цикла во входные регистры сумматоров 9 и 1 Г загружается содержимое текущих ячеек памяти блоков -1 и 4, адреса которых определяются сигналом U , и ячеек памяти блоков 2 и 3, адреса которых (сигналы иj)определяются младшими

k

2 разрядами сигналов U, Во второй

половине такта результат суммирования загружается в-те же ячейки памяти блоков 2 и Зо Аналогично, в первой половине каждого такта первого цикла во входные регистры сумматоров 10 и 12 загружается сдвинутое сдвигателями 13 и 14 на | разрядов

1587230 JO

реса ячеек памяти блоков t и 4 (сиг налы Uj, и) равны в каждом такте первого цикла и пробег ают значения от О до 2 % В конце каждого такта первого цикла по первым входам-выхо дам в использованные ячейки памяти блоков 1 и 4 загружаются нули. В случае равенства сигналов U и U схемой -27 запрещае тся запись по вторым входам-выходам блоков 2 и 3 (сигнал и ,5 устанаапивается в О), суммирование в этом случае ведется сумматорами 9 и 12, а результаты загружаются по первыг.1 входам-выходам в блоки 2 и 3 о

Результатом работы устройства в первом 1щкле второго этапа являются новые, сформированные в блоках 2-и 3 массивы сумм частичных произведений, размеры которых уменьшены в 2 раз а также обнуление блоков 1 и 4„

Второй цикл (последний для данного примера, такты с 26 по 28 включительно) начинается установкой в 1 сигнала U и в О сигнала U , подачей кода 11 на входы управлегшя коммутаторов 16, 17, 20 и 21 (сигналы и ,) и кода 01 на входы Сдлиг сдвигателей 13 и 14. В этом цикле роль текущих множимых играет содер15

20

25

30

жимое ячеек памяти блоков 2 и 3,

их

адреса - роль множителей, которые опять разбиваются пополам Работа устройства во втором аналогич35 на работе в первом цикле за исключе- нием того, что результаты суммирования накапливаются в блоках 1 и 4 Сигналы и, определяются младимми k

40 4 Разрядами сигналов U., и U з, сигнаjлы и - старшими разрядами, сдвигатели 13 и 14 осуществляют сдвиги

k 45 на разрядов влево, а в конце цикла

содержимое блоков 2 и 3 обнуляется В остальных циклах второго этапа число которых в общем случае зависит от выбранного k, устройство работавлево содержимое ячеек памяти блоков 50 ет аналогично. Размеры массивов час1 и 4, адреса которых определяются

сигналами U, равными U , и ячеек

памяти блоков 2 и 3, адреса которых

(сигналы и,) определяются старшими

k

2 разрядами кодов сигналов U U

Во второй Половине такта результат суммирования опять загружается в те же ячейки памяти блоков 2 и 3. Адтичных произведений, формируемых в блоках 1 и 4 или 2 и 3, убывают. В результате таких преобразований к концу последнего цикла (в данном при- 55 мере уже к концу второго цикла) получаются массивы, состояние всего из двух элементов (в данном примере эт массивы находятся в блоках 1 и 4). В ячейке памяти с единичным адресом

10

587230 JO

реса ячеек памяти блоков t и 4 (сигналы Uj, и) равны в каждом такте первого цикла и пробег ают значения от О до 2 % В конце каждого такта первого цикла по первым входам-выходам в использованные ячейки памяти блоков 1 и 4 загружаются нули. В случае равенства сигналов U и U схемой -27 запрещае тся запись по вторым входам-выходам блоков 2 и 3 (сигнал и ,5 устанаапивается в О), суммирование в этом случае ведется сумматорами 9 и 12, а результаты загружаются по первыг.1 входам-выходам в блоки 2 и 3 о

Результатом работы устройства в первом 1щкле второго этапа являются новые, сформированные в блоках 2-и 3 массивы сумм частичных произведений, размеры которых уменьшены в 2 раза а также обнуление блоков 1 и 4„

Второй цикл (последний для данного примера, такты с 26 по 28 включительно) начинается установкой в 1 сигнала U и в О сигнала U , подачей кода 11 на входы управлегшя коммутаторов 16, 17, 20 и 21 (сигналы и ,) и кода 01 на входы Сдлиг сдвигателей 13 и 14. В этом цикле роль текущих множимых играет содер15

20

25

30

жимое ячеек памяти блоков 2 и 3,

их

тичных произведений, формируемых в блоках 1 и 4 или 2 и 3, убывают. В результате таких преобразований к концу последнего цикла (в данном при- 55 мере уже к концу второго цикла) получаются массивы, состояние всего из двух элементов (в данном примере эт массивы находятся в блоках 1 и 4). В ячейке памяти с единичным адресом

находится представленный в дополни- тфльном коде результат вычислений, кЬторьй может быть снят с выходов результата устройства во второй по- лЬвине последнего такта последнего 141кла второго этапа работы устрой- (в данном случае во второй по- л|овине 28-го такта) с

: Обнуление ячеек памяти блоков, rhe к концу второго этапа находится результат вычислений, т.е„ подготовка устройства к работе с новым массивом операндов, происходит на третьем этапе, включающем в себя два зтапа. В данном примере результат вычислений находится в блоках 1 и А, г|оэтому третий этап начинается ус- ановкой в О сигналов U5, U и U . Сигналы и,, IL, могут находиться

f2

произвольном состоянии, сигналы , и J быть равны друг дру- fy (фиг. 2, такты 29,30)о В третьем :1тапе устройство работает аналогич- jio. В первом такте этапа (29-й такт) Ыгналы и равны нулю, поэтому об- 1уля1отся ячейки памяти блоков 1 и 4, b нулевьпми адресами, при этом для Гюддержания сигнала U,-, в 1 сигналы и должны быть не.равны сигналам и (на фиг. 2 для определеннос- :ти они равны единице) . Во втором такте третьего этапа аналогично об- -нуляются ячейки с единичными адреса- мио Если k выбрано так, что к кон- |цу второго этапа результат находит- ся в блоках 2 и 3, то к началу треть его цикла в О устанавливаются сиг- налы и и и,1, сигналы 11., U могут ;быть в произвольном СОСТОЯНИИ, сигналы и,, U4. должны быть равны друг другу о В первом такте сигналы U и Uj равны нулю, поэтому обнуляются ячейки памяти блоков 2 и 3 с нулевыми адресами„ Во втором такте аналогично обнуляются ячейки с единичными адресами К концу третьего этапа устройство готово к работе с новыми массивами операндов, либо может быт переведено в режим Ожидание, когд сигналы и и и, U i Ug попарно раны друг другу, сигналы U, U, и. ,... ,U ,1 установлены в О, сигналы и, могут находиться в произвольном состоянии (фиг. 2). В этом режиме в устройстве не вьшолня ются никакие действия , Формула изобретени Устройство для умножения с накоплением комплексньпс чисел, содержаще

5

0

5

30

35

40

45

50

55

регистры реальной и мнимой частей множимого, регистры реальной и мни-мой частей множителя, первый и второй двухвходовые .сумматоры, первый и второй трехвходовые коммутаторы, выходы регистра реальной части множимого соединены с первыми информацион- ньми входами первого и второго трех- входовых коммутаторов, входы управления которых соединены с первыми управляю1 ими входами устройства, второй управляющий вход устройства соединен с входом Сдвиг-загрузка регистров реальной и мнимой частей множимого и множителя, входы реальной и мнимой частей множителей устройства соединены соответственно с информационными входами регистров реальной и мнимой частей множителя, а входы реальной и мнимой частей множимых соединены с информационными входами соответственно регистров реальной и мнимой частей множимого, отличающееся тем, что, с целью, увеличения быстродействия при получени1- суммь парных произведений комплексных чисел, введены первый и второй двухпортовые блоки памяти реальной части, первый,и второй двухпортовые блоки памяти мнимой части, первая, вторая,,третья и четвертая группы элементов И, первьй, второй, третий и четвертый двухвходовые коммутаторы, третий и четвертьпЧ трехвходовые коммутаторы, первый и второй блоки совпадения, первый и второй элементы И, первый и второй элементы ИЛИ-НЕ, элемент ИЛИ, входы последовательного ввода данных регистра мнимой части множимого соединены с входами последовательного ввода данных регистров реальной части множимого и с шиной нулевого потенциала, а выходы регистра мнимой части соединены с первыми информационными входами третьего и четвертого трехвходовых коммутаторов, входы управления которых соединены с входами управления первого и второго трехвходовых коммутаторов и с первыми управляющими входами устройства, вторые информационные входы третьего и четвертого трехвходовых коммутаторов соединены соответственно с первыми информационными входами первого и второго двухвходовых коммутаторов, с выходами первой и второй групп элемента И, с первыми входами-выходами первых блоков памяти реальной и

13

мнимой частей, первые входы Запис которых соединены с выходами элемета ИЛИ, а вторые входы-выходы явля выходами результата соответственно реальной и мнимой частей устройства и соединены соответственно с выходами первого и второго трех- входовых сумматоров, с первыми информационными входами третьей и четвертой групп элементов И, с вторыми информационными входами первого и второго трехвходовых коммутаторов, первыми информационными входами третьего и четвертого двухвходовых коммутаторов, выходы которых соединены с первыми информационными входами соответственно первого и второго трехвходовых сумматоров, вторы . информационные входы которых соединены соответственно с третьими инфо ма1Д10}шыми входами первого и второго трехвходовых коммутаторов, выходами третьей и четвертой групп элементов И, с первыми входами-выходами вторых блоков памяти реальной и мнимой частей, первые входы Запись которых соединены с первым входом первого элемента ШШ-НЕ и с третьим управляюищм входом устройства, вторые входы Запись вторых блоков памяти реальной и мнимой частей соединены с первым входом второго элемента ИЛИ-НЕ и с выходом первого блока совпадения, вторые входы-выходы блоков памяти реальной и мнимой частей соединены соответственно с первыми информационными входами первой и второй групп элементов И, с выходами первого и второго двухвходовых сумматоров, с третьими информационными входами третьего и четвертого трехвходовых коммутаторов и с вторыми информа ционными входами первого и второго двухвходовых коммутаторов, выходы которых соединены с первыми информационными входами соответственно первого и второго двухвходовых сумматоров, вторые информационные входы которых соединены соответственно с выходами первого комбинационного сдвигателя и с выходами четвертого трехвходового коммутатора, а также с вторыми информационными входами первого и второго трехвходовых сумматоров, третьи информационные входы которых соединены} соответственно с выходами первого трехвходового ког-1мутатора и с выхо

587230

U

10

15

20

25

0

5

дами второго комбинащюнного сдвигателя, входы управления вторыми информационными входами,первого и второго трехвходовых сумматоров соединены с выходом второго элемента ШШ-НК, а входы Работа соединены с входаьш Работа первого и второго двухвходовых сумматоров, с первым и вторым входами Чтение первых и вторых блоков памяти реальной и мнимой частей, с входаъш управления третьим состояinieM выходов первой, второй, третьей и четвертой групп элементов И, с четверть управляющими входами устройст-ва, первые адресные входы которого соединены с вто- рыми входами Адрес первого блока памяти реальной части, первыми входами Адрес первого блока памяти мнимой части, с первыми информационными входами второго блока совпадения и младшими выходными разрядами регистра реальной части мно/игтеля, выход старшего разряда которого соединен с первым входом первого элемента И, выход которого соединен с входом Сложение-вычитание второго двухвходо- вого сумматора, с первым входом Сложение-вычитание второго трех- . входного сумматора и с первым входом Сложение-вычитание первого трехвходового сумматора, второй вход Сложение-вычитание которого соединен с входом Сложение-вычитание 35 первого двухвходового сумматора и с . выходом первого элемента ИЛИ-НЕ, второй вход которого соединен с выходом старшего разряда регистра мнимой части множителя и с первым входом второго элемента И, выход которого соединен с вторым входом Спо- жение-вьгчитание второго трехвходового сумматора, второй вход второго элемента И соединен с вторым входом первого элемента И, с входами управления третьим состоянием выходов регистров реальной и мнимой частей множителя и с пятым управляюищм входом устройства, вторые адресные входы которого соединены с выходами младших разрядов регистра мнимой части множителя, первыми входами Адрес первого блока памяти реальной части, вторыми входами Адрес первого бло- Iка памяти мнимой части и вторыми ин-| формахщонными входами второго блока совпадения, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ

30

40

45

Фиг.1

Jm

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения с накоплением комплексных чисел | 1987 |

|

SU1478211A1 |

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Устройство для умножения с накоплением | 1987 |

|

SU1451683A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

Изобретение относится к вычислительной технике, и может быть использовано в высокопроизводительных вычислительных системах в качестве сопроцессора и позволяет повысить быстродействие. Устройство содержит четыре блока памяти для накопления частичных произведений реальных и мнимых частей и операционную часть, состоящую из четырех сумматоров, коммутаторов, сдвигателей. Быстродействие достигается за счет двухэтапной векторной обработки массива данных. Первый этап включает векторную операцию образования в блоках памяти массива частичных произведений, на втором этапе получают результат путем векторной операции умножения и суммирования частичных произведений. 2 ил.

| Устройство для умножения с накоплением | 1988 |

|

SU1509876A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сомотюк М.В., Ноюн В.П | |||

| Операционные устройства для суммирования парных произведений и перемножения комплексных чисел | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1988-05-30—Подача