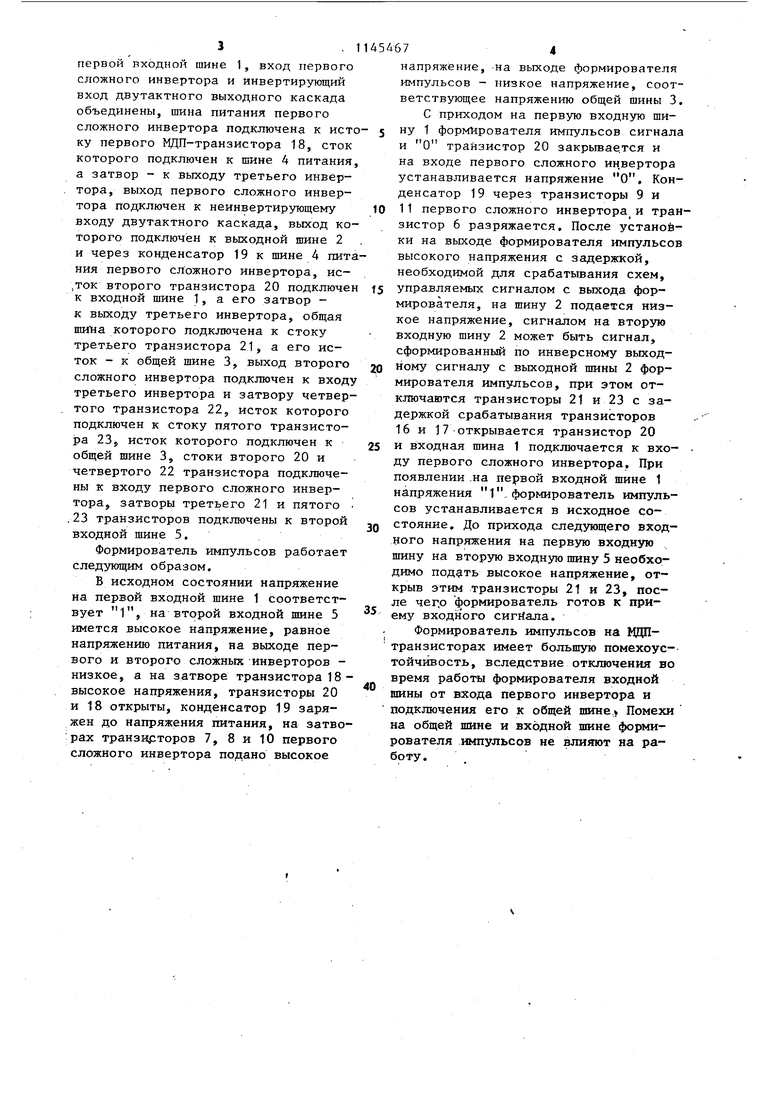

Изобретение относится к электронике и может быть использовано в им пульсных интегральных схемах на МДП-транзисторах. Известен формирователь импульсов используемый в качестве входной согласующей схемы состоящей из двух инверторов с общим входом, причем затвор нагрузочного транзистора вто рого инвертора подключен к выходу первого l . Недостатки устройства - высокая рассеивающая мощность и сниженньй уровень выходного напряжения. Наиболееблизок к предлагаемому формирователь импульсов на ЩП-тран зисторах, содержащий первую входную выходную и общую шину питания5 двутактный выходной каскад на .МДП-тран зисторах обогащенного типа, первый и второй сложные инверторы, третий инвертор с нагрузочным МДП-транзистором обедненного типа, первый МДПтранзистор обедненного типа и конденсатор, причем вход второго сложного инвертора подключен к первой входной шине, вход первого сложного инвертора и инвертирующий вход двутактного выходного каскада объедине ны, шина питания первого сложного .инвертора подключена к истоку первого МДП-транзистора обедненного ти па, сток которого подключен к шине питания5 а затвор - к выходу третьего инвертора, выход первого сложно инвертора подключен к неинвёртирующему входу двутактного каскада, вы ход двутактного каскада подключен к выходной шине и через конденсатор к шине питания первого сложного инвертора 2 „ Недостатками известного формирователя импульсов являются малая помехоустойчивость j при появлении помех на входной шине, малое выходное напряжение на выходной шине, (меньшее, чем напряжение источника питания j на величину падения напряжения на выходных транзисторах), а та же большая потребляемая мощность от источника питания. Цель изобретения - повьш1ёние,помехоустойчивости и снижение потребляемой мопршсти. Поставленная цель достигается тем, что в формирователь импульсов на ВДП-транзисторах, содержащий пер .вую входную, выходную, общую шины и шину питания, двутактньпЧ выходной каскад на НПП-траизисторах обогащенного типа, первый и второй сложные инверторы, третий инвертор с нагрузочным МЛП-транзистором обедненного типа, первый Щ ;П-тра зистор обедненного типа и конденсатор, причем вход второго сложного инвертора подключен к первой входной шине, вход первого сложного инвертора и инвертирующий входдвутактного выходного каскада объединены, шина, питания первого сложного инвертора подключена к истоку первого МДП-транзистора обедненного типа, сток которого подключен к шине питания, а затвор - к вы.ходу третьего инвертора, выход, первого сложного инвертора подключен к неинвертирующему входу двутактного каскада, выход двутактного каскада подключен к выходной шине и через конденсатор к шине питания первого сложного инвертора дополнительно введены вторая входная шина, второй, третий, четвертый и пятый МДП транзисторы обогащенного типа, при этом исток второго транзистора подключен к входной шине, а его затвор - к выходу третьего инвертора, общая шина которого подключена к стоку третьего-транзистора, а его исток - к обг: ш;ей шине5 выход второго сложного инвертора подключен к входу третьего инвертора и затвору четвертого транзистора, исток которого подключен к стоку пятого транзистора, исток которого подключен к общей шине, стоки второго и четвертого транзистора подключены к входу первого сложного инвертора, затворы третьего и пятого транзисторов подключены к вто рой входной шине. - . На чертеже приведена принципиальная схема формирователя импульсов. Формирователь импульсов содержит первую входную 1, выходную 2 и общую 3 шины, шину 4 питания, BTOPJTO входную шину 5, двутактный выходной каскад на МДП-транзисторах 6 и 7 обогащенного типа, первый сложный инвертор на транзисторах 8-11, состояш 1Й из инвертора с нагрузочным транзис тором 9 обедненного типа и двутакт- ного ключа с транзистором 11 обедненного типа, второй сложный инвертор на транзисторах 12-15 третий инвертор на транзисторах 16 и 17, первый МДП-транзистор 18 обедненного типа и конденсатор 19, npi-мем вход второго сложного инвертора подключен к

3,

первой входной шине 1, вход первого сложного инвертора и инвертирующий вход двутактного выходного каскада объединены, шина питания первого сложного инвертора подключена к ист ку первого МДП-транзистора 18, сток которого подключен к шине 4 питания а затвор - к выходу третьего инвертора, выход первого сложного инвертора подключен к неинвертирующе входу двутактного каскада, выход которого подключён к выходной шине 2 и через конденсатор 19 к шине 4 пит ния первого сложного инвертора, ис,ток второго транзистора 20 подключе к входной шине 1, а его затвор к выходу третьего инвертора, общая miiHa которого подключена к стоку третьего транзистора 21, а его исток - к общей шине 3, выход второго сложного инвертора подключен к вход третьего инвертора и затвору четвертого транзистора 22, исток которого подключен к стоку пятого транзистора 23, исток которого подключен к общей шине 3, стоки второго 20 и четвертого 22 транзистора подключены к входу первого сложного инвертора, затворы третьего 21 и пятого .23 транзисторов подключены к второй входной шине 5.

Формирователь импульсов работает следующим образом.

В исходном состоянии напряжение на первой входной щине 1 соответствует 1, на второй входной шине 5 имется высокое напряжение, равное напряжению питания, на выходе первого и второго сложных инверторов низкое, а на затворе транзистора 18высокое напряжения, транзисторы 20 и 18 открыты, конденсатор 19 заряжен до напряжения питания, на затворах транзцрторов 7, 8 и Ю первого сложного инвертора подано высокое

454674

напряжение, на выходе формирователя импульсов - низкое напряжение, соответствующее напряжению общей шины 3. С приходом на первую входную шину 1 формирователя импульсов сигнала и О транзистор 20 закрьгоае.тся и на входе первого сложного инвертора устанавливается напряжение О, Конденсатор 19 через транзисторы 9 и 10 11 первого сложного инвертора и транзистор 6 разряжается. После установки на выходе формирователя импульсов высокого напряжения с задержкой, необходимой для срабатывания схем, t5 управляемых сигналом с выхода формирователя, на шину 2 подается низкое напряжение, сигналом на вторую входную шину 2 может быть сигнал, сформированный по инверсному выходному сигналу с выходной шины 2 формирователя импульсов, при этом отключаются транзисторы 21 и 23 с задержкой срабатывания транзисторов 16 и 17 открывается транзистор 20 25 и входная шина 1 подключается к входу первого сложного инвертора. При появлении ,на первой входной шине 1 напряжения 1. формирователь импульсов устанавливается в исходное состояние. До прихода следующего входного напряжения на первую входную шину на вторую входную шину 5 необходимо подать высокое напряжение, открыв этим транзисторы 21 и 23, после чегр формирователь готов к приему входного сигнала.

Формирователь импульсов на ВДПтранзисторах имеет большую помехоустойчивость, вследствие отключения во время работы формирователя входной шины от входа первого инвертора и подключения его к общей шине Помехи на общей шине и входной шине формирователя импульсов не влияют на работу.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU911692A1 |

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Формирователь импульсов | 1983 |

|

SU1166279A1 |

| Формирователь импульсов | 1981 |

|

SU1003348A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Формирователь импульсов | 1981 |

|

SU991507A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Формирователь импульсов | 1982 |

|

SU1091327A1 |

| Формирователь импульсов на МДП-транзисторах | 1982 |

|

SU1172003A1 |

ФОРМИРОВАТЕЛЬ РМПУЛЬСОВ на ЩП-транзисторах, содержащий первую входную, выходную, общую шину и шину питания, двутактный выходной каскад на МПД-транзисторах обогащенного типа, первый и второй сложные инверторы, третий инвертор с нагрузочным МДП-транзистором обедненного типа, первый адп-транзистор обедненного типа и конденсатор, причем вход второго сложного инвертора подключен к первой входной шине, вход первого сложного инвертора и инвертирующий вход двутактного выходного каскада объединены, шина питания первого сложного инвертора подключена к истоку первого ВДП-гранзистора обедненного типа, сток которого подключен к шине питания, а затвор.к выходу третьего инвертора, выход первого сложного инвертора подключен к неинвертирующему входу двутактного каскада, выход двутактного каскада подключен к выходной шине и через конденсатор к шине питания первого сложного инвертора, отличающийся тем, что, с целью повышения помехоустойчивости, дополнительно введены вторая входная шина, второй, третий, четвертый и пятый МДП-транзисторы обогащенного типа, при этом исток втфрого транзистора подключен к входной шине, а его затi вор - к выходу третьего инвертора, общая шина которого подключена к (Л стоку третьего транзистора, а его исток - к общей шине, выход второго сложного инвертора подключен к входу третьего инвертора и затвору четвертого транзистора, исток которого подключен к стоку пятого транзистора, исток которого подключен к общей шине стоки второго и четвертого транзисторов подключены к входу первого ел сложного инвертора, затворы третьего, 4 Од и пятого транзисторов подключены к второй входной шине.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент ФРГ 2926156, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| , 2 | |||

| Формирователь импульсов | 1980 |

|

SU919062A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-15—Публикация

1983-07-29—Подача